Изобретение относится к устройствам для обработки цифровых данных с помощью электрических устройств, в частности к устройствам для передачи данных.

Известно устройство [1] для передачи данных, содержащее блок передачи данных и блок приема данных, подключенные к противоположным сторонам канала связи, состоящего из первой и второй линий связи, блок передачи данных содержит первый микропроцессор, соединенный с первым блоком памяти и регистром, выходы которого через первый и второй усилители подключены к первой и второй линиям связи, блок приема данных содержит третий и четвертый усилители, входы которых подключены к первой и второй линиям связи, а выходы - к входному порту, выходы которого соединены с входами второго микропроцессора, соединенного с вторым блоком памяти.

Устройство [1] предназначено для синхронной передачи данных по каналу связи. Сигналы в первой и второй линиях канала связи представлены двумя уровнями. Первый уровень соответствует лог. 0, второй - лог. 1. Блок передачи данных формирует поток битов, выдаваемый в первую линию. При этом синхросигнал выдается во вторую линию и формируется таким образом, чтобы его фронты определяли границы битовых интервалов при передаче одноименных битов (последовательности лог. 0 или лог. 1) по первой линии. Блок приема данных восстанавливает исходный синхросигнал по совокупности фронтов сигналов в линиях канала связи.

Недостатком устройства [1] является низкая скорость передачи кадров данных. Из-за отсутствия аппаратных средств передачи по каналу связи кадровых синхроимпульсов в потоке данных присутствуют флаги, предваряющие начало каждого кадра. Флаг представляет собой некоторую уникальную последовательность битов, которая не встречается в теле кадра. Чтобы обеспечить такую уникальность, применяют битстаффинг - добавление служебных битов в поток полезных данных. Добавление флаговых кодов и служебных битов в поток "полезных" данных приводит к снижению скорости его передачи.

Известно устройство [2] для передачи данных, содержащее блок передачи данных и блок приема данных, подключенные к противоположным сторонам канала связи, состоящего из первой и второй линий связи, блок передачи данных содержит первый элемент Исключающее ИЛИ, первый и второй усилители, выходы которых подключены к первой и второй линиям связи, блок приема данных содержит третий и четвертый усилители, входы которых подключены к первой и второй линиям связи, элемент И, инвертор, блок фазовой автоподстройки частоты, первый, второй и третий триггеры, выход инвертора соединен с входом синхронизации первого триггера, выход которого соединен с входом данных второго триггера.

Устройство [2] предназначено для синхронной передачи данных по каналу связи. Под управлением сигнала битовой синхронизации в блок передачи данных от внешнего источника информации поступают данные и кадровые синхроимпульсы. Из блока передачи данных по первой линии канала связи передается сигнал данных, по второй - обобщенный сигнал синхронизации, в котором суммированы (по модулю два) битовые и кадровые синхросигналы. В блоке приема данных суммарный синхросигнал разделяется на кадровые и битовые синхроимпульсы, которые вместе с данными передаются во внешний приемник информации.

Недостатками устройства [2] являются низкая скорость передачи данных и повышенный уровень генерируемых перекрестных помех. Низкая скорость обусловлена тем, что передача каждого бита данных (за исключением размещенных на стыках между кадрами) сопровождается двукратным изменением состояния сигнала во второй линии канала связи. Повышенный уровень генерируемых перекрестных помех возникает из-за того, что в энергетическом спектре синхросигнала, передаваемого по второй линии канала связи, доминирует одна частотная составляющая. Эта составляющая передается на соседние провода кабеля из-за наличия емкостных и индуктивных паразитных связей и приводит к появлению в них наведенных сигналов помехи.

Цель изобретения - повышение скорости передачи данных и уменьшение уровня генерируемых перекрестных помех.

Цель достигается тем, что в устройстве для передачи данных, содержащем блок передачи данных и блок приема данных, подключенные к противоположным сторонам канала связи, состоящего из первой и второй линий связи, блок передачи данных содержит первый элемент Исключающее ИЛИ, первый и второй усилители, выходы которых подключены к первой и второй линиям связи, блок приема данных содержит третий и четвертый усилители, входы которых подключены к первой и второй линиям связи, элемент И, инвертор, блок фазовой автоподстройки частоты, первый, второй и третий триггеры, выход инвертора соединен с входом синхронизации первого триггера, выход которого соединен с входом данных второго триггера, блок передачи данных дополнительно содержит сдвиговый регистр, генератор синхросигналов, четвертый и пятый триггеры, второй и третий элементы Исключающее ИЛИ, первый выход генератора синхросигналов является первым выходом битовой синхронизации устройства, второй выход генератора синхросигналов соединен с входами синхронизации сдвигового регистра, четвертого и пятого триггеров, первый выход сдвигового регистра соединен с входом первого усилителя и с первым входом первого элемента Исключающее ИЛИ, второй выход сдвигового регистра соединен с вторым входом первого элемента Исключающее ИЛИ, выход которого соединен с первым входом второго элемента Исключающее ИЛИ, второй вход которого соединен с нулевым выходом пятого триггера, выход второго элемента Исключающее ИЛИ соединен с первым входом третьего элемента Исключающее ИЛИ, второй вход которого соединен с выходом четвертого триггера, выход третьего элемента Исключающее ИЛИ соединен с входом данных пятого триггера, единичный выход которого соединен с входом второго усилителя, вход данных сдвигового регистра является входом данных устройства, вход данных четвертого триггера является входом кадровой синхронизации устройства, блок приема данных дополнительно содержит первый и второй формирователи импульсов и элемент ИЛИ, выход третьего усилителя соединен с входом первого формирователя импульсов и с входом данных третьего триггера, выход которого является выходом данных устройства, выход четвертого усилителя соединен с входом второго формирователя импульсов, выход которого соединен с первыми входами элементов И и ИЛИ, выход первого формирователя импульсов соединен с вторыми входами элементов И и ИЛИ, выход элемента И соединен с входом установки единицы первого триггера, вход данных которого соединен с шиной нулевого потенциала, выход элемента ИЛИ соединен с входом блока фазовой автоподстройки частоты, выход которого является вторым выходом битовой синхронизации устройства и соединен с входами синхронизации второго и третьего триггеров и с входом инвертора, выход второго триггера является выходом кадровой синхронизации устройства.

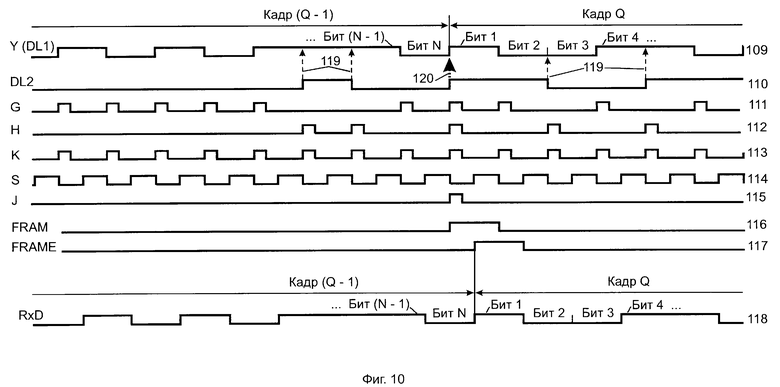

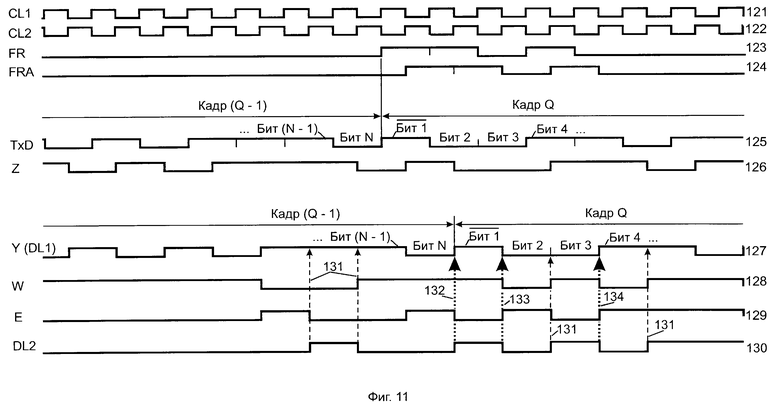

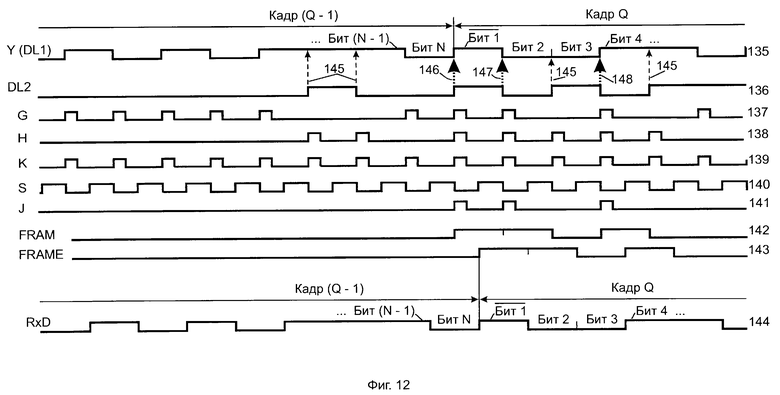

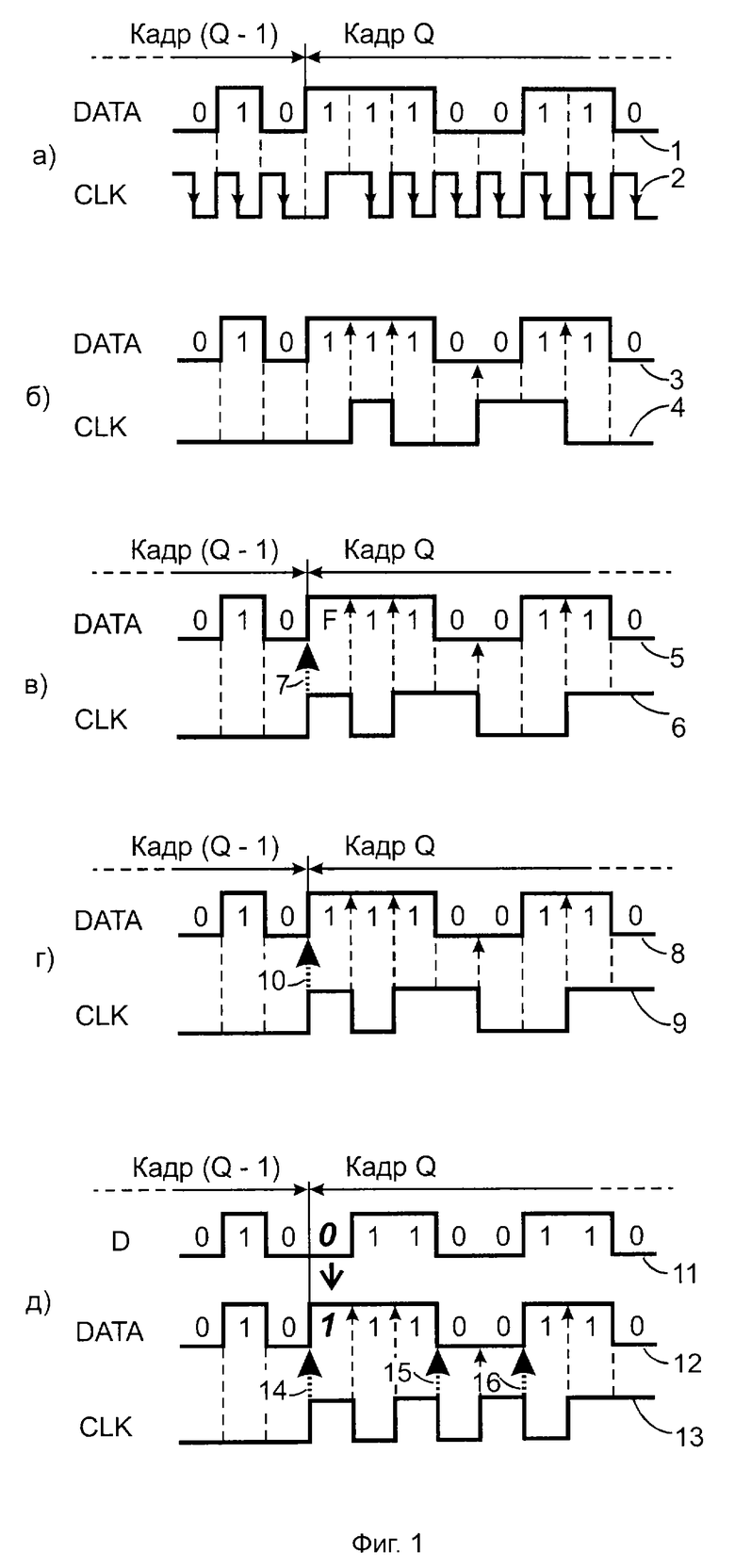

На фиг. 1 представлены временные диаграммы, поясняющие способы передачи данных, применяемые при использовании известных и предлагаемого устройств; на фиг.2 - пример схемы включения предлагаемого устройства в телекоммуникационную систему; на фиг.3 - структурная схема блока передачи данных; на фиг. 4 - структурная схема блока приема данных; на фиг.5 и фиг.6 - временные диаграммы работы блоков передачи и приема данных в отсутствие кадровых синхроимпульсов; на фиг.7 и фиг.8 - временные диаграммы работы блоков передачи и приема данных при пересылке кадров с однобитовыми флагами; на фиг.9 и фиг.10 - временные диаграммы работы блоков передачи и приема данных при пересылке бесфлаговых кадров с разноименными битами по обеим сторонам межкадровой границы; на фиг.11 и фиг.12 - временные диаграммы работы блоков передачи и приема данных при пересылке бесфлаговых кадров с одноименными битами по обеим сторонам межкадровой границы.

Временные диаграммы 1 и 2 (фиг.1, а) соответствуют сигналам данных DATA и синхронизации CLK, формируемым в устройстве [2]. Временные диаграммы 3 и 4 (фиг. 1, б) определяют правила кодирования и соответствуют сигналам данных DATA и синхронизации CLK в устройстве [1]. Временные диаграммы 5 и 6 (фиг.1, в) соответствуют сигналам данных DATA и синхронизации CLK, принятым в предлагаемом устройстве при передаче кадров с однобитовым флагом F; 7 - момент преднамеренного нарушения принятых в [1] правил кодирования. Временные диаграммы 8 и 9 (фиг.1, г) соответствуют сигналам данных DATA и синхронизации CLK, принятым в предлагаемом устройстве при передаче бесфлаговых кадров с разноименными битами по обеим сторонам межкадровой границы; 10 - момент преднамеренного нарушения правил кодирования. Временные диаграммы 11, 12 и 13 (фиг.1, д) соответствуют сигналам исходных данных D, преобразованных данных DATA с искусственно введенной ошибкой и сигналу синхронизации CLK, принятым в предлагаемом устройстве при передаче бесфлаговых кадров с одноименными битами исходных данных D по обеим сторонам межкадровой границы; 14, 15 и 16 - моменты преднамеренных нарушений правил кодирования.

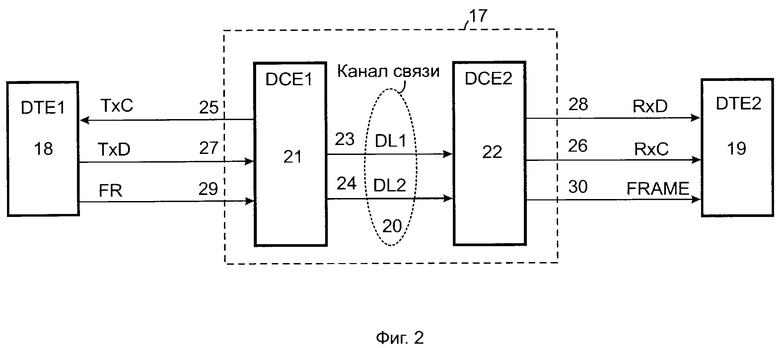

Телекоммуникационная система (фиг.2) содержит предлагаемое устройство 17 для передачи данных и подключенные к нему первое 18 и второе 19 оконечные устройства DTE1 и DTE2. Устройство 17 содержит подключенные к противоположным сторонам канала связи 20 блок 21 передачи данных DCE1 и блок 22 приема данных DCE2. Канал связи 20 содержит первую 23 и вторую 24 линии связи. Выходы 25 и 26 блоков 21 и 22 являются первым и вторым выходами битовой синхронизации устройства 17. Вход 27 блока 21 и выход 28 блока 22 являются входом и выходом данных устройства 17. Вход 29 блока 21 и выход 30 блока 22 являются входом и выходом кадровой синхронизации устройства 17.

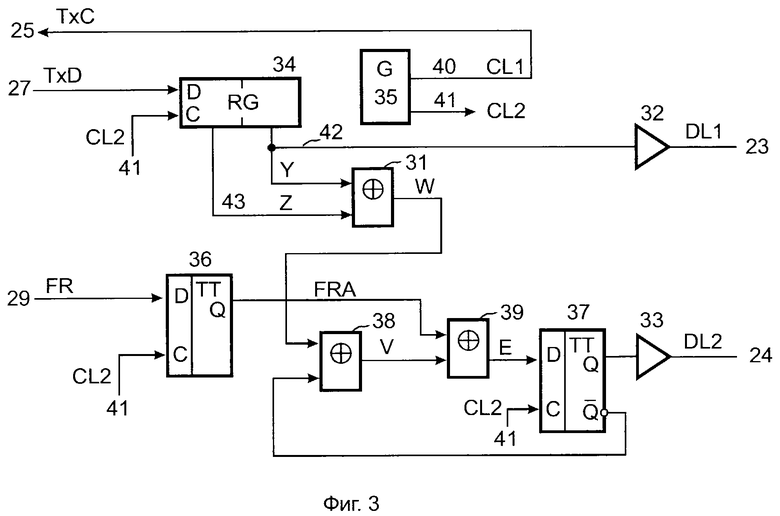

Блок 21 передачи данных (фиг.3) содержит первый элемент Исключающее ИЛИ 31, первый 32 и второй 33 усилители, выходы которых подключены к первой 23 и второй 24 линиям связи, а также сдвиговый регистр 34, генератор 35 синхросигналов, четвертый 36 и пятый 37 триггеры, второй 38 и третий 39 элементы Исключающее ИЛИ, первый выход 40 генератора 35 синхросигналов является первым выходом 25 битовой синхронизации устройства, второй выход 41 генератора 35 синхросигналов соединен с входами синхронизации сдвигового регистра 34, четвертого 36 и пятого 37 триггеров, первый выход 42 сдвигового регистра 34 соединен с входом первого усилителя 32 и с первым входом первого элемента Исключающее ИЛИ 31, второй выход 43 сдвигового регистра 34 соединен с вторым входом первого элемента Исключающее ИЛИ 31, выход которого соединен с первым входом второго элемента Исключающее ИЛИ 38, второй вход которого соединен с нулевым выходом пятого триггера 37, выход второго элемента Исключающее ИЛИ 38 соединен с первым входом третьего элемента Исключающее ИЛИ 39, второй вход которого соединен с выходом четвертого триггера 36, выход третьего элемента Исключающее ИЛИ 39 соединен с входом данных пятого триггера 37, единичный выход которого соединен с входом второго усилителя 33, вход данных сдвигового регистра 34 является входом 27 данных устройства, вход данных четвертого триггера 36 является входом 29 кадровой синхронизации устройства.

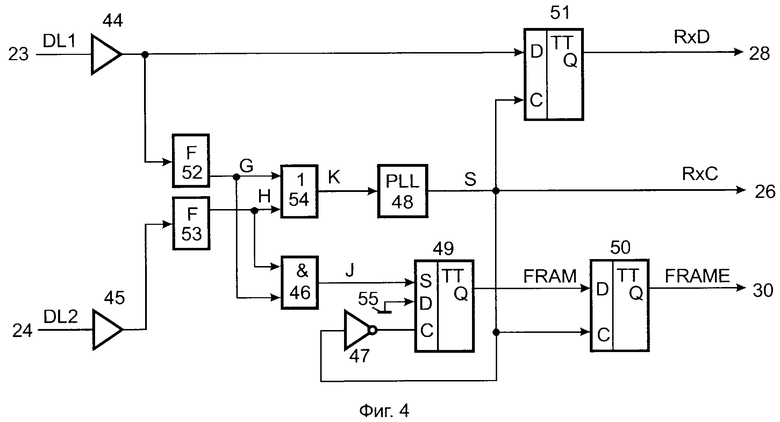

Блок 22 приема данных (фиг.4) содержит третий 44 и четвертый 45 усилители, входы которых подключены к первой 23 и второй 24 линиям связи, элемент И 46, инвертор 47, блок 48 фазовой автоподстройки частоты, первый 49, второй 50 и третий 51 триггеры, выход инвертора 47 соединен с входом синхронизации первого триггера 49, выход которого соединен с входом данных второго триггера 50. Блок 22 приема данных содержит также первый 52 и второй 53 формирователи импульсов и элемент ИЛИ 54, выход третьего усилителя 44 соединен с входом первого формирователя 52 импульсов и с входом данных третьего триггера 51, выход которого является выходом 28 данных устройства, выход четвертого усилителя 45 соединен с входом второго формирователя 53 импульсов, выход которого соединен с первыми входами элементов И 46 и ИЛИ 54, выход первого формирователя 52 импульсов соединен с вторыми входами элементов И 46 и ИЛИ 54, выход элемента И 46 соединен с входом установки единицы первого триггера 49, вход данных которого соединен с шиной 55 нулевого потенциала, выход элемента ИЛИ 54 соединен с входом блока 48 фазовой автоподстройки частоты, выход которого является вторым выходом 26 битовой синхронизации устройства и соединен с входами синхронизации второго 50 и третьего 51 триггеров и с входом инвертора 47, выход второго триггера 50 является выходом 30 кадровой синхронизации устройства.

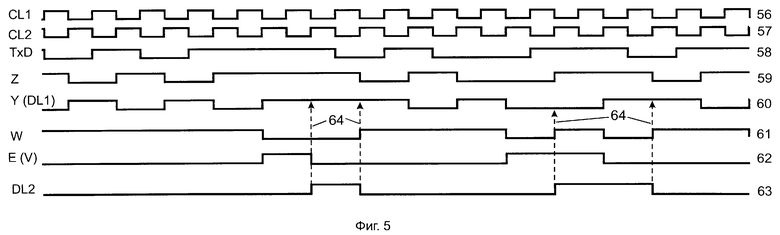

Временные диаграммы 56 и 57 (фиг.5) соответствуют сигналам на выходах 40 и 41 генератора 35 синхросигналов. Временные диаграммы 58, 59 и 60 отображают сигналы в точках 27, 43 и 42 (23) блока 21. Временные диаграммы 61, 62 и 63 соответствуют сигналам на выходах элементов 31, 39 и в линии 24. Указатели 64 соответствуют "недостающим" фронтам сигнала в линии 23.

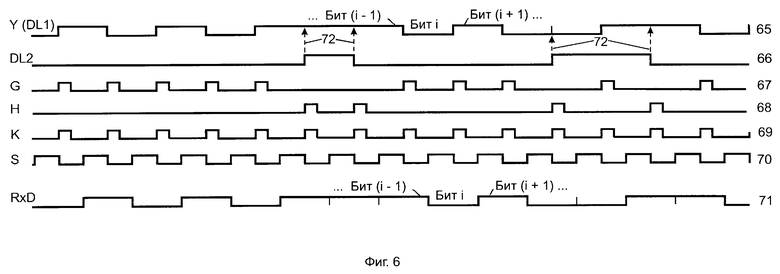

Временные диаграммы 65 и 66 (фиг.6) отображают сигналы в линиях 23 и 24. Временные диаграммы 67-71 соответствуют сигналам на выходах формирователей 52, 53 импульсов, на входе и выходе блока 48 и на выходе 28 блока 17. Указатели 72 соответствуют "недостающим" фронтам сигнала в линии 23.

Временные диаграммы 73 и 74 (фиг.7) соответствуют сигналам на выходах 40 и 41 генератора 35 синхросигналов. Временные диаграммы 75 и 76 соответствуют сигналам на входе данных и выходе триггера 36. Временные диаграммы 77, 78 и 79 отображают сигналы в точках 27, 43 и 42 (23) блока 21. Временные диаграммы 80, 81 и 82 соответствуют сигналам на выходах элементов 31, 39 и в линии 24. Указатели 83 соответствуют "недостающим" фронтам сигнала в линии 23. Указатель 84 соответствует моменту нарушения правил кодирования.

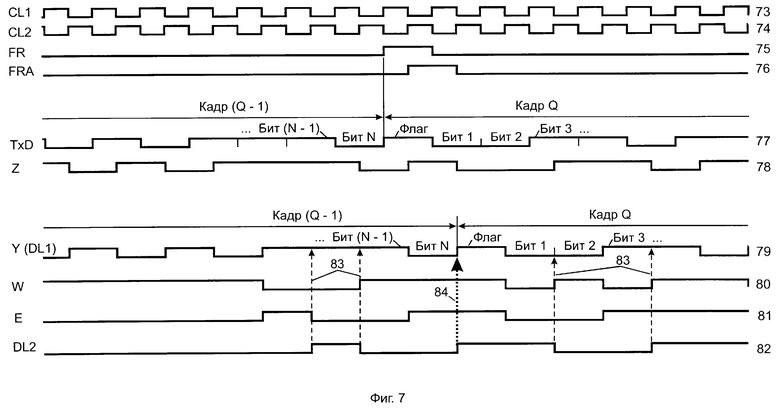

Временные диаграммы 85 и 86 (фиг.8) отображают сигналы в линиях 23 и 24. Временные диаграммы 87-90 соответствуют сигналам на выходах формирователей 52, 53 импульсов, на входе и выходе блока 48. Временные диаграммы 91-94 соответствуют сигналам на выходе элемента И 46, на входе данных и выходе триггера 50 и на выходе 28 блока 22. Указатели 95 соответствуют "недостающим" фронтам сигнала в линии 23. Указатель 96 соответствует моменту нарушения правил кодирования.

Временные диаграммы 97 и 98 (фиг.9) соответствуют сигналам на выходах 40 и 41 генератора 35 синхросигналов. Временные диаграммы 99 и 100 соответствуют сигналам на входе данных и выходе триггера 36. Временные диаграммы 101, 102 и 103 отображают сигналы в точках 27, 43 и 42 (23) блока 21. Временные диаграммы 104, 105 и 106 соответствуют сигналам на выходах элементов 31, 39 и в линии 24. Указатели 107 соответствуют "недостающим" фронтам сигнала в линии 23. Указатель 108 соответствует моменту нарушения правил кодирования.

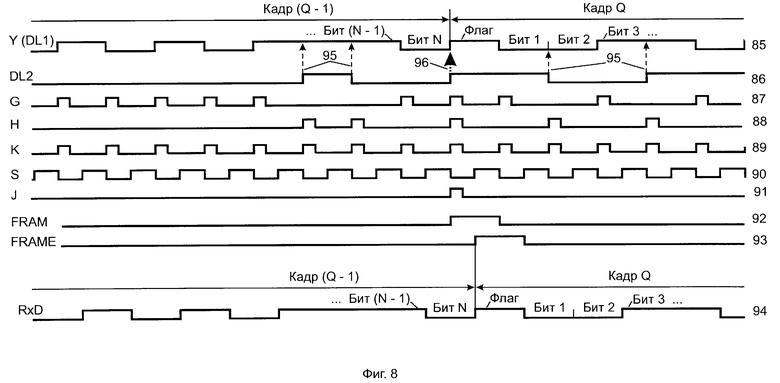

Временные диаграммы 109 и 110 (фиг.10) отображают сигналы в линиях 23 и 24. Временные диаграммы 111-114 соответствуют сигналам на выходах формирователей 52, 53 импульсов, на входе и выходе блока 48. Временные диаграммы 115-118 соответствуют сигналам на выходе элемента И 46, на входе данных и выходе триггера 50 и на выходе 28 блока 22. Указатели 119 соответствуют "недостающим" фронтам сигнала в линии 23. Указатель 120 соответствует моменту нарушения правил кодирования.

Временные диаграммы 121 и 122 (фиг.11) соответствуют сигналам на выходах 40 и 41 генератора 35 синхросигналов. Временные диаграммы 123 и 124 соответствуют сигналам на входе данных и выходе триггера 36. Временные диаграммы 125, 126 и 127 отображают сигналы в точках 27, 43 и 42 (23) блока 21. Временные диаграммы 128, 129 и 130 соответствуют сигналам на выходах элементов 31, 39 и в линии 24. Указатели 131 соответствуют "недостающим" фронтам сигнала в линии 23. Указатели 132, 133 и 134 соответствуют моментам нарушения правил кодирования.

Временные диаграммы 135 и 136 (фиг.12) отображают сигналы в линиях 23 и 24. Временные диаграммы 137-140 соответствуют сигналам на выходах формирователей 52, 53 импульсов, на входе и выходе блока 48. Временные диаграммы 141-144 соответствуют сигналам на выходе элемента И 46, на входе данных и выходе триггера 50 и на выходе 28 блока 22. Указатели 145 соответствуют "недостающим" фронтам сигнала в линии 23. Указатели 146, 147 и 148 соответствуют моментам нарушения правил кодирования.

Далее рассмотрены способы передачи данных, применяемые при использовании известных (фиг.1, а, б) и предлагаемого (фиг.1, в-д) устройств.

Как показано на фиг. 1, а-д, из устройства-передатчика в устройство-приемник передаются сигналы DATA (диаграммы 1, 3, 5, 8, 12) и CLK (диаграммы 2, 4, 6, 9, 13). Сигнал DATA предназначен для передачи последовательного потока битов данных. В примерах, приведенных на фиг.1, каждому биту из передаваемой последовательности 01011100110 выделен так называемый битовый интервал. Границы между битовыми интервалами показаны на диаграммах штриховыми линиями. Сигналам лог. 1 и лог. 0 в данных примерах соответствуют напряжения высокого и низкого уровней.

Непрерывный поток битов, передаваемый между телекоммуникационными устройствами (передатчиком и приемником), обычно представлен в виде последовательности некоторых структурных единиц, например кадров.

Сигнал CLK предназначен для разделения потока данных на битовые интервалы. В примерах, показанных на фиг.1, а, в-д, этот же сигнал позволяет приемнику определять межкадровые границы. Источник синхросигналов может конструктивно размещаться в передатчике, приемнике или вне того и другого.

На временных диаграммах, показанных на фиг.1, а, [2], показан "стык" между двумя кадрами с номерами Q-1 и Q. Из этих диаграмм следует, что первый битовый интервал кадра Q сопровождается однократным нарушением регулярной последовательности импульсов сигнала CLK. Точнее, в этом интервале истинность передаваемого бита подтверждается положительным фронтом сигнала CLK, тогда как во всех остальных интервалах установившиеся значения сигналов данных соответствуют отрицательным фронтам сигнала CLK (на диаграмме 2 эти фронты помечены вертикальными стрелками). Приемник, обнаружив "неоднородность" сигнала CLK, принимает к сведению факт завершения предыдущего и начала следующего кадра. Такой способ синхронизации не обеспечивает высокой скорости передачи данных. Это связано с тем, что каждому биту данных, за исключением первого в кадре, соответствуют два изменения сигнала CLK (а не одно изменение, как в последующих примерах). Другой недостаток состоит в том, что энергетический спектр сигнала CLK содержит ярко выраженный максимум на частоте, равной скорости передачи данных. Эта спектральная составляющая передается на соседние провода кабеля из-за наличия емкостных и индуктивных паразитных связей, что приводит к появлению наведенных сигналов помехи.

При передаче данных согласно временным диаграммам 3 и 4, приведенным на фиг.1, б, [1], сигнал синхронизации CLK изменяется только в тех случаях, когда сигнал DATA остается неизменным. Таким образом, на любой границе битового интервала изменяется либо сигнал DATA, либо сигнал CLK (но не оба одновременно, как в некоторых ситуациях при работе предлагаемого устройства). Приемник отслеживает изменения этих сигналов и в любой ситуации располагает информацией о местоположении границ битовых интервалов.

Такой способ передачи данных требует не более одного изменения сигнала CLK в каждом битовом интервале. Иными словами, временная диаграмма 4 по сравнению с диаграммой 2 "в два и более раз низкочастотна". Поэтому если "сжать" диаграммы 3 и 4 по горизонтали в два раза, то при той же максимальной частоте сигнала CLK, что и на диаграмме 2, получим удвоенную скорость передачи. Еще одно преимущество: по сравнению с предыдущим способом передачи данных (см. фиг. 1, а), данный способ "разравнивает" энергетический спектр сигнала CLK. Теперь он не содержит выраженного спектрального максимума, что способствует снижению уровня генерируемых перекрестных помех, воздействующих на соседние провода кабеля. В данном решении, однако, не предусмотрены аппаратные средства выделения границ кадров.

Способы передачи данных (фиг.1, в-д) с помощью предлагаемого устройства близки только что описанному (см. фиг.1, б). Точно так же "недостающие" фронты сигнала DATA восполняются гарантированными фронтами сигнала CLK. Но теперь сигнал CLK в дополнение к функции восполнения "потерянных" битовых границ отображает также и межкадровые границы.

В предлагаемом решении кадры могут передаваться двумя основными способами. Первый (фиг.1, б) подразумевает наличие флагового (служебного) бита F в начале каждого кадра; второй способ (фиг.1, г, д) применим к передаче кадров "стык в стык", без введения каких-либо служебных битов вблизи межкадровых границ. Второй способ предпочтителен, так как данные передаются с большей скоростью благодаря исключению из потока "лишних" (с точки зрения потребителя данных) битов F. Но этот способ, в отличие от первого, требует некоторых "интеллектуальных затрат" со стороны потребителя данных, так как в среднем в половине ситуаций нужно не только вычислить положение межкадровой границы, но и проинвертировать первый бит кадра, как будет показано далее. Рассмотрим оба способа подробнее.

Первый способ позволяет обозначить межкадровую границу выполнением следующих двух правил.

Правило 1.1. Флаговый бит F кадра Q (см. фиг.1, в) выбирается противоположным последнему биту предыдущего кадра Q - 1. В данном примере эти биты равны соответственно 1 и 0. Это обеспечивает гарантированный перепад уровней сигнала DATA на межкадровой границе.

Правило 1.2. На межкадровой границе сигнал CLK изменяет состояние. В данном примере сигнал CLK на межкадровой границе переходит из 0 в 1.

В результате выполнения обоих правил создается "уникальная" кодовая ситуация, при которой изменению сигнала CLK соответствует изменение (а не статическое состояние) сигнала DATA. Эта ситуация обозначена стрелкой-указателем 7 и может рассматриваться как допустимое нарушение правил кодирования, принятых в [1]. Действительно, межбитовая граница в данном случае продублирована одновременно изменяющимися сигналами DATA и CLK, что не может ухудшить качество синхронизации между приемником и передатчиком. Приемник воспринимает эту кодовую ситуацию как межкадровую границу.

Второй способ позволяет обозначить межкадровую границу выполнением следующих двух правил.

Правило 2.1. Если по обеим сторонам межкадровой границы присутствуют разноименные биты (01 или 10), то сигнал CLK на этой границе изменяет состояние, см. фиг.1, г, указатель 10. Эта ситуация, по существу, аналогична рассмотренной ранее (см. указатель 7) и отличается от нее только тем, что вместо служебного бита F передается "полезный" бит, который "случайно" оказался противоположным предыдущему.

Правило 2.2. Если по обеим сторонам межкадровой границы первоначально присутствуют одноименные биты (00 или 11), то перепад уровней сигнала DATA на этой границе создается искусственно, инвертированием первого бита кадра Q, как показано на фиг. 1, д. В приведенном примере исходные данные D (диаграмма 11) содержат нулевые биты по обеим сторонам межкадровой границы, но, благодаря инвертированию первого бита кадра Q, сигнал данных DATA с искусственно внесенной ошибкой содержит перепад уровней на этой границе. Чтобы отличить эту ситуацию от предыдущей (см. правило 2.1), в сигнал CLK вводится не одно, а ряд описанных ранее нарушений правил кодирования. Первое из них (указатель 14) соответствует межкадровой границе. В данном примере используются три следующих подряд нарушения правил (указатели 14 - 16), хотя возможны и иные "договоренности" между передатчиком и приемником. Приемник обнаруживает обусловленную "договором" последовательность нарушений правил, по первому из них определяет межкадровую границу и инвертирует первый бит кадра Q, восстанавливая исходную последовательность битов (см. диаграмму 11).

Чтобы обеспечить защиту от вырожденных кадров, например типа "все нули" или "все единицы", в которых вообще отсутствуют перепады сигнала данных, применяется скремблирование (особый вид шифрации потока данных, см., например, пат. США 5530959), при котором любые реальные потоки битов приобретают вид псевдослучайных. В таких потоках в среднем каждый второй битовый интервал содержит перепад уровней сигнала данных.

Далее рассмотрен пример схемы включения предлагаемого устройства в телекоммуникационную систему.

Предлагаемое устройство 17 для передачи данных (фиг.2) подключено к двум оконечным устройствам DTE1 18 и DTE2 19, например к двум компьютерам. В процессе работы системы данные передаются из устройства 18 в устройство 19. Для передачи данных в обратном направлении необходимо второе устройство 17, включенное встречно.

Пара сигналов ТхС - TхD на выходе 25 и входе 27 устройства 17 обеспечивает синхронную передачу данных из устройства 18 в блок 21. Положительные фронты сигнала ТхС задают границы битовых интервалов. По отрицательным фронтам сигнала ТхС соответствующие биты данных TхD временно запоминаются в блоке 21. Признак FR начала кадра формируется устройством 18 в виде сигнала лог. 1 и передается на вход 29 устройства 17 одновременно с первым битом этого кадра.

Пара сигналов RхC-RхD на выходах 26 и 28 устройства 17 обеспечивает синхронную передачу данных из блока 22 в устройство 19. Положительные фронты сигнала RхC задают границы битовых интервалов. По отрицательным фронтам сигнала RхC соответствующие биты данных RxD запоминаются в устройстве 19. Признак FRAME начала кадра формируется устройством 17 на выходе 30 в виде сигнала лог. 1 и передается на вход устройства 19 одновременно с первым битом этого кадра.

По линиям 23 и 24 канала связи 20 передаются сигналы DL1 и DL2 -аналоги сигналов DATA и CLK, показанных ранее на диаграммах 5, 6; 8, 9; 12, 13, фиг. 1, б-д. Канал связи 20 может быть выполнен в виде двух витых пар проводов, двух оптоволоконных линий или иных средств передачи сигналов, в том числе, содержащих ретрансляторы.

Далее рассмотрены три режима работы предлагаемого устройства. В первом режиме данные передаются без кадровых синхроимпульсов, см. фиг.1, б. Во втором режиме передаваемые кадры помечены флагами F, см. фиг.1, в. В третьем режиме кадры не содержат флаговых битов, см. фиг.1, г, д.

Первый режим работы устройства

Все процессы, протекающие при передаче данных, синхронизированы сигналами от генератора 35 (см. фиг.3). Сигнал CL1 (ТхС) с выхода 40 генератора 35 поступает на выход 25 устройства и далее передается в устройство DTE1 18. В ответ на этот сигнал из устройства DTE1 18 выдаются данные TхD. Они поступают на вход 27 устройства и далее на вход данных двухразрядного сдвигового регистра 34. Под действием положительных фронтов сигнала CL2 на входе 41 синхронизации этого регистра данные продвигаются в нем, выдаются через усилитель 32 в линию 23 и одновременно с этим анализируются элементом Исключающее ИЛИ 31. До тех пор, пока биты в регистре 34 чередуются (...010101...), формируется сигнал W= 1, который поддерживает элемент 38 в режиме инвертирования сигнала, поступающего с нулевого выхода триггера 37.

Так как в данном режиме сигнал FR кадровой синхронизации на входе 29 устройства отсутствует (постоянно равен лог. 0), триггер 36 постоянно находится в нулевом состоянии (FRA=0). При этом элемент 39 работает в режиме повторения сигнала V (Е=V). Сигнал с нулевого выхода триггера 37 возвращается на его вход данных после инвертирования элементом 38, поэтому в каждом такте текущее состояние этого триггера подтверждается (см. начальные участки временных диаграмм, приведенных на фиг.5). Сигнал DL2 в линии 24 остается неизменным.

Обнаружение элементом 31 одинаковых битов в регистре 34 означает, что в линии 24 необходимо создать перепад уровней сигнала. В этой ситуации сигнал W= 0 переводит элемент 38 в режим повторения сигнала с нулевого выхода триггера, так что этот триггер включается в счетный режим, при котором его состояние под действием тактового импульса CL2 изменяется на противоположное. Такие изменения в данном примере повторяются четыре раза и отмечены на фиг. 5 указателями 64. Как видно из диаграмм, эти указатели соответствуют "отсутствующим" фронтам сигнала в линии 23 (диаграмма 60).

Сигналы DL1 и DL2 (диаграммы 65 и 66, фиг.6) поступают в блок 22 приема данных (фиг.4) из линий 23 и 24, проходят через усилители 44, 45 и формирователи 52 и 53 импульсов. Сигнал G (диаграмма 67) на выходе формирователя 52 импульсов сопровождает любое изменение сигнала DL1, т.е. вырабатывается как по положительному, так и по отрицательному фронтам сигнала DL1. В данном примере в сигнале G импульсы отсутствуют на позициях, соответствующих вертикальным стрелкам 72 между диаграммами 66 и 65. Сигнал Н (диаграмма 68) на выходе формирователя 53 импульсов сопровождает любое изменение сигнала DL2, т. е. вырабатывается как по положительному, так и по отрицательному фронтам сигнала DL2. С помощью элемента ИЛИ 54 "недостающие" импульсы сигнала G восполняются, и сигнал К (диаграмма 69) представляет собой периодическую последовательность импульсов без "пробелов". Этот сигнал поступает на вход блока 48 фазовой автоподстройки частоты.

Блок 48 может быть выполнен по одной из известных схем (см., например, пат. США 6215835 В1). Он предназначен для формирования высокостабильного синхросигнала S (RхC) на основе непрерывного слежения за входным сигналом К. В данном примере отрицательный фронт сигнала S "привязан" к положительному фронту сигнала К. Благодаря достаточной "инерционности" блока 48 сигнал S практически нечувствителен к "дрожанию фазы" сигнала К и иным его кратковременным искажениям, вызванным помехами в канале связи. (Такое использование стандартного блока фазовой автоподстройки частоты в телекоммуникационных системах является общепринятым и далее не детализируется).

Так как в данном режиме импульсы G и Н никогда не формируются одновременно, сигнал J на выходе элемента И 46 постоянно равен 0, триггеры 49 и 50 находятся в нулевом состоянии. Принятые из канала связи данные проходят через триггер 51 и передаются на выход 28 устройства, см. диаграмму 71. Эта диаграмма полностью соответствует исходной диаграмме 58 (см. фиг.5) с учетом задержки передачи.

Второй режим работы устройства

Этот режим отличается от предыдущего тем, что на вход 29 кадровой синхронизации устройства периодически поступают однократные импульсы FR, соответствующие флаговым битам передаваемых кадров, см. фиг.7, 8. Это приводит к одновременному формированию фронтов сигналов в линиях 23 и 24, что отражено указателем 84. Указатели 83 соответствуют моментам формирования "недостающих" фронтов сигнала DL1, см. диаграммы 82 и 79.

В данном режиме, в отличие от предыдущего, в блоке приема данных в момент 96 (см. фиг.8) формируется сигнал J=1 (диаграмма 91), который устанавливает триггер 49 в единичное состояние. Сигнал с выхода этого триггера проходит через триггер 50 и поступает на выход 30 кадровой синхронизации устройства. Диаграммы 94 и 93 полностью соответствуют исходным (77 и 75) с учетом задержки передачи.

Третий режим работы устройства

В этом режиме возможны две ситуации. Первая характеризуется наличием противоположных битов по обеим сторонам межкадровой границы. В этом случае временные диаграммы, приведенные на фиг.9 и 10, отличаются от диаграмм на фиг.7 и 8 только тем, что вместо флагового бита передается первый "полезный" бит данных кадра. Вторая ситуация также характеризуется наличием противоположных битов по обеим сторонам межкадровой границы, но, как уже отмечалось, первый бит кадра преднамеренно искажен для создания гарантированного перепада уровней сигнала DL1 на межкадровой границе. Чтобы отличить вторую ситуацию от первой, вместо одного передаются три кадровых импульса.

На диаграммах, приведенных на фиг.11, показана ситуация, при которой на вход 29 кадровой синхронизации устройства поступает триада кадровых импульсов (диаграмма 123). Это приводит к появлению трех событий одновременного формирования фронтов сигналов в линиях 23 и 24, что отражено указателями 132, 133 и 134. Указатели 131 соответствуют моментам формирования "недостающих" фронтов сигнала DL1, см. диаграмму 127.

В данном режиме в блоке приема данных сигнал J=1 формируется троекратно, см. диаграмму 141 на фиг.12. Этот сигнал троекратно устанавливает триггер 49 в единичное состояние. (Отметим, что в D-триггере сигнал S установки единицы имеет более высокий приоритет, чем сигнал на динамическом входе С). Сигнал с выхода этого триггера проходит через триггер 50 и поступает на выход 30 кадровой синхронизации устройства. Как уже отмечалось, в данном примере получение устройством DTE2 19 серии близлежащих кадровых импульсов свидетельствует о необходимости инвертирования первого бита кадра.

Возможны также иные способы передачи данных с помощью предлагаемого устройства. Например, для повышения помехоустойчивости можно оперировать не одним и тремя кадровыми импульсами, а группами из М и 2М импульсов, где М ! 10.

Источники информации

1. Патент США 6044421.

2. Патент США 5724360 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214045C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

Изобретение относится к устройствам для передачи данных и может быть использовано в синхронных телекоммуникационных системах. Технический результат заключается в повышении скорости передачи данных и уменьшении уровня генерируемых перекрестных помех. Устройство содержит блоки передачи и приема данных, подключенные к противоположным сторонам канала связи, блок передачи данных содержит три элемента Исключающее ИЛИ, два усилителя, два триггера, сдвиговый регистр и генератор синхроимпульсов. Блок приема данных содержит два усилителя, элементы И, ИЛИ, инвертор, блок фазовой автоподстройки частоты, три триггера и два блока формирователей импульсов. Устройство передают по каналу связи кодированный сигнал, в котором содержится последовательный поток данных, сопровождаемый битовыми и кадровыми синхроимпульсами, при этом гарантируется изменение состояния канала в каждом битовом интервале. 12 ил.

Устройство для передачи данных, содержащее блок передачи данных и блок приема данных, подключенные к противоположным сторонам канала связи, состоящего из первой и второй линий связи, блок передачи данных сдержит первый элемент Исключающее ИЛИ, первый и второй усилители, выходы которых подключены к первой и второй линиям связи, блок приема данных содержит третий и четвертый усилители, входы которых подключены к первой и второй линиям связи, элемент И, инвертор, блок фазовой автоподстройки частоты, первый, второй и третий триггеры, выход инвертора соединен с входом синхронизации первого триггера, выход которого соединен с входом данных второго триггера, отличающееся тем, что блок передачи данных дополнительно содержит сдвиговый регистр, генератор синхросигналов, четвертый и пятый триггеры, второй и третий элементы Исключающее ИЛИ, первый выход генератора синхросигналов является первым выходом битовой синхронизации устройства, второй выход генератора синхросигналов соединен с входами синхронизации сдвигового регистра, четвертого и пятого триггеров, первый выход сдвигового регистра соединен с входом первого усилителя и с первым входом первого элемента Исключающее ИЛИ, второй выход сдвигового регистра соединен с вторым входом первого элемента Исключающее ИЛИ, выход которого соединен с первым входом второго элемента Исключающее ИЛИ, второй вход которого соединен с нулевым выходом пятого триггера, выход второго элемента Исключающее ИЛИ соединен с первым входом третьего элемента исключающее ИЛИ, второй вход которого соединен с выходом четвертого триггера, выход третьего элемента Исключающее ИЛИ соединен с входом данных пятого триггера, единичный выход которого соединен с входом второго усилителя, вход данных сдвигового регистра является входом данных устройства, вход данных четвертого триггера является входом кадровой синхронизации устройства, блок приема данных дополнительно содержит первый и второй формирователи импульсов, сигналы на выходе которых сопровождают любое изменение сигналов соответственно из первой и второй линий связи, и элемент ИЛИ, выход третьего усилителя соединен с входом первого формирователя импульсов и с входом данных третьего триггера, выход которого является выходом данных устройства, выход четвертого усилителя соединен с входом второго формирователя импульсов, выход которого соединен с первыми входами элементов И и ИЛИ, выход первого формирователя импульсов соединен с вторыми входами элементов И и ИЛИ, выход элемента И соединен с входом установки единицы первого триггера, вход данных которого соединен с шиной нулевого потенциала, выход элемента ИЛИ соединен с входом блока фазовой автоподстройки частоты, выход которого является вторым выходом битовой синхронизации устройства и соединен с входами синхронизации второго и третьего триггеров и с входом инвертора, выход второго триггера является выходом кадровой синхронизации устройства.

| US 5724360 A, 03.03.1998 | |||

| US 6044421 A, 28.03.2000 | |||

| СИНХРОНИЗАЦИЯ ПЕРЕДАЧИ ДАННЫХ В ДВУСТОРОННЕЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2156035C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

Авторы

Даты

2003-10-10—Публикация

2001-12-03—Подача