Изобретение относится к устройствам для обработки цифровых данных с помощью электрических устройств, в частности к устройствам для передачи данных.

Известно устройство [1] для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, первый и второй сдвиговые регистры и мультиплексор, выходы первого и второго сдвиговых регистров через мультиплексор подключены к первой линии канала связи, выходы генератора синхросигналов подключены к второй линии канала связи, к управляющим входам первого и второго сдвиговых регистров и мультиплексора и являются первым и вторым выходами синхронизации устройства, параллельные входы первого и второго сдвиговых регистров являются первой и второй группами входов данных устройства, блок приема данных содержит третий и четвертый сдвиговые регистры и формирователь синхросигналов, вход которого соединен с второй линией канала связи, входы последовательных данных третьего и четвертого сдвиговых регистров соединены с первой линией канала связи, выходы формирователя синхросигналов соединены с управляющими входами третьего и четвертого сдвиговых регистров и являются третьим и четвертым выходами синхронизации устройства, параллельные выходы третьего и четвертого сдвиговых регистров являются первой и второй группами выходов данных устройства.

Устройство [1] предназначено для синхронной передачи данных по каналу связи. По первой линии канала связи передается сигнал данных, по второй - сигнал синхронизации. Сигналы в первой и второй линиях канала связи представлены двумя уровнями. Первый уровень соответствует лог. 0, второй - лог. 1. Блок передачи данных формирует поток битов поочередной выдачей последовательных данных из первого и второго сдвиговых регистров. При этом истинность передаваемых в канал связи битов данных подтверждается поочередно положительными и отрицательными фронтами сигнала синхронизации. Блок приема данных поочередно принимает биты в третий и четвертый сдвиговые регистры под управлением положительных и отрицательных фронтов синхросигнала, принятого из канала связи.

Недостатками устройства [1] являются низкая скорость передачи данных и повышенный уровень генерируемых перекрестных помех. При частоте синхросигнала, равной F (Гц), скорость передачи данных равна 2F (бит/с). Повышенный уровень генерируемых перекрестных помех обусловлен тем, что в энергетическом спектре синхросигнала доминирует составляющая частотой F. Эта составляющая передается на соседние провода кабеля из-за наличия емкостных и индуктивных паразитных связей и приводит к появлению наведенных сигналов помехи.

Известно устройство [2] для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, сдвиговый регистр, элемент Исключающее ИЛИ, первый триггер, первый и второй усилители, первый выход генератора синхросигналов является первым выходом синхронизации устройства, второй выход генератора синхросигналов соединен с входами синхронизации сдвигового регистра и первого триггера, вход данных сдвигового регистра является первым входом данных устройства, первый выход сдвигового регистра соединен с первым входом элемента Исключающее ИЛИ и через первый усилитель - с первой линией канала связи, второй выход сдвигового регистра соединен с вторым входом элемента Исключающее ИЛИ, единичный выход первого триггера через второй усилитель соединен с второй линией канала связи, блок приема данных содержит третий и четвертый усилители, первый и второй формирователи импульсов, первый элемент ИЛИ, блок фазовой автоподстройки частоты и второй триггер, входы третьего и четвертого усилителей соединены с первой и второй линиями канала связи, выходы третьего и четвертого усилителей через первый и второй формирователи импульсов соединены с входами первого элемента ИЛИ, выход которого соединен с входом блока фазовой автоподстройки частоты, выход которого является вторым выходом синхронизации устройства и соединен с входом синхронизации второго триггера, единичный выход которого является первым выходом данных устройства, вход данных второго триггера соединен с выходом третьего усилителя.

Устройство [2] предназначено для синхронной передачи данных по каналу связи. По первой линии канала связи передается сигнал данных, по второй - сигнал синхронизации. Сигналы в первой и второй линиях канала связи представлены двумя уровнями. Первый уровень соответствует лог. 0, второй - лог. 1. Блок передачи данных формирует поток битов выдачей последовательных данных из сдвигового регистра. При этом синхросигнал формируется таким образом, чтобы его фронты определяли границы битовых интервалов при передаче одноименных битов. Блок приема данных восстанавливает исходный синхросигнал по совокупности фронтов сигналов в линиях канала связи.

Недостатком устройства [2] является низкая скорость передачи данных. Максимальная частота сигналов в первой или второй линиях канала связи составляет F (Гц), минимальная частота равна нулю. При этом сигналы взаимно дополняют друг друга. Скорость передачи данных постоянна и равна 2F (бит/с).

Цель изобретения - повышение скорости передачи данных.

Цель достигается тем, что в устройстве для передачи данных, содержащем подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, сдвиговый регистр, элемент Исключающее ИЛИ, первый триггер, первый и второй усилители, первый выход генератора синхросигналов является первым выходом синхронизации устройства, второй выход генератора синхросигналов соединен с входами синхронизации сдвигового регистра и первого триггера, вход данных сдвигового регистра является первым входом данных устройства, первый выход сдвигового регистра соединен с первым входом элемента Исключающее ИЛИ и через первый усилитель - с первой линией канала связи, второй выход сдвигового регистра соединен с вторым входом элемента Исключающее ИЛИ, единичный выход первого триггера через второй усилитель соединен с второй линией канала связи, блок приема данных содержит третий и четвертый усилители, первый и второй формирователи импульсов, первый элемент ИЛИ, блок фазовой автоподстройки частоты и второй триггер, входы третьего и четвертого усилителей соединены с первой и второй линиями канала связи, выходы третьего и четвертого усилителей через первый и второй формирователи импульсов соединены с входами первого элемента ИЛИ, выход которого соединен с входом блока фазовой автоподстройки частоты, выход которого является вторым выходом синхронизации устройства и соединен с входом синхронизации второго триггера, единичный выход которого является первым выходом данных устройства, вход данных второго триггера соединен с выходом третьего усилителя, блок передачи данных дополнительно содержит третий триггер, элемент И и мультиплексор, выход элемента Исключающее ИЛИ соединен с входом данных третьего триггера, выход которого соединен с управляющим входом мультиплексора и с первым входом элемента И, выход которого является третьим выходом синхронизации устройства, первый вход данных мультиплексора является вторым входом данных устройства, второй вход данных мультиплексора соединен с нулевым выходом первого триггера, вход данных которого соединен с выходом мультиплексора, первый выход генератора синхросигналов соединен с вторым входом элемента И, третий выход генератора синхросигналов соединен с входом синхронизации третьего триггера, блок приема данных дополнительно содержит третий формирователь импульсов, четвертый, пятый и шестой триггеры и второй элемент ИЛИ, выход которого является четвертым выходом синхронизации устройства, входы второго элемента ИЛИ соединены с выходами четвертого и пятого триггеров, входы установки нуля которых соединены с выходом третьего формирователя импульсов, а входы синхронизации - с единичным и нулевым выходами второго триггера, входы данных четвертого и пятого триггеров соединены с шиной положительного напряжения, вход третьего формирователя импульсов соединен с выходом блока фазовой автоподстройки частоты и с входом синхронизации шестого триггера, вход данных которого соединен с выходом четвертого усилителя, выход шестого триггера является вторым выходом данных устройства.

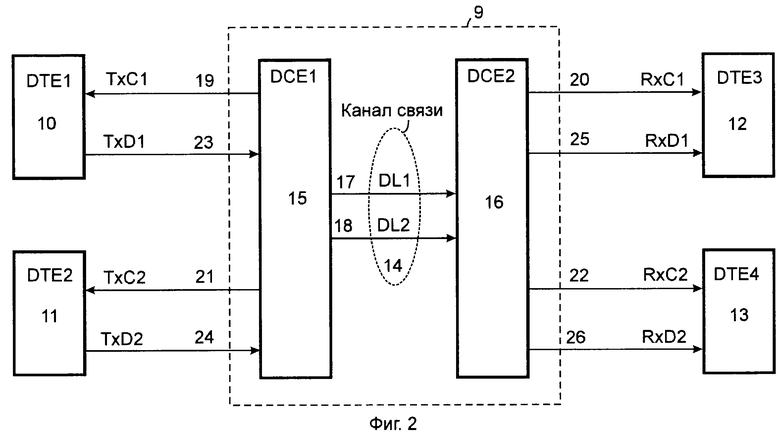

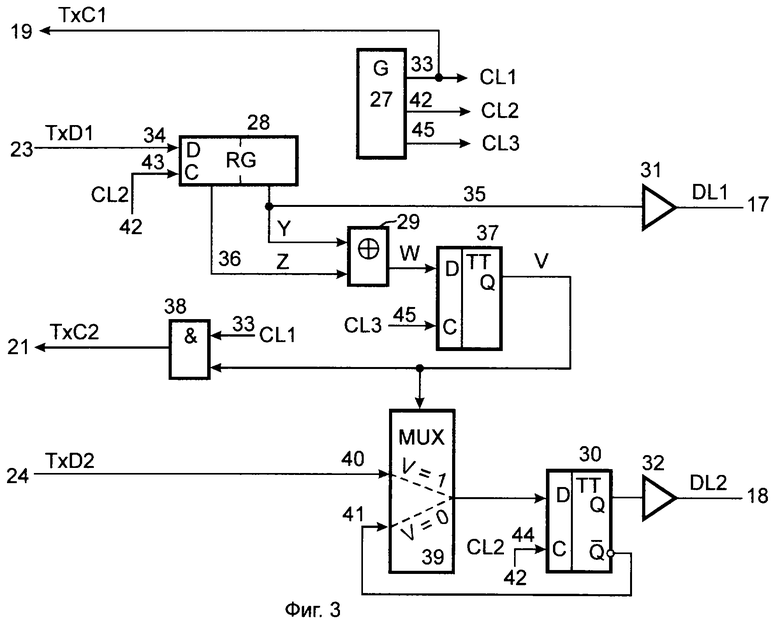

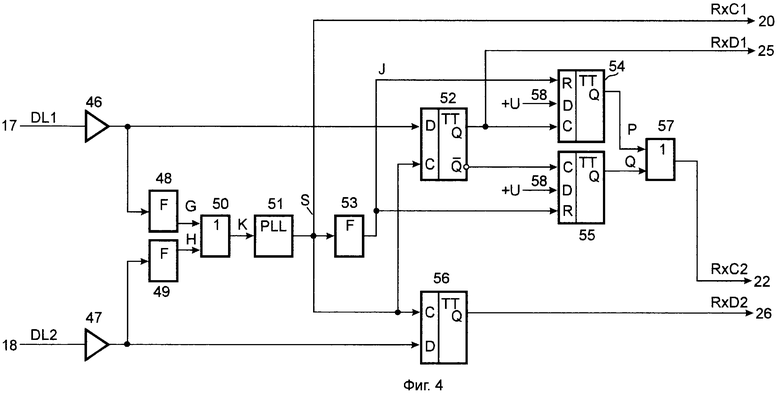

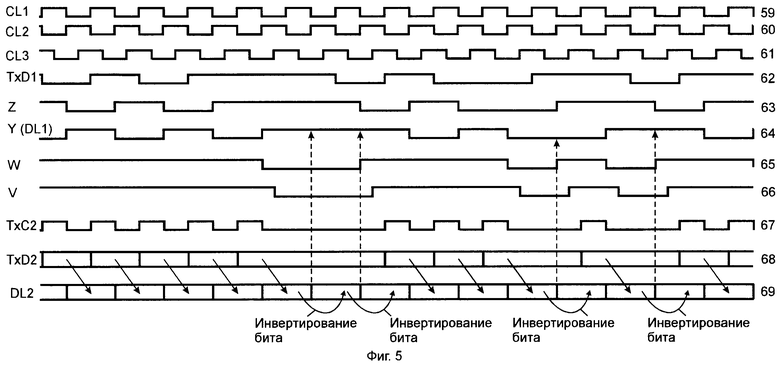

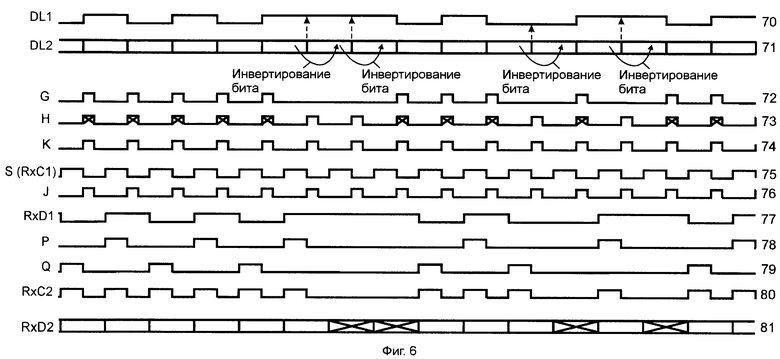

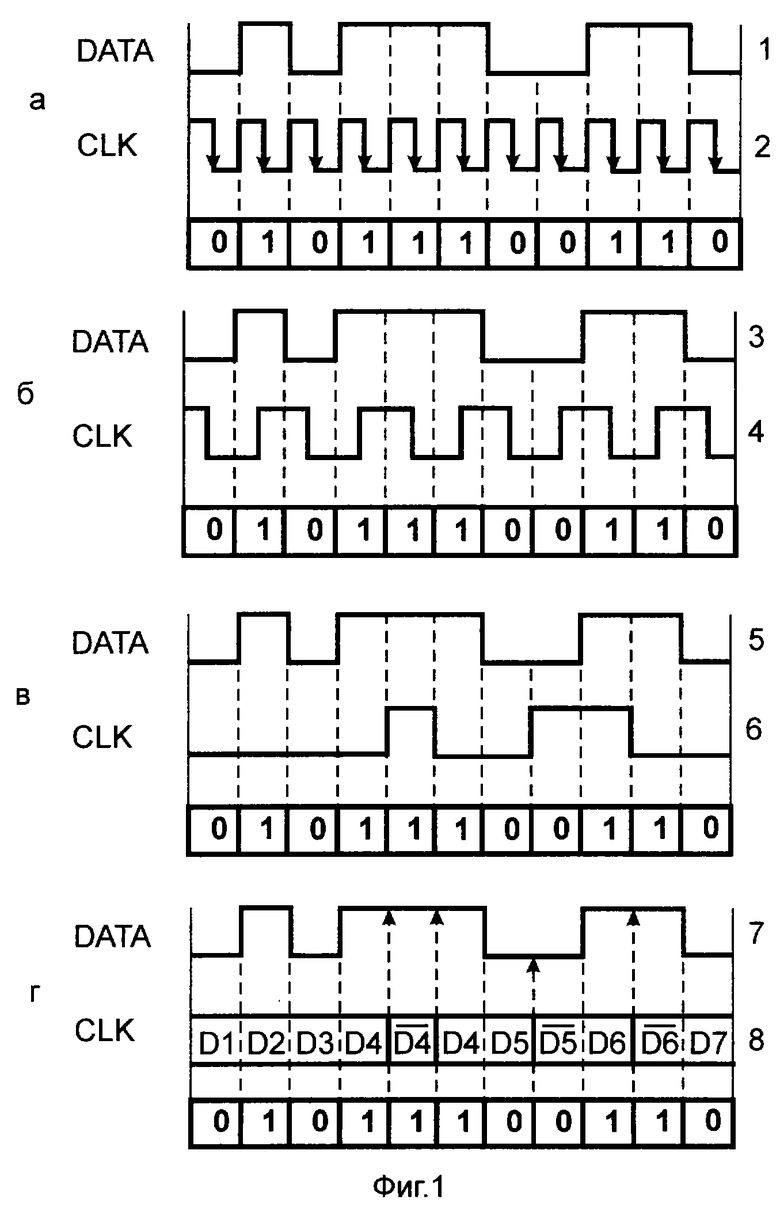

На фиг. 1 представлены временные диаграммы, поясняющие способы передачи данных, применяемые при использовании известных и предлагаемого устройств; на фиг. 2 - пример схемы включения предлагаемого устройства в телекоммуникационную систему; на фиг.3 - структурная схема блока передачи данных; на фиг.4 - структурная схема блока приема данных; на фиг.5 - временная диаграмма сигналов блока передачи данных; на фиг.6 - временная диаграмма сигналов блока приема данных.

Временные диаграммы 1 и 2 (фиг.1, а) соответствуют сигналам данных DATA и синхронизации CLK, формируемым в соответствии с общепринятым способом последовательной синхронной передачи данных, см., например, рекомендации ITU-T (МСЭ-Т) V.24, V.28. Временные диаграммы 3 и 4 (фиг.1, б) соответствуют сигналам данных DATA и синхронизации CLK, используемым в устройстве [I]. Временные диаграммы 5 и 6 (фиг.1, в) соответствуют сигналам данных DATA и синхронизации CLK, принятым в устройстве [2]. Временные диаграммы 7 и 8 (фиг. 1, г) соответствуют сигналам данных DATA и синхронизации CLK, принятым в предлагаемом устройстве. (Как будет показано, сигнал CLK, представленный на диаграмме 8, используется не только по прямому назначению).

Телекоммуникационная система (фиг.2) содержит предлагаемое устройство 9 для передачи данных и подключенные к нему первое - четвертое 10-13 оконечные устройства DTE1 - DTE4. Устройство 9 содержит подключенные к противоположным сторонам канала связи 14 блок 15 передачи данных (DCE1) и блок 16 приема данных (DCE2). Канал связи 14 содержит первую 17 и вторую 18 линии связи. Выходы 19 и 20 блоков 15 и 16 являются первым и вторым выходами синхронизации устройства 9. Выходы 21 и 22 блоков 15 и 16 являются третьим и четвертым выходами синхронизации устройства 9. Входы 23 и 24 блока 15 являются первым и вторым входами данных устройства 9. Выходы 25 и 26 блока 16 являются первым и вторым выходами данных устройства 9.

Блок передачи данных (фиг.3) содержит генератор 27 синхросигналов, сдвиговый регистр 28, элемент Исключающее ИЛИ 29, первый триггер 30, первый 31 и второй 32 усилители, первый выход 33 генератора синхросигналов является первым выходом 19 синхронизации устройства, вход 34 данных сдвигового регистра 28 является первым входом 23 данных устройства, первый выход 35 сдвигового регистра 28 соединен с первым входом элемента Исключающее ИЛИ 29 и через первый усилитель 31 - с первой линией 17 канала связи 14, второй выход 36 сдвигового регистра 28 соединен с вторым входом элемента Исключающее ИЛИ 29, единичный выход первого триггера 30 через второй усилитель 32 соединен с второй линией 18 канала связи 14.

Блок передачи данных содержит также третий триггер 37, элемент И 38 и мультиплексор 39, выход элемента Исключающее ИЛИ 29 соединен с входом данных третьего триггера 37, выход которого соединен с управляющим входом мультиплексора 39 и с первым входом элемента И 38, выход которого является третьим выходом 21 синхронизации устройства, первый вход 40 данных мультиплексора 39 является вторым входом 24 данных устройства, второй вход 41 данных мультиплексора 39 соединен с нулевым выходом первого триггера 30, вход данных которого соединен с выходом мультиплексора 39, первый выход 33 генератора 27 синхросигналов соединен с вторым входом элемента И 38, второй выход 42 генератора 27 синхросигналов соединен с входами 43 и 44 синхронизации сдвигового регистра 28 и первого триггера 30, третий выход 45 генератора 27 синхросигналов соединен с входом синхронизации третьего триггера 37.

Блок приема данных (фиг.4) содержит третий 46 и четвертый 47 усилители, первый 48 и второй 49 формирователи импульсов, первый элемент ИЛИ 50, блок 51 фазовой автоподстройки частоты и второй триггер 52, входы третьего 46 и четвертого 47 усилителей соединены с первой 17 и второй 18 линиями канала связи 14, выходы третьего 46 и четвертого 47 усилителей через первый 48 и второй 49 формирователи импульсов соединены с входами первого элемента ИЛИ 50, выход которого соединен с входом блока 51 фазовой автоподстройки частоты, выход которого является вторым выходом 20 синхронизации устройства и соединен с входом синхронизации второго триггера 52, единичный выход которого является первым выходом 25 данных устройства, вход данных второго триггера 52 соединен с выходом третьего усилителя 46.

Блок приема данных содержит также третий 53 формирователь импульсов, четвертый 54, пятый 55 и шестой 56 триггеры и второй элемент ИЛИ 57, выход которого является четвертым выходом 22 синхронизации устройства, входы второго элемента ИЛИ 57 соединены с выходами четвертого 54 и пятого 55 триггеров, входы установки нуля которых соединены с выходом третьего 53 формирователя импульсов, а входы синхронизации - с единичным и нулевым выходами второго триггера 52, входы данных четвертого 54 и пятого 55 триггеров соединены с шиной 58 положительного напряжения, имитирующего сигнал лог. 1, вход третьего 53 формирователя импульсов соединен с выходом блока 51 фазовой автоподстройки частоты и с входом синхронизации шестого триггера 56, вход данных которого соединен с выходом четвертого усилителя 47, выход шестого триггера 56 является вторым выходом данных устройства.

Временные диаграммы 59, 60 и 61 (фиг.5) соответствуют сигналам на выходах 33, 42 и 45 генератора 27 блока 15. Временные диаграммы 62, 63 и 64 отображают сигналы в точках 34, 36 и 35 блока 15. Временные диаграммы 65, 66 и 67 соответствуют сигналам на входе данных триггера 37, на выходе этого триггера и на выходе элемента И 38. Временные диаграммы 68 и 69 соответствуют сигналам на входе 24 и выходе 18 блока 15.

Временные диаграммы 70 и 71 (фиг.6) отображают сигналы на входах 17 и 18 блока 16. Временные диаграммы 72 - 76 соответствуют сигналам на выходах формирователей импульсов 48, 49, на входе и выходе блока 51 и на выходе формирователя импульсов 53. Временные диаграммы 77-81 отображают сигналы на выходе 25, на входах элемента ИЛИ 57 и на выходах 22 и 26 блока 16.

Далее рассмотрены способы передачи данных, применяемые при использовании известных (фиг.1, а - в) и предлагаемого (фиг.1, г) устройств.

Как показано на фиг. 1, а-г, из устройства-передатчика в устройство-приемник передаются два сигнала: DATA (диаграммы 1, 3, 5, 7) и CLK (диаграммы 2, 4, 6, 8). Сигнал DATA предназначен для передачи последовательного потока битов данных. В примере, приведенном на фиг.1, каждому биту из последовательности 01011100110 выделен так называемый битовый интервал. Границы между битовыми интервалами показаны на диаграммах штриховыми линиями. Сигналам лог. 1 и лог. 0 в данном примере соответствуют напряжения высокого и низкого уровня.

Сигнал синхронизации CLK в известных устройствах формируется по-разному, но во всех рассматриваемых вариантах он используется только по прямому назначению - для разграничения битовых интервалов. В предлагаемом устройстве сигнал CLK используется как по прямому назначению, так и (одновременно с этим) для передачи дополнительного потока данных.

При передаче данных согласно временным диаграммам 1 и 2, приведенным на фиг. 1, а, по положительному фронту синхросигнала CLK устройство-передатчик начинает выдачу очередного бита данных. По отрицательному фронту этого синхросигнала устройство-приемник фиксирует полученный бит. Источник синхросигналов может конструктивно размещаться в передатчике, приемнике или вне того и другого.

При передаче данных согласно временным диаграммам 3 и 4, приведенным на фиг. 1, б, истинность передаваемых битов данных DATA подтверждается поочередно положительными и отрицательными фронтами сигнала CLK. Иными словами, положительные и отрицательные фронты сигнала CLK соответствуют установившимся значениям сигнала данных используются приемником для фиксации битов (например, в одном или двух сдвиговых регистрах). Границы битовых интервалов смещены относительно фронтов сигнала CLK на четверть периода этого сигнала. По сравнению с предыдущим способом передачи данных частота сигнала CLK снижена в два раза при сохранении той же скорости передачи данных.

При передаче данных согласно временным диаграммам 5 и 6, приведенным на фиг. 1, в, сигнал синхронизации CLK изменяется только в тех случаях, когда сигнал DATA остается неизменным. Таким образом, на любой границе битового интервала изменяется либо сигнал DATA, либо сигнал CLK. Приемник отслеживает изменения этих сигналов и всегда располагает информацией о местоположении битовых границ. По сравнению с предыдущим способом передачи данных данный способ "разравнивает" энергетический спектр сигнала CLK. Теперь он не содержит выраженной спектральной линии, что способствует снижению уровня генерируемых перекрестных помех, воздействующих на соседние провода кабеля.

Способ передачи данных, примененный в предлагаемом устройстве (см. фиг. 1, г), близок только что описанному (см. фиг.1, в). Точно так же "недостающие" фронты сигнала DATA восполняются гарантированными фронтами сигнала CLK. Но в данном случае сигнал CLK не "простаивает без информационной нагрузки" и по возможности используется для передачи дополнительного потока данных.

Сравнивая временные диаграммы 6 и 8, можно отметить, что в течение первых четырех битовых интервалов сигнал CLK можно использовать как "транспортное средство" для передачи четырех дополнительных битов D1-D4. Эти биты, конечно, могут иметь произвольные значения. В частности, все они могут быть нулевыми или единичными. Такая "свобода выбора" возможна благодаря тому, что сигнал DATA в этот период изменяется в каждом битовом интервале и используется приемником для распознавания межбитовых границ.

После передачи битов D1-D4 создается гарантированный перепад уровней сигнала CLK, так как сигнал DATA остается неизменным. Это достигается инвертированием бита D4. Далее бит повторно инвертируется, так как сигнал DATA по-прежнему неизменен, затем передается бит D5, и т. д. Гарантированные изменения состояния сигнала CLK соответствуют вертикальным стрелкам на рисунке. Таким образом, в данном примере сигнал CLK дополнительно "переносит" данные D1-D7 одновремено с передачей "основных" данных сигналом DATA.

При равновероятном появлении сигналов лог. 0 и лог. 1 в потоке данных DATA (что можт быть достигнуто его предварительным скремблированием) пропускная способность дополнительного канала передачи данных составляет 50% пропускной способности основного канала. Действительно, вероятность перепада уровней сигнала DATA на границе битовых интервалов i и j равна 0,5 и не зависит от предыстории. Но именно эта вероятность определяет событие "вставки" очередного бита D в поток сигналов CLK. Таким образом, в среднем каждый второй битовый интервал пригоден для передачи дополнительного бита данных. В результате общая пропускная способность (или скорость передачи данных) предлагаемого устройства по сравнению с прототипом увеличена в 1,5 раза.

Далее рассмотрен пример схемы включения предлагаемого устройства в телекоммуникационную систему.

Предлагаемое устройство 9 для передачи данных (фиг.2) подключено к четырем оконечным устройствам DTE1 (10) - DTE4 (13), например к четырем компьютерам. В процессе работы системы данные передаются из устройства 10 в устройство 12 по основному каналу передачи данных. Одновременно с этим по дополнительному каналу данные передаются из устройства 11 в устройство 13. (Для передачи данных в обратном направлении необходимо второе устройство 9, включенное встречно).

Пара сигналов ТxС1-TxDl (TxC2-TxD2) обеспечивает синхронную передачу данных из устройства 10 (11) в блок 15. Положительные фронты сигнала ТxС1 (TxC2) задают границы битовых интервалов. По отрицательным фронтам сигнала ТxС1 (TxC2) соответствующий бит данных TxD1 (TxD2) временно запоминается в блоке 15.

Пара сигналов RxC1-RxD1 (RxC2-RxD2) обеспечивает синхронную передачу данных из блока 16 в устройство 12 (13). Положительные фронты сигнала RxC1 (RxC2) задают моменты начала битовых интервалов. По отрицательным фронтам сигнала RxC1 (RxC2) соответствующие биты данных RxD1 (RxD2) запоминаются в устройстве 12(13).

По линиям 17 и 18 канала связи 14 передаются сигналы DL1 и DL2 - аналоги сигналов DATA и CLK, показанных на диаграммах 7 и 8, фиг.1, г. Канал связи 14 может быть выполнен в виде двух витых пар проводов, двух оптоволоконных линий или иных средств передачи сигналов, в том числе содержащих ретрансляторы.

Далее рассмотрена работа блока 15 передачи данных (см. фиг.3, 5).

Все процессы, протекающие в устройстве, синхронизированы сигналами от генератора 27. Сигнал CL1 (ТхС1) с выхода 33 генератора 27 поступает на выход 19 устройства и далее передается в устройство DTE1 (10). В ответ на этот сигнал из устройства DTE1 (10) выдаются данные TxD1. Они поступают на вход 23 устройства и далее на вход 34 двухразрядного сдвигового регистра 28. Под действием положительных фронтов сигнала CL2 данные продвигаются в этом регистре, выдаются через усилитель 31 в линию 17 и одновременно с этим анализируются элементом Исключающее ИЛИ 29. До тех пор, пока биты в регистре 28 чередуются (...010101...), формируется сигнал V=1, который разрешает работу элемента И 38. На его выходе 21 формируется синхросигнал ТхС2, в ответ на который на вход 24 из устройства DTE2 (11) поступают биты данных TxD2 дополнительного канала передачи. Эти биты проходят через мультиплексор 39, триггер 30, усилитель 32 и поступают в линию 18.

Обнаружение элементом Исключающее ИЛИ 29 одинаковых битов в регистре 28 означает невозможность передачи очередного "полезного" бита по дополнительному каналу (из-за отсутствия перепада уровней сигнала в основном канале). Поэтому работа с устройством DTE2 (11) приостанавливается сигналом V=0. Этот сигнал запирает элемент И 38 по нижнему входу и переключает мультиплексор 39 в состояние, при котором триггер 30 работает в счетном режиме, т. е. в каждом такте инвертирует хранящийся в нем бит. Таким образом, как уже было показано, восполняются "отсутствующие" фронты сигнала DL 1.

Далее рассмотрена работа блока 16 приема данных (см. фиг.4, 6).

Сигналы DL1 и DL2 (диаграммы 70 и 71) поступают в блок 16 из линий 17 и 18, проходят через усилители 46, 47 и формирователи импульсов 48 и 49.

Сигнал G (диаграмма 72) на выходе формирователя импульсов 48 сопровождает любое изменение сигнала DL1. В данном примере в сигнале G отсутствуют импульсы на позициях, соответствующих вертикальным стрелкам между диаграммами 71 и 70. Сигнал Н (диаграмма 73) на выходе формирователя импульсов 49 сопровождает любое изменение сигнала DL2. Так как в данном примере сигнал DL2 показан условно, без указания конкретного кода, то заранее не известно, будут ли сформированы импульсы, помеченные на диаграмме 73 крестиками. Но зато можно утверждать, что остальные импульсы на этой диаграмме будут обязательно сформированы, так как они соответствуют гарантированным изменениям сигнала DL2 при его инвертировании. Таким образом, с помощью элемента ИЛИ 50 "недостающие" импульсы восполняются, и сигнал К представляет собой периодическую последовательность импульсов без "пробелов". Этот сигнал поступает на вход синхронизации блока 51 фазовой автоподстройки частоты.

Блок 51 может быть выполнен по одной из известных схем (см., например, пат. США 6215835 В1). Он предназначен для формирования высокостабильного синхросигнала S (RxC1) на основе непрерывного слежения за входным сигналом К. В данном примере отрицательный фронт сигнала S "привязан" к положительному фронту сигнала К. Благодаря достаточной "инерционности" блока 51 сигнал S практически нечувствителен к "дрожанию фазы" сигнала К и иным его кратковременным искажениям, вызванным помехами в канале связи. (Такое использование стандартного блока фазовой автоподстройки частоты в телекоммуникационных системах является общепринятым и далее не детализируется.)

По положительному фронту сигнала S принимаемые из линий 17 и 18 данные записываются в триггеры 52 и 56. Сигналы с выходов этих триггеров поступают на выходы 25 и 26 блока 16 и далее в устройства DTE3 (12) и DTE4 (13). Как отмечалось, сигнал RxD2 содержит не только "полезные", но и "служебные" биты, полученные инвертированием предыдущих.

Служебные биты сигнала RxD2 (помеченные крестиками на диаграмме 81), в отличие от полезных не сопровождаются отрицательными фронтами сигнала RxC2 и поэтому не воспринимаются устройством DTE4 (13). Для такого "прореживания" импульсов используются триггеры 54, 55 и элемент ИЛИ 57. Триггер 54 устанавливается в единичное состояние по положительному фронту сигнала RxD1, а триггер 55 - по отрицательному фронту этого сигнала. Возврат этих триггеров в нулевое состояние происходит под действием импульсов J, которые поступают с формирователя импульсов 53 и соответствуют отрицательным фронтам сигнала S. Сигналы Р и Q с выходов триггеров 54 и 55 суммируются элементом ИЛИ 57. Поэтому в периоды стабильности сигнала RxD1 синхросигнал RxC2 не вырабатывается, что и требуется для фильтрации служебных битов.

Источники информации

1. Патент США 6269414 BL.

2. Патент США 6044421 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214045C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2003 |

|

RU2242789C1 |

Изобретение относится к устройствам для передачи данных и может быть использовано в синхронных телекоммуникационных системах. Техническим результатом является повышение скорости передачи данных. Устройство содержит блок приема данных и блок передачи данных, при этом блок передачи данных содержит генератор синхросигналов, сдвиговый регистр, элемент Исключающее ИЛИ, триггер, два усилителя, блок приема данных содержит два усилителя, два формирователя импульсов, элемент ИЛИ, блок фазовой автоподстройки частоты, триггер. 6 ил.

Устройство для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, сдвиговый регистр, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый триггер, первый и второй усилители, первый выход генератора синхросигналов является первым выходом синхронизации устройства, второй выход генератора синхросигналов соединен с входами синхронизации сдвигового регистра и первого триггера, вход данных сдвигового регистра является первым входом данных устройства, первый выход сдвигового регистра соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и через первый усилитель - с первой линией канала связи, второй выход сдвигового регистра соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, единичный выход первого триггера через второй усилитель соединен с второй линией канала связи, блок приема данных содержит третий и четвертый усилители, первый и второй формирователи импульсов, первый элемент ИЛИ, блок фазовой автоподстройки частоты и второй триггер, входы третьего и четвертого усилителей соединены с первой и второй линиями канала связи, выходы третьего и четвертого усилителей через первый и второй формирователи импульсов соединены с входами первого элемента ИЛИ, выход которого соединен с входом блока фазовой автоподстройки частоты, выход которого является вторым выходом синхронизации устройства и соединен с входом синхронизации второго триггера, единичный выход которого является первым выходом данных устройства, вход данных второго триггера соединен с выходом третьего усилителя, отличающееся тем, что блок передачи данных дополнительно содержит третий триггер, элемент И и мультиплексор, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом данных третьего триггера, выход которого соединен с управляющим входом мультиплексора и с первым входом элемента И, выход которого является третьим выходом синхронизации устройства, первый вход данных мультиплексора является вторым входом данных устройства, второй вход данных мультиплексора соединен с нулевым выходом первого триггера, вход данных которого соединен с выходом мультиплексора, первый выход генератора синхросигналов соединен с вторым входом элемента И, третий выход генератора синхросигналов соединен с входом синхронизации третьего триггера, блок приема данных дополнительно содержит третий формирователь импульсов, четвертый, пятый и шестой триггеры и второй элемент ИЛИ, выход которого является четвертым выходом синхронизации устройства, входы второго элемента ИЛИ соединены с выходами четвертого и пятого триггеров, входы установки нуля которых соединены с выходом третьего формирователя импульсов, а входы синхронизации - с единичным и нулевым выходами второго триггера, входы данных четвертого и пятого триггеров соединены с шиной положительного напряжения, вход третьего формирователя импульсов соединен с выходом блока фазовой автоподстройки частоты и с входом синхронизации шестого триггера, вход данных которого соединен с выходом четвертого усилителя, выход шестого триггера является вторым выходом данных устройства.

| US 6044421 А, 28.03.2000 | |||

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ | 1991 |

|

RU2013867C1 |

| US 6269414 А, 31.07.2001 | |||

| МНОГОПРОГРАММНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ТЕЛЕВИЗИОННОЙ ИНФОРМАЦИИ | 1990 |

|

RU2024213C1 |

Авторы

Даты

2003-05-27—Публикация

2001-11-21—Подача