Предлагаемое изобретение относится к устройствам для обработки цифровых данных с помощью электрических устройств, в частности к устройствам для передачи данных.

Известно устройство [1] для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит первый и второй усилители, выходы которых соединены с первой и второй линиями канала связи, блок приема данных содержит третий и четвертый усилители, входы которых соединены с первой и второй линиями канала связи.

Устройство [1] предназначено для синхронной передачи данных по каналу связи. По первой линии канала связи передается сигнал данных, по второй - сигнал синхронизации. Сигналы в первой и второй линиях канала связи представлены двумя уровнями напряжения. Первый уровень соответствует сигналу лог.0, второй - сигналу лог. 1. Блок передачи данных формирует последовательный поток битов, при этом синхросигнал формируется таким образом, чтобы его отрицательные фронты определяли границы битовых интервалов, а положительные фронты соответствовали центрам этих интервалов. Блок приема данных фиксирует поступающие из канала связи биты в моменты формирования положительных фронтов синхросигнала.

Недостатками устройства [1] являются низкая скорость передачи данных и высокий уровень помех, излучаемых на соседние провода многожильного кабеля, в котором физически реализован канал связи. Первый недостаток связан с тем, что передача каждого бита данных сопровождается двумя изменениями состояния синхросигнала. Поэтому при ограниченной параметрами линии частоте F (Гц) синхросигнала скорость передачи данных недостаточно высока и составляет F (бит/с). Второй недостаток обусловлен тем, что в спектре синхросигнала доминирует ярко выраженный энергетический максимум на частоте F. Это приводит к тому, что из-за паразитных связей с линией передачи синхросигнала в соседних проводах многожильного кабеля формируется достаточно выраженный периодический сигнал помехи частотой F.

Известно устройство [2] для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит первый компьютер, первый и второй усилители, выходы которых соединены с первой и второй линиями канала связи, входы первого и второго усилителей соединены с выходным портом первого компьютера, блок приема данных содержит второй компьютер, третий и четвертый усилители, входы которых соединены с первой и второй линиями канала связи, выходы третьего и четвертого усилителей соединены с входным портом второго компьютера.

Устройство [2] предназначено для синхронной передачи данных по каналу связи. По первой линии канала связи передается сигнал данных, по второй - сигнал синхронизации. Сигналы в первой и второй линиях канала связи представлены двумя уровнями напряжения. Первый уровень соответствует сигналу лог.0, второй - сигналу лог. 1. Блок передачи данных формирует последовательный поток битов, при этом синхросигнал формируется таким образом, чтобы его фронты определяли границы битовых интервалов при передаче одноименных битов. Блок приема данных восстанавливает исходный синхросигнал по совокупности фронтов сигналов в линиях канала связи.

Устройство [2] обеспечивает вдвое большую скорость передачи данных по сравнению с устройством [1], так как передача каждого бита данных сопровождается не более чем одним изменением состояния синхросигнала. В спектрах передаваемых по линиям сигналов нет ярко выраженных доминантных составляющих, поэтому снижен уровень излучаемых помех. Однако потенциальные возможности повышения скорости передачи данных устройством [2] остаются не исчерпанными, так как линия передачи синхросигнала используется только по прямому назначению, и данные по ней не передаются.

Известно устройство [3] для передачи данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, первый и второй усилители, выходы которых соединены с первой и второй линиями канала связи, блок приема данных содержит третий и четвертый усилители, входы которых соединены с первой и второй линиями канала связи, и блок формирования синхросигнала, содержащий первый и второй формирователи импульсов, элемент ИЛИ и блок фазовой автоподстройки частоты, выход которого является выходом блока формирования синхросигнала, входы первого и второго формирователей импульсов являются первым и вторым входами блока формирования синхросигнала, выходы первого и второго формирователей импульсов соединены с входами элемента ИЛИ, выход которого соединен с входом блока фазовой автоподстройки частоты.

Устройство [3] обеспечивает более высокую скорость передачи данных по сравнению с устройством [2] благодаря использованию второй линии канала связи не только по прямому назначению (т.е. для передачи синхросигнала), но и для передачи дополнительного потока данных. Первая линия канала связи может рассматриваться как основная, с гарантированной скоростью передачи данных. Скорость передачи данных по второй линии может изменяться в зависимости от вида битовой последовательности, передаваемой по первой линии. При использовании скремблирования данных, передаваемых по первой линии, скорость дополнительного потока данных составляет 50% скорости основного потока.

Устройство [3] имеет два недостатка. Первый недостаток - невысокая дальность связи между блоками передачи и приема данных. Он связан с тем, что с увеличением расстояния между этими блоками из-за различий физических характеристик двух линий связи, образующих канал, разность задержек распространения сигналов по этим линиям может достигать значительных величин и, в частности, превосходить длительность битового интервала. В этом случае устройство [3] теряет работоспособность.

Второй недостаток заключается в том, что при работе с битовыми потоками, представленными в виде последовательностей информационных кадров, скорость передачи данных снижается. Это обусловлено следующими причинами. Для разграничения кадров в потоки данных вводятся флаги, предваряющие начало каждого кадра. Флаг представляет собой некоторую “уникальную” последовательность битов, которая не встречается в “теле” кадра. Чтобы гарантировать такую уникальность, применяют битстаффинг - добавление служебных битов в поток “полезных” данных. Таким образом, добавление флагов и применение битстаффинга приводит к снижению скорости передачи потоков “полезных” данных по первой и второй линиям канала связи.

Цель изобретения - увеличение дальности связи и повышение скорости передачи данных по первой линии канала связи.

Цель достигается тем, что в устройстве для передачи данных, содержащем подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, первый и второй усилители, выходы которых соединены с первой и второй линиями канала связи, блок приема данных содержит третий и четвертый усилители, входы которых соединены с первой и второй линиями канала связи, и блок формирования синхросигнала, содержащий первый и второй формирователи импульсов, элемент ИЛИ и блок фазовой автоподстройки частоты, выход которого является выходом блока формирования синхросигнала, входы первого и второго формирователей импульсов являются первым и вторым входами блока формирования синхросигнала, выходы первого и второго формирователей импульсов соединены с входами элемента ИЛИ, выход которого соединен с входом блока фазовой автоподстройки частоты, блок передачи данных дополнительно содержит первый компьютер и двухканальный преобразователь параллельного кода в последовательный, выходы данных первого и второго каналов которого соединены с входами первого и второго усилителей, а выход готовности - с входным портом первого компьютера, выходной порт которого соединен с группой входов данных двухканального преобразователя параллельного кода в последовательный, выход генератора синхросигналов соединен с входом синхронизации двухканального преобразователя параллельного кода в последовательный, блок приема данных дополнительно содержит второй компьютер, двухканальный преобразователь последовательного кода в параллельный, первый и второй регулируемые элементы задержки, входы данных которых соединены с выходами третьего и четвертого усилителей, а группы управляющих входов - с первым и вторым выходными портами второго компьютера, выходы первого и второго регулируемых элементов задержки соединены с первым и вторым входами блока формирования синхросигнала, а также с входами данных первого и второго каналов двухканального преобразователя последовательного кода в параллельный, вход синхронизации которого соединен с выходом блока формирования синхросигналов, а группа выходов данных - с первым входным портом второго компьютера, второй входной порт которого соединен с выходом готовности двухканального преобразователя последовательного кода в параллельный.

Двухканальный преобразователь параллельного кода в последовательный содержит первый и второй сдвиговые регистры, первый двоичный счетчик и элемент И-НЕ, выход которого соединен с управляющими входами первого и второго сдвиговых регистров и является выходом готовности двухканального преобразователя параллельного кода в последовательный, группа входов данных которого соединена с входами данных первого и второго сдвиговых регистров, а вход синхронизации - с входами синхронизации первого и второго сдвиговых регистров и с входом синхронизации первого двоичного счетчика, выходы которого соединены с входами элемента И-НЕ, выходы данных первого и второго каналов преобразователя параллельного кода в последовательный соединены с выходами первого и второго сдвиговых регистров.

Двухканальный преобразователь последовательного кода в параллельный содержит первый и второй параллельные регистры, третий и четвертый сдвиговые регистры, второй двоичный счетчик, первый и второй элементы И и инвертор, вход которого соединен с входами синхронизации третьего и четвертого сдвиговых регистров и является входом синхронизации двухканального преобразователя последовательного кода в параллельный, входы данных первого и второго каналов которого соединены с входами данных третьего и четвертого сдвиговых регистров, группа выходов данных двухканального преобразователя последовательного кода в параллельный соединена с выходами первого и второго параллельных регистров, входы которых соединены с выходами третьего и четвертого сдвиговых регистров, выход инвертора соединен с входом синхронизации второго двоичного счетчика и с первым входом второго элемента И, выход которого соединен с входами синхронизации первого и второго параллельных регистров, второй вход второго элемента И соединен с выходом первого элемента И и является выходом готовности двухканального преобразователя последовательного кода в параллельный, выходы второго двоичного счетчика соединены с входами первого элемента И.

Регулируемый элемент задержки содержит мультиплексор и группу последовательно включенных элементов задержки, вход первого, выход последнего и точки объединения соседних элементов задержки соединены с входами данных мультиплексора, управляющие входы которого являются группой управляющих входов регулируемого элемента задержки, выход мультиплексора является выходом регулируемого элемента задержки, вход первого элемента задержки является входом данных регулируемого элемента задержки.

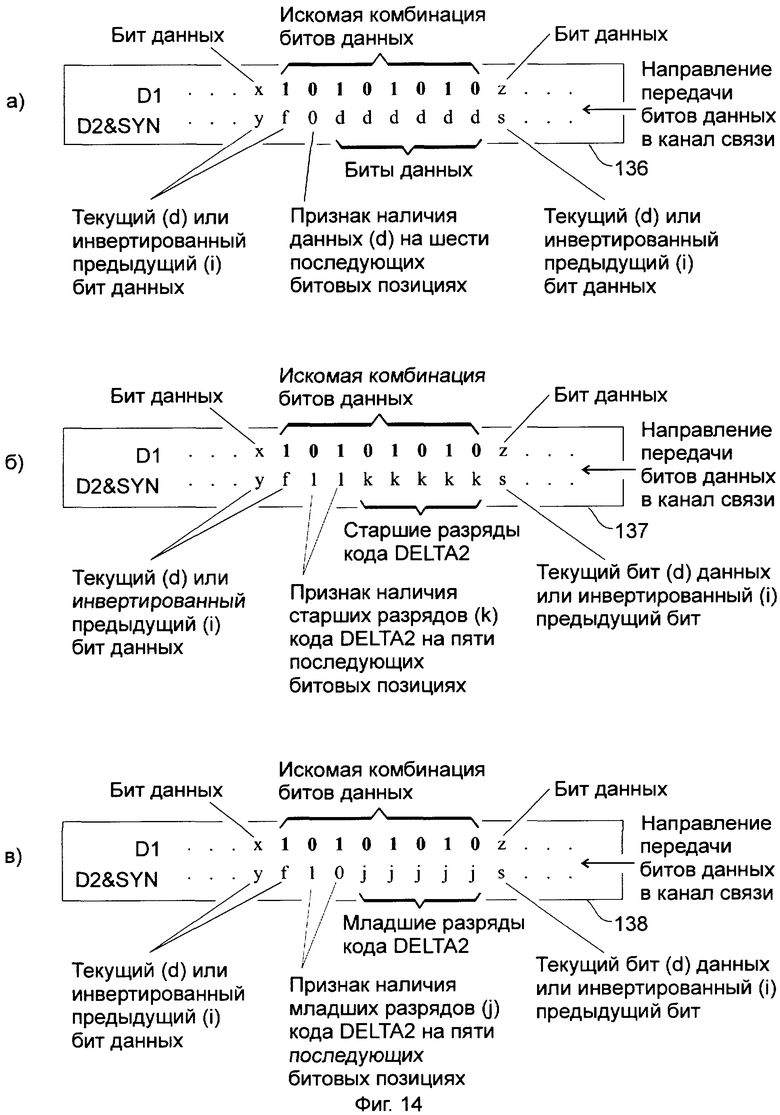

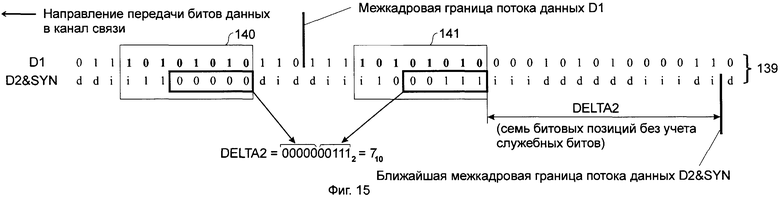

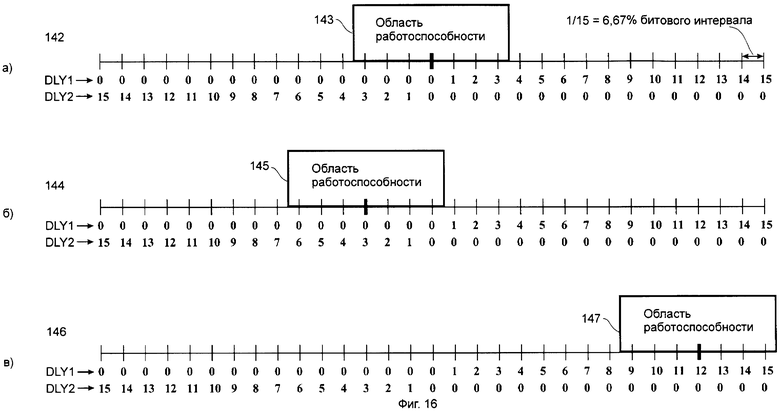

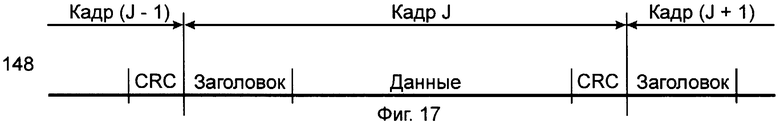

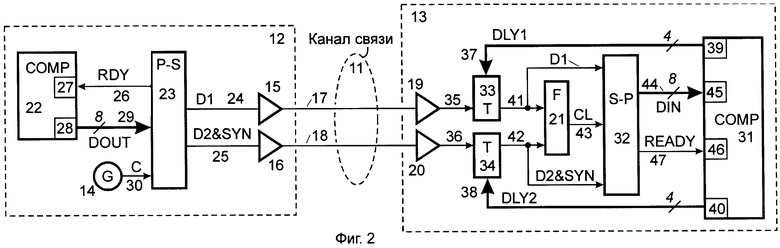

На фиг.1 представлены временные диаграммы, поясняющие способы передачи данных, применяемые при использовании известных и предлагаемого устройств, на фиг.2 - функциональная схема предлагаемого устройства для передачи данных, на фиг.3 и фиг.4 - функциональная схема двухканального преобразователя параллельного кода в последовательный и временные диаграммы его работы, на фиг.5 - функциональная схема блока формирования синхросигнала и временные диаграммы его работы, на фиг.6 - функциональная схема двухканального преобразователя последовательного кода в параллельный и временные диаграммы его работы, на фиг.7 и фиг.8 - функциональная схема регулируемого элемента задержки и временные диаграммы его работы, на фиг.9 - схема, поясняющая процесс подготовки исходных данных к выдаче в канал связи, на фиг.10 - диаграммы, поясняющие способ определения границ кадров, переданных по первой линии канала связи и размещенных в памяти второго компьютера, на фиг.11 - варианты построения кодов для передачи данных или указания положения границ кадров, передаваемых по первой линии канала связи, на фиг.12 - примеры кодовых ситуаций при передаче данных и указании положения границы между кадрами, передаваемыми по первой линии канала связи, на фиг.13 - диаграммы, поясняющие способ определения границ кадров, переданных по второй линии канала связи и размещенных в памяти второго компьютера, на фиг.14 - варианты построения кодов для передачи данных или указания положения границ кадров, передаваемых по второй линии канала связи, на фиг.15 - пример кодовой ситуации при указании положения границы между кадрами, передаваемыми по второй линии канала связи, на фиг.16 - диаграммы, поясняющие адаптацию устройства к разности задержек распространения сигнала по первой и второй линиям канала связи, на фиг.17 - структура информационного кадра.

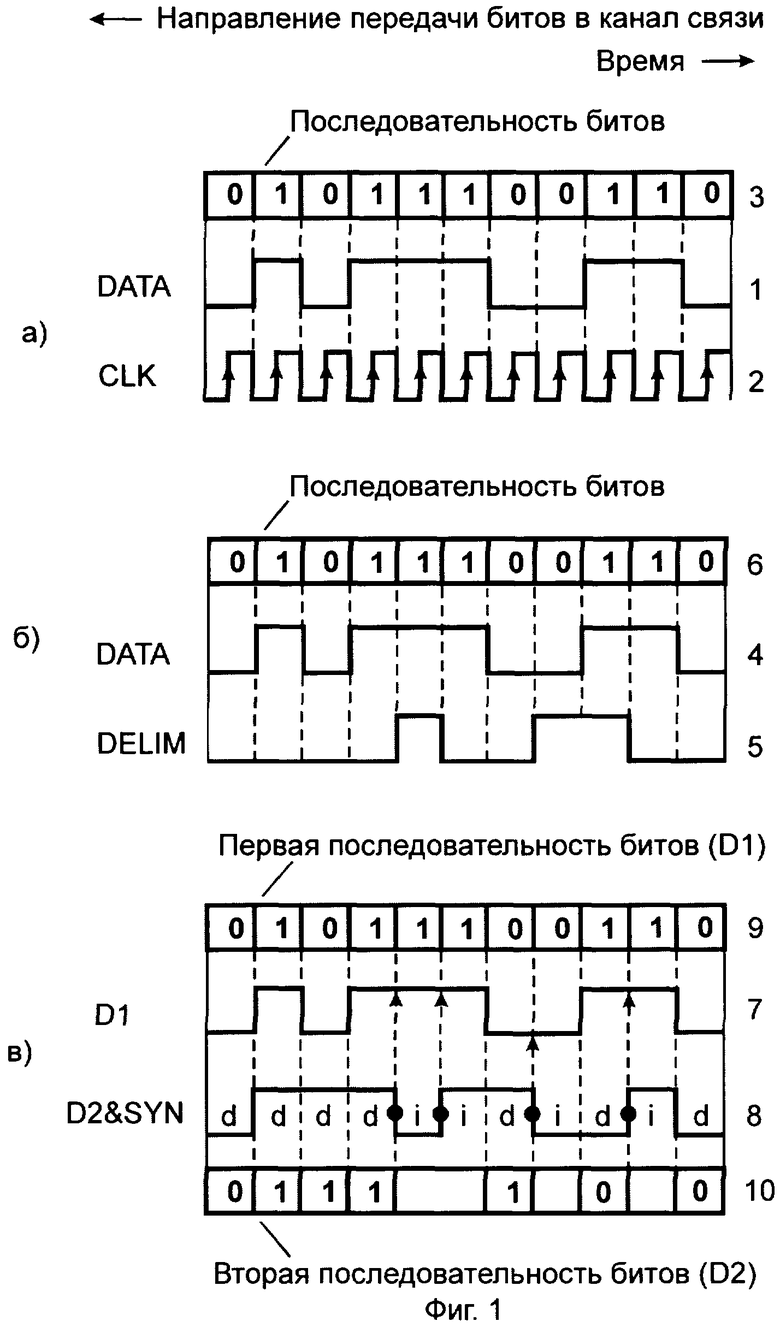

Временные диаграммы 1 и 2 (фиг.1, а) соответствуют сигналам данных DATA и синхронизации CLK, формируемым в соответствии с общепринятым способом последовательной синхронной передачи данных 3 [1]. Временные диаграммы 4 и 5 (фиг.1, б) соответствуют сигналам данных DATA и разграничения DELIM битовых интервалов при передаче последовательности 6 битов устройством [2].

Временные диаграммы 7 и 8 (фиг.1, в) соответствуют сигналам данных D1 и комплексному сигналу D2&SYN, объединяющему данные D2 и синхросигнал SYN [3]. Первая 9 и вторая 10 последовательности битов соответствуют данным D1 и D2. Этот способ передачи данных с некоторыми добавлениями применен и в предлагаемом устройстве.

Предлагаемое устройство для передачи данных (фиг.2) содержит подключенные к противоположным сторонам канала связи 11 блок 12 передачи данных и блок 13 приема данных, блок 12 передачи данных содержит генератор 14 синхросигналов, первый 15 и второй 16 усилители, выходы которых соединены с первой 17 и второй 18 линиями канала связи 11, блок 13 приема данных содержит третий 19 и четвертый 20 усилители, входы которых соединены с первой 17 и второй 18 линиями канала связи 11, и блок 21 формирования синхросигнала.

Блок 12 передачи данных дополнительно содержит первый компьютер 22 и двухканальный преобразователь 23 параллельного кода в последовательный, выходы 24 и 25 данных первого и второго каналов которого соединены с входами первого 15 и второго 16 усилителей, а выход 26 готовности - с входным портом 27 первого компьютера 22, выходной порт 28 которого соединен с группой входов 29 данных двухканального преобразователя 23 параллельного кода в последовательный, выход генератора 14 синхросигналов соединен с входом 30 синхронизации двухканального преобразователя 23 параллельного кода в последовательный.

Блок 13 приема данных дополнительно содержит второй компьютер 31, двухканальный преобразователь 32 последовательного кода в параллельный, первый 33 и второй 34 регулируемые элементы задержки, входы 35 и 36 данных которых соединены с выходами третьего 19 и четвертого 20 усилителей, а группы 37 и 38 управляющих входов - с первым 39 и вторым 40 выходными портами второго компьютера 31, выходы 41 и 42 первого 33 и второго 34 регулируемых элементов задержки соединены с первым и вторым входами блока 21 формирования синхросигнала, а также с входами данных первого и второго каналов двухканального преобразователя 32 последовательного кода в параллельный, вход 43 синхронизации которого соединен с выходом блока 21 формирования синхросигналов, а группа 44 выходов данных - с первым входным портом 45 второго компьютера 31, второй входной порт 46 которого соединен с выходом 47 готовности двухканального преобразователя 32 последовательного кода в параллельный.

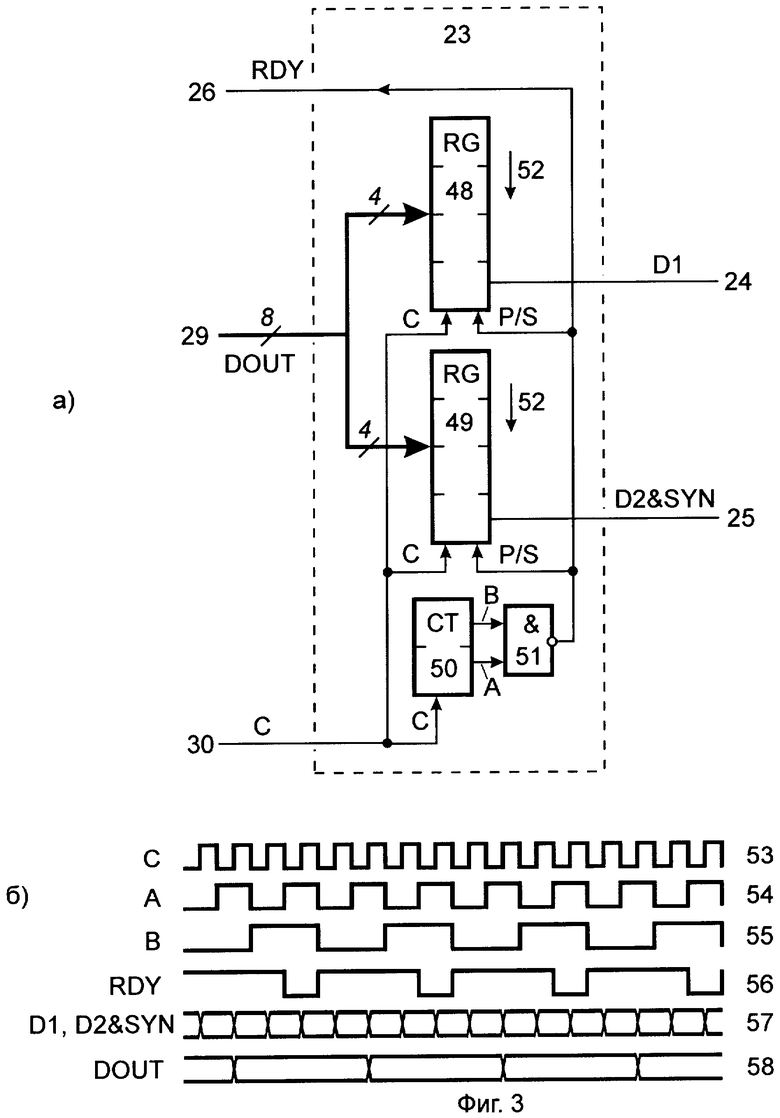

Двухканальный преобразователь 23 параллельного кода в последовательный (фиг.3) содержит первый 48 и второй 49 сдвиговые регистры, первый двоичный счетчик 50 и элемент И-НЕ 51, выход которого соединен с управляющими входами первого 48 и второго 49 сдвиговых регистров и является выходом 26 готовности двухканального преобразователя 23 параллельного кода в последовательный, группа входов 29 данных которого соединена с входами данных первого 48 и второго 49 сдвиговых регистров, а вход 30 синхронизации - с входами синхронизации первого 48 и второго 49 сдвиговых регистров и с входом синхронизации первого двоичного счетчика 50, выходы которого соединены с входами элемента И-НЕ 51, выходы 24 и 25 данных первого и второго каналов преобразователя 23 параллельного кода в последовательный соединены с выходами первого 48 и второго 49 сдвиговых регистров. Направление сдвига данных в регистрах 48 и 49 показано стрелками 52.

Временные диаграммы 53-55 соответствуют сигналам на входе синхронизации и выходах двоичного счетчика 50. Временная диаграмма 56 отображает сигнал на выходе элемента И-НЕ 51. Временная диаграмма 57 соответствует сигналам на выходах 24 и 25 блока 23. Временная диаграмма 58 отображает сигналы на входах 29 блока 23. Временные диаграммы 59-61 (фиг.4) соответствуют сигналам на входе 30 и выходах 24 и 25 блока 23.

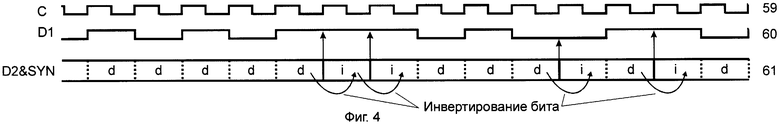

Блок 21 формирования синхросигнала (фиг.5) содержит первый 62 и второй 63 формирователи импульсов, элемент ИЛИ 64 и блок 65 фазовой автоподстройки частоты, выход которого является выходом 43 блока 21 формирования синхросигнала, входы первого 62 и второго 63 формирователей импульсов являются первым 41 и вторым 42 входами блока 21 формирования синхросигнала, выходы первого 62 и второго 63 формирователей импульсов соединены с входами элемента ИЛИ 64, выход которого соединен с входом блока 65 фазовой автоподстройки частоты.

Временные диаграммы 66 и 67 соответствуют сигналам на входах 41 и 42 блока 21. Временные диаграммы 68-70 отображают сигналы на входах и выходе элемента ИЛИ 64. Временная диаграмма 71 соответствует сигналу на выходе 43 блока 21.

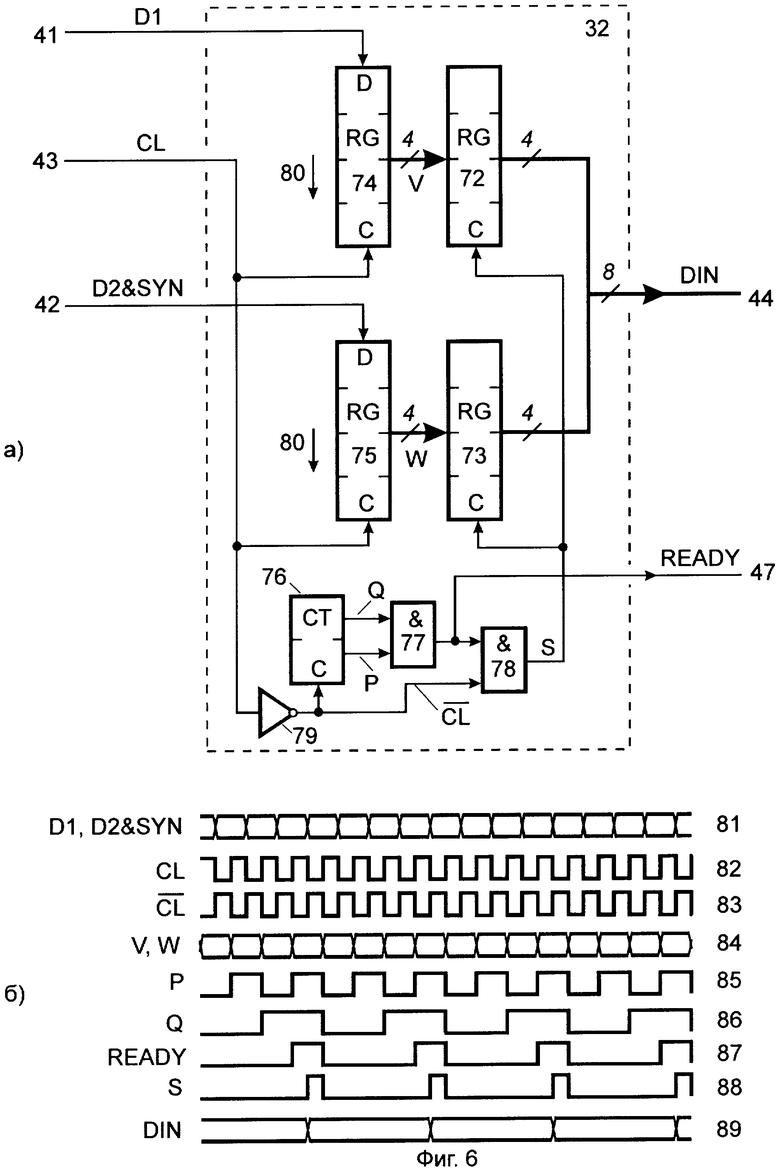

Двухканальный преобразователь 32 последовательного кода в параллельный (фиг.6) содержит первый 72 и второй 73 параллельные регистры, третий 74 и четвертый 75 сдвиговые регистры, второй двоичный счетчик 76, первый 77 и второй 78 элементы И и инвертор 79, вход которого соединен с входами синхронизации третьего 74 и четвертого 75 сдвиговых регистров и является входом 43 синхронизации двухканального преобразователя 32 последовательного кода в параллельный, входы 41 и 42 данных первого и второго каналов которого соединены с входами данных третьего 74 и четвертого 75 сдвиговых регистров, группа выходов 44 данных двухканального преобразователя 32 последовательного кода в параллельный соединена с выходами первого 72 и второго 73 параллельных регистров, входы которых соединены с выходами третьего 74 и четвертого 75 сдвиговых регистров, выход инвертора 79 соединен с входом синхронизации второго двоичного счетчика 76 и с первым входом второго элемента И 78, выход которого соединен с входами синхронизации первого 72 и второго 73 параллельных регистров, второй вход второго элемента И 78 соединен с выходом первого элемента И 77 и является выходом 47 готовности двухканального преобразователя 32 последовательного кода в параллельный, выходы второго двоичного счетчика 76 соединены с входами первого элемента И 77. Направление сдвига данных в регистрах 74 и 75 показано стрелками 80.

Временная диаграмма 81 соответствует сигналам на входах 41 и 42 блока 32, временные диаграммы 82 и 83 отображают сигналы на входе и выходе инвертора 79, временная диаграмма 84 соответствует сигналам на выходах сдвиговых регистров 74 и 75, временные диаграммы 85 и 86 отображают сигналы на выходах двоичного счетчика 76, временные диаграммы 87 и 88 соответствуют сигналам на выходах элементов И 77 и 78, временная диаграмма 89 отображает сигналы на выходах 44 блока 32.

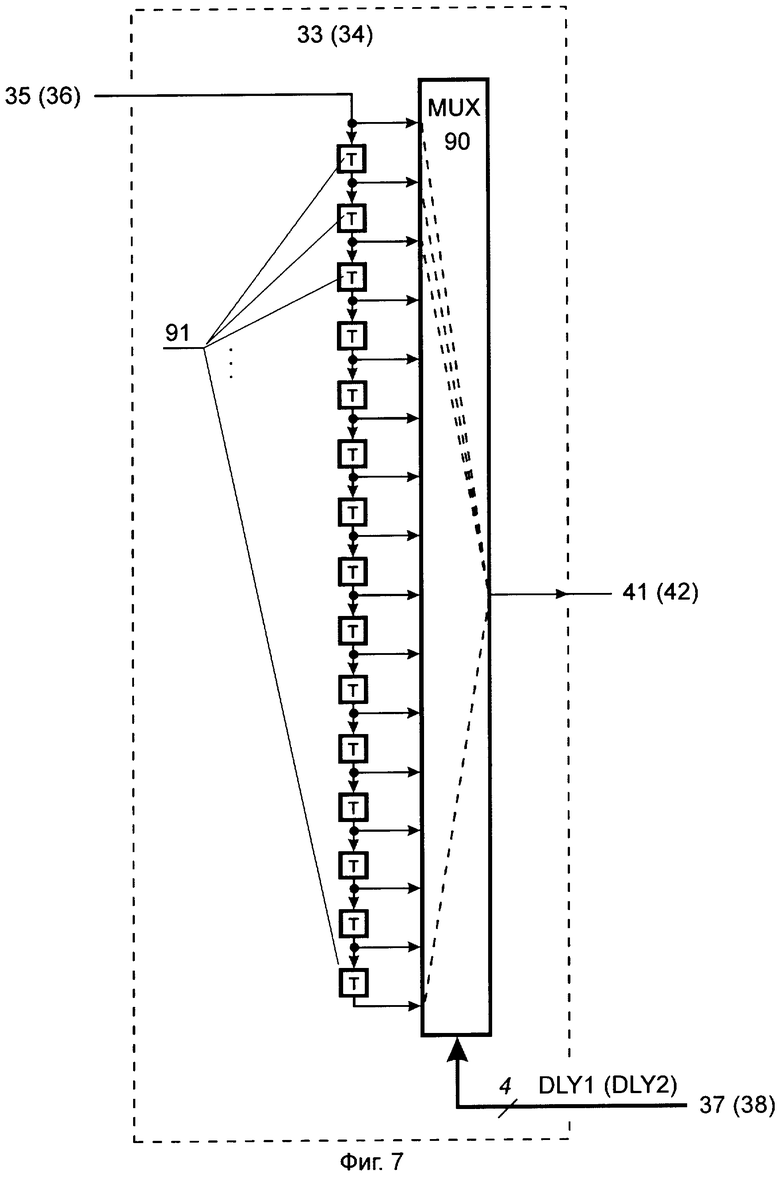

Регулируемый элемент задержки 33 (34) (фиг.7) содержит мультиплексор 90 и группу последовательно включенных элементов задержки 91, вход первого, выход последнего и точки объединения соседних элементов задержки соединены с входами данных мультиплексора 90, управляющие входы которого являются группой 37 (38) управляющих входов регулируемого элемента задержки 33 (34), выход мультиплексора 90 является выходом 41 (42) регулируемого элемента задержки 33 (34), вход первого элемента задержки 91 является входом 35 (36) данных регулируемого элемента задержки 33 (34).

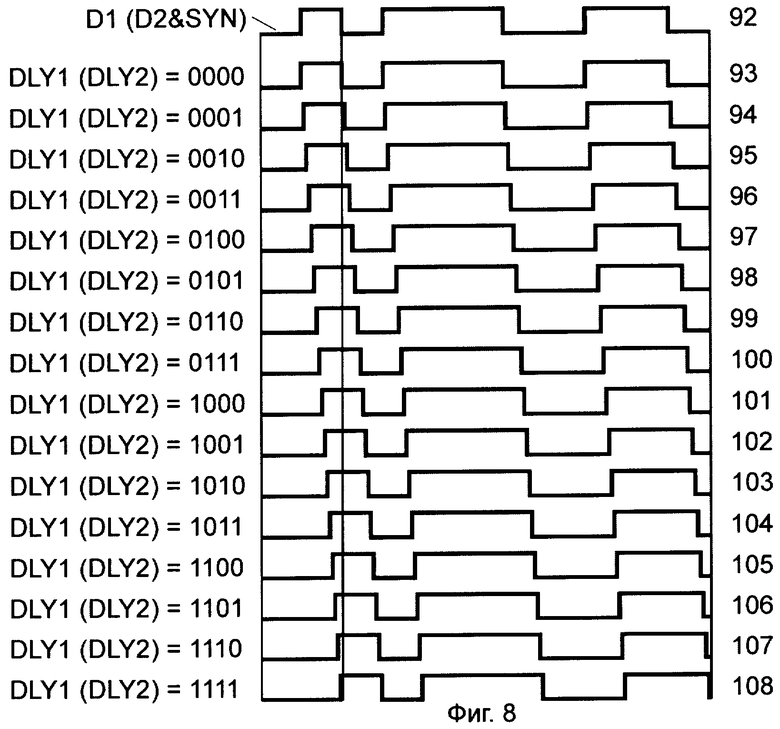

Временная диаграмма 92 (фиг.8) соответствует сигналу на входе 35 (36) данных регулируемого элемента задержки 33 (34). Временные диаграммы 93-108 отображают сигнал на выходе 41 (42) данных регулируемого элемента задержки 33 (34) при различных кодах DLY1 (DLY2).

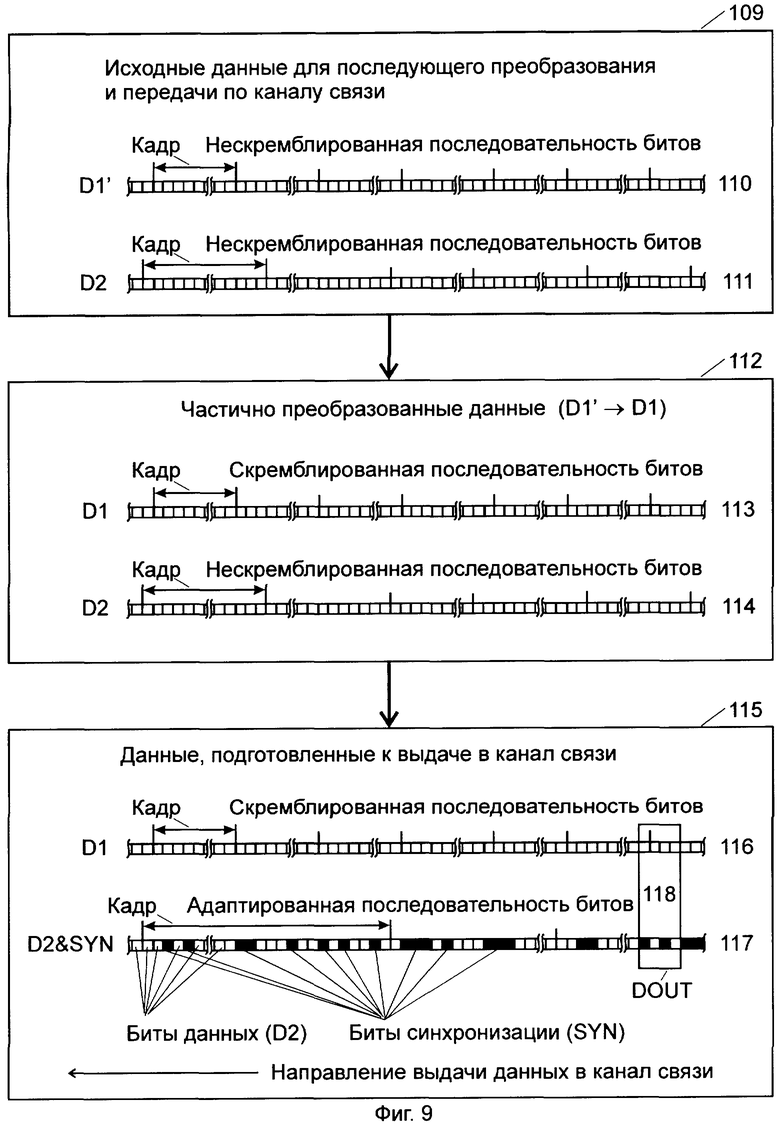

Исходные данные 109 (фиг.9) для последующего преобразования и передачи по каналу связи размещены в памяти первого компьютера 22 в виде последовательностей битов, представленных диаграммами 110 и 111. Частично преобразованные данные 112 размещены в памяти первого компьютера 22 в виде последовательностей битов, представленных диаграммами 113 и 114. Данные 115, подготовленные к выдаче в канал связи, размещены в памяти первого компьютера 22 в виде последовательностей битов, представленных диаграммами 116 и 117. Байт 118 данных, выдаваемый первым компьютером 22 в выходной порт 28, содержит четыре бита из последовательности 116 и четыре бита из последовательности 117.

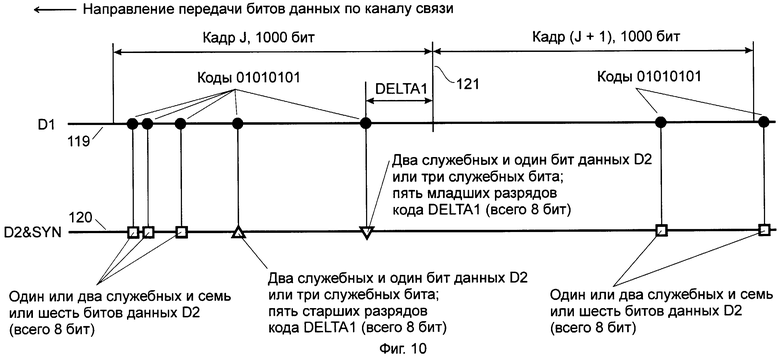

Диаграммы 119 и 120 (фиг.10) отображают последовательности битов, размещенные в памяти второго компьютера 31 после их приема из канала связи; линия 121 указывает границу между соседними кадрами данных, переданных по первой 17 линии канала связи 11.

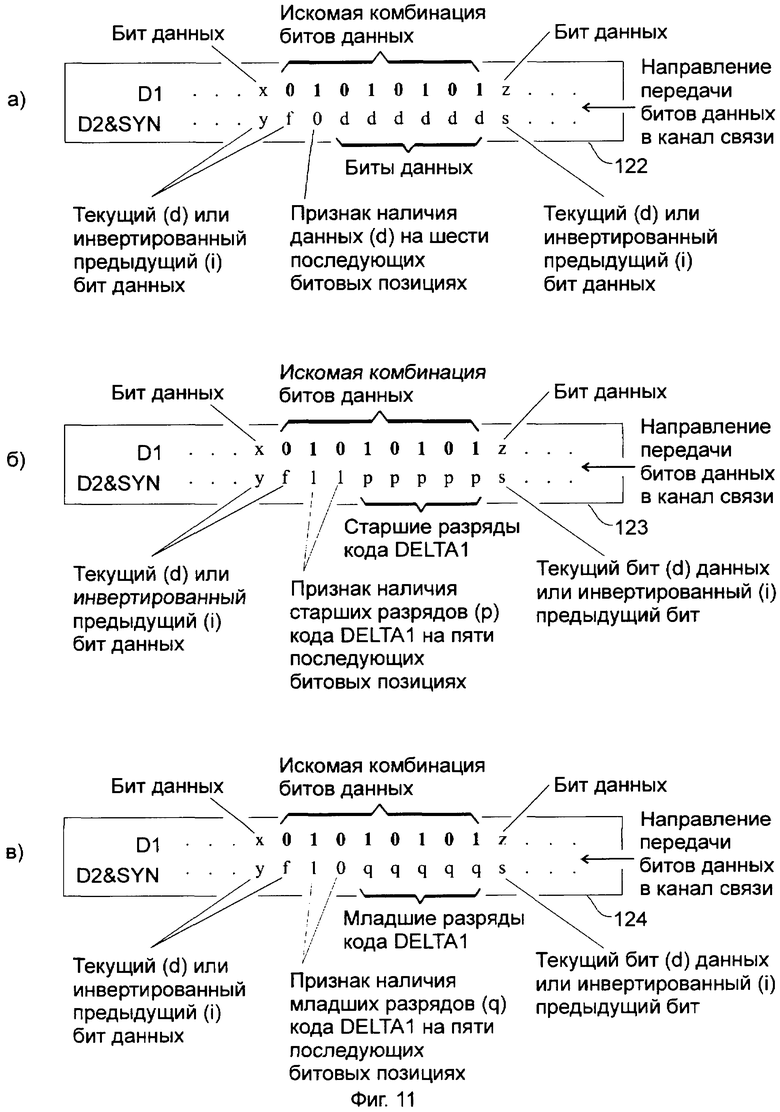

Диаграмма 122 (фиг.11) соответствует передаче битов данных без указания положения границ между кадрами, диаграммы 123 и 124 - передаче старших и младших разрядов указателя положения ближайшей границы между кадрами, переданными по первой 17 линии канала связи 11.

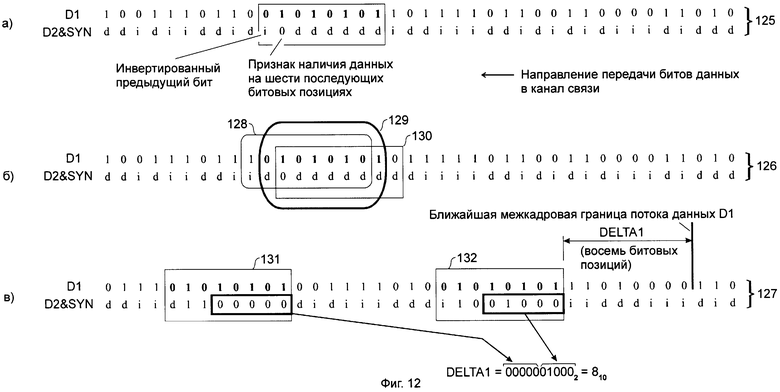

Кодовые ситуации 125 и 126 (фиг.12) соответствуют передаче данных без указания положения границ между кадрами. Кодовая ситуация 127 отображает указание положения границы между кадрами, передаваемыми по первой 17 линии канала связи 11. Рамками 128, 129 и 130 выделены пересекающиеся группы битов. Рамками 131 и 132 выделены группы битов, включающие старшие и младшие разряды указателя положения границы между кадрами.

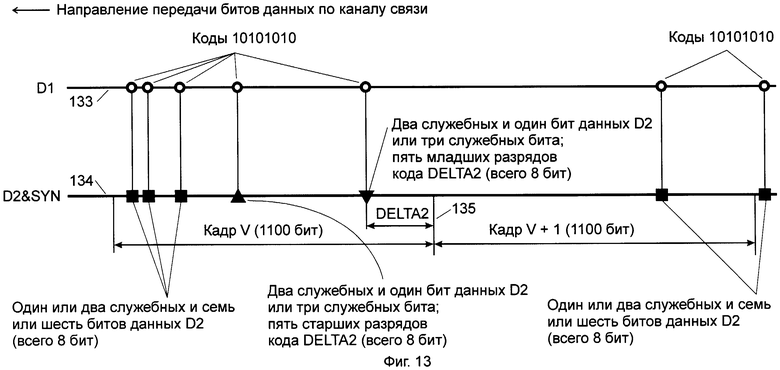

Диаграммы 133 и 134 (фиг.13) отображают последовательности битов, размещенные в памяти второго компьютера 31 после их приема из канала связи; линия 135 указывает границу между соседними кадрами данных, переданных по второй 18 линии канала связи 11.

Диаграмма 136 (фиг.14) соответствует передаче битов данных без указания положения границ между кадрами, диаграммы 137 и 138 - передаче старших и младших разрядов указателя положения ближайшей границы между кадрами, переданными по второй 18 линии канала связи 11.

Кодовая ситуация 139 (фиг.15) отображает указание положения границы между кадрами, передаваемыми по второй 18 линии канала связи 11. Рамками 140 и 141 выделены группы битов, включающие старшие и младшие разряды указателя положения границы между кадрами.

Диаграмма 142 (фиг.16) показывает положение области 143 работоспособности устройства при нулевой разности задержек распространения сигнала по первой 17 и второй 18 линиям канала связи 11. Диаграмма 144 отображает положение области 145 работоспособности устройства при положительной разности задержек распространения сигнала по первой и второй линиям канала связи. Диаграмма 146 показывает положение области 147 работоспособности устройства при отрицательной разности задержек распространения сигнала по первой и второй линиям канала связи. Диаграмма 148 (фиг.17) отображает структуру информационного кадра.

Далее рассмотрены способы передачи данных, применяемые при использовании известных устройств [1-3] (фиг.1).

Как показано на фиг.1, а, из устройства - передатчика в устройство - приемник передаются два сигнала: данные DATA и синхросигнал CLK (диаграммы 1 и 2). Сигнал DATA предназначен для передачи последовательного потока битов данных 3. В примере, приведенном на фиг.1, каждому биту из последовательности 01011100110 выделен так называемый битовый интервал. Границы между битовыми интервалами показаны на фиг.1 штриховыми линиями. Сигналам лог. 1 и лог. 0 в данном примере соответствуют напряжения высокого и низкого уровня.

При передаче данных согласно временным диаграммам 1 и 2 по отрицательному фронту синхросигнала CLK устройство - передатчик начинает выдачу очередного бита данных. По положительному фронту этого синхросигнала устройство - приемник фиксирует полученный бит. Источник синхросигналов может конструктивно размещаться в передатчике, приемнике или вне того и другого.

При передаче последовательности битов 6 согласно временным диаграммам 4 и 5, приведенным на фиг.1, б [2], сигнал DELIM разграничения битовых интервалов изменяется только в тех случаях, когда сигнал данных DATA остается неизменным. Таким образом, на любой границе битового интервала изменяется либо сигнал DATA, либо сигнал DELIM. Приемник отслеживает изменения этих сигналов и поэтому всегда располагает информацией о местоположении границ между битовыми интервалами.

Сравнивая пары диаграмм 1-2 и 4-5, можно отметить следующее. Во-первых, передаваемые данные формируются с одинаковым разбиением сигнала DATA на битовые интервалы. Во-вторых, сигнал DELIM претерпевает всего лишь четыре изменения, в то время как сигнал CLK изменяется 21 раз. В течение одного битового интервала сигнал CLK изменяется дважды, а сигнал DELIM - не более одного раза. Из этого следует, что при одинаковых физических параметрах устройств [1] и [2] (длине и конструкции кабеля, образующего канал связи, типах кабельных усилителей и т.п.) устройство [2] способно передавать данные с удвоенной скоростью.

Действительно, диаграммы 4-6 можно “сжать” по оси времени в два раза, при этом максимальная частота сигналов DATA и DELIM будет равна частоте сигнала CLK. Правомерна также иная трактовка результатов сравнения пар диаграмм 1-2 и 4-5: при равной скорости передачи данных устройствами [1] и [2] в устройстве [2] вдвое уменьшена максимально возможная частота сигнала, сопровождающего данные. Кроме того, при передаче случайных данных сигнал DELIM, в отличие от сигнала CLK, также можно рассматривать как случайный. При этом он не содержит ярко выраженных спектральных составляющих, что способствует снижению уровня помех, излучаемых в соседние провода кабеля. (Для преобразования произвольных данных к виду, близкому случайному, используют их аппаратное или программное скремблирование при передаче и дескремблирование при приеме).

В устройстве [3] применен усовершенствованный способ передачи данных с использованием сигнала разграничения битовых интервалов (фиг.1, в). Так же как и в устройстве [2], данные передаются по первой линии канала связи, а сигнал разграничения битовых интервалов - по второй. Однако в устройстве [3] сигнал разграничения битовых интервалов используется как по прямому назначению, так и (одновременно с этим) для передачи дополнительного потока данных. Точнее, устройство [3] одновременно передает по первой и второй линиям канала связи первую 9 и вторую 10 битовые последовательности D1 и D2. Первая последовательность (основная) передается с гарантированной скоростью, определяемой частотой следования битовых интервалов. Вторая последовательность (дополнительная) передается с меньшей скоростью, зависящей от вида первой последовательности.

Временная диаграмма 7 идентична диаграммам 1 и 4. Диаграммы 5 и 8 различаются тем, что последняя, помимо “обязательных” для разделения битовых интервалов фронтов сигнала (помечены точками), содержит семь позиций для передачи битовой последовательности 10 (D2). Обозначение “D2&SYN” отражает тот факт, что вторая линия канала связи используется для передачи данных D2 и битов синхронизации SYN, каждый из которых в устройстве [3] формируется инвертированием предыдущего бита.

Поясним сказанное. В период, соответствующий первым четырем битовым интервалам, сигнал D2&SYN можно использовать как “транспортное средство” для передачи первых четырех битов (dddd)=0111 из последовательности 10 (D2). В общем случае эти биты могут иметь произвольные значения. В частности, все они могут быть нулевыми или единичными. Такая “свобода выбора” значений битов возможна благодаря тому, что сигнал D1 в указанный период изменяется в каждом битовом интервале и используется приемником для распознавания границ между битами.

После выдачи битов (dddd)=0111, принадлежащих последовательности 10 (D2), на границе между четвертым и пятым битовыми интервалами передатчик создает гарантированный перепад уровней сигнала D2&SYN (этот перепад помечен точкой), так как сигнал D1 остается неизменным. Это достигается размещением в пятом битовом интервале инвертированного четвертого бита (i). Далее бит повторно инвертируется и размещается в шестом интервале, так как сигнал D1 по-прежнему неизменен, затем в седьмом интервале размещается очередной бит d, принадлежащий последовательности 10 (D2) и т.д.

При равновероятном появлении сигналов лог. 0 и лог. 1 в потоке данных D1 (что может быть достигнуто его предварительным скремблированием) скорость передачи данных D2 составляет 50% скорости передачи данных D1. Действительно, вероятность перепада уровней сигнала D1 на границе битовых интервалов j и k равна 0,5 и не зависит от предыстории. Но именно эта вероятность определяет возможность размещения очередного бита d в потоке сигналов D2&SYN. Таким образом, в среднем, каждый второй битовый интервал пригоден для передачи бита d данных. В результате, суммарная скорость передачи данных устройством [3] по сравнению с устройством [2] увеличена в 1,5 раза.

Рассмотренный способ передачи данных (см. фиг.1, в) с некоторыми усовершенствованиями использован в предлагаемом устройстве. Усовершенствования повышают скорость передачи данных, представленных в виде последовательности информационных кадров. Сигнал D2&SYN в предлагаемом устройстве несет дополнительную информационную нагрузку - он содержит сведения о расположении границ кадров, передаваемых по первой и второй линиям канала связи.

Ниже рассмотрена работа предлагаемого устройства в общем виде.

Устройство (фиг.2) обеспечивает передачу данных из компьютера 22 в компьютер 31. Данные в канале связи 11 представлены двумя параллельными потоками (основным и дополнительным), передаваемыми по линиям 17 и 18. Оба потока представлены последовательностями кадров. Каждый кадр содержит, в частности, контрольную сумму (циклический избыточный код CRC, см. фиг.17), по которой компьютер 31 может судить о правильности его передачи по каналу связи 11.

Так как задержки передачи сигналов по линиям 17 и 18 могут заметно различаться, а разбиение этих сигналов на битовые интервалы - общее, то для надежной передачи данных необходимо выравнивание задержек. Оно выполняется подбором оптимальной величины регулируемой (компенсирующей) задержки, которая задается элементами 33 или 34. Эта величина определяется компьютером 31 по результатам проведения серии программно-управляемых экспериментов, в ходе которых выявляется область работоспособности устройства (см. фиг.16). Параметры настройки регулируемых элементов задержки 33 и 34 выбираются так, чтобы обеспечить попадание в центр найденной области работоспособности. В результате устройство адаптируется к разности параметров линий 17 и 18 канала связи 11.

При этом разделение передаваемых потоков данных на кадры не приводит к снижению скорости передачи основного потока данных благодаря тому, что информация о положении межкадровых границ включается в состав дополнительного (а не основного) потока данных (см. фиг.10 - фиг.15).

Ниже рассмотрена работа составных частей устройства.

Компьютер 22 (фиг.2) хранит данные, которые должны быть переданы в компьютер 31. Эти данные могут быть сформированы, например, в результате опроса датчиков либо получены по каналам связи (датчики и упомянутые каналы связи не показаны) и т.д. Данные преобразуются (в частности, данные основного канала программно или аппаратно скремблируются) и затем побайтно передаются через выходной порт 28 в двухканальный преобразователь 23 параллельного кода в последовательный. Передаче каждого байта предшествует проверка сигнала готовности, который поступает во входной порт 27. Выдача очередного байта компьютером 22 в порт 28 происходит только при обнаружении очередного сигнала готовности (RDY=1) во входном порте 27.

Все процессы, протекающие при передаче данных, синхронизированы сигналами от генератора 14. Этот генератор формирует непрерывную последовательность синхроимпульсов со скважностью, равной двум (см. диаграмму 53 на фиг.3). Период синхросигнала равен длительности битового интервала.

Двухканальный преобразователь 23 параллельного кода в последовательный (фиг.3) при наличии сигнала P/S=0 по положительному фронту синхросигнала С принимает байт данных DOUT в регистры 48 и 49. После перехода сигнала P/S в состояние лог. 1 по положительным фронтам синхросигнала С данные в регистрах 48 и 49 сдвигаются в направлениях, указанных стрелками 52. Сдвиг повторяется три раза, затем в регистрах фиксируется новый байт данных DOUT, затем осуществляется троекратный сдвиг четырехразрядных кодов в регистрах и т.д. (см. временные диаграммы 53-58). В результате на выходах 24 и 25 формируются две последовательности битов (основная и дополнительная), которые через усилители 15 и 16 передаются в линии 17 и 18 канала связи 11.

Сигнал P/S=0 (RDY=0) формируется при наличии двух сигналов лог. 1 на выходах двоичного счетчика 50. Счетчик 50 прибавляет единицу по отрицательному фронту синхросигнала. Начальное состояние счетчика не определено.

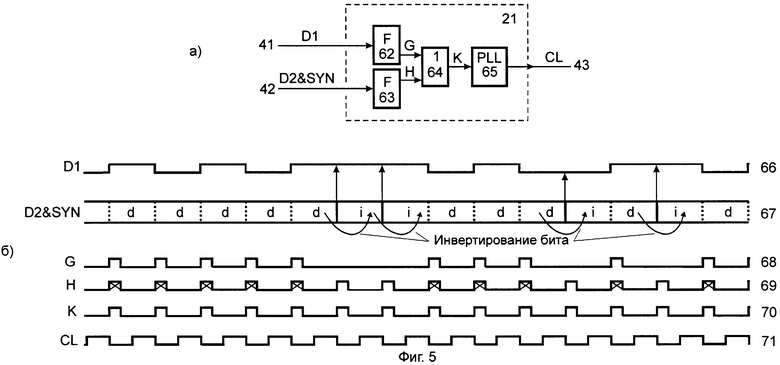

Как показано на временных диаграммах 60 и 61 (фиг.4), по линиям 17 и 18 канала связи 11 передаются сигналы D1 и D2&SYN - аналоги соответствующих сигналов, показанных на фиг.1, в. Границы битовых интервалов определяются положительными фронтами синхросигнала С (диаграмма 59) от генератора 14. Сигнал D2&SYN содержит биты данных d и служебные биты i, каждый из которых получен инвертированием предыдущего. Служебные биты i обеспечивают формирование “обязательных” фронтов сигнала в линии 18 в тех случаях, когда сигнал в линии 17 остается неизменным.

На фиг.4 “необязательные” фронты сигнала D2&SYN отображены пунктирными линиями. Термин “необязательные” использован в том смысле, что наличие или отсутствие фронта зависит от конкретной последовательности передаваемых битов d. “Обязательные” фронты (положительные или отрицательные) сигнала D2&SYN отображены на фиг.4 сплошными линиями; вертикальные стрелки указывают границы битовых интервалов сигнала D1, который в течение некоторых периодов времени остается неизменным. Далее будет показано, что биты d используются как для передачи данных по линии 18 канала связи 11, так и для указания положения границ между кадрами, передаваемыми по линиям 17 и 18.

Канал связи 14 может быть выполнен в виде двух витых пар проводов, двух оптоволоконных линий или иных средств передачи сигналов, в том числе содержащих ретрансляторы.

Переданные по каналу связи 14 ослабленные сигналы восстанавливаются по амплитуде усилителями 19 и 20. Разность задержек сигналов с выходов усилителей 19 и 20 компенсируется регулируемыми элементами задержки 33 или 34. Выровненные по времени сигналы поступают на входы блока 21 формирования синхросигнала (фиг.5, а). Формирователь импульсов 62 (63) вырабатывает кратковременный (например, длительностью, равной четверти битового интервала) положительный импульс в ответ на любое изменение сигнала на его входе, т.е. реагирует как на положительный, так и на отрицательный фронт входного сигнала (фиг.5, б, диаграммы 66-69).

В примере, приведенном на фиг.5, б, в сигнале G отсутствуют импульсы на позициях, соответствующих вертикальным стрелкам между диаграммами 67 и 66. Так как сигнал D2&SYN показан условно, без указания конкретного кода, то заранее не известно, будут ли сформированы импульсы, помеченные на диаграмме 69 крестиками. Но при этом можно утверждать, что остальные импульсы на этой диаграмме будут обязательно сформированы, так как они соответствуют гарантированным изменениям сигнала D2&SYN при его инвертировании. Таким образом, с помощью элемента ИЛИ 64 “недостающие” импульсы восполняются, и сигнал К (диаграмма 70) представляет собой периодическую последовательность импульсов без “пробелов”. Этот сигнал поступает на вход синхронизации блока 65 фазовой автоподстройки частоты.

Блок 65 может быть выполнен по одной из известных схем (см., например, пат. США №6215835 B1). Он предназначен для формирования высокостабильного синхросигнала CL на основе непрерывного слежения за входным сигналом К. В данном примере отрицательный фронт сигнала CL привязан к положительному фронту сигнала К. Благодаря достаточной “инерционности” блока 65 сигнал CL практически нечувствителен к “дрожанию фазы” сигнала К и иным его кратковременным искажениям, вызванным помехами в канале связи. (Такое использование стандартного блока фазовой автоподстройки частоты в телекоммуникационных системах является общепринятым и далее не детализируется).

Сигналы D1, D2&SYN и CL поступают на входы 41-43 двухканального преобразователя 32 последовательного кода в параллельный (фиг.6). По положительному фронту сигнала CL данные в сдвиговых регистрах 74 и 75 продвигаются на один разряд в направлениях, указанных стрелками 80. Одновременно с этим в освободившиеся разряды регистров 74 и 75 принимаются биты данных D1 и D2&SYN. В каждом четвертом такте синхросигнала CL содержимое сдвиговых регистров 74 и 75 переписывается в параллельные регистры 72 и 73. Таким образом, последовательные потоки данных D1 и D2&SYN преобразуются в поток байтов DIN (см. временные диаграммы 81-89).

Переход сигнала READY из состояния лог. 1 в состояние лог. 0 свидетельствует о готовности вновь сформированного байта DIN к последующему считыванию компьютером 31. Сигнал READY=1 (признак отсутствия готовности данных DIN) формируется при наличии двух сигналов лог. 1 на выходах двоичного счетчика 76. Счетчик 76 выполнен по схеме с последовательным переносом, что исключает ложные срабатывания элемента И 77 при переключении счетчика из состояния “01” в состояние “10”. Прибавление единицы младшего разряда к текущему содержимому счетчика происходит по отрицательному фронту синхросигнала на его входе С. Начальное состояние счетчика 76 не определено, поэтому первоначальная точка отсчета границ байтов DIN произвольна (потоки байтов DOUT и DIN могут совпадать или не совпадать из-за смещения точек отсчета границ, что в данном случае несущественно).

Регулируемый элемент задержки 33 (34) (фиг.7) построен на основе последовательно включенных элементов задержки 91. Время распространения сигнала через элемент 91 в данном примере равно 1/15 части битового интервала. Мультиплексор 90 транслирует сигнал с входа, выбранного кодом DLY1 (DLY2). При DLY1=0000 (DLY2=0000) сигнал с входа 35 (36) передается на выход 41 (42) без задержки (задержкой мультиплексора пренебрегаем); при DLY1=0001 (DLY2=0001) - с задержкой элемента 91 и т.д.; при DLY1=1111 (DLY2=1111) - с задержкой, равной одному битовому интервалу (фиг.8, временные диаграммы 92-108). В отсутствие необходимости коррекции задержек коды DLY1 и DLY2 выбираются нулевыми.

Компьютер 31 использует входные порты 45 и 46 для приема потока байтов DIN. Принятые данные размещаются в памяти компьютера и анализируются. Определяются границы информационных кадров, из последовательности битов D2&SYN удаляются биты синхронизации SYN, программно или аппаратно дескремблируются данные, полученные по линии 17 канала связи 11. Затем проверяется правильность принятых кадров сопоставлением вычисленных и полученных из канала связи циклических избыточных кодов CRC (см. структуру кадра, приведенную на фиг.17).

При выполнении программы поиска области работоспособности компьютер 31 подбирает оптимальное соотношение кодов DLY1 и DLY2, при котором происходит попадание в центр этой области (см. фиг.16).

Далее приведено более подробное описание работы устройства.

Исходные данные 109 (фиг.9), предназначенные для преобразования и последующей передачи в канал связи, хранятся в памяти компьютера 22 и представлены последовательностями битов D1’ и D2 (диаграммы 110 и 111). Эти последовательности разделены на информационные кадры. Кадры последовательностей D1’ и D2 в общем случае могут иметь разную длину. На первом этапе преобразования (см. указатель 112) данные D1’ скремблируются, т.е. приводятся к виду, при котором их можно рассматривать как случайные (псевдослучайные).

Для определенности предположим, что при скремблировании используется аппаратный или программный генератор псевдослучайной последовательности с периодом повторения 28-1=255 бит. Таким образом, не скремблированная последовательность битов D1’ преобразуется в скремблированную последовательность D1 (диаграмма 113), в которой любой заранее заданный восьмиразрядный код (за исключением нулевого) повторяется со средним периодом, близким 255 бит. Последовательность битов D2 (114) остается неизменной, т.е. совпадает с последовательностью 111.

Скремблирование, во-первых, позволяет заменить длинные цепочки одноименных битов (000...0 или 111...1), которые могут присутствовать в данных D1’, псевдослучайными битами. Последние характеризуются практически равной вероятностью появления лог. 0 и 1. При этом, как уже отмечалось, вероятность перепада уровней сигнала D1 на границе битовых интервалов j и k равна 0,5 и не зависит от предыстории. Это гарантирует передачу данных d (см. фиг.4) без заметных приостановок. Во-вторых, благодаря скремблированию, в основном потоке данных 113 (116) с некоторым случайным периодом наблюдаются не перекрывающиеся коды 01010101 и 10101010, каждый из которых наиболее благоприятен для размещения данных d в дополнительном потоке, так как при передаче этих кодов сигнал в линии 17 изменяется в каждом битовом интервале. Эти коды, как показано далее, используются для передачи по линии 18 информации о положении границ между кадрами.

На втором этапе преобразования (см. указатель 115) данные D1 остаются неизменными (последовательности 113 и 116 совпадают), а в последовательность 114 вводятся биты SYN синхронизации. В результате формируется адаптированная к последовательности D1 (116) последовательность D2&SYN (117). К битам синхронизации относятся рассмотренные ранее биты i (см. фиг.4, диаграмму 61), а также указатели положения границ между кадрами, структура которых рассмотрена ниже. Фрагменты последовательностей 116 и 117 (один из фрагментов выделен рамкой 118) последовательно пересылаются компьютером 22 в выходной порт 28.

Переданные по каналу связи последовательности 116 и 117 размещаются в памяти компьютера 31, который анализирует их и преобразует в обратной последовательности, выполняя переход от диаграммы 115 к диаграмме 112 и затем к диаграмме 109.

Указание положения границ кадров осуществляется на этапе формирования компьютером 22 адаптированной последовательности битов 117 следующим образом. Как показано на фиг.10 черными точками, в потоке псевдослучайных данных D1 (119) периодически (со средним периодом, близким 255 бит) встречаются коды 01010101. Передача этих кодов сопровождается гарантированным изменением состояния сигнала D1 в первой линии 17 канала связи 11 на границах между битовыми интервалами. Поэтому коды 01010101 (равно как и не перекрывающиеся с ними коды 10101010) удобно использовать для передачи некоторых “особых” кодов по второй линии 18 канала связи 11.

Особые коды на диаграмме 120 размещены под кодами 01010101 и отображены в виде квадратов и треугольников. Коды, обозначенные квадратами, используются для передачи данных d (фиг.11, а, диаграмма 122). Код, обозначенный треугольником с направленной вверх вершиной, используется для указания пяти старших разрядов кода DELTA1, с помощью которого задается расстояние от границы 121 между кадрами до ближайшего расположенного слева кода 01010101, передаваемого по первой 17 линии канала связи 11 (фиг.11, б, диаграмма 123). Код, обозначенный треугольником с направленной вниз вершиной, используется для указания пяти младших разрядов кода DELTA1 (фиг.11, в, диаграмма 124).

Для того чтобы компьютер 31 после приема и размещения последовательностей 116 и 117 (фиг.9) в памяти мог различить указанные особые коды, применен следующий способ их идентификации. Если второй разряд (считая от единицы слева направо) особого кода равен 0, то на шести последующих битовых позициях размещены данные d (фиг.11, а, диаграмма 122). В противном случае в зависимости от состояния третьего разряда (1 или 0) на шести последующих битовых позициях размещены старшие или младшие разряды кода DELTA1 (фиг.11, б, в, диаграммы 123 и 124). Первые разряды f особых кодов могут использоваться для передачи битов d или i в зависимости от значения бита “х”, предшествующего передаче кода 01010101: при х=1 передается бит d (так как имеется перепад уровня сигнала D1); при х=0 передается бит i (так как перепада уровня сигнала нет). В зависимости от значения бита данных z бит s используется либо для передачи бита данных d (при z=0 имеется отрицательный фронт сигнала D1), либо для передачи бита i (при z=1 нет изменения уровня сигнала).

В кодовой ситуации, показанной на фиг.10, передаваемые по первой линии 17 канала связи 11 кадры данных имеют длину 1000 бит. Кадры непрерывно следуют друг за другом. В среднем, число особых кодов, соответствующих каждому кадру, составляет 1000/255 ≈ 3,9. Два ближайших слева к границе 121 особых кода (если они есть) используются для отображения расстояния DELTA1 до этой границы; остальные (если они есть) применяются для передачи данных d. Некоторые кадры не сопровождаются достаточным для отображения расстояния DELTA1 числом особых кодов (см. кадр J+1 на фиг.10). Такие кадры остаются без указателей границ. Компьютер 31 регистрирует границы большинства принятых кадров; остальные границы (относительно положения которых нет информации в явном виде) вычисляются на основе предыдущих или (и) последующих, сопровождаемых кодами DELTA1.

Рассмотренный способ указания положения границ между кадрами более подробно поясняется примерами кодовых ситуаций, представленными на фиг.12.

Диаграмма 125 (фиг.12, а) отображает использование особого кода, размещенного под кодом 01010101 (оба кода выделены рамкой), для передачи данных d. Эта диаграмма соответствует последовательностям битов, подготовленным к выдаче в канал связи 11 из памяти компьютера 22. Диаграмма получена в результате адаптации последовательности битов 117 к последовательности 116 (фиг.9). Адаптация в данном случае состоит в следующем. Компьютер 22 просматривает скремблированную последовательность битов D1 и обнаруживает в ней код 01010101. Предположим, что компьютер 22 принял решение использовать соответствующий особый код не для указания положения границы между кадрами (например, когда для такого указания уже выделены другие особые коды, обнаруженные при более раннем просмотре последовательности битов D1), а для передачи данных d. В этом случае первый бит особого кода устанавливается в состояние i (предыдущий бит инвертируется), так как коду 01010101 предшествует нулевой бит. Второй бит особого кода устанавливается компьютером 22 в 0, что является признаком наличия данных на шести последующих битовых позициях, затем размещаются биты d.

Эта же диаграмма (125) соответствует данным, размещенным в памяти компьютера 31 после их передачи по каналу связи 11. Компьютер 31 просматривает диаграмму через движущуюся слева направо рамку и обнаруживает в верхней строке код 01010101, а под ним - особый код i0dddddd. Первый бит этого кода игнорируется (как служебный), второй бит, равный нулю, свидетельствует о том, что на шести последующих битовых позициях размещены данные D2, что принимается к сведению.

Для указания положений границ кадров, передаваемых по линиям 17 и 18 канала связи 11, используются соответственно коды D1=01010101 и D1=10101010, причем эти коды не пересекаются в любых сочетаниях (т.е. не содержат общих битов). Для однозначности трактовки “спорных” кодовых ситуаций, подобных выделенным на диаграмме 126 (фиг.12, б) рамками 128-130, принимаются два соглашения.

1. Если обнаружена группа битов, в которой можно выделить пересекающиеся коды 01010101 и 10101010, то за основу принимается код 01010101, так как он имеет более высокий приоритет при поиске, чем код 10101010.

2. Если обнаружена группа битов, в которой можно выделить пересекающиеся коды 01010101, то за основу принимается крайний левый код 01010101 в этой группе (то же относится и к кодам 10101010 при их поиске).

Поясним сказанное. При просмотре последовательности 126 сначала проводится поиск не пересекающихся между собой кодов 01010101. Из пересекающихся кодов 01010101, например содержащихся в последовательности 10101010101, выделяется крайний левый восьмиразрядный код 01010101 (этот код подчеркнут, см. также содержимое рамки 129). Коды 10101010 (рамки 128 и 130) игнорируются; поиск таких кодов проводится на последующих этапах с учетом ранее найденных кодов 01010101. Точнее, при последующем поиске кодов 10101010 найденные ранее коды D1=01010101 (подобные коду, выделенному рамкой 129) не должны пересекаться с искомыми.

Кодовая ситуация 127 (фиг.12, в) отображает указание положения границы между кадрами, передаваемыми по первой 17 линии канала связи 11. Код DELTA1 составлен из двух частей, принадлежащих особым кодам, размещенным в рамках 131 и 132. В данном примере код DELTA1 равен восьми, что, как следует из диаграммы 127, согласуется с числом битовых позиций, отделяющих правую границу особого кода в рамке 132 от ближайшей справа границы между кадрами.

Диаграммы, представленные на фиг.13 - фиг.15, по содержанию близки рассмотренным ранее (см. фиг.10 - фиг.12). Отличия состоят в том, что в данном случае описывается способ указания границ кадров, передаваемых по второй 18 (а не по первой 17) линии канала связи 11. При этом вместо кодов D1=01010101, отображаемых семью изменениями уровня сигнала, используются равноценные коды D1=10101010 для передачи особых кодов по второй 18 линии канала связи 11.

Указание положения границ кадров, передаваемых по второй 18 линии канала связи 11, осуществляется на этапе подготовки последовательности 117 (фиг.9).

Особые коды на диаграмме 134 (фиг.13) отображены в виде черных квадратов и треугольников и размещены под кодами 10101010, обозначенными кружками. Коды, обозначенные квадратами, используются для передачи данных d (фиг.14, а, диаграмма 136). Код, обозначенный треугольником с направленной вверх вершиной, используется для указания пяти старших разрядов кода DELTA2, с помощью которого задается расстояние от границы 135 между кадрами до ближайшего расположенного слева кода 10101010, передаваемого по первой 17 линии канала связи 11 (фиг.14, б, диаграмма 137). Код, обозначенный треугольником с направленной вниз вершиной, используется для указания пяти младших разрядов кода DELTA2 (фиг.14, в, диаграмма 138).

Для того чтобы компьютер 31 после приема и размещения последовательностей 116 и 117 (фиг.9) в памяти мог различить указанные особые коды, применен способ идентификации, полностью совпадающий с рассмотренным ранее. Если второй разряд (считая от единицы слева направо) особого кода равен 0, то на шести последующих битовых позициях размещены данные d (фиг.14, а, диаграмма 136). В противном случае в зависимости от состояния третьего разряда (1 или 0) на шести последующих битовых позициях размещены старшие или младшие разряды кода DELTA2 (фиг.14, б, в, диаграммы 137 и 138). Первые разряды f особых кодов могут использоваться для передачи битов d или i в зависимости от значения бита “х”, предшествующего передаче кода 10101010: при х=0 передается бит d (так как имеется перепад уровня сигнала D1); при х=1 передается бит i (так как перепада уровня сигнала нет). В зависимости от значения бита данных z бит s используется либо для передачи бита данных d (при z=1 имеется положительный фронт сигнала D1), либо для передачи бита i (при z=0 нет изменения уровня сигнала).

В кодовой ситуации, показанной на фиг.13, передаваемые по второй линии 18 канала связи 11 кадры данных имеют длину 1100 бит. Кадры непрерывно следуют друг за другом. В среднем, число особых кодов 10101010, соответствующих каждому кадру, составляет 1100/255≈4,3. Два ближайших слева к границе 135 особых кода (если они есть) используются для отображения расстояния DELTA2 до этой границы; остальные (если они есть) применяются для передачи данных d. Некоторые кадры не сопровождаются достаточным для отображения расстояния DELTA2 числом особых кодов (см. кадр V+1 на фиг.13). Компьютер 31 регистрирует границы большинства принятых кадров; остальные границы (относительно положения которых нет информации в явном виде) вычисляются на основе предыдущих или (и) последующих, сопровождаемых кодами DELTA2.

Рассмотренный способ указания положения границ между кадрами, передаваемыми по второй 18 линии канала связи 11, более подробно поясняется примером кодовой ситуации, представленным на фиг.15.

Код DELTA2 составлен из двух частей, принадлежащих особым кодам, размещенным в рамках 140 и 141. В данном примере код DELTA2 равен семи, что, как следует из диаграммы 139, согласуется с числом позиций битов d, отделяющих правую границу особого кода в рамке 141 от ближайшей справа границы между кадрами, передаваемыми по второй 18 линии канала связи 11.

Описанный способ кодирования-декодирования информации о положении границ между кадрами, передаваемыми по линиям канала связи 11, позволяет компьютеру 31 восстановить исходную структуру принятых из канала данных, т.е. сформировать разделенные на кадры последовательности битов, эквивалентные приведенным на диаграммах 110 и 111 (фиг.9).

Кадр (см. диаграмму 148 на фиг.17) содержит заголовок, данные и циклический избыточный код CRC (контрольную сумму). Этот код вычисляется компьютером 22 для каждого кадра на этапе формирования исходных данных (см. диаграммы 110 и 111). Компьютер 31 проверяет соответствие полученного из канала связи кода CRC вновь вычисленному. В отсутствие ошибок принятый и вычисленный коды совпадают; при наличии ошибок коды различаются. Таким образом, компьютер 31 способен обнаруживать ошибки в принятом кадре (и, анализируя код CRC, исправлять некоторые из них).

Далее рассмотрен процесс адаптации устройства к разности задержек, которыми сопровождается передача данных по линиям 17 и 18 канала связи 11.

В исходном состоянии (например, при первом включении устройства) компьютер 31 устанавливает первый 33 и второй 34 регулируемые элементы задержки в состояния, при которых сигналы с входов 35 и 36 непосредственно (с пренебрежимо малой задержкой мультиплексора 90) передаются на их выходы 41 и 42. Это достигается установкой на управляющих входах 37 и 38 этих мультиплексоров нулевых кодов (DLY1=DLY2=0). При нулевой разности задержек, которыми сопровождается передача данных по линиям 17 и 18 канала связи 11 (идеальная ситуация), выбранная настройка элементов 33 и 34 обеспечивает попадание в центр области 143 (фиг.16) работоспособности устройства. В этом случае принятые из канала связи кадры либо не содержат ошибок, либо их интенсивность не превышает допустимого уровня.

Для определения положений правой и левой границ области 143 работоспособности устройства компьютер 31 проводит две серии экспериментов.

В первой серии экспериментов определяется положение правой границы области работоспособности. Задержка элемента 34 устанавливается равной 0. Задержка элемента 33 постепенно увеличивается до предельного значения, после которого интенсивность ошибок превышает допустимый уровень либо устройство оказывается неработоспособным. В примере, приведенном на фиг.16, а, код DLY1 последовательно устанавливается в состояния 1, 2 и 3; при каждом состоянии проверяется правильность приема по обеим линиям канала связи 11 некоторого заранее заданного числа кадров, например, равного 1000. При DLY1=4 интенсивность ошибок превышает допустимый уровень либо устройство теряет работоспособность.

Во второй серии экспериментов определяется положение левой границы области работоспособности. Задержка элемента 33 устанавливается равной 0. Задержка элемента 34 постепенно увеличивается до предельного значения, после которого интенсивность ошибок превышает допустимый уровень либо устройство оказывается неработоспособным. В примере, приведенном на фиг.16, а, код DLY2 последовательно устанавливается в состояния 1, 2 и 3; при этом устройство сохраняет работоспособность. Код DLY2=4 соответствует выходу за пределы области работоспособности устройства. Центр этой области, таким образом, соответствует условию DLY1=DLY2=0.

В примере, показанном на фиг.16, б, область 145 работоспособности смещена влево относительно области 143; ее центр определяется условием DLY1=0, DLY2=3. Начальная установка нулевых кодов DLY1=DLY2=0 соответствует работоспособному состоянию устройства, однако в данном случае первый же эксперимент по поиску положения правой границы области 145 завершается потерей работоспособности. Левая граница и центр области 145 определяются условиями DLY1=0, DLY2=6 и DLY1=0, DLY2=3.

В примере, показанном на фиг.16, в, область 147 работоспособности смещена вправо настолько, что начальная установка нулевых кодов DLY1=DLY2=0 соответствует неработоспособному состоянию устройства. Это связано с тем, что задержка передачи сигнала по линии 18 значительно превышает задержку передачи сигнала по линии 17. Компьютер 31 проводит поиск области 147 перебором приведенных на диаграмме 146 сочетаний кодов DLY1 и DLY2. Как следует из этой диаграммы, для выравнивания задержек сигналов, передаваемых по линиям 17 и 18 канала связи 11, следует задать режим работы элемента 33 установкой кода DLY1 в диапазоне 9-15. Центр области 147 определяются условиями DLY1=12, DLY2=0.

Полученные в результате проведения описанных программно-управляемых экспериментов оптимальные коды DLY1 и DLY2, соответствующие центру найденной области работоспособности, запоминаются в энергонезависимой памяти компьютера 31. Если параметры канала связи периодически изменяются (например, из-за перепадов температуры), то адаптация устройства к таким изменениям проводится достаточно часто, чтобы вовремя отслеживать такие изменения.

Таким образом, увеличение дальности связи предлагаемого устройства по сравнению с устройством [3] достигнуто благодаря его адаптации к разности задержек распространения сигнала по двум параллельным линиям канала связи. Эта разность компенсируется задержкой того сигнала, который приходит в блок приема данных с относительным опережением другого.

По сравнению с устройством [3] повышена скорость передачи основного потока данных, передаваемых по первой линии канала связи и представленных в виде последовательности информационных кадров. В то время как в устройстве [3] начало каждого кадра помечается флаговым кодом, а в тело кадра в результате применения битстаффинга вводятся служебные биты, в предлагаемом устройстве кадры передаются без флаговых кодов и без применения битстаффинга. Указание положения границ между информационными кадрами, передаваемыми по первой и второй линиям канала связи, проводится только с использованием информации, передаваемой в составе дополнительного потока данных.

Источники информации

1. Патент США №6044421 (Fig.5).

2. Патент США №6044421 (Fig.1, 2).

3. Патент РФ №2205445 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214045C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

Изобретение относится к устройствам для передачи данных и может быть использовано в синхронных телекоммуникационных системах. Технический результат, достигаемый при реализации изобретения, - увеличение дальности связи и повышение скорости передачи данных по первой линии канала связи. Устройство содержит подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит первый компьютер, двухканальный преобразователь параллельного кода в последовательный, генератор синхросигналов, первый и второй усилители, блок приема данных содержит второй компьютер, двухканальный преобразователь последовательного кода в параллельный, первый и второй регулируемые элементы задержки, третий и четвертый усилители и блок формирования синхросигнала. Увеличение дальности связи достигнуто благодаря адаптации устройства к разности задержек распространения сигнала по двум параллельным линиям канала связи. Повышение скорости передачи данных по первой линии обеспечивается указанием положения границ между информационными кадрами без использования флаговых и иных служебных битов. 3 з.п. ф-лы, 17 ил.

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНЫХ СООБЩЕНИЙ | 1991 |

|

RU2013867C1 |

| US 6044421 A, 28.03.2000 | |||

| US 6269414 A, 31.07.2001. | |||

Авторы

Даты

2004-12-20—Публикация

2003-06-09—Подача