Изобретение относится к электронным схемам общего назначения, в частности к схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами.

Известно устройство [1], содержащее подключенные к противоположным сторонам канала связи блоки передачи и приема данных, входы блоков передачи и выходы блоков приема данных являются входами и выходами устройства, канал связи содержит группу витых пар проводов по числу входов устройства. По одной из витых пар проводов канала передается сигнал синхронизации, по остальным витым парам - биты данных.

Недостатком устройства [1] является низкая эффективность использования канала связи. Для передачи n-разрядных слов канал должен содержать n+1 витую пару проводов, одна из которых используется для трансляции синхросигнала, а остальные - для пересылки битов данных.

Известно устройство [2] для кодирования - декодирования данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов является первым выходом синхронизации устройства, группа входов блока передачи данных является группой входов данных устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов канала связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов канала связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра, выход инвертора является вторым выходом синхронизации устройства, группа выходов блока приема данных является группой выходов данных устройства.

Устройство [2] преобразует параллельный двоичный код данных и синхросигнал в группу троичных сигналов, которая передается по каналу связи - набору витых пар проводов. На приемной стороне устройства группа троичных сигналов преобразуется в исходный двоичный код, сопровождаемый восстановленным синхросигналом.

Недостатком устройства [2] является низкая скорость передачи данных по каналу связи. Это связано с тем, что в канале связи данные чередуются во времени с синхросигналом. Поэтому половина потенциальной пропускной способности канала связи теряется. Цель изобретения - повышение скорости передачи данных.

Цель достигается тем, что в устройстве для кодирования - декодирования данных, содержащем подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов является первым выходом синхронизации устройства, группа входов блока передачи данных является группой входов данных устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов канала связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов канала связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра, выход инвертора является вторым выходом синхронизации устройства, группа выходов данных блока приема данных является группой выходов данных устройства, блок передачи данных дополнительно содержит регистр, компаратор, первый и второй триггеры, группа входов данных устройства соединена с первой группой входов компаратора и с входами данных регистра, выходы которого соединены с входами шифратора и с второй группой входов компаратора, выход которого соединен с входом данных первого триггера, выход единичного плеча которого соединен с входом шифратора и с входом данных второго триггера, выход которого соединен с входом установки нуля первого триггера, выход нулевого плеча которого соединен с входом установки нуля второго триггера, выход генератора синхросигналов соединен с входами синхронизации регистра, первого и второго триггеров, блок приема данных дополнительно содержит второй регистр, группу формирователей импульсов, блок фазовой автоподстройки частоты, элемент ИЛИ, элемент ИЛИ-НЕ, выходы дешифратора соединены с входами группы формирователей импульсов, выходы которых через элемент ИЛИ соединены с входом блока фазовой автоподстройки частоты, выход которого соединен с входом инвертора, с первым входом элемента ИЛИ-НЕ и с входом синхронизации первого регистра, выход элемента ИЛИ-НЕ соединен с входом синхронизации второго регистра, выходы первого регистра соединены с входами данных второго регистра и с входом элемента задержки, выход которого соединен с вторым входом элемента ИЛИ-НЕ, выходы второго регистра являются группой выходов данных блока приема данных.

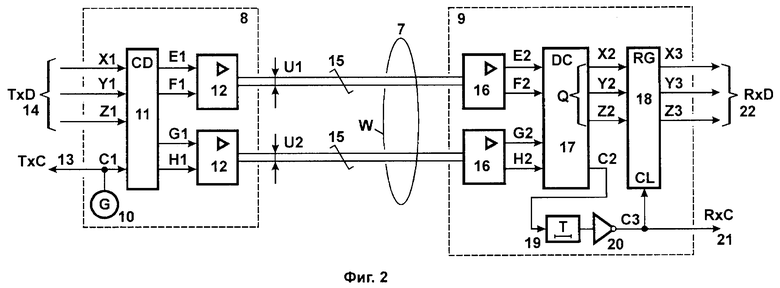

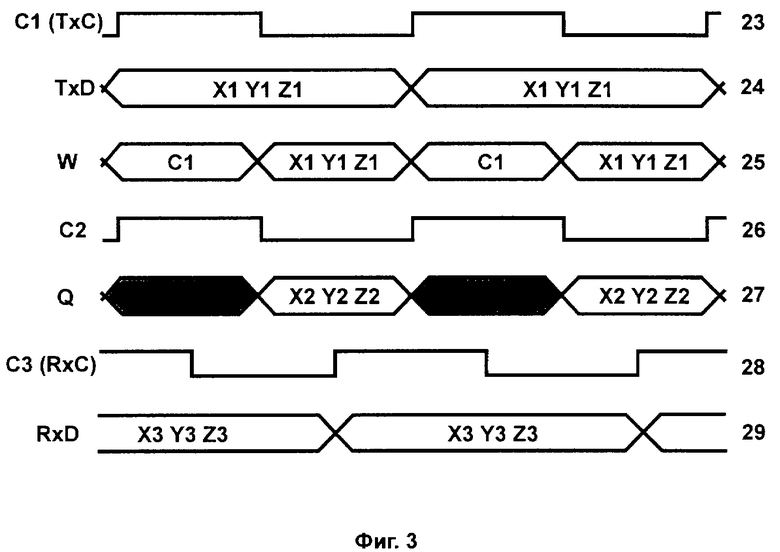

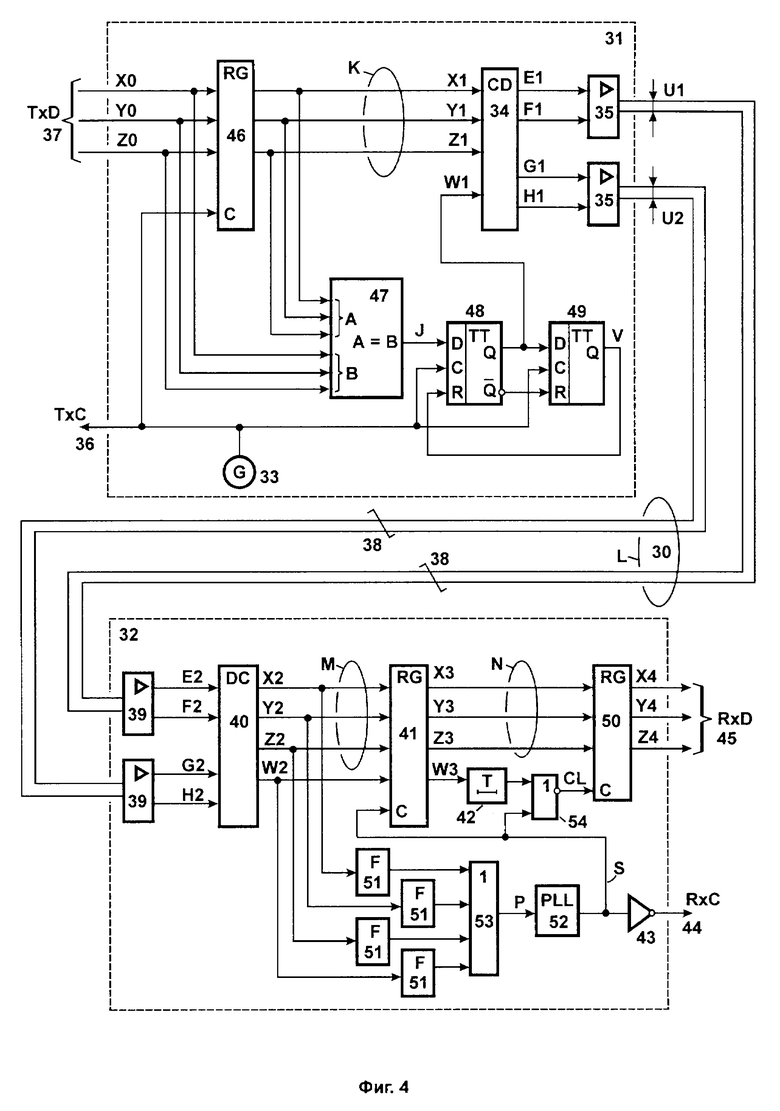

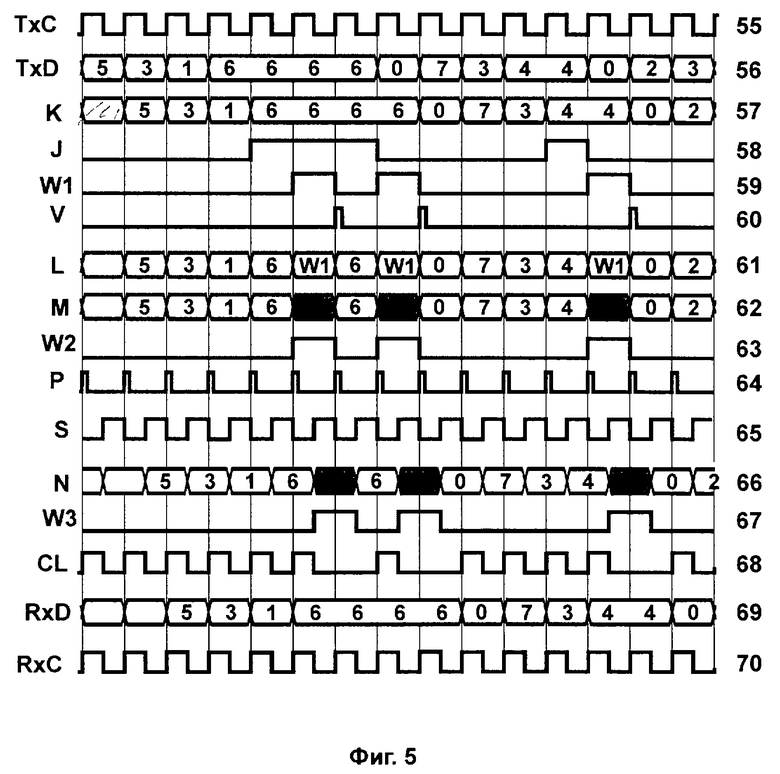

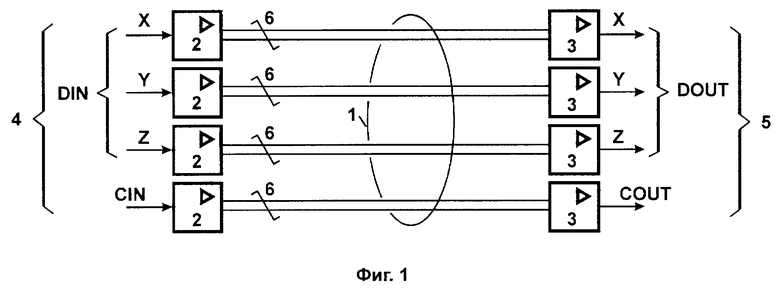

На фиг.1 и 2 представлены схемы известных устройств [1] и [2]; на фиг.3 - временные диаграммы передачи данных устройством [2]; на фиг.4 и 5 - схема и временные диаграммы работы предлагаемого устройства.

Устройство [1] (фиг.1) содержит подключенные к противоположным сторонам канала связи 1 блоки 2 передачи и 3 приема данных, входы 4 блоков передачи и выходы 5 блоков приема данных являются входами и выходами устройства, канал связи 1 содержит группу витых пар 6 проводов по числу входов устройства.

Устройство [2] (фиг.2) содержит подключенные к противоположным сторонам канала связи 7 блок 8 передачи данных и блок 9 приема данных, блок 8 содержит генератор 10 синхросигналов, шифратор 11, группу выходных усилителей 12, выход генератора 10 является первым выходом 13 синхронизации устройства, группа входов 14 блока передачи данных является группой входов данных устройства, группа выходов шифратора 11 соединена с входами группы выходных усилителей 12, выходы которых соединены с витыми парами 15 проводов канала 7, блок 9 приема данных содержит группу входных усилителей 16, дешифратор 17, первый регистр 18, элемент задержки 19 и инвертор 20, входы группы входных усилителей 16 соединены с витыми парами 15 проводов канала 7, а их выходы - с входами дешифратора 17, выходы которого соединены с входами данных регистра 18, выход инвертора 20 является вторым выходом 21 синхронизации устройства, группа выходов 22 данных блока приема данных является группой выходов данных устройства.

Временные диаграммы 23 и 24 (фиг.3) соответствуют сигналам на выходе 13 и входах 14 блока 8 (см. фиг.2); диаграмма 25 отображает сигналы в канале 7; диаграммы 26 и 27 соответствуют сигналам на выходах дешифратора 17; диаграммы 28 и 29 показывают сигналы на выходах 21 и 22 блока 9.

Предлагаемое устройство (фиг.4) содержит подключенные к противоположным сторонам канала связи 30 блок 31 передачи данных и блок 32 приема данных, блок 31 содержит генератор 33 синхросигналов, шифратор 34, группу выходных усилителей 35, выход генератора 33 является первым 36 выходом синхронизации устройства, группа 37 входов блока 31 является группой входов данных устройства, группа выходов шифратора 34 соединена с входами группы выходных усилителей 35, выходы которых соединены с витыми парами 38 проводов канала связи, блок 32 приема данных содержит группу входных усилителей 39, дешифратор 40, первый 41 регистр, элемент 42 задержки и инвертор 43, входы группы входных усилителей 39 соединены с витыми парами 38 проводов канала 30, а их выходы - с входами дешифратора 40, выходы которого соединены с входами данных регистра 41, выход инвертора 43 является вторым выходом 44 синхронизации устройства, группа выходов 45 блока 32 является группой выходов данных устройства.

Блок 31 передачи данных дополнительно содержит регистр 46, компаратор 47, первый 48 и второй 49 триггеры, группа входов 37 устройства соединена с первой группой входов компаратора 47 и с входами данных регистра 46, выходы которого соединены с входами шифратора 34 и с второй группой входов компаратора 47, выход которого соединен с входом данных триггера 48, выход единичного плеча которого соединен с входом шифратора 34 и с входом данных триггера 49, выход которого соединен с входом установки нуля триггера 48, выход нулевого плеча которого соединен с входом установки нуля триггера 49, выход генератора 33 соединен с входами синхронизации регистра 46, первого 48 и второго 49 триггеров.

Блок 32 приема данных дополнительно содержит второй 50 регистр, группу формирователей 51 импульсов, блок 52 фазовой автоподстройки частоты, элемент ИЛИ 53, элемент ИЛИ-НЕ 54, выходы дешифратора 40 соединены с входами группы формирователей 51 импульсов, выходы которых через элемент ИЛИ 53 соединены с входом блока 52 фазовой автоподстройки частоты, выход которого соединен с входом инвертора 43, с первым входом элемента ИЛИ-НЕ 54 и с входом синхронизации регистра 41, выход элемента ИЛИ-НЕ 54 соединен с входом синхронизации регистра 50, выходы регистра 41 соединены с входами данных регистра 50 и с входом элемента 42 задержки, выход которого соединен с вторым входом элемента ИЛИ-НЕ 54, выходы регистра 50 являются группой 45 выходов данных блока 32.

Временные диаграммы 55, 56 и 57 (фиг.5) отображают сигналы на входе синхронизации, входах данных и выходах регистра 46 (см. фиг.4); диаграммы 58 и 59 - сигналы на входе и выходе триггера 48; диаграмма 60 - сигнал на выходе триггера 49; диаграмма 61 - сигналы в канале 30; диаграммы 62 и 63 - сигналы на выходах дешифратора 40; диаграммы 64 и 65 - сигналы на входе и выходе блока 52; диаграммы 66 и 67 - сигналы на выходах регистра 41; диаграмма 68 - сигнал на выходе элемента ИЛИ-НЕ 54; диаграммы 69 и 70 - сигналы на выходах 45 и 44 блока 32.

В схеме, приведенной на фиг.1, трехразрядный параллельный код данных DIN (X Y Z) и сопровождающий его синхросигнал CIN передаются по витым парам 6 проводов канала 1 к удаленному абоненту. Напряжение между проводами витой пары 6 может быть отрицательным или положительным в зависимости от значения передаваемого бита (лог. 0 или 1). Выходной код данных DOUT (X Y Z) и принятый синхросигнал COUT совпадают с входными с точностью до задержек передачи.

Пересылка трехразрядного параллельного кода и синхросигнала может быть выполнена с использованием меньшего числа витых пар проводов [2], как показано на фиг.2.

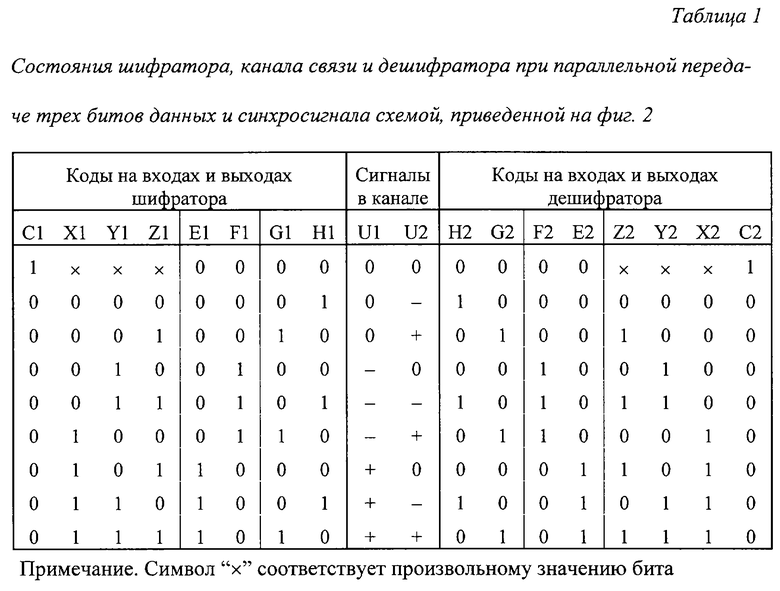

В этой схеме применено трехуровневое кодирование сигнала в канале. Напряжение U1 (U2) между проводами витой пары 15 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 12 в зависимости от сочетания битов E1 F1 (G1 H1) на его входах следующим образом. При Е1=F1=0 (G1=H1=0) напряжение U1 (U2) нулевое, при Е1= 0, F1=1 (G1=0, H1=1) - отрицательное, при Е1=1, F1=0 (G=1, H1=0) - положительное. Код E1 F1 G1 H1 формируется шифратором 11 из входного кода X1 Y1 Z1 C1 (данные, синхросигнал), как показано в левой части табл.1.

Входные усилители и дешифратор осуществляют обратное преобразование сигналов, представленных напряжениями U1 и U2 в витых парах проводов канала. В этом можно убедиться сопоставлением левой и правой частей табл.1 - они симметричны. В центральной части таблицы показаны девять возможных комбинаций сигналов в канале. Первая комбинация (00) произвольно выбрана для отображения единичного состояния синхросигнала. Символы "х" в левой части таблицы означают, что при С1=1 входные сигналы TхD не воспринимаются шифратором. Эти же символы в правой части таблицы показывают, что при выдаче синхросигнала С2 выходные данные Х2 Y2 Z2 не определены и не могут использоваться для выдачи абоненту. Остальные восемь комбинаций сигналов в канале произвольно распределены для отображения восьми состояний трехразрядного кода X1 Y1 Z1 при условии, что С1=0. Шифратор и дешифратор могут быть выполнены на основе ПЗУ, программируемой логики или построены из обычных логических элементов.

Из временных диаграмм, показанных на фиг.3, следует, что сигналы W, передаваемые по каналу 7, поочередно отображают синхросигнал С1 и данные (группу битов X1, Y1, Z1). Как отмечалось, группа выходных сигналов дешифратора 17 не определена при наличии синхросигнала. Этот факт отмечен затененными областями на временной диаграмме 27 группы Q сигналов Х2, Y2, Z2. Для устранения неопределенности этих сигналов применен параллельный регистр 18. Данные принимаются в него по положительному фронту сигнала С3, который формируется из сигнала С2 после его задержки на четверть периода синхросигнала и последующего инвертирования. В результате сигналы RхD и RхC с некоторой задержкой повторяют сигналы TхD и ТхС.

Данный способ уменьшения числа витых пар проводов канала связи применим и к схемам с большей разрядностью. При трехуровневом кодировании число состояний линии, содержащей N витых пар проводов, равно 3N. Одно из этих состояний следует выделить для кодирования синхросигнала. С помощью оставшихся 3N-1 состояний можно отобразить М-разрядный двоичный код TхD, где М= [log2(3N-1)], прямые скобки обозначают целую часть заключенного в них числа. Так, при N=2, 3, 4,..., 10 разрядность М передаваемого кода составляет 3, 4, 6, 7, 9, 11, 12, 14, 15.

Принцип действия предлагаемого устройства (см. фиг.4, 5) близок рассмотренному, но по каналу 30 передаются только коды данных и, если это необходимо, признаки повтора передаваемого кода. При этом гарантируется изменение состояния канала в каждом такте, что позволяет восстановить синхросигнал блоком приема данных. Таким образом, скорость передачи данных предлагаемым устройством удваивается по сравнению с прототипом [2] за счет исключения непосредственной пересылки кодированного синхросигнала по каналу связи.

Все процессы, протекающие при передаче данных предлагаемым устройством, синхронизируются сигналом ТхС от генератора 33. По положительному фронту этого сигнала источник данных (на чертежах не показан) формирует на входах 37 устройства очередной трехразрядный двоичный код Х0 Y0 Z0 передаваемых данных TхD (Х0 - старший разряд). В примере, приведенном на диаграммах 55 и 56 (см. фиг.5), от источника данных под управлением сигнала ТxС поступает такая последовательность кодов: 1012=5, 0112=3, 0012=1,..., 0112=3. При этом коды "6" и "4" повторяются в четырех и двух смежных тактах.

Регистр 46 принимает данные по положительному фронту сигнала ТхС, поэтому в этом регистре фиксируется "старый" код TхD, прежде чем на его входы поступит "новый" код. (По этой схеме построены обычные сдвиговые регистры с общей цепью синхронизации). В результате данные К на выходах регистра 46 формируются с задержкой на один такт по сравнению с данными TxD на его входах (см. диаграмму 57, повторяющую диаграмму 56 со сдвигом вправо на один период сигнала ТхС).

Компаратор 47 сравнивает старый код с новым. При совпадении кодов формируется сигнал J= 1 (диаграмма 58). Этот сигнал сдвигается на один такт и "прореживается", если его длительность превышает один период синхросигнала.

Результирующий сигнал W1, формируемый триггерами 48 и 49 (см. диаграммы 59 и 60), поступает на шифратор 34 вместе с данными и несет информацию о повторах кодов (6, 6, 6, 6 и 4, 4). Шифратор 34, усилители 35, 39 и дешифратор 40 выполняют преобразование кодов в соответствии с табл.2.

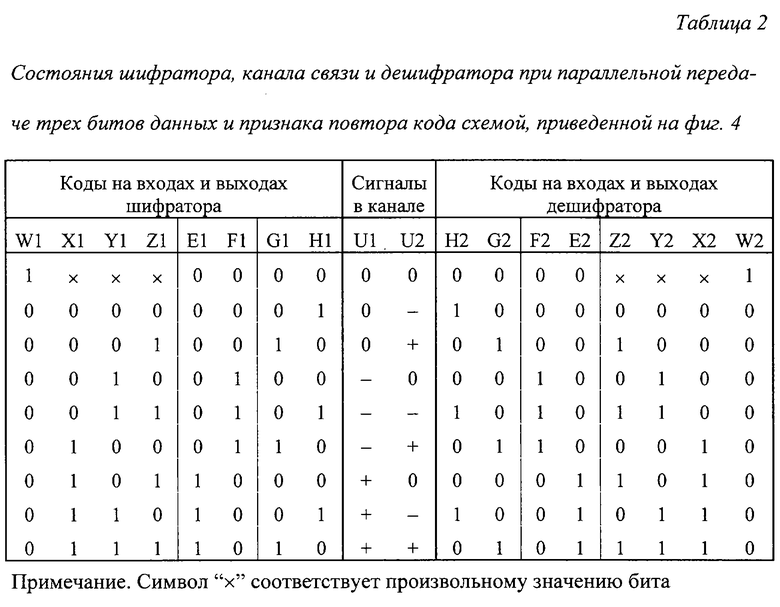

В предлагаемой схеме, так же, как и в прототипе, применено трехуровневое кодирование сигнала в линии. Напряжение U1 (U2) между проводами витой пары 38 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 35 в зависимости от сочетания битов E1 F1 (G1 H1) на его входах следующим образом. При Е1=F1=0 (G1=H1=0) напряжение U1 (U2) нулевое, при Е1=0, F1=1 (G1=0, H1=1) - отрицательное, при E1= 1, F1=0 (G=1, H1=0) - положительное. Код E1 Fl G1 H1 формируется шифратором 11 из входного кода X1 Y1 Z1 W1 (данные, признак повтора), как показано в левой части табл.2.

Входные усилители 39 и дешифратор 40 осуществляют обратное преобразование сигналов, представленных напряжениями U1 и U2 в витых парах проводов канала 30. В этом можно убедиться сопоставлением левой и правой частей табл. 2 - они симметричны. В центральной части таблицы показаны девять возможных комбинаций сигналов в канале. Первая комбинация (00) произвольно выбрана для отображения признака W1= 1 повтора кода данных. Символы "х" в левой части таблицы означают, что при W1=1 входные сигналы К не воспринимаются шифратором.

Эти же символы в правой части таблицы показывают, что при выдаче дешифратором признака W2=1 повтора кода выходные данные Х2 Y2 Z2 не определены и не могут использоваться для выдачи абоненту. Остальные восемь комбинаций сигналов в канале произвольно распределены для отображения восьми состояний трехразрядного кода X1 Y1 Z1 при условии, что W1=0. Шифратор и дешифратор могут быть выполнены на основе ПЗУ, программируемой логики или построены из обычных логических элементов.

Сигналы в канале связи (диаграмма 61) в каждом такте несут информацию о передаваемом трехразрядном коде либо о том, что в данном такте код повторяется. Сигналы М на выходе дешифратора (диаграмма 62) содержат области неопределенности, выделенные серым фоном; им соответствуют единичные состояния сигнала W2 (диаграмма 63). Так как признак повтора кодируется в канале уникальным сочетанием сигналов и не может длиться более одного такта (благодаря "прореживанию"), то создается гарантия того, что в каждом такте состояние канала изменяется, т.е. отлично от предыдущего. Для регистрации границ тактовых интервалов использованы формирователи 51 импульсов, элемент ИЛИ 53 и блок 52 фазовой автоподстройки частоты. Формирователи импульсов реагируют на любой фронт входного сигнала выдачей на входы элемента ИЛИ кратковременных сигналов лог. 1. Поэтому на выходе элемента ИЛИ формируется непрерывная последовательность импульсов, представленная на диаграмме 64.

Эта последовательность поступает на вход синхронизации блока 52 фазовой автоподстройки частоты. Блок 52 может быть выполнен по одной из известных схем (см., например, пат. США 6215835 В1). Он предназначен для формирования высокостабильного синхросигнала S на основе непрерывного слежения за входным сигналом Р. В данном примере отрицательный фронт сигнала S привязан к положительному фронту сигнала Р (см. диаграммы 65 и 64). Благодаря достаточной инерционности блока 52 сигнал S практически нечувствителен к "дрожанию фазы" сигнала Р и иным его кратковременным искажениям, вызванным помехами в канале связи. (Такое использование стандартного блока фазовой автоподстройки частоты в телекоммуникационных системах является общепринятым и далее не детализируется).

По положительному фронту сигнала S установившиеся на выходе дешифратора сигналы фиксируются в регистре 41 (см. диаграммы 66 и 67). Далее, если нет повтора, код из регистра 41 переписывается в регистр 50. При наличии повтора элемент ИЛИ-НЕ блокируется сигналом W3=1, незначительно задержанным элементом 42 (для предотвращения "гонок" сигналов). Поэтому сигнал CL синхронизации регистра 50 имеет форму, показанную на диаграмме 68.

Как следует из диаграммы 69, выходные данные RхD повторяют входные данные TхD с точностью до задержки передачи. При этом сигнал RхC (диаграмма 70) обеспечивает правильную синхронизацию данных RхD.

Предлагаемое устройство, так же, как и прототип, применимо и для передачи кодов большей разрядности. При трехуровневом кодировании число состояний линии, содержащей N витых пар проводов, равно 3N. Одно из этих состояний выделяется для кодирования признака повтора. С помощью оставшихся 3N-1 состояний можно отобразить М-разрядный двоичный код TхD, где М=[log2(3N-1)], прямые скобки обозначают целую часть заключенного в них числа. Так, при N=2, 3, 4,..., 10 разрядность М передаваемого кода составляет 3, 4, 6, 7, 9, 11, 12, 14, 15.

Применение предлагаемого устройства позволяет повысить скорость передачи данных в два раза по сравнению с прототипом.

Источники информации

1. Патент США 5160929, Fig. 1.

2. Патент США 5160929, Fig. 2 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214045C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ДЛИНЫ ДВУХПРОВОДНОЙ ЛИНИИ ПЕРЕДАЧИ ДАННЫХ | 2002 |

|

RU2233554C1 |

Изобретение относится к устройствам для кодирования - декодирования данных и может быть использовано в синхронных телекоммуникационных системах. Цель изобретения - повышение скорости передачи данных. Устройство содержит подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов является первым выходом синхронизации устройства, группа входов блока передачи данных является группой входов данных устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов канала связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и инвертор, группа выходов блока приема данных является группой выходов данных устройства. Повышение скорости передачи данных достигнуто благодаря применению схемы кодирования с гарантированным изменением состояния канальных сигналов в смежных тактах. 5 ил., 2 табл.

Устройство для кодирования - декодирования данных, содержащее подключенные к противоположным сторонам канала связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов является первым выходом синхронизации устройства, группа входов блока передачи данных является группой входов данных устройства, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов канала связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и инвертор, входы группы входных усилителей соединены с витыми парами проводов канала связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра, выход инвертора является вторым выходом синхронизации устройства, группа выходов данных блока приема данных является группой выходов данных устройства, отличающееся тем, что блок передачи данных дополнительно содержит регистр, компаратор, первый и второй триггеры, группа входов данных устройства соединена с первой группой входов компаратора и с входами данных регистра, выходы которого соединены с входами шифратора и с второй группой входов компаратора, выход которого соединен с входом данных первого триггера, выход единичного плеча которого соединен с входом шифратора и с входом данных второго триггера, выход которого соединен с входом установки нуля первого триггера, выход нулевого плеча которого соединен с входом установки нуля второго триггера, выход генератора синхросигналов соединен с входами синхронизации регистра, первого и второго триггеров, блок приема данных дополнительно содержит второй регистр, группу формирователей импульсов, блок фазовой автоподстройки частоты, элемент ИЛИ, элемент ИЛИ-НЕ, выходы дешифратора соединены с входами группы формирователей импульсов, выходы которых через элемент ИЛИ соединены с входом блока фазовой автоподстройки частоты, выход которого соединен с входом инвертора, с первым входом элемента ИЛИ-НЕ и с входом синхронизации первого регистра, выход элемента ИЛИ-НЕ соединен с входом синхронизации второго регистра, выходы первого регистра соединены с входами данных второго регистра и с входом элемента задержки, выход которого соединен с вторым входом элемента ИЛИ-НЕ, выходы второго регистра являются группой выходов данных блока приема данных.

| US 5160929 А, 03.11.1992 | |||

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| RU 2004943 С1, 15.12.1993 | |||

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА ВО МНОГОЗНАЧНЫЙ КОД (ВАРИАНТЫ) | 1997 |

|

RU2109400C1 |

| БИБЛИОТЕКА IК. И. Умрихин и А. А. Шахназаров'~°°~~~~~~~~—• .. ~=»J | 0 |

|

SU299639A1 |

Авторы

Даты

2003-10-10—Публикация

2002-01-22—Подача