Изобретение относится к области обработки цифровых данных, а именно к обработке данных в полупроводниковых запоминающих устройствах (памяти) и к архитектуре памяти, в частности к устройствам оперативной памяти (RAM), динамической памяти (DRAM), кэш-памяти и т.п.

Компьютерная система обычно включает центральный процессор для выполнения команд по заданным задачам и память для хранения данных, программ и т.п., запрашиваемых центральным процессором. Для улучшения характеристики компьютерной системы в основном стараются увеличить быстродействие центрального процессора, а также сделать время доступа к памяти как можно короче, так чтобы центральный процессор мог работать, по крайней мере, без состояний ожидания. Однако современное состояние в этой области характеризуется растущим разрывом между скоростью обработки данных в процессорах и быстродействием оперативной памяти, в частности, ограниченной шириной используемой шины. Можно уже говорить о том, что время выполнения однотактной команды центрального процессора на порядок и более меньше времени доступа к памяти вне кристалла [см. например: В.Корнеев. Параллельные вычислительные системы. М.: Нолидж, 1999]. Чтобы компенсировать разрыв между быстродействием центрального процессора и быстродействием памяти, используют различные технические решения.

Известно использование динамической памяти с произвольным доступом (DRAM), при этом передача данных между DRAM и центральным процессором осуществляется последовательными блоками информации или данных. При этом, например, известна полупроводниковая память, сформированная на полупроводниковом кристалле, с матрицей памяти, разделенной на два банка, состоящих из верхней и нижней матрицы ячеек памяти [патент RU 2156506, опубл. 20.09.2000]. Между первым и вторым банками памяти установлено устройство управления, предназначенное для генерирования управляющих сигналов, а также устройствами выбора шин. Однако такое решение позволяет только минимизировать время состояние ожидания центрального процессора.

Известно применение для увеличения быстродействия оптимизации систем для обработки запросов на доступ к шине, например, известна система, переключающая микропроцессор в состояние прерывания в ответ на запрашивающий прерывание сигнал и соединяющий микропроцессор с локальной шиной центрального процессорного устройства на предопределенный минимальный период времени [патент RU 2067314, опубл. 27.09.1996]. Использование в системе шины адреса не позволяет значительно увеличить быстродействие системы.

Известно применение для увеличения быстродействия ЭВМ многопроцессорных систем построения ЭВМ. Например, известны система и способ назначения шины данных для процессоров с цифровой обработкой сигнала [заявка PCT/GB 95/02130, публикация WO 9608774 от 21.03.1996]. Известная система включает множество процессоров, общую шину к ресурсу, который используется процессорами совместно. Каждый процессор может содержать внутреннюю память, так что он обладает возможностью выполнения команд без назначения ему шины, при этом каждый процессор может содержать регистры, что также позволяет ему выполнять команды без назначения шины. Быстродействие такой системы также сдерживается шириной шины и наличием шины адреса.

Известно использование для повышения быстродействия однонаправленных шин. В качестве прототипа выбрано одно из таких технических решений, а именно известная интегральная микросхема, содержащая запоминающее устройство данных, и способ обработки данных в такой интегральной микросхеме [патент RU 2137186, опубл. 10.09.1999]. Интегральная микросхема содержит центральный процессор, соединенный однонаправленной шиной считывания и однонаправленной шиной записи и адреса с памятью данных (например, кэш, ЗУПВ или диск) в виде кэш-памяти, содержащей матрицу запоминающих ячеек. Шина считывания и шина записи и адреса формируются только в одном направлении. При этом технический результат заключается в устранении потерь времени за счет изменения направления на обратное прохождение сигнала по шине. Слова считывания данных и командно-информационные слова передаются из кэш-памяти в сердечник центрального процессора по шине считывания. Командно-адресные слова, слова считывания адреса, записи адреса и записи данных мультиплексируются с временным разделением на шине записи и адреса для поступления из сердечника в кэш-память. Техническое решение обеспечивает передачу в пакетном режиме, тем самым уменьшая число адресов, которые нужно передавать на шину записи и адреса, освобождая пропускную способность на этой шине для использования слов записи данных. Наличие шины адреса также сдерживает быстродействие известной системы. Кроме того, эта система имеет ограниченное использование для специфических устройств.

Решаемая техническая задача - повышение быстродействия обработки цифровых данных в компьютерной системе.

Предлагается способ обработки цифровых данных в запоминающем устройстве, включающей операции записи и считывания цифровых данных в ячейках памяти запоминающего устройства центральным процессором через систему шин по командам центрального процессора, а также операции управления записью и считыванием цифровых данных. Новым является то, что часть операций управления осуществляют независимо от центрального процессора в самом запоминающем устройстве, при этом одновременно или последовательно в нескольких ячейках памяти выполняют одну или несколько из следующих операции управления: установка битового режима, при котором операцию записи или считывания выполняют над одной ячейкой памяти; установка режима потока, при котором операцию записи или считывания одновременно выполняют над группой ячеек; поиск имени цифровых данных; передача указателя следующему потоку для приема новой порции имени цифровых данных от центрального процессора; передача указателя следующему потоку для приема конца имени цифровых данных от центрального процессора; передача указателя предыдущему или следующему потоку для чтения цифровых данных центральным процессором; перевод указателя назад или вперед для инициализации цифровых данных; передача указателя предыдущему или следующему потоку для записи цифровых данных с центрального процессора; передача указателя предыдущему или следующему потоку для проверки состояния ячейки памяти; передача указателя предыдущему или следующему потоку для сравнения; потеря указателя; выполнение команды центрального процессора.

В каждую ячейку памяти можно дополнительно записывать цифровые данные из группы: признак начала и/или конца имени потока; признак состояния ячейки памяти; признак операции, выполняемой ячейкой памяти; признак шины данных, к которой следует подключать ячейку памяти.

Для осуществления способа предлагается запоминающее устройство (память) в виде полупроводникового устройства памяти, содержащей ячейки памяти, выполненные с возможностью подключения к системе шин для соединения с центральным процессором. Новым является то, что память дополнительно включает блок управления с элементами управления, а каждая ячейка памяти содержит встроенный микропроцессор, включающий регистры, выполненные с возможностью хранения признаков начала имени потока данных и его конца, информации о состоянии и режиме работы встроенного микропроцессора, при этом блок управления выполнен с возможностью управления обработкой информации в ячейках памяти, а ячейки памяти выполнены с возможностью подключения к шине данных и шине управления, включающей линии управления прерыванием. Естественно, что физически шина прерывания может быть выполнена отдельно, в этом случае ячейки памяти выполнены с возможностью подключения к шине данных и как к шине управления, так и к шине прерывания.

Встроенный микропроцессор может включать в себя следующие регистры:

- регистр хранения признака начала имени потока цифровых данных;

- регистр хранения признака конца имени потока цифровых данных;

- один или несколько регистров состояния встроенного микропроцессора;

- один или несколько регистров режима работы встроенного микропроцессора, при этом как число регистров состояния, так и число регистров режима работы равно числу одновременно доступных потоков. При этом встроенный микропроцессор также может включать регистр хранения информации о линии шины данных, к которой следует подключаться ячейке памяти.

Блок управления может содержать линию управления, последовательно соединяющую встроенные микропроцессоры (например, через их регистры) с помощью встроенных между соседними ячейками памяти ключей. При этом линию управления лучше выполнять однонаправленной.

Блок управления может содержать элементы управления в виде узлов сравнения, которые включают элементы И, хотя бы по одному элементу И на каждую ячейку памяти, при этом первый вход каждого элемента И выполнен с возможностью подключения только к одной определенной ячейке памяти, второй вход каждого элемента И выполнен с возможностью подключения к шине данных, а выход каждого элемента И имеет возможность подключения к ключу между указанной ячейкой памяти и смежной с ней вдоль линии управления ячейкой памяти. При этом узлы сравнения могут быть подключены к источнику питания.

Ключи могут быть выполнены на базе транзисторов, которые могут быть встроены в линию управления с помощью эмиттера и коллектора, а базы транзисторов при этом соединены с управляющими устройствами блока управления и/или встроенными микропроцессорами.

Ячейки памяти могут быть выполнены с возможностью подключения:

- к одной шине данных и одной шине управления;

- к одной шине данных и двум или более шинам управления;

- к двум или более шинам данных и к такому же количеству шин управления.

Память со всеми входящими в нее элементами можно выполнять в виде отдельной интегральной микросхемы, при этом такую интегральную микросхему лучше оснастить устройством охлаждения (например, вентилятором).

Изобретение поясняется графическими материалами.

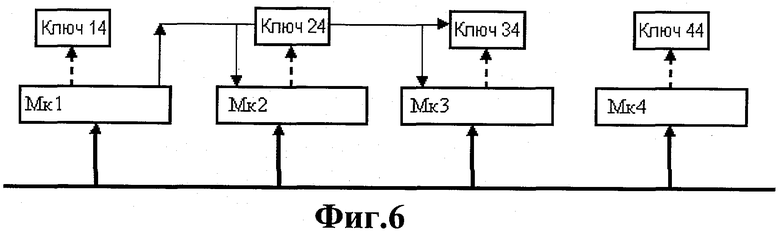

На фиг.1 представлена принципиальная схема памяти. Стрелками показано направление передачи данных (сигналов).

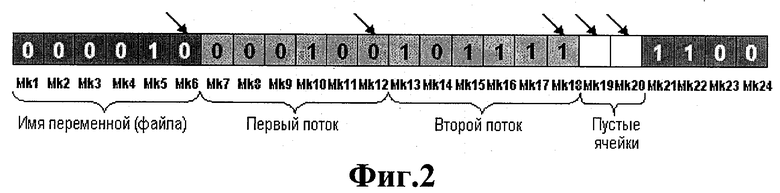

На фиг.2 представлен чертеж, поясняющий принцип хранения данных в ячейках памяти. Наклонными стрелками, направленными вниз, отмечены ячейки памяти, в регистрах "Стоп" которых записано "Истина".

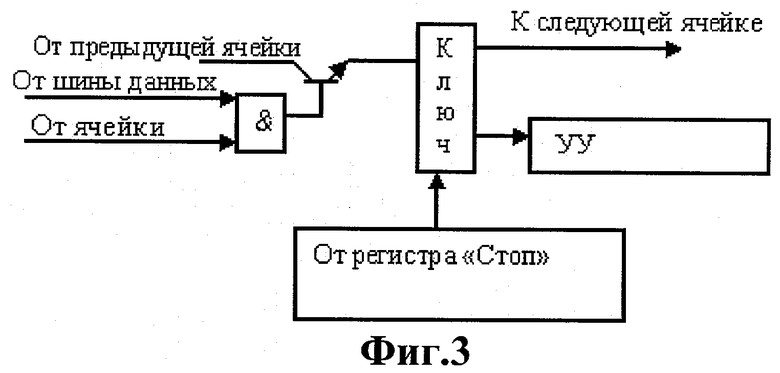

На фиг.3 представлен схематично принцип работы узла сравнения. Здесь применяются следующие обозначения: & - логический элемент И; УУ - устройство управления. Стрелками показано направление передачи данных (сигналов).

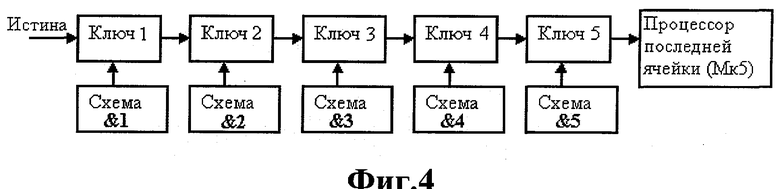

На Фиг.4 проиллюстрирована передача сигнала по линии управления, где также обозначено & - логический элемент И. Стрелками показано направление передачи данных (сигналов).

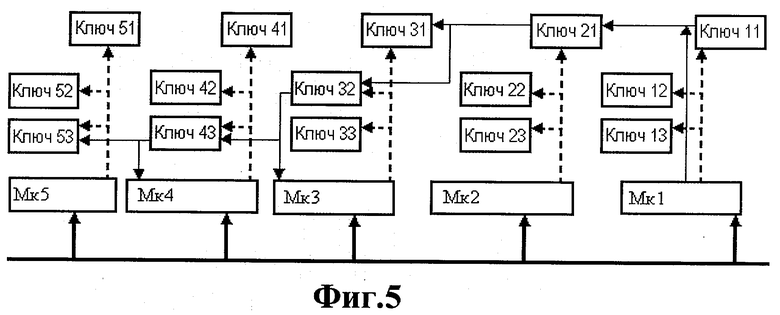

На фиг.5 проиллюстрировано осуществление операции передачи указателя. Стрелками показан путь прохождения сигналов, при этом стрелки выполнены следующими линиями: сигнал «Прими указатель» - сплошной тонкой линией; сигнал управления ключами - пунктирной линией; сигнал «Передача указателя» - сплошной основной линией.

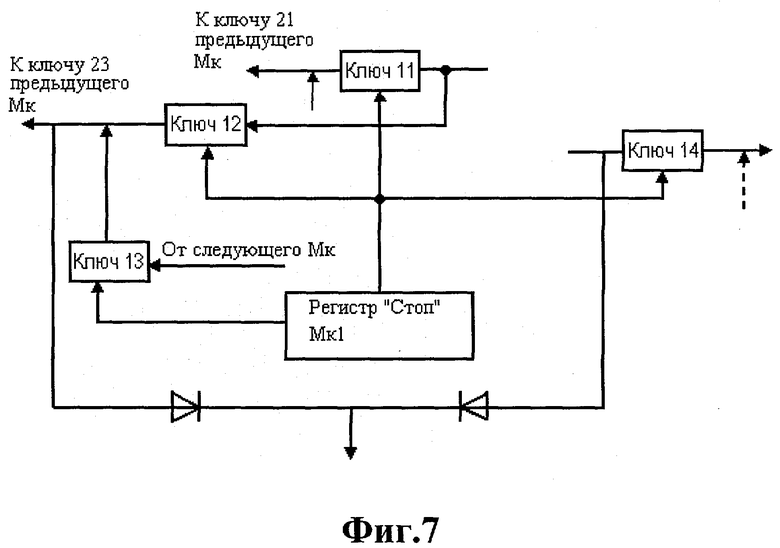

На фиг.6 проиллюстрировано осуществление операции передачи указателя следующему потоку. Характер линий стрелок тот же, как описано для фиг.5.

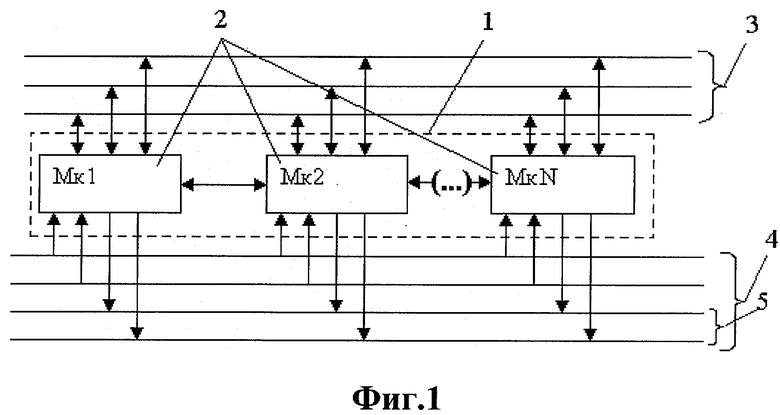

На фиг.7 представлена примерная схема компоновки узла передачи указателя. Здесь стрелкой, выполненной сплошной тонкой линией, показан участок линии управления, в которую необходимо подавать сигнал для перевода указателя к предыдущему потоку; стрелкой, выполненной пунктирной линией, - участок линии управления, в которую необходимо подавать сигнал для перевода указателя к следующему потоку; а стрелкой, выполненной сплошной основной линией, - сигнал «Прими указатель».

В общем виде (см. фиг.1) предлагаемое запоминающее устройство 1 (далее - память) 1 включает N ячеек памяти 2 (далее - ячейка) со встроенными микропроцессорами Мк1-МкN, последовательно подключенными к шине данных 3 и шине управления 4, включающей линии управления прерыванием 5, для соединения с центральным процессором (далее - ЦП; не показан). Шина адреса отсутствует, благодаря чему, во-первых, отпадает необходимость увеличения разрядности шины адреса, применяемое для «классических» архитектур для увеличения объема памяти, поэтому имеется возможность увеличивать объем памяти 1 практически неограниченно; во-вторых, процесс считывания цифровых данных (далее - данные) осуществляется проще, как будет показано ниже, что увеличивает скорость считывания.

Так как в предлагаемой архитектуре шина адреса отсутствует, то ячейка 2 сама определяет, какие операции выполнять с помощью своего встроенного микропроцессора Мк при получении сигналов от центрального процессора или нескольких центральных процессоров. Встроенный микропроцессор Мк каждой ячейки 2 содержит ряд регистров (не показаны), в общем случае число которых зависит от того, к скольким потокам данных он одновременно может получить доступ. Для организации доступа к одному потоку необходимы: один регистр для хранения признака начала имени потока данных - регистр "Имя"; один регистр для хранения признака конца имени потока данных - регистр "Стоп"; один регистр для хранения информации, свидетельствующей о состоянии, в котором находится микропроцессор, - регистр "Указатель"; один регистр, в котором будет храниться информация о том, к какой линии в шине данных 3 при передаче данных должна подключаться ячейка 2, - регистр "Линия" (это сделано для того, чтобы архитектура памяти, созданная для 64-битных систем могла успешно работать и в 16-битных системах); один регистр для хранения информации о режиме работы встроенного микропроцессора - регистр "Режим". Разумеется, имеется собственно ячейка 2, в которой будет храниться необходимая информация. При нескольких одновременно доступных потоках количество регистров увеличивается на два для каждого дополнительного потока путем прибавления дополнительного регистра "Указатель" и дополнительного регистра "Режим" на каждый дополнительный поток.

Каждый встроенный микропроцессор Мк может независимо выполнять следующие команды:

- установить битовый режим - код 00001;

- установить потоковый режим - код 00010;

- поиск имени - код 00011;

- передать указатель следующему потоку для приема новой порции имени - код 00100;

- передать указатель следующему потоку для приема конца имени - код 00101;

- передать указатель предыдущему потоку для чтения данных - код 00110;

- передать указатель следующему потоку для чтения данных - код 00111;

- перевести указатель назад для инициализации - код 01000;

- перевести указатель вперед для инициализации - код 01001;

- передать указатель предыдущему потоку для записи данных - код 01010;

- передать указатель следующему потоку для записи данных - код 01011;

- передать указатель предыдущему потоку для проверки состояния - код 01100;

- передать указатель следующему потоку для проверки состояния - код 01101;

- передать указатель предыдущему потоку для сравнения - код 01110;

- передать указатель следующему потоку для сравнения - код 01111;

- потеря указателя - код 10000;

- выполнить команду - код 10001.

Рассмотрим принцип работы памяти 1 с предлагаемой архитектурой, для чего проследим процесс выполнения вышеописанных команд. Заранее примем условие - имеется один ЦП, и он может получить одновременно доступ только к одному потоку данных.

Первые две команды устанавливают режим работы. В битовом режиме операции производятся только над одной ячейкой 2, такой режим эффективен, когда нужно изменить какой-нибудь бит в потоке. В потоковом режиме операции выполняются над целой группой ячеек памяти 2 одновременно; его введение связано с необходимостью увеличения производительности ЭВМ при считывании или записи больших объемов данных. Величина потока (количество одновременно обрабатываемых ячеек памяти) определяется в процессе инициализации, но не может быть больше, чем количество линий в шине данных 3. Переход от одного режима к другому можно осуществлять в любое время. При этом, если был потоковый режим, а перешли в битовый режим, указатель становится на первую ячейку 2 того потока, который был активным. Если осуществляется переход от битового режима к потоковому режиму, то возможны варианты:

а) потоки не были созданы (в эту область памяти еще нечего не записывалось); в этом случае возможна как потеря информации, т.к. память будет принимать данные все равно по одной ячейке 2 (биту), а ЦП - передавать как целый поток (байтами), так и искажение, когда память выдает сигнал на одну линию, при этом ЦП считывает со всех линий шины данных 3; чтобы всего этого не произошло, необходимо проверять, в каком состоянии находится ячейка 2 отдельной командой;

б) потоки существуют; в этом случае активным становится весь поток, которому принадлежала бы эта ячейка 2.

Подробнее остановимся на понятии потока. Схематично хранящиеся в памяти данные представлены на фиг.2, где каждая изображенная клетка представляет собой ячейку 2 со встроенными микропроцессорами Мк1-Мк24. Более темные клетки со значением «0» или «1» внутри - это ячейки 2, хранящие имя переменной (чем больше переменных может одновременно храниться в памяти, тем больше ячеек 2 необходимо отвести для хранения имени). Более светлые клетки со значением «0» или «1» внутри - это ячейки 2, хранящие значение переменной. Белые клетки - это пустые ячейки. Т.о. изображенная на фиг.2 переменная представлена тремя потоками: в первый поток входят ячейки, пронумерованные снизу с Мк1 до Мк6 включительно; во второй поток входят ячейки с Мк7 до Мк12; в третий поток входят ячейки с Мк13 до Мк18. В общем случае ячейки Мк19 и Мк20 тоже представляют собой потоки. Ячейки Мк21-Мк24 являются частью имени следующей переменной (следующего потока).

Поясним выполнение команды "Поиск имени" для потокового режима, когда в память 1 записана переменная А (см. фиг.фиг.1, 3 и 4).

Итак, когда ЦП необходимо получить значение переменной А, он выставляет на шину управления 4 команду "Поиск имени", при получении которой к шине данных 3 подключаются по одному из входов элемента И, но лишь тех ячеек 2, которые имеют признак "Начало имени". Одновременно с этим в регистры «Указатель» этих ячеек 2 записывается значение "истина", а на линии управления прерыванием выставляется сигнал с кодом "00001", свидетельствующий о том, что в памяти 1 обнаружены имена файлов либо переменных (и имеет смысл проводить поиск). Вторые входы элементов И подключаются собственно к ячейкам 2. После этого ЦП подает на шину управления 4 команду с кодом «10000», а на шину данных 3 - первую часть имени. Если сигнал, поступивший с шины данных 3, соответствует сигналу, записанному в ячейках памяти 2, то на входе устройства управления (далее - УУ) последней ячейки 2 активного потока появляется сигнал «истина» иначе «ложь». Это происходит следующим образом. Элементы И управляют ключами, которые включены в линию управления, в начало которой подан сигнал «истина» как показано на фиг.4. УУ обрабатывает эту информацию следующим образом: если на его вход поступил сигнал "ложь", то генерируется сигнал, по которому все ячейки этого потока записывают «ложь» в свои регистры "Указатель", а на линии управления прерыванием 5 перестают поступать какие-либо сигналы; если - "истина", то возможны два пути, а именно, ЦП подаст сигнал с кодом "00100" либо "00101". При поступлении сигнала с кодом «00100» активным станет следующий поток, а ячейки 2 этого потока станут ждать, когда ЦП подаст сигнал, разрешающий произвести сравнение информации, поступившей на шину данных, с информацией, которую они хранят. При поступлении сигнала с кодом «00101» все произойдет почти так же, как и при поступлении сигнала с кодом «00100», за исключением одного - по завершении операции на линии управления прерыванием 5 будет выдан сигнал с кодом «00010», свидетельствующий о том, что переменная с таким именем найдена.

Итак, на запрос ЦП, хранится ли в памяти 1 переменная с именем "А", ЦП получил утвердительный ответ. Теперь для того, чтобы получить значение этой переменной, ЦП подает команду с кодом "00111", при получении которой активным станет следующий поток, а ячейки 2 подключатся к шине данных 3 (каждая ячейка подключится именно к своей линии в шине данных 3) уже не через элемент И, а непосредственно. После такого подключения ЦП останется только подать команду с кодом «10001», чтобы произошла операция считывания. Если значение переменной занимает в памяти, к примеру, 32 бита, а считывание идет потоками по 8 бит, то для того, чтобы прочитать следующую порцию, ЦП передает последовательно команды "00111" и "10001". Следует отметить, что ЦП не требуется знать, сколько бит занимает в памяти 1 информация о значении переменной "А" для того, чтобы ЦП считал информацию о значении переменной со всех ячеек, просто после считывания последнего потока на линии управления прерыванием 5 генерируется сигнал с кодом "00011", свидетельствующий о том, что достигнут конец переменной (файла). Это происходит следующим образом: если при очередной попытке чтения, а именно после выполнения команды "00111", указатель переместится на ячейку, в которой хранится имя переменной В, то произойдет генерация сигнала последней ячейкой 2 первого потока, которая и выдаст этот сигнал на линию управления прерыванием; если при очередной попытке чтения, а именно после выполнения команды "00111", указатель переместится на ячейку 2, не содержащую данных, то ее УУ также генерирует сигнал "00011" на линию управления прерыванием. Хранение переменной частями при этом недопустимо.

Рассмотрим, как происходит процесс сравнения имени переменной с именем, передаваемым по шине данных 3.

Для этого, как уже отмечалось выше, информация из ячейки 2 поступает в узел сравнения, реализованный на элементе И, туда же поступает информация с соответствующей линии шины данных 3 (см. фиг.3). Узел сравнения управляет ключом, который открыт, если в ходе операции получен результат «истина», и закрыт, если - «ложь». Линия управления, в которую вмонтирован ключ, в зависимости от того, что записано в регистре «Стоп», может подключиться либо к своему встроенному микропроцессору Мк (когда «истина») или к выходу, обозначенному на фиг.3 как «От предыдущей ячейки», если там записан сигнал «Ложь». Причем, если происходит подключение к своему встроенному микропроцессору Мк, то на выход «От предыдущей ячейки» автоматически подается сигнал «Истина». Подключение достигается тем, что в линию управления встроен элемент «Ключи», который реализован на двух транзисторах. Переключение ключа осуществляется автоматически при изменении информации в соответствующем регистре. Кроме того, независимо от того, имеет ли ячейка 2 указатель или нет, хранит ячейка 2 какую-либо информацию или нет, на узел сравнения подается питание - это сделано для того, чтобы на линии всегда был высокий потенциал сигнала «истина». Как видно из схемы на фиг.4 для примера пакета информации из пяти ячеек 2, сигнал «истина» достигнет последнего встроенного микропроцессора Мк5 лишь тогда, когда все ключи будут открыты, т.е. информация, переданная по шине данных 3, совпадет с информацией, хранящейся в ячейках памяти 2. Встроенный микропроцессор Мк5 получит право обработать эту информацию, т.к. у него в регистре записана «истина». Характер обработки был показан выше.

Рассмотрим, как реализован процесс передачи указателя между пятью ячейками 2 (см. фиг.5). При подаче команд с кодами от «00100» до «01111» каждая ячейка 2 из активного потока, во-первых, проверяет, записан ли в регистре «Стоп» сигнал «истина», и если да, то встроенный микропроцессор Мк1 с такой записью выставляет на одну из шин устройства управления сигнал «Прими указатель» (в зависимости от того, в какую сторону передавать указатель, например, на фиг.5 передача идет предыдущему потоку), после чего заносит в регистр «Указатель» сигнал «ложь». Если такой записи в этом регистре нет, то встроенный микропроцессор Мк2 заносит в регистр «Указатель» сигнал «ложь» (указатель теряется сразу). Встроенные микропроцессоры Мк3 и Мк4, наоборот, заносят в свои регистры «Указатель» сигнал «истина», т.к. они получили сигнал «Прими указатель». Режим работы ключей зависит от информации, хранящейся в регистре «Стоп» и в общем случае для пяти ячеек 2, является следующим: при сигнале «истина» с регистрах «Стоп», соответствующих встроенных микропроцессоров Мк1-Мк-5, ключи 11, 21, 31, 41 и 51 закрыты, а при сигнале «ложь» в этих регистрах - открыты; при сигнале «истина» в регистрах «Стоп» ключи 12, 22, 32, 42 и 52 открыты, а при сигнале «ложь» в этих регистрах - закрыты; при сигнале «истина» в регистрах «Стоп» ключи 13, 23, 33, 43 и 53 закрыты, а при сигнале «ложь» в этих регистрах - открыты. Применительно к фиг.5 состояние ключей следующее: ключи 11, 31, 51, 13, 33, 53, 22 и 42 - закрыты; ключи 12, 21, 23, 32, 41, 43 и 52 - открыты.

Передача указателя следующему потоку реализуется проще, чем описано выше (см. фиг.6), т.к. за встроенным микропроцессором Мк, хранящим последний бит активного потока (именно он генерирует сигнал «Прими указатель»), сразу располагаются встроенные микропроцессоры, которым необходимо передать указатель. Поэтому для каждого встроенного микропроцессора Мк необходим всего один ключ, состояние которого определяется данными, хранящимися в регистре «Стоп». Если в регистре «Стоп» записан сигнал «истина», то ключ закрыт, в противном случае - ключ открыт. На фиг.6 показано, что встроенные микропроцессоры Мк1 и Мк3 хранят последний бит потока, однако встроенный микропроцессор Мк1 - активного потока, поэтому генерирует сигнал «Прими указатель», а Мк3 - пассивного потока, поэтому его ключ 34 закрыт, благодаря чему сигнал не проходит дальше. Вариант выполнения компоновки узла передачи указателя показан на фиг.7.

Рассмотрим, как происходит процесс инициализации (разметки). Сразу заметим, что при подаче питания на ячейки 2 в их регистры «Стоп» сразу записывается сигнал «Истина», причем это осуществляют сами встроенные микропроцессоры Мк1-МкN, а не ЦП. Предположим, что в памяти 1 уже были размещены некоторые данные и возникла необходимость произвести размещение в памяти некоторой переменной. Процесс поиска места в общем случае сводится к простому переводу указателя от одной ячейки 2 к другой, проверке ее состояния (хранит информацию или хранит имя переменной или пустая) и подсчету последовательно расположенных пустых ячеек 2. Наконец, найдено место для размещения переменной и указатель установлен на первой ячейке 2, далее эта ячейка, получив команду с кодом «01000» или «01001», подключит к шине данных 3 все регистры в заранее установленном порядке, к примеру: к первой линии - регистр «Имя»; ко второй линии - регистр «Стоп»; к третьей линии - собственно ячейку памяти 2; к остальным линиям - регистр «Линия». Благодаря такому одновременному подключению инициализация произойдет за один цикл.

Рассмотрим возможные аспекты программирования ЭВМ, построенных с использованием предлагаемого способа и запоминающего устройства. При программировании необходимо учитывать тот факт, что из-за практически неограниченного объема памяти в нее можно будет записывать огромное количество переменных, констант, файлов и тому подобной информации. Однако запуск одновременно двух одинаковых программ имеет свои особенности, т.к. возникнет необходимость работы с одинаковыми переменными (хотя записать две переменные с одинаковыми именами можно, но при их считывании могут возникнуть проблемы). Решить эту проблему можно, написав программу, которая будет проверять - не запущена в данный момент такая же программа, и если да, то эта программа должна поменять имена переменных, констант или файлов таким образом, чтобы при выполнении программ в памяти не нашлось бы двух переменных с одинаковыми именами, после чего бы компилировала программу и запускала новую версию программы.

С использованием предлагаемого технического решения возможно конструирование ЭВМ, содержащих:

1) Одну шину передачи данных и одну шину управления. Применение ЭВМ, построенной по такой технологии в промышленности (например, станки с ЧПУ), даст высокий экономический эффект, т.к. в силу особенностей там не требуется высокое быстродействие, и будет достигнута низкая цена производства данного рода ЭВМ, а следовательно, и промышленного оборудования на их основе.

2) Одну шину передачи данных и несколько шин управления. Данная схема с успехом может применяться в бытовой электронике. Отличительной особенностью является более высокая скорость работы ЭВМ по сравнению с первым вариантом.

3) Несколько шин передачи данных и такое же количество шин управления (многопроцессорные ЭВМ). Данная схема отличается высокой скоростью вычислений. Основное применение таких ЭВМ - серверы.

Рассмотрим особенности применения предлагаемого технического решения в многопроцессорных ЭВМ. Одна из основных решаемых проблем - как обеспечить максимальную скорость записи-считывания при обращении двух или более центральных процессоров к одному и тому же потоку (ячейке). Для этого на программном уровне возможно внесение в список команд встроенного микропроцессора Мк ячейки памяти 2 команды, обеспечивающие обработку вышеописанной ситуации. При этом, если к ячейке 2 одновременно обратятся хотя бы два центральных процессора ЦП1 и ЦП2, причем у ЦП1 более высокий приоритет и он подключен к шине №1, то ячейка 2 выдаст на шину прерываний №1 (линию прерываний) сигнал с кодом «00100», а шину данных №2 либо отключит, предварительно подав на ее шину прерываний сигнал «00101» (если ЦП1 затребовал запись или процессор ЦП1 затребовал считывание, а процессор №2 запись), либо оставит подключенной (если ЦП1 затребовал считывание и ЦП2 также затребовал считывание), но также подав при этом на шину прерываний №2 сигнал «00101». С приходом сигнала «00100» ЦП1, сгенерировав сигнал «10001», сможет произвести требуемую операцию в любой момент. Поступление же сигнала с кодом «00101» означает, что ЦП должен ожидать, либо когда ЦП с более старшим приоритетом произведет свои операции, либо когда поступят данные (при считывании), либо перевести указатель. Разумеется, что ЦП должны поддерживать вышеизложенные принципы работы. Таким образом, в первую очередь будут обрабатываться команды ЦП, имеющего наибольший приоритет из обратившихся, но при совпадении запрошенных действий ЦП с наименьшими приоритетами могут получить данные (исключение представляет команда записи и инициализации). После выполнения операций ЦП с наибольшим приоритетом ячейка 2 определит, у кого из оставшихся ЦП (если таковые остались) имеется наибольший уровень допуска, и будет обрабатывать его команды.

Безусловно, что при работе предлагаемого запоминающего устройства увеличится энергопотребление и для интегральной микросхемы, на которой реализовано запоминающее устройство, потребуется принудительное охлаждение, например, с помощью вентилятора. Однако эти недостатки будут в значительной степени компенсированы значительным увеличением быстродействия ЭВМ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительная система | 1977 |

|

SU692400A1 |

| ПОЛУПРОВОДНИКОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1997 |

|

RU2169951C2 |

| МУЛЬТИПРОЦЕССОРНАЯ АРХИТЕКТУРА, ОПТИМИЗИРОВАННАЯ ДЛЯ ПОТОКОВ | 2008 |

|

RU2450339C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| УПРАВЛЕНИЕ СКОРОСТЬЮ, С КОТОРОЙ ОБРАБАТЫВАЮТСЯ ЗАПРОСЫ НА ПРЕРЫВАНИЕ, ФОРМИРУЕМЫЕ АДАПТЕРАМИ | 2010 |

|

RU2526287C2 |

| ИЗМЕРИТЕЛЬНОЕ СРЕДСТВО ДЛЯ ФУНКЦИЙ АДАПТЕРА | 2010 |

|

RU2523194C2 |

| УСТРОЙСТВО В ПРИЕМНИКЕ ДЛЯ ОБРАБОТКИ ЗАПИСАННЫХ ИЛИ ПЕРЕДАВАЕМЫХ АУДИОКОМПОНЕНТ, ВИДЕОКОМПОНЕНТ И КОМПОНЕНТ ДАННЫХ СИГНАЛА ПРОГРАММЫ | 1995 |

|

RU2154353C2 |

| АКТИВАЦИЯ/ДЕАКТИВАЦИЯ АДАПТЕРОВ ВЫЧИСЛИТЕЛЬНОЙ СРЕДЫ | 2010 |

|

RU2562372C2 |

| СПОСОБ ОБЕСПЕЧЕНИЯ СВЯЗИ В КОММУНИКАЦИОННОЙ СРЕДЕ, КОМПЬЮТЕРНАЯ СИСТЕМА И ЭНЕРГОНЕЗАВИСИМЫЙ МАШИНОЧИТАЕМЫЙ НОСИТЕЛЬ ДАННЫХ | 2012 |

|

RU2574815C2 |

| УСТРОЙСТВО И СПОСОБ УПРОЩЕННОЙ ЗАПИСИ И ВОСПРОИЗВЕДЕНИЯ АНАЛОГОВОГО СИГНАЛА | 1998 |

|

RU2204176C2 |

Изобретение относится к области обработки цифровых данных, в частности, к обработке данных в полупроводниковых запоминающих устройствах (памяти) и к архитектуре памяти, в частности, к устройствам оперативной памяти (RAM), динамической памяти (DRAM), кэш-памяти и т.п. Техническим результатом является повышение быстродействия обработки цифровых данных в компьютерной системе. Запоминающее устройство в виде полупроводникового устройства памяти содержит блок управления с элементами управления и ячейки памяти, каждая из которых выполнена с возможностью подключения к системе шин для соединения с центральным процессором и содержит встроенный микропроцессор, включающий регистры, выполненные с возможностью хранения признаков начала имени потока данных и его конца, информации о состоянии и режиме встроенного микропроцессора. Способ описывает процесс обработки данных в указанном запоминающем устройстве. 5 з.п. ф-лы, 7 ил.

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ДАННЫХ И ШИНА ПРОЦЕССОРА | 1994 |

|

RU2137186C1 |

Авторы

Даты

2005-11-10—Публикация

2004-02-02—Подача