Область техники

Данное изобретение относится к области технологии изготовления высококачественных электронных компонентов в части проведения испытаний, включая их электротермотренировку (ЭТТ) и контроль, а конкретно - к способу испытаний и контроля электронных компонентов.

Уровень техники

Общеизвестно, что при производстве электронных компонентов для обеспечения высоких показателей надежности прибегают к различным типам их испытаний, включая электротермотренировку (ЭТТ) перед установкой в электронную аппаратуру (см., например, "Конструирование и расчет БГИС, микросборок и аппаратуры на их основе", под ред. Б.Ф.Высоцкого, с.189, М., Радио и связь, 1981). После 168-часовой ЭТТ обнаруживается до 98,5% потенциально бракованных компонентов.

Известно техническое решение по патенту США 5640752 от 24 июня 1997 г., Н 05 К 3/30 "Метод и аппаратура для производства гарантированно годного кристалла".

Представляется метод и аппаратура для производства гарантированно годного кристалла, включающий следующие шаги: тестирование годности кристалла на пластине, расчленение пластины на единичные кристаллы, а затем тестирование кристалла путем сборки носителя, имеющего межсоединения, приспособленные для электрического соединения между контактными площадками на кристалле и внешними тестирующими устройствами. Во время сборки носителя кристалл и межсоединения оптически совмещаются и входят в контакт с определенной контактной силой. В собранном носителе кристалл и межсоединения сочленяются вместе с помощью механизма распределения силы, который включает в себя выгнутую скобу, пластину для надавливания и пружинный зажим. Контактирование с кристаллом происходит через кремниевую пластину, на которой сформированы заостренные выступы, врезающиеся в контактные площадки кристалла. В сочлененном виде кристалл и носитель подвергаются тренировке и контролю, после чего носитель разбирается и тестированный кристалл удаляется.

Данный метод обладает существенными недостатками, которые не позволяют его практическое использование: так как толщина контактной площадки кристалла не превышает 1 мкм, то величина врезания выступов в контактную площадку должна составлять 0,2...0,8 мкм, а плоскостность расположения выступающих частей выступов тоже должна составлять доли микрометра, что практически невозможно выполнить; попадание любой инородной частицы (пыли) размером в несколько микрометров в зону контактирования контакта с контактной площадкой приведет к перекосу кристалла и потере контакта по большому количеству зон контактирования, что будет определено системой тестирования как брак кристалла, хотя он может быть годным; при контактировании острые поверхности наконечников, имеющих сложный профиль, будут нарушать поверхность контактной площадки, что сделает невозможным вторичное контактирование к площадке при стандартном корпусировании кристалла.

Известно также техническое решение по патенту США 5399505 от 21 марта 1995 г., H 01 L 21/66 "Метод и аппаратура для осуществления на уровне пластин тестирования кристаллов интегральных схем".

На пластину наносят проводники, которые используют для передачи электрических сигналов к кристаллам интегральных схем и от них так, что может быть проведено на уровне пластины, тестирования и ЭТТ кристаллов интегральных схем. При этом каждый проводник на пластине электрически соединен с одной и той же контактной площадкой на каждом кристалле. Каждый проводник на пластине включает по меньшей мере свою часть проводника, которая проходит сверху поверхности по меньшей мере одного кристалла интегральной схемы.

Данное техническое решение применимо только в тех редких случаях, когда допустимо по условиям контроля параллельное соединение всех одноименных контактных площадок каждого кристалла. При этом возникает определенная трудность в адресе вышедшего из строя кристалла. Для многовыводных кристаллов неизбежна сложная многоуровневая развода для вывода каждой контактной площадки на периферийную область пластины. При этом возможна емкостная паразитная связь между нанесенным проводником и полупроводниковой структурой.

Известно техническое решение по европатенту 0287451 от 12 апреля 1988 г., H 01 L 21/66 "Способ и устройство для соединения и монтажа электронного компонента при испытаниях".

Способ предусматривает соединение компонента с рамкой по периферии компонента с помощью проволочных проводников. Испытания компонента проводят, соединяя испытательное оборудование с рамкой. После испытаний компонент монтируют на подложке, а соединение компонента с подложкой осуществляют проводниками, соединяющими компонент с рамкой. После соединения проводники перерезают между контактными площадками на подложке и рамкой, после чего рамку убирают.

Данный способ имеет в качестве недостатка применение проволочных выводов для соединения контактных площадок компонента с испытательным оборудованием и дальнейшим их перерезанием для осуществления соединений в аппаратуре, что практически неосуществимо для многовыводных кристаллов. В случае обрыва хотя бы одного проволочного вывода весь кристалл придется забраковать. Не решен вопрос с теплоотводом от кристалла во время ЭТТ и контроля. В настоящее время фирма Aehr Test Systems разработала универсальную систему тестирования и ЭТТ на целой пластине одновременно всех кристаллов, которая содержит десятки тысяч зондовых контактов.

Такое решение не может быть оптимальным, так как в случае деформации или окисления хотя бы одного контакта (что требует постоянного контроля состояния контактирующего устройства) все сложнейшее контактирующее устройство выходит из строя. Кроме того, при сокращении шага между контактными площадками до 150 мкм и размере контактной площадки 70×70 мкм (что сейчас уже осуществляется) применение зондовых устройств становится практически невозможным.

Тестирование в носителях многоразового использования применяет та же фирма для достаточно простых кристаллов с небольшим количеством внешних выводов и с большим шагом между контактными площадками. Кристаллы зажимаются в индивидуальные контактирующие устройства, которые запаяны в коммутирующую плату. После проведения ЭТТ и контроля контактирующие устройства раскрывают и годные кристаллы используют в аппаратуре. Общий недостаток всех механических контактирующих устройств - низкая надежность контактирования и большой шаг расположения внешних контактных площадок на кристалле.

Проведение ЭТТ и контроля компонентов с шариковыми выводами возможно только при минимальном шаге расположения выводов, равном 0,75 мм (см. статью "Burn-in test sockets benefical for high volume CSP application" в журнале "Advanced Packaging" июль-август 1998 г.).

Известно техническое решение по российскому патенту 2133522 от 20 июля 1999 г., H 01 L 21/66 "Способ изготовления и контроля электронных компонентов".

Множество кристаллов располагают в пресс-форме, ориентируясь на контактные площадки кристаллов и базовые элементы пресс-формы, изолируют все незащищенные поверхности кристаллов, кроме контактных площадок. При расположении в пресс-форме кристаллы фиксируют между собой с образованием группового носителя, обеспечивая расположение лицевых поверхностей кристаллов в единой плоскости с одной из поверхностей группового носителя, при этом на эту плоскость наносят одновременно все проводники, необходимые для ЭТТ и контроля, а также внешний разъем носителя.

К недостаткам данного способа следует отнести неразборность групповой микроплаты и, как следствие, невозможность вычленения из нее и дальнейшего использования голого кристалла. Неизбежны также чрезмерно длинные соединения кристаллов с устройствами формирования входных импульсов и обработки выходной информации.

Известно также техническое решение по российскому патенту 2193260 от 20 ноября 2002 г., H 01 L 25/04 "Способ изготовления многокомпонентного трехмерного электронного модуля".

Бескорпусные компоненты размещают в окнах групповой керамической заготовки с ориентацией по контуру и с соблюдением единой плоскости расположения активных зон компонентов и лицевой поверхности заготовки. Компоненты фиксируют в таком положении и изолируют электрически незащищенные зоны компонентов по их лицевой стороне. Далее наносят проводники на лицевую и обратную стороны заготовки и компонентов, одновременно формируя разъем и соединительные проводники, необходимые для ЭТТ и контроля. Годные микроплаты вырезают из групповой заготовки и собирают "в пакет", соединяя их между собой капиллярной пайкой. К одной из граней пакета припаивают теплорастекатель с внешними выводами и герметизируют изготовленный модуль.

Данное решение относится только к изготовлению керамических микроплат и сборке из них трехмерного модуля.

Однако данное техническое решение по патенту 2193260 является наиболее близким аналогом патентуемого способа испытаний и контроля электронных компонентов.

Сущность изобретения

Техническим результатом данного изобретения является обеспечение высокого качества изготовления электронных компонентов, в том числе бескорпусных и корпусированных многоконтактных компонентов с произвольным шагом и местом расположения контактных площадок или внешних выводов.

Способ испытаний и контроля электронных компонентов включает предварительное изготовление базовой платы, используя подложку, в окнах которой размещают постоянные компоненты и/или микроплаты с ними, выполняющие функции формирования входных сигналов и обработку выходных сигналов при последующих испытаниях, включая электротермотренировку (ЭТТ) и контроль испытуемых компонентов. При этом подложку базовой платы изготавливают преимущественно из электроизоляционного теплопроводного материала. Подложку базовой платы можно изготавливать также из полимерного материала литьем или прессованием с одновременным фиксированием постоянных компонентов и/или микроплат с ними и образованием окон и отверстий в подложке базовой платы.

Испытуемые полупроводниковые компоненты подготавливают, применяя стандартные технологические процессы, включающие предварительный контроль компонентов на пластине, прецизионную сквозную резку пластины с точностью выполнения габаритных размеров компонентов не хуже ±5 мкм, очистку компонентов в деионизованной воде, переукладку условно годных после контроля на пластине испытуемых компонентов в защитную (от электростатики и механических повреждений) кассету. В конструкциях микроплат и в базовой плате используют только гарантированно годные постоянные компоненты. Микроплаты изготавливают с учетом технических решений по российским патентам 2133522 и 2193260.

После фиксирования постоянных компонентов и/или микроплат фиксирующим составом, изолирования стыков между ними и окнами в подложке базовой платы изолирующим составом, а также после нанесения постоянных проводников, на поверхности подложки локально наносят защитный слой, способный противостоять воздействию сред при проведении дальнейших операций; при этом образуют зоны контактирования, оставляя открытыми от защитного слоя только те участки постоянных проводников, которые будут контактировать с впоследствии наносимыми временными проводниками.

После чего в свободных окнах базовой платы размещают испытуемые компоненты, подлежащие испытаниям и функциональному контролю; затем их фиксируют фиксирующим составом и изолируют изолирующим составом стыки компоненты - окна. Изолирование стыков между постоянными и испытуемыми компонентами и окнами в подложке производят с одновременным изолированием сколов, полученных в результате резки полупроводниковой пластины (или подготовки компонентов), но при этом исключают попадание изолирующего состава на контактные площадки постоянных и испытуемых компонентов. После фиксирования постоянных и испытуемых компонентов и/или микроплат, а также после изолирования стыков между ними и окнами в подложке, в случае необходимости, производят операцию термообработки.

В случае образования значительного зазора между испытуемыми компонентами и окнами в базовой плате размещение испытуемых компонентов в окнах базовой платы производят путем их приклейки лицевой поверхностью к предварительно нанесенной на лицевую поверхность базовой платы клейкой ленте, при этом испытуемые компоненты ориентируют по их контактным площадкам, используя в качестве шаблона "свободную" маску для дальнейшего нанесения временных проводников; после фиксирования испытуемых компонентов клейкую ленту удаляют и очищают лицевые поверхности базовой платы и испытуемых компонентов от остатков клея преимущественно плазмохимическим методом.

Далее наносят временные проводники, соединяющие контактные площадки или постоянные проводники испытуемых компонентов с незащищенными участками постоянных проводников, расположенными в зонах контактирования базовой платы.

Нанесение постоянных и временных проводников производят преимущественно методом вакуумного напыления через "свободные" маски материалом, позволяющим сохранить при удалении временных проводников ранее нанесенные постоянные проводники на поверхности подложки базовой платы и испытуемых компонентов.

Затем проводят испытания и функциональный контроль испытуемых компонентов с компьютерной регистрацией вышедших из строя компонентов; после чего удаляют временные проводники, не разрушая при этом нанесенные ранее постоянные проводники; затем удаляют фиксирующий и изолирующий составы с поверхностей испытанных компонентов и из стыков компоненты - окна. Удаление временных проводников производят методом химического травления с последующей нейтрализацией, промывкой и вакуумной сушкой. Можно удалять фиксирующий и изолирующий составы методом растворения в ультразвуковой ванне с последующей промывкой и вакуумной сушкой. Можно также удалять временные проводники, фиксирующий и изолирующий составы методом сквозной резки (например, лазерной) в местах стыка испытанных компонентов с окнами. Существует вариант изолирования стыков между компонентами и окнами изолирующим составом, а также локального нанесения защитного слоя на подложку базовой платы методом распыления диэлектрика через "свободную" маску или методом трафаретной печати.

Далее извлекают все испытанные компоненты из окон базовой платы и, учитывая компьютерные данные, годные компоненты упаковывают в защитную кассету. При этом базовую плату используют в дальнейшем многократно для проведения испытаний и контроля следующей партии аналогичных электронных компонентов.

Перечень фигур чертежей

В дальнейшем предлагаемое изобретение поясняется конкретными примерами его выполнения и прилагаемыми чертежами, на которых:

фиг.1 изображает технологический маршрут испытаний и контроля электронных компонентов;

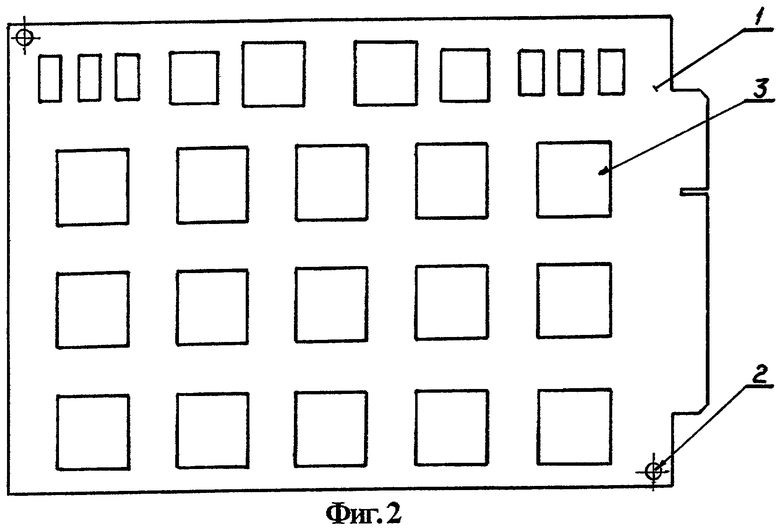

фиг.2 изображает подложку базовой платы после прошивки в ней сквозных отверстий и окон;

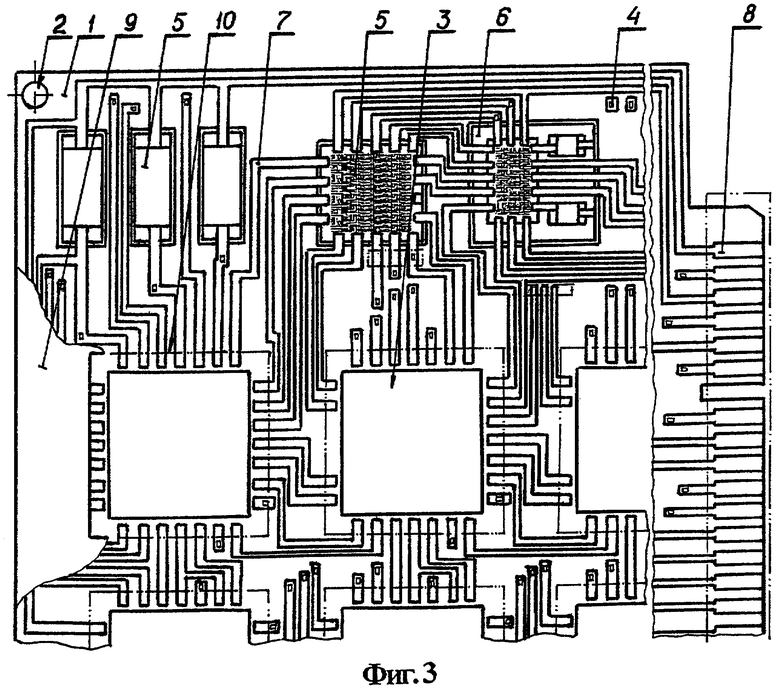

фиг.3 изображает базовую плату;

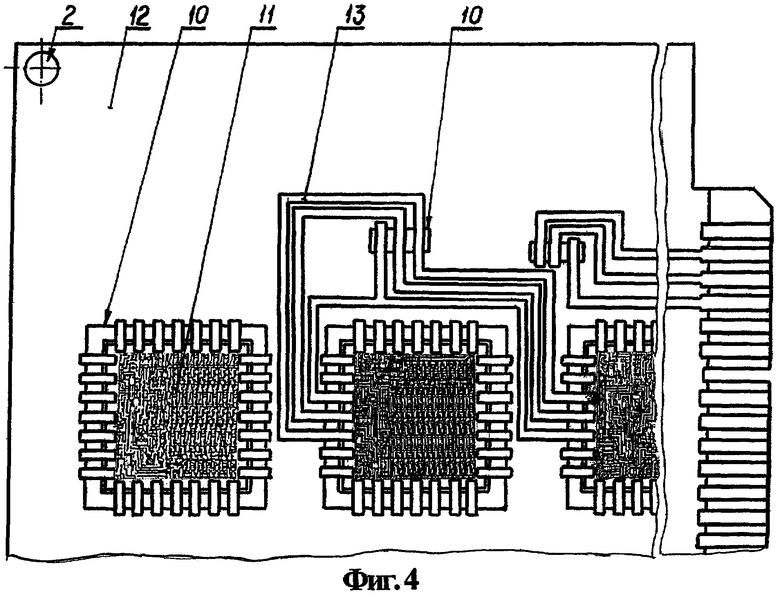

фиг.4 изображает испытуемые компоненты в составе базовой платы;

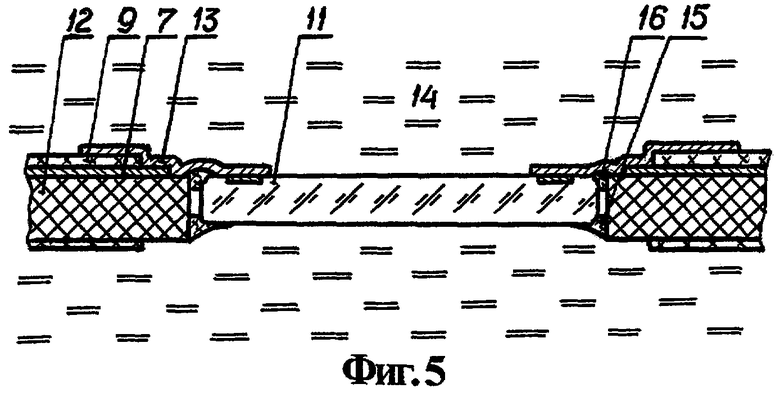

фиг.5 изображает операцию удаления временных проводников;

фиг.6 изображает операцию удаления фиксирующего и изолирующего составов;

фиг.7 изображает годные после испытаний компоненты, упакованные в защитную кассету.

Сведения, подтверждающие возможность осуществления изобретения

Для реализации данного изобретения разработан технологический процесс, укрупненный маршрут которого показан на фиг.1. Группа операций 11 обеспечивает изготовление базовой платы.

Подложку базовой платы (в дальнейшем - подложку) изготавливают преимущественно из электроизоляционного теплопроводного материала, например из керамики. Подложку можно изготавливать из нетеплопроводного материала (типа стеклоэпоксида), но тогда в этом случае необходимо предусматривать применение дополнительного теплоотвода при проведении испытаний и контроля.

Подготовку подложки (опер.11а) производят с применением алмазного инструмента на стандартных установках резки полупроводниковых пластин. При этом подложку, при необходимости, предварительно шлифуют для получения нужного размера по толщине. Далее в подложке прошивают сквозные отверстия и окна (опер.11b). Общий вид подложки показан на фиг.2. В подложке 1 имеются сквозные базовые отверстия 2, необходимые для дальнейшего использования "свободных" масок. Точность выполнения межцентровых расстояний и допуск на диаметр отверстий должен быть не более ±10 мкм. В подложке 1 также прошиваются сквозные окна 3 для размещения постоянных и испытуемых электронных компонентов и микроплат. Точность выполнения данной операции выбирают такой, чтобы обеспечить максимальный зазор между окном и впоследствии размещенным в нем компонентом или микроплатой не более 0,25 от размера минимальной контактной площадки компонента или микроплаты. В подложке 1 прошиваются также переходные отверстия 4 (на фиг.2 условно не показаны) для последующего соединения проводников, расположенных на противоположных поверхностях подложки.

Далее в соответствии с операцией 11с в окнах подложки 1 размещают постоянные компоненты 5 (фиг.3) и/или микроплаты 6 с ними, которые обеспечивают формирование входных сигналов и обработку выходных сигналов, необходимых для дальнейших испытаний, включая электротермотренировку (ЭТТ) и контроль испытуемых компонентов.

Затем постоянные компоненты 5 и микроплаты 6 фиксируют фиксирующим составом в окнах 3 подложки 1 с образованием единой плоскости лицевых поверхностей постоянных компонентов 5 и микроплат 6 с поверхностью подложки 1 (опер.11d). Далее изолируют изолирующим составом стыки между постоянными компонентами 5 и/или микроплатами 6 и окнами 3 в плодложке. При этом изолирующий состав не должен перекрывать контактные площадки постоянных компонентов 5 или микроплат 6 (опер.11е). Наносят постоянные проводники 7 на поверхности подложки 1 с одновременной металлизацией переходных отверстий 4 и образованием внешнего разъема 8 (опер.11f).

Далее наносят (опер.11g) защитный слой 9 на всю поверхность заготовки 1, за исключением зон контактирования 10, с размещением в них участков постоянных проводников 7, необходимых для дальнейшего контактирования. Материалом защитного слоя 9 может служить эпоксидный лак или любой другой материал, способный противостоять воздействию сред при проведении дальнейших операций. На этом изготовление базовой платы заканчивают.

Одновременно проводят подготовку испытуемых компонентов к испытаниям и функциональному контролю (группа операций 1). Эти операции приведены только для случая поставки компонентов в виде полупроводниковых пластин. Все эти операции (1а...1е) являются стандартными в полупроводниковом производстве и особых пояснений не требуют, за исключением операции 1с. Резку полупроводниковой пластины производят насквозь с ориентацией на контактные площадки компонентов с точностью выполнения габаритных размеров не хуже ±5 мкм.

Далее (фиг.4) размещают испытуемые компоненты 11 в свободных окнах базовой платы 12 по аналогии с выполнением операции 11с (опер.2), фиксируют их (опер.3) в окнах 3 фиксирующим составом по аналогии с операцией 11d и изолируют стыки между испытуемыми компонентами 11 и окнами 3 в базовой плате 12 (опер.4) изолирующим составом по аналогии с операцией 11е.

После этого наносят (опер.5) на поверхности базовой платы 12 временные проводники 13, соединяющие контактные площадки испытуемых компонентов 11 с участками постоянных проводников 7, расположенными в зонах контактирования 10. Одновременно наносятся временные проводники 13 на ламели внешнего разъема 8. Нанесение постоянных 7 и временных 13 проводников производят преимущественно методом вакуумного напыления через "свободные" маски с использованием базовых отверстий 2 материалом, позволяющим сохранить при удалении временных проводников 13 ранее нанесенные постоянные проводники 7 на поверхности подложки 1.

"Свободные" маски изготавливают (опер.12) путем рихтовки и очистки ферромагнитной ленты (опер.12а), лазерным прорезанием рисунка будущих проводников (опер.12b), подшлифовкой плоскостей от наплывов материала масок (опер.12с) и покрытием поверхностей масок антиадгезионным составом типа фторопласта (опер.12d).

Операции 11а...11f и 2...5 выполняют с учетом технических решений по российскому патенту 2193260.

Далее проводят испытания и контроль (или диагностику) испытуемых компонентов 11 (опер.6) в соответствии с техническими условиями на них.

Затем удаляют временные проводники 13 (опер.7) преимущественно методом химического травления (фиг.5). При этом травящий состав 14 удаляет временные проводники 13, оставляя целыми постоянные проводники 7, расположенные в зонах контактирования 10, образованных защитным слоем 9. После этой операции, при необходимости, проводят нейтрализацию, отмывку в дистиллированной воде и вакуумную сушку.

Далее производят удаление фиксирующего 15 и изолирующего 16 составов (фиг.6, опер.8) преимущественно методом растворения в ультразвуковой ванне растворителем 17. Испытанные компоненты 11 извлекают из окон 3 базовой платы 12 (опер.9) и, при необходимости, промывают вместе с базовой платой 12 в дистиллированной воде и подвергают вакуумной сушке.

Годные испытанные компоненты 11 упаковывают в защитную кассету 18 (фиг.7, опер.10), внутренние полости которой покрыты токопроводящим слоем 19, защищающим испытанные компоненты 11 от статического электричества, а конструкция защитной кассеты 18 предусматривает также механическую защиту годных компонентов. Базовую плату 12 используют многократно для проведения испытаний и функционального контроля аналогичных электронных компонентов.

Данное изобретение может быть с успехом использовано при климатических и ресурсных испытаниях, а также при групповой электротермотренировке с одновременным функциональным контролем бескорпусных электронных компонентов независимо от количества контактных площадок на компоненте, размера, места и шага их расположения. В качестве испытуемых компонентов можно применить микроплаты или другие электронные изделия, смонтированные преимущественно на коммутационных платах, а также готовые интегральные схемы с внешними выводами. При этом патентуемый способ обеспечивает высоконадежное непосредственное контактирование испытуемых компонентов с внешними устройствами.

Пример промышленного применения.

В настоящее время бескорпусные активные электронные компоненты (кристаллы), имеющие большое количество контактных площадок (100 и более) с малыми размерами (70×70 мкм) и шагом их расположения (150 мкм), на предприятии-изготовителе подвергаются только частичному контролю из-за невозможности изготовления многозондовых установок для таких кристаллов. А необходимые испытания, тренировку и функциональный контроль кристаллов осуществляют только при приварке их к промежуточному носителю ("пауку"), что неизбежно ухудшает показатели надежности, увеличивает размеры корпуса и стоимость ИС.

Используя патентуемое решение можно, например, подвергнуть ЭТТ и полностью проконтролировать современный кристалл процессора РХА 255 фирмы Intel, имеющий размер 10×10 мм, количество контактных площадок 256, расположенных с шагом 150 мкм.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИЗГОТОВЛЕНИЯ МНОГОКОМПОНЕНТНОГО ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193260C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2006 |

|

RU2314598C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ПОЛИМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2001 |

|

RU2193259C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2002 |

|

RU2221312C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2011 |

|

RU2475885C1 |

| ТРЕХМЕРНЫЙ ЭЛЕКТРОННЫЙ МОДУЛЬ С ШАРИКОВЫМИ ВЫВОДАМИ | 2006 |

|

RU2312425C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ГИБРИДНОГО ЭЛЕКТРОННОГО МОДУЛЯ | 2002 |

|

RU2222074C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ТРЕХМЕРНОГО ЭЛЕКТРОННОГО ПРИБОРА | 2012 |

|

RU2498453C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ СВЧ ТРЕХМЕРНОГО МОДУЛЯ | 2012 |

|

RU2498454C1 |

| СПОСОБ НАНЕСЕНИЯ ПРОВОДНИКОВ НА ПОВЕРХНОСТИ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 2006 |

|

RU2312423C1 |

Использование: в области производства электронных компонентов, обладающих высокими показателями надежности, в том числе производства гарантированно годных компонентов. Сущность изобретения: испытания, включая электротермотренеровку и контроль испытуемых компонентов, производят с помощью базовой платы, содержащей постоянные электронные компоненты, обеспечивающие формирование входных сигналов и обработку выходных сигналов для последующих испытаний и контроля компонентов. В окнах базовой платы размещают испытуемые компоненты, закрепляют их и наносят методом вакуумного напыления временные проводники, соединяющие испытуемые компоненты с проводниками на базовой плате. После испытаний и контроля удаляют временные проводники и извлекают из окон базовой платы полученные таким образом годные компоненты, а базовую плату используют многократно для испытаний и контроля следующих партий аналогичных компонентов. Техническим результатом изобретения является обеспечение высокого качества изготовления электронных компонентов, в том числе бескорпусных и корпусированных многоконтактных компонентов с произвольным шагом и местом расположения контактных площадок или внешних выводов. 12 з.п. ф-лы, 7 ил.

| СПОСОБ ИЗГОТОВЛЕНИЯ И КОНТРОЛЯ ЭЛЕКТРОННЫХ КОМПОНЕНТОВ | 1997 |

|

RU2133522C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПЕЧАТНЫХ ПЛАТ | 1990 |

|

RU2072120C1 |

| US 5399505 A, 21.03.1995 | |||

| СЕПАРАТОР ДЛЯ ОЧИСТКИ СЕМЯН ОТ ПРИМЕСЕЙ | 0 |

|

SU287451A1 |

Авторы

Даты

2006-03-20—Публикация

2003-11-14—Подача