ОБЛАСТЬ ИЗОБРЕТЕНИЯ

Настоящее изобретение относится в общем случае к области микропроцессоров и компьютерных систем. Более конкретно, настоящее изобретение относится к способу и устройству для параллельного объединения данных со сдвигом вправо.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

По мере развития технологии процессоров также создаются новые коды программ для работы на компьютерах с этими процессорами. Пользователи в общем случае ожидают и требуют более высокой производительности от своих компьютеров независимо от типа используемого программного обеспечения. Одна из таких проблем может возникнуть из-за типов команд и операций, которые в текущий момент выполняются в процессоре. Некоторые типы операций требуют большего времени для завершения из-за сложности операций и/или необходимых для них схем. Это создает возможность оптимизации способа, которым некоторые сложные операции выполняются в процессоре.

Медиаприложения (мультимедийные прикладные программы) способствуют разработкам микропроцессоров в течение более десяти лет. Фактически, большинство обновлений вычислительной техники за последние годы были вызваны медиаприложениями. Эти обновления преобладающим образом происходили в пределах потребительского сегмента, хотя существенные усовершенствования также имели место в предпринимательском сегменте, например, для целей образования и коммуникации с учетом развлекательного аспекта. Однако будущие медиаприложения будут предъявлять все более высокие требования к вычислениям. В результате, в ближайшем будущем пользование персональными компьютерами (ПК) будет характеризоваться более интересными аудиовизуальными эффектами, а также будет более легким в практическом применении, и что еще более важно, компьютеры будут объединены со средствами связи.

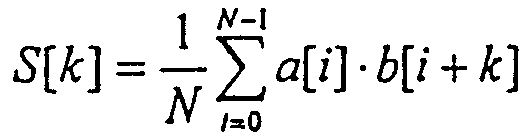

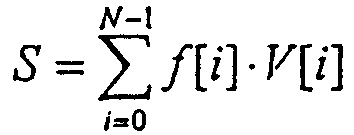

Соответственно, отображение изображений так же, как воспроизведение аудио и видеоданных, которое все вместе упоминается как содержимое, стало все более и более популярными приложениями для существующих вычислительных устройств. Операции фильтрации и свертки являются примерами самых обычных операций, выполняемых с данными содержимого, такого как изображение, аудио и видеоинформация. Как известно специалистам, вычисления фильтрации и корреляции выполняют с помощью операции умножения с накоплением, которая суммирует произведения данных и коэффициентов. Корреляция двух векторов А и B состоит в вычислении суммы S:

уравнение (1), которое очень часто используется при k=0:

уравнение (1), которое очень часто используется при k=0:

уравнение (2)

уравнение (2)

В случае, когда N-отводный фильтр f применяют к вектору V, сумма S может быть рассчитана следующим образом:

уравнение (3)

уравнение (3)

Такие операции требуют большого объема вычислений, но обеспечивают высокий уровень параллелизма данных, который может использоваться при эффективном воплощении с использованием различных устройств хранения данных, таких, например, как регистры с одним потоком команд и множеством потоков данных (SIMD).

Применение операций фильтрации можно найти в большом множестве задач обработки изображений и видеоинформации, а также связи. Примерами использования фильтров являются уменьшение артефактов формирования блоков данных в видеоизображении стандарта MPEG (стандарт, выработанный экспертной группой по кинематографии), уменьшение шумов и звуков, отделение водяных знаков от значений пикселов для улучшения обнаружения водяных знаков, корреляция для сглаживания, увеличение резкости, сокращение шума, обнаружение краев и масштабирование размеров изображений или видеокадров, дискретизация видеокадров для оценки движения суб-пикселов, улучшение качества аудиосигнала и изменение формы импульсов и коррекция сигналов в связи. Соответственно, операции фильтрации так же, как свертки, жизненно важны для вычислительных устройств, которые обеспечивают воспроизведение содержимого, которое включает в себя изображение, аудио и видеоданные.

К сожалению, существующие способы и команды направлены на общие потребности фильтрации и не являются всесторонними. Фактически, многие виды архитектур не поддерживают средство для эффективного вычисления фильтрации для разных длин фильтра и типов данных. Кроме того, упорядочивание данных в устройствах хранения данных, таких как регистры SIMD, так же, как возможность суммирования смежных значений в регистре и частичных переносов данных между регистрами, в общем случае не поддерживаются. В результате, существующие виды архитектур требуют ненужных изменений типа данных, которые минимизируют количество операций за одну команду и значительно увеличивают количество тактовых циклов, требуемых для упорядочивания данных для арифметических операций.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Настоящее изобретение показано для примера, а не для ограничения, на чертежах, на которых одинаковые ссылочные позиции обозначают сходные элементы и на которых:

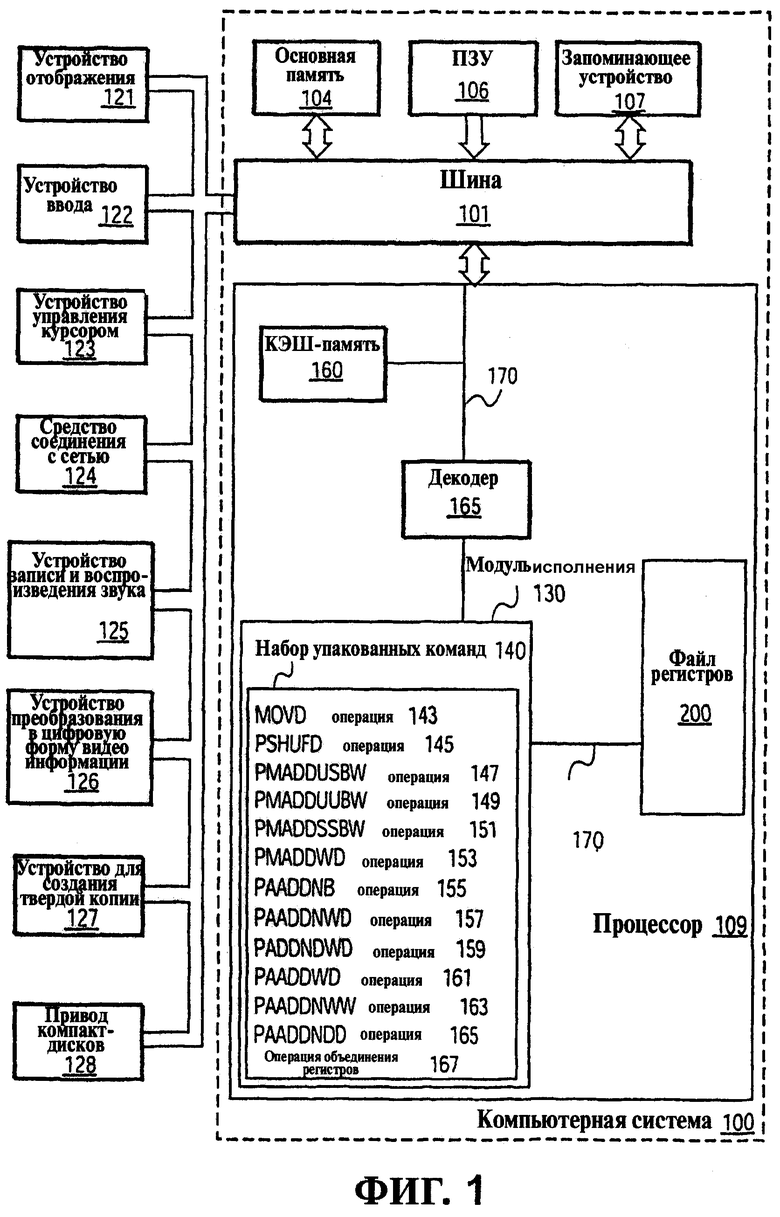

Фиг.1 - структурная схема компьютерной системы, реализующей один из вариантов осуществления настоящего изобретения;

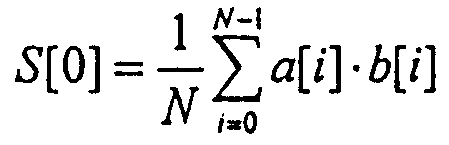

Фиг.2 - структурная схема варианта осуществления процессора, как показано на фиг.1, в соответствии с другим вариантом осуществления настоящего изобретения;

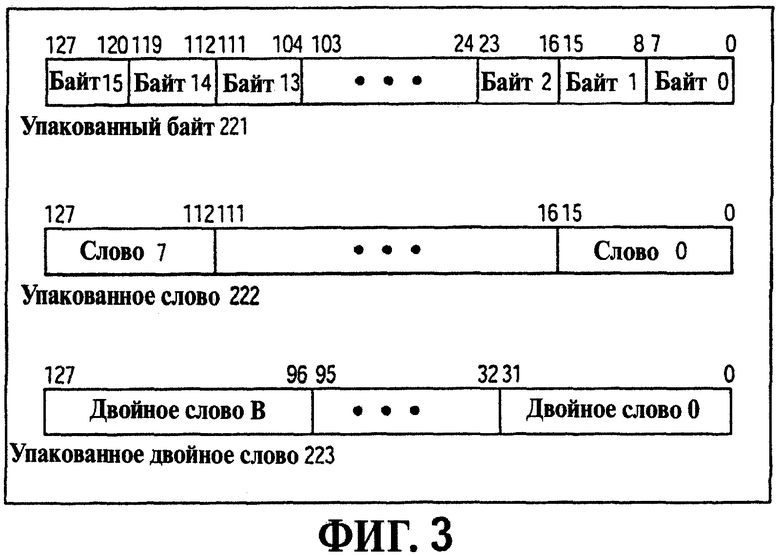

Фиг.3 - иллюстрация видов упакованных данных согласно другому варианту осуществления настоящего изобретения;

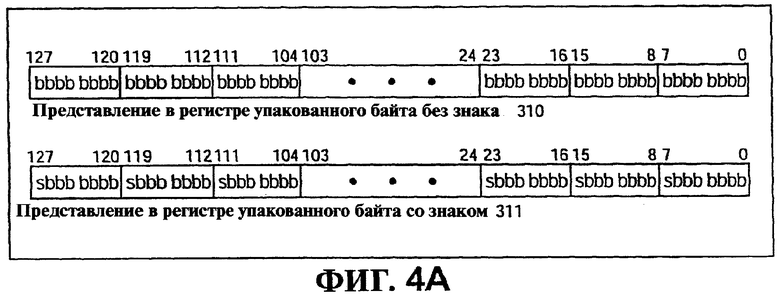

Фиг.4A - представление в регистре упакованного байта согласно одному из вариантов осуществления настоящего изобретения;

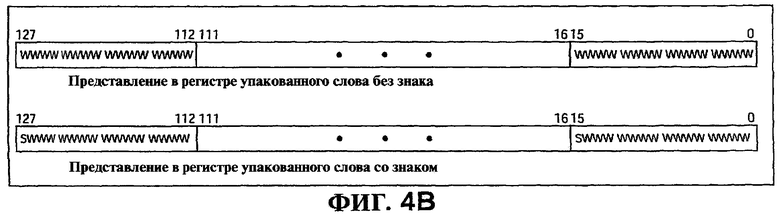

Фиг.4B - представление в регистре упакованного слова согласно одному из вариантов осуществления настоящего изобретения;

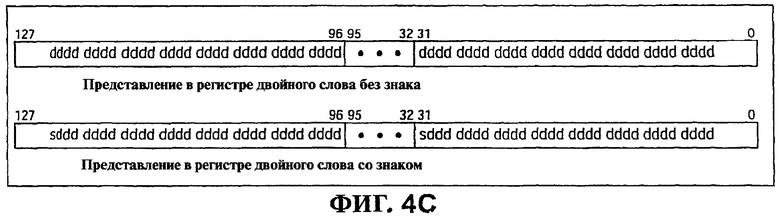

Фиг.4C - представление в регистре упакованного двойного слова согласно одному из вариантов осуществления настоящего изобретения;

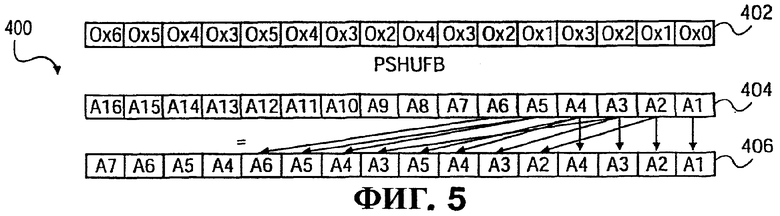

Фиг.5 - диаграмма, иллюстрирующая действие команды перемещения байтов в соответствии с вариантом осуществления настоящего изобретения;

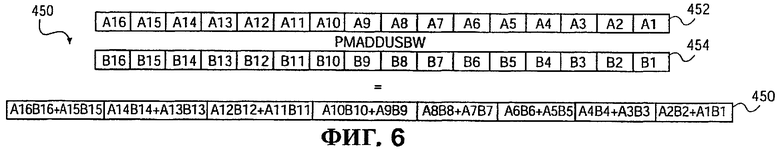

Фиг.6 - диаграмма, иллюстрирующая команду умножения с накоплением байтов в соответствии с вариантом осуществления настоящего изобретения;

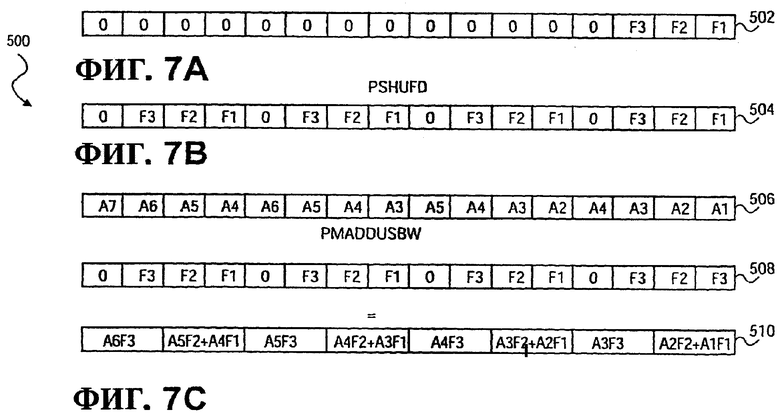

Фиг.7A-7C - диаграммы, иллюстрирующие команду перемещения байтов по фиг.5, объединенную с командой умножения с накоплением байтов по фиг.6, для получения множества сумм пар произведений в соответствии с другим вариантом осуществления настоящего изобретения;

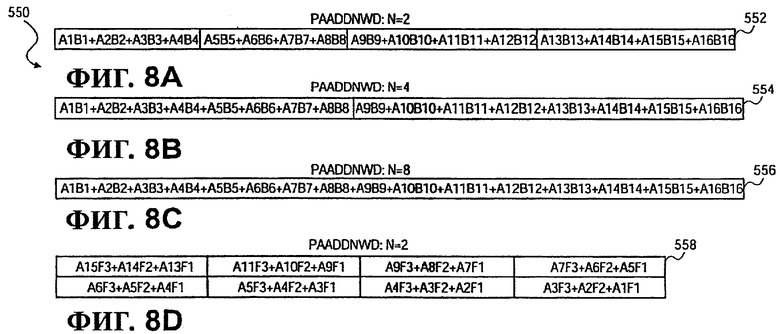

Фиг.8A-8D - диаграммы, иллюстрирующие команду суммирования смежных элементов в соответствии с другим вариантом осуществления настоящего изобретения;

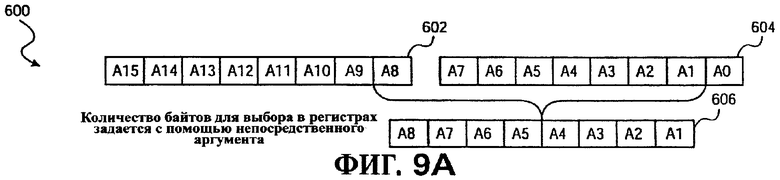

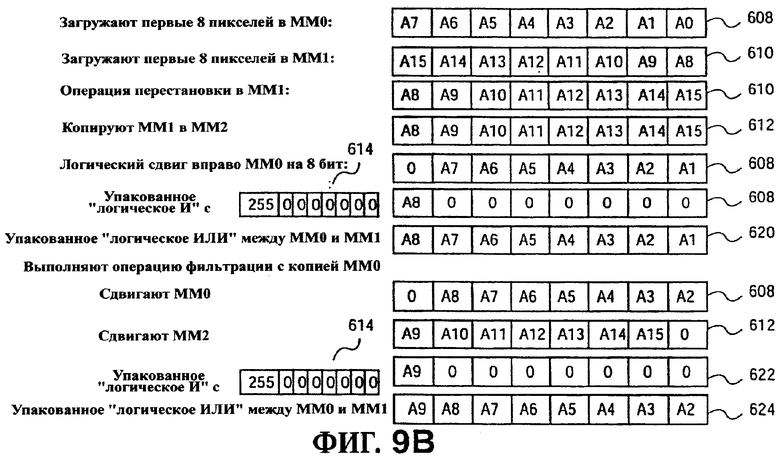

Фиг.9A и 9B - команда объединения регистров в соответствии с другим вариантом осуществления настоящего изобретения;

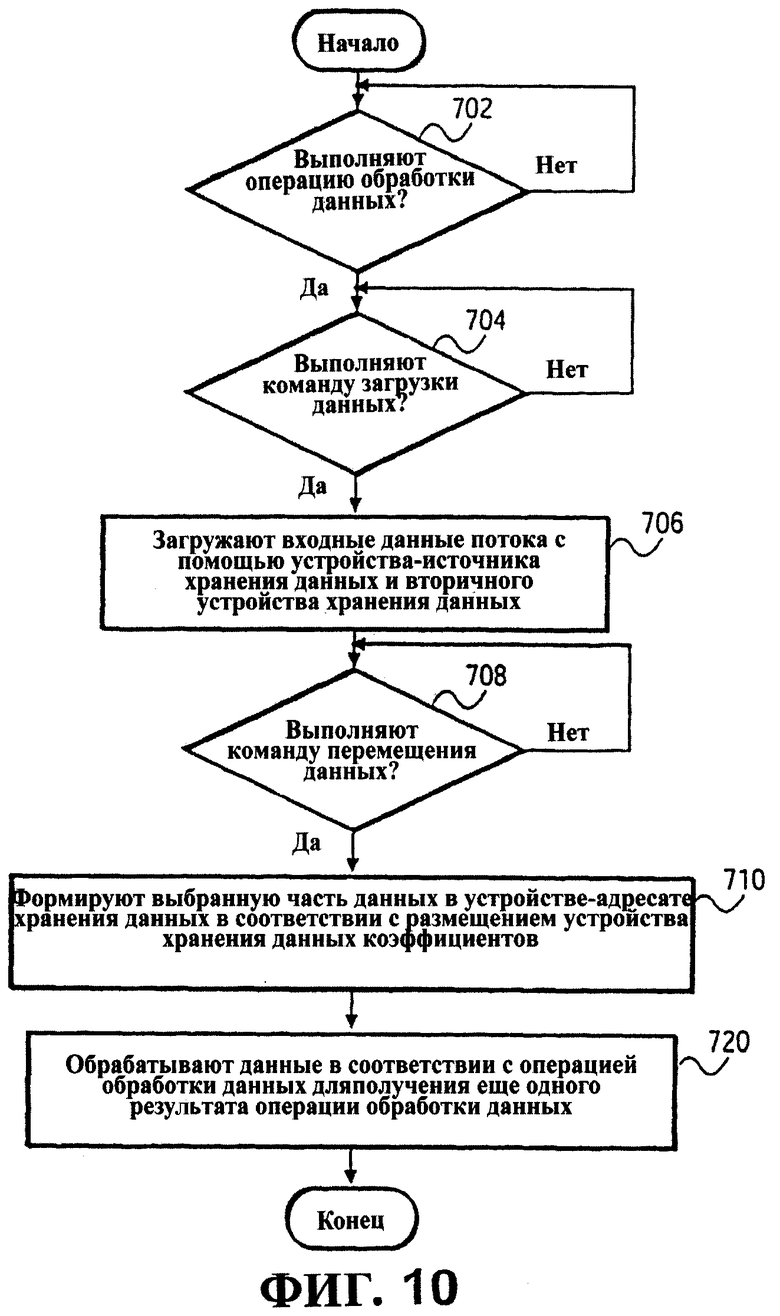

Фиг.10 - блок-схема последовательности операций для эффективной обработки данных содержимого в соответствии с одним из вариантов осуществления настоящего изобретения;

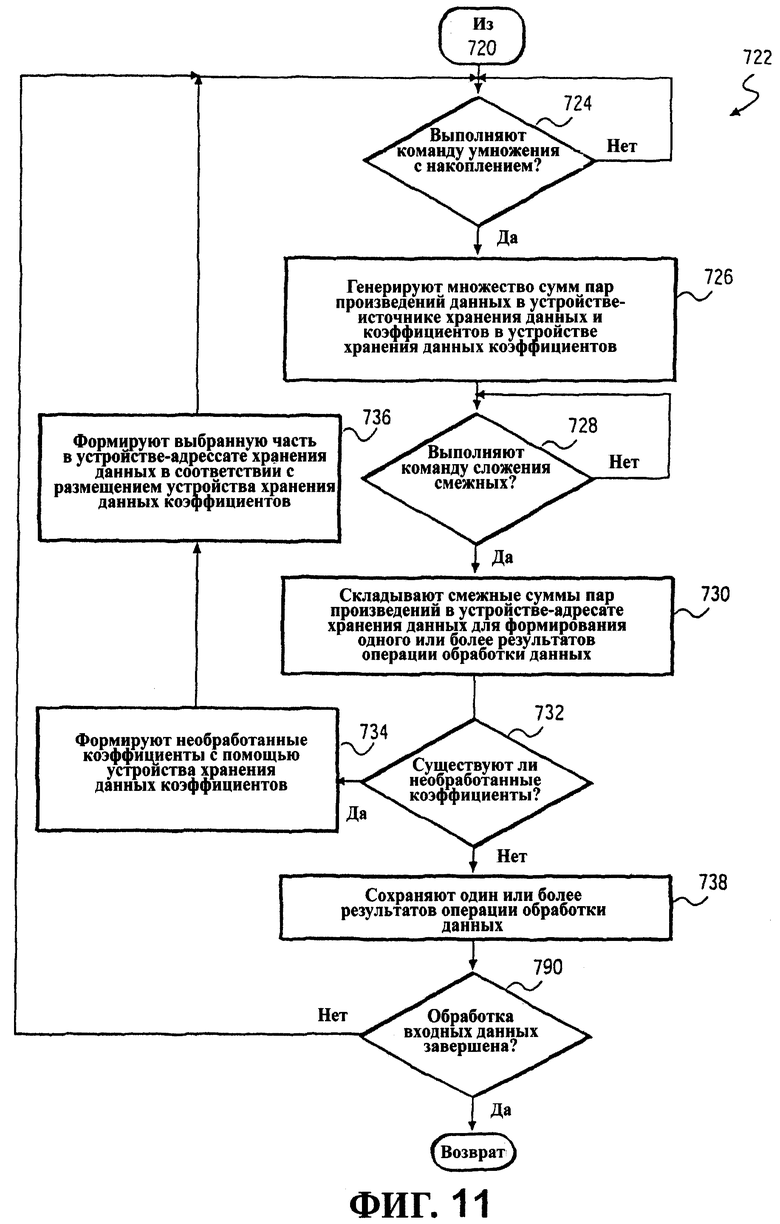

Фиг.11 - блок-схема способа обработки данных содержимого согласно операции обработки данных в соответствии с другим вариантом осуществления настоящего изобретения;

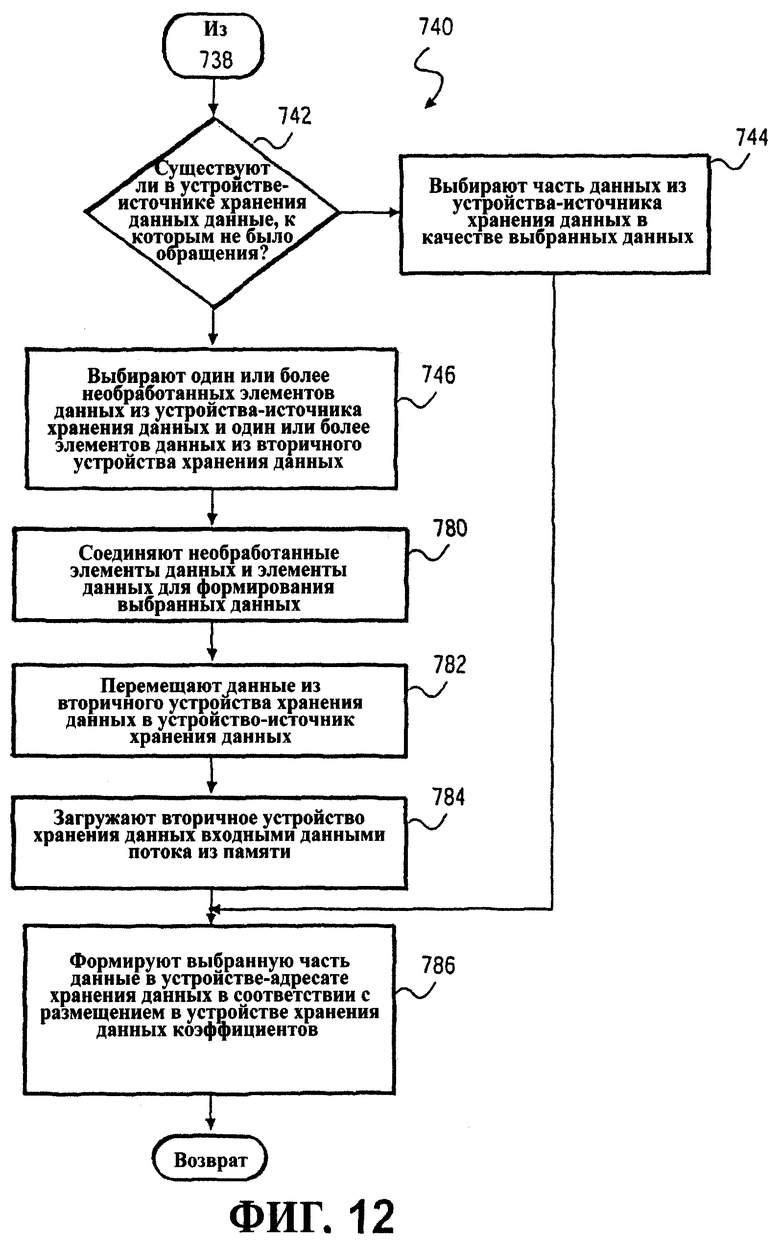

Фиг.12 - блок-схема последовательности операций для продолжения обработки данных содержимого в соответствии с другим вариантом осуществления настоящего изобретения;

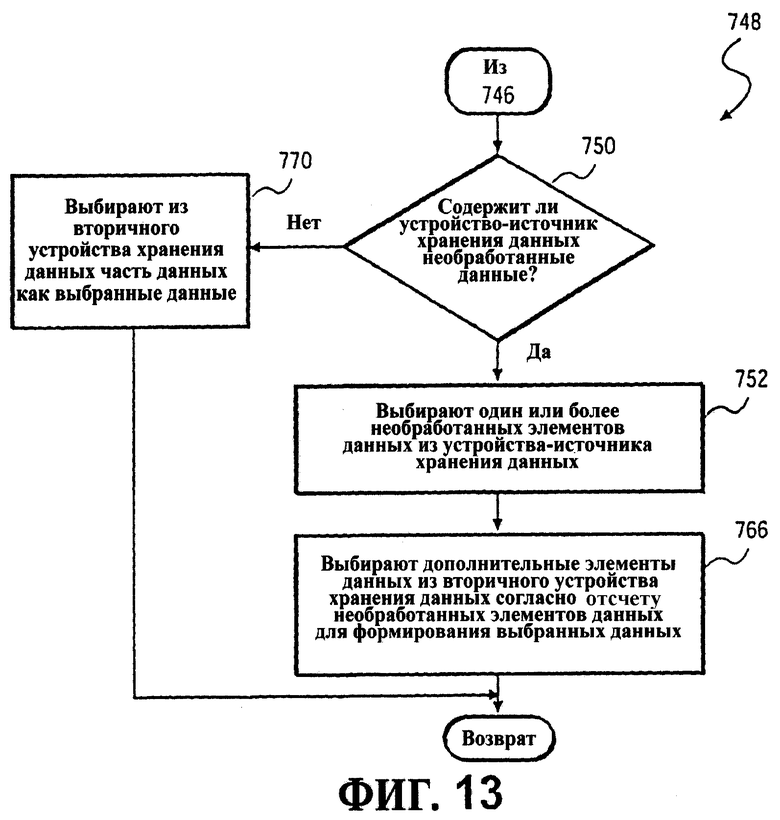

Фиг.13 - блок-схема последовательности операций, иллюстрирующая операцию объединения регистров в соответствии с другим вариантом осуществления настоящего изобретения.

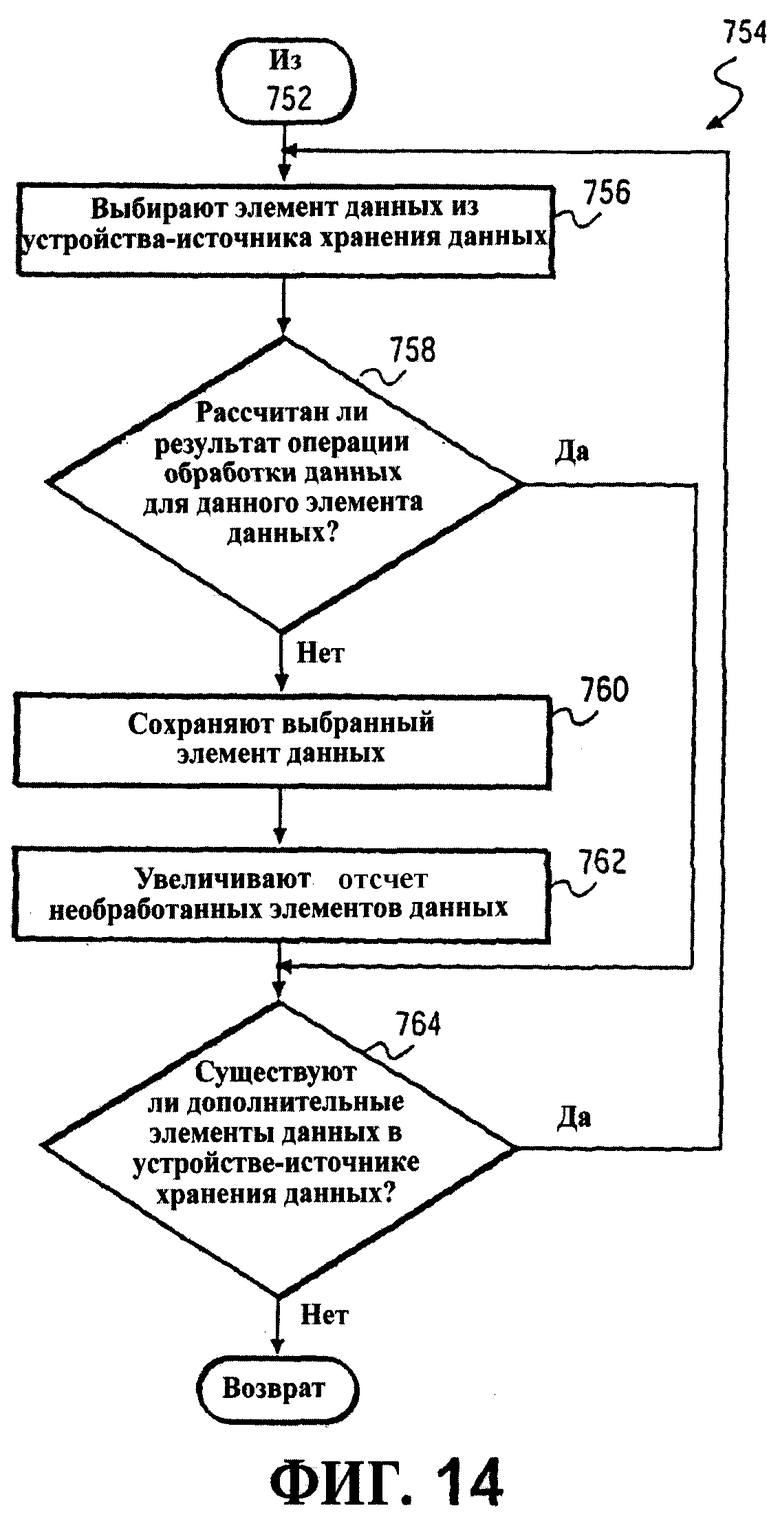

Фиг.14 - блок-схема последовательности операций способа выбора необработанных элементов данных из устройства-источника хранения данных в соответствии с примерным вариантом осуществления настоящего изобретения;

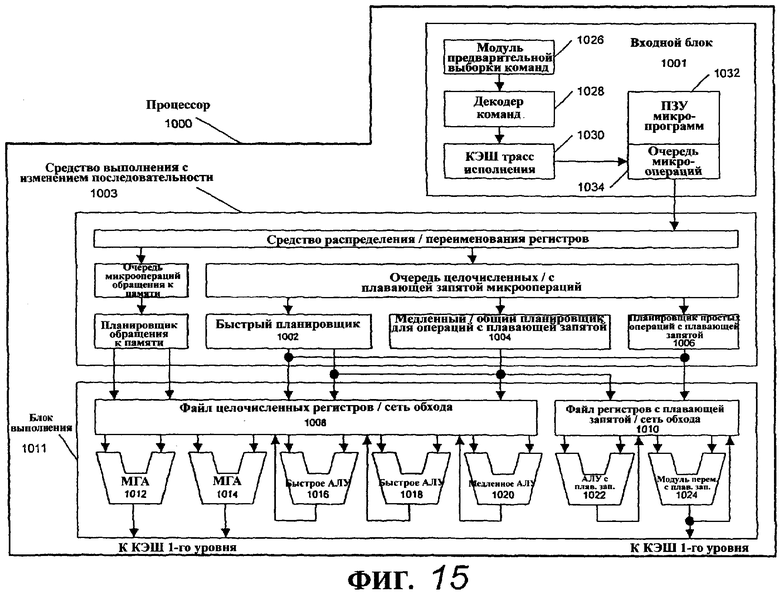

Фиг.15 - структурная схема микроархитектуры процессора одного из вариантов осуществления, которая включает в себя логические схемы для параллельного выполнения операции объединения со сдвигом вправо в соответствии с настоящим изобретением;

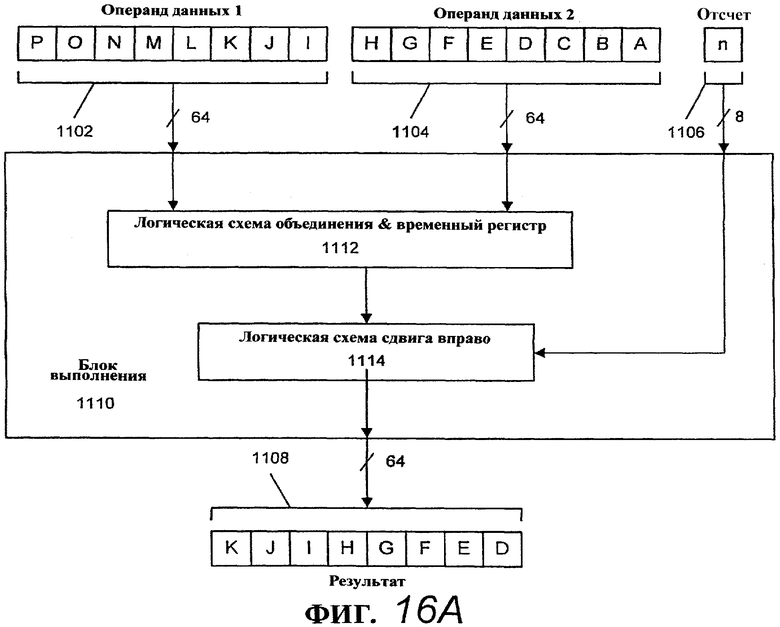

Фиг.16A - структурная схема одного из вариантов осуществления логической схемы для выполнения операции параллельного объединения со сдвигом вправо с операндами данных в соответствии с настоящим изобретением;

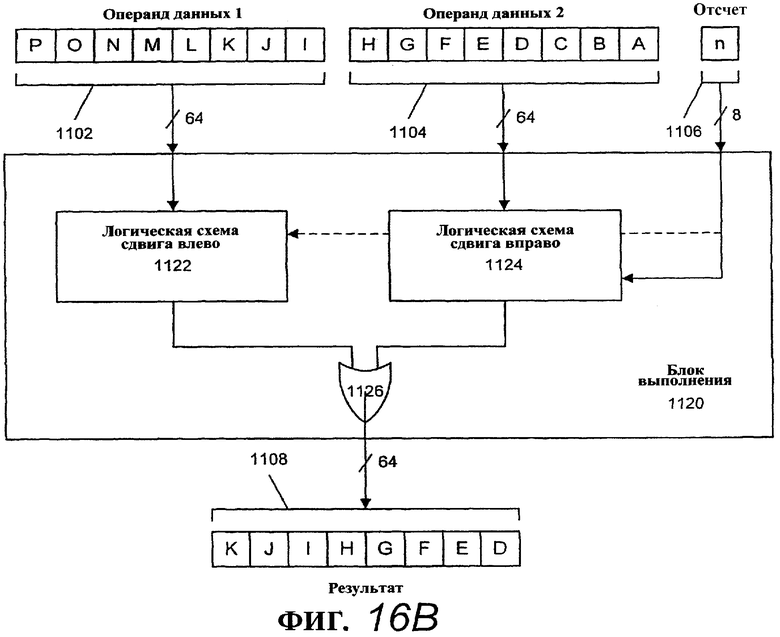

Фиг.16B - структурная схема другого варианта осуществления логической схемы для выполнения операции объединения со сдвигом вправо;

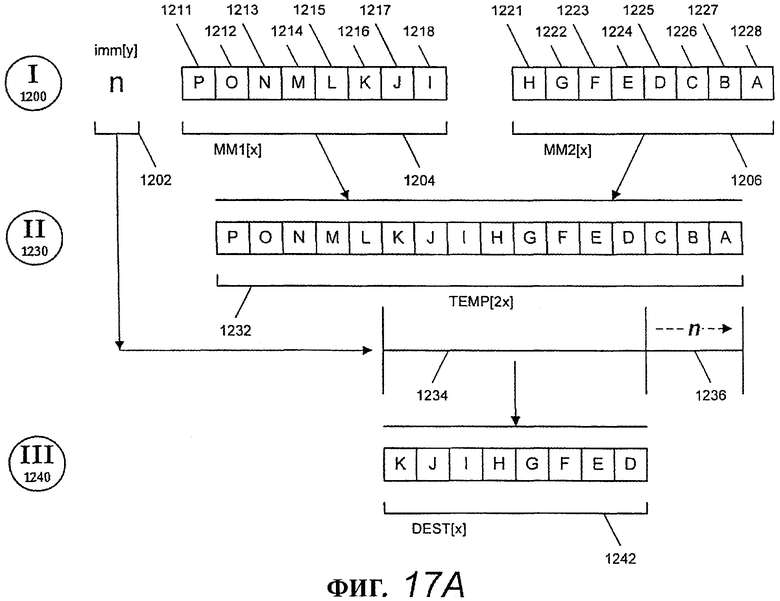

Фиг.17A - иллюстрирующая действия параллельной команды объединения со сдвигом вправо в соответствии с первым вариантом осуществления настоящего изобретения;

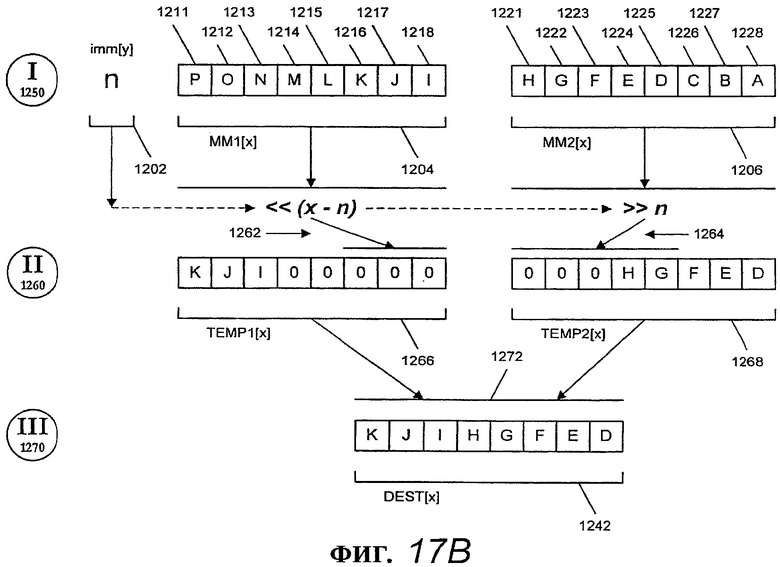

Фиг.17B - иллюстрирующая действия команды объединения со сдвигом вправо в соответствии со вторым вариантом осуществления;

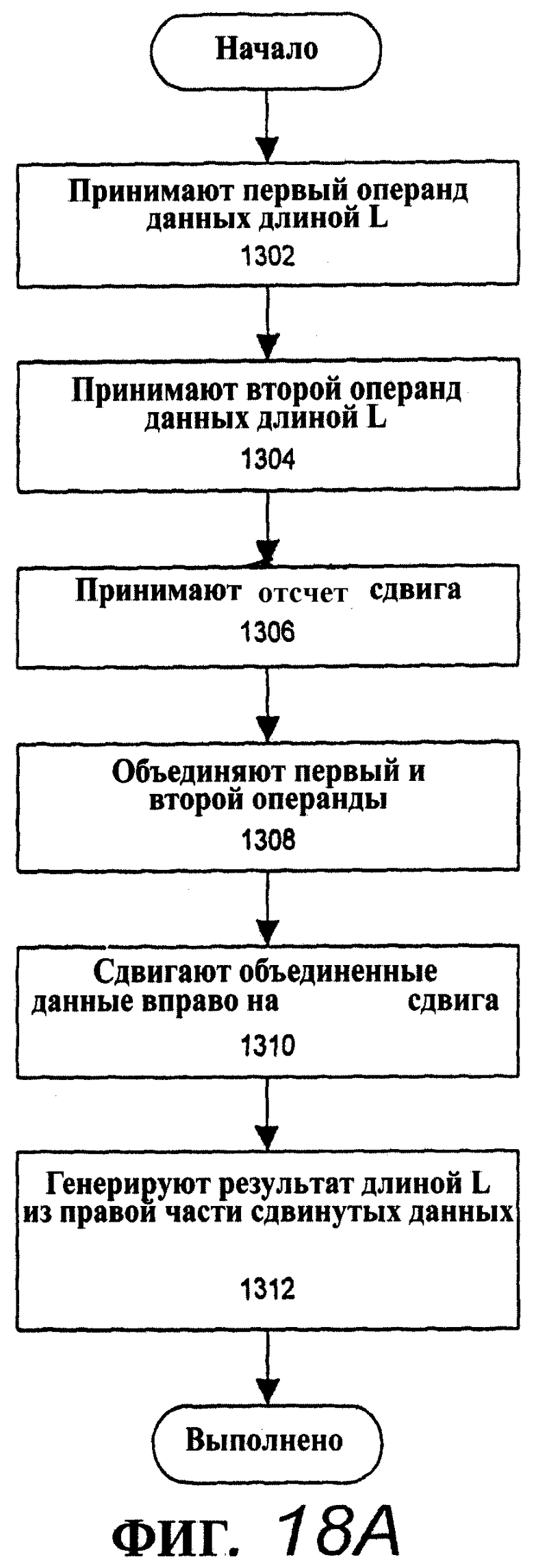

Фиг.18А - последовательность операций одного из вариантов осуществления способа параллельного сдвига вправо и объединения операндов данных;

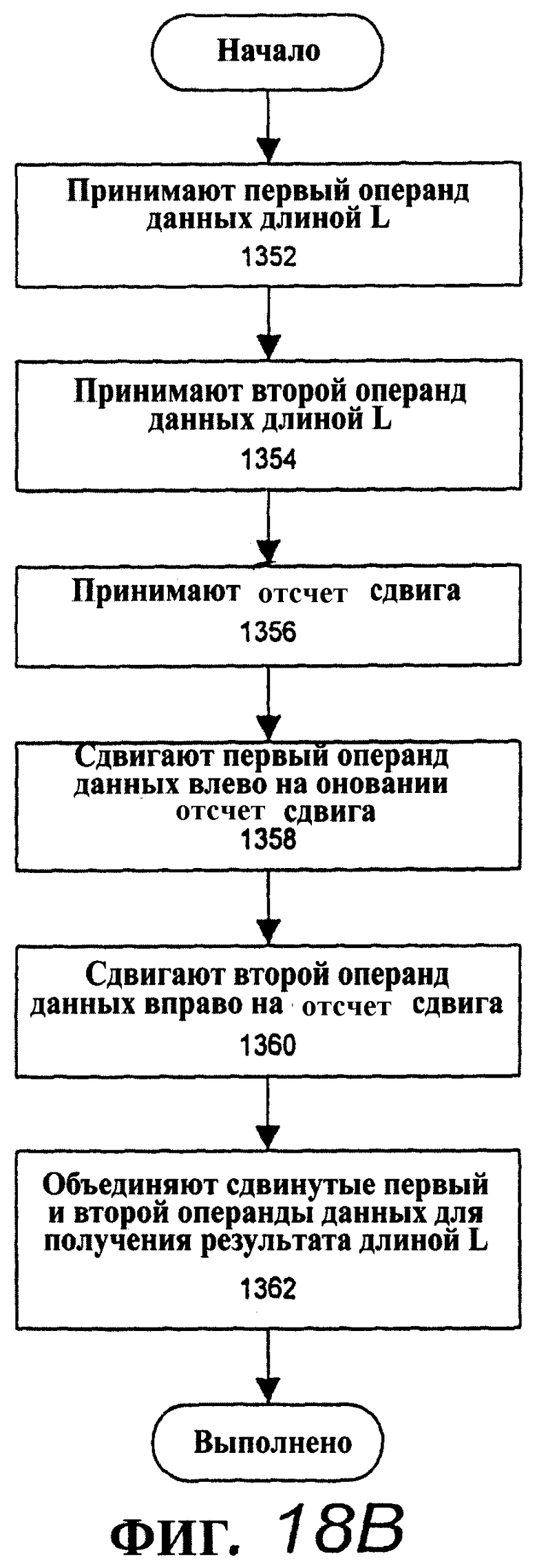

Фиг.18B - последовательность операций другого варианта осуществления способа сдвига вправо и объединения данных;

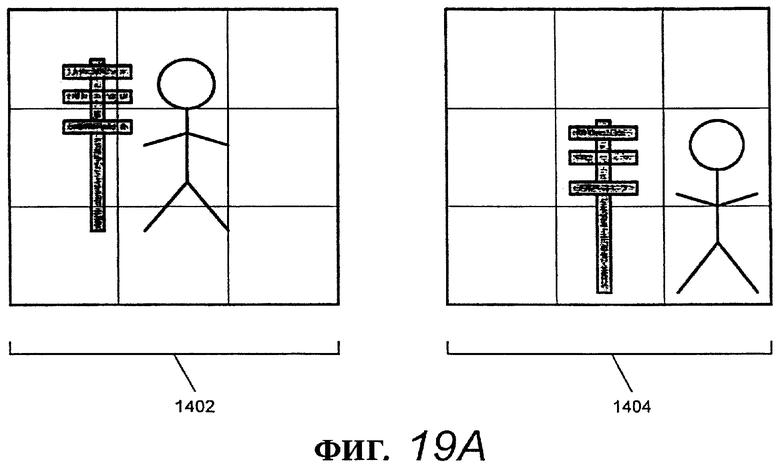

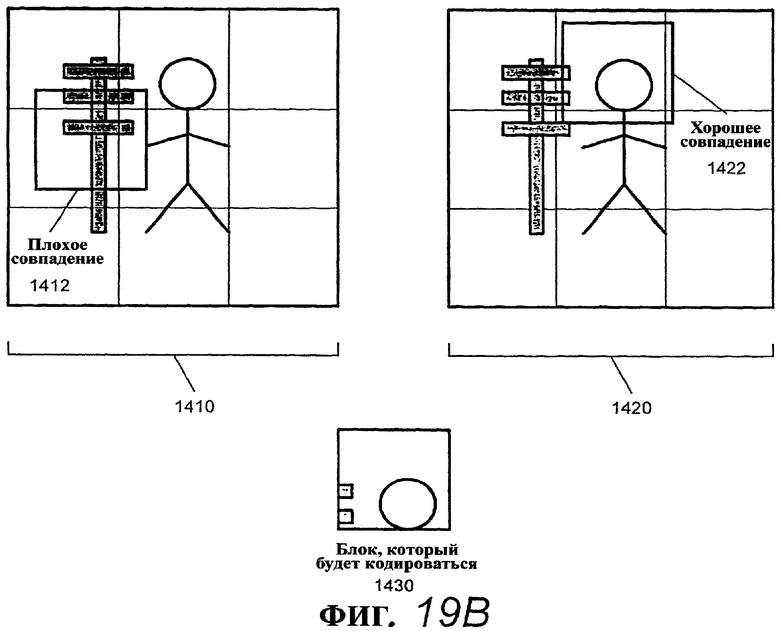

Фиг.19A-B - примеры оценки движения;

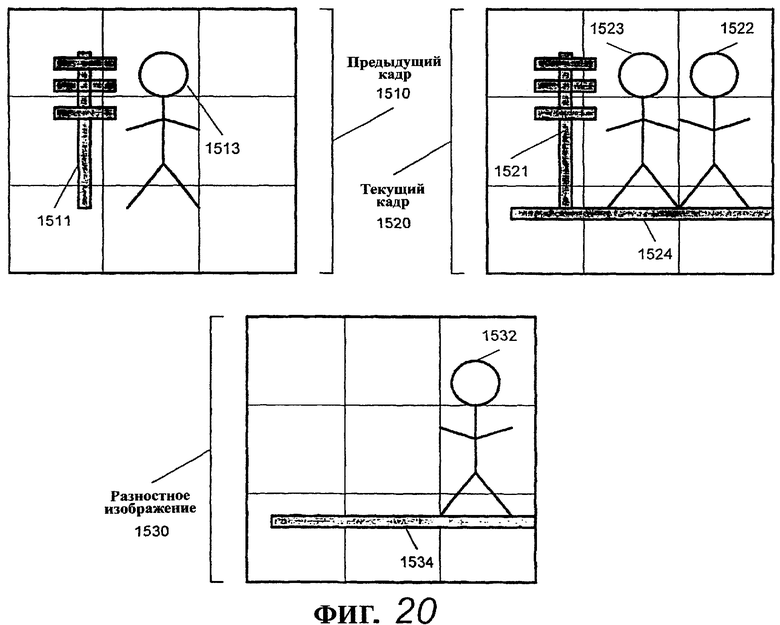

Фиг.20 - пример применения оценки движения и результирующего предсказания;

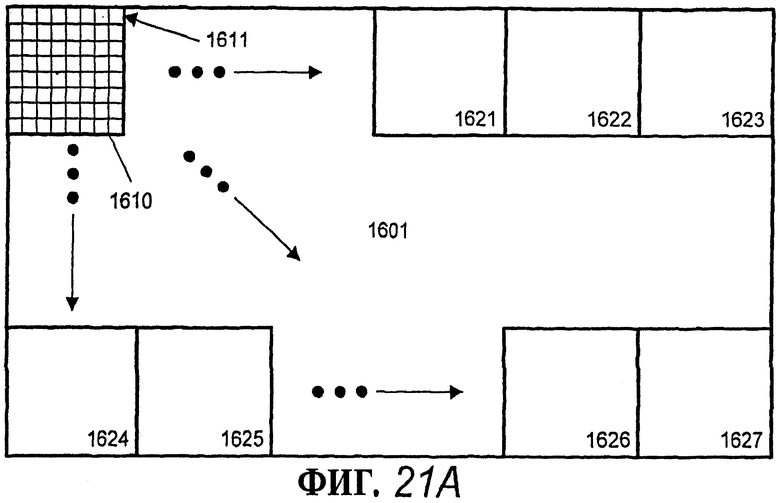

Фиг.21A-B - пример текущего и предыдущего кадров, обрабатываемых во время оценки движения;

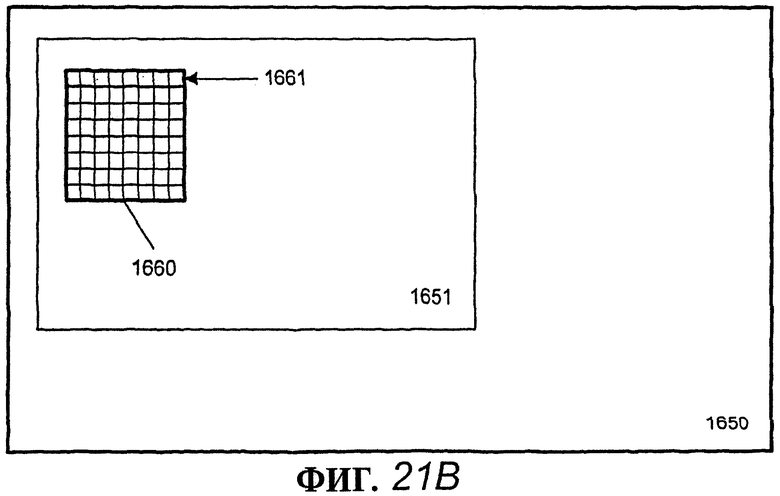

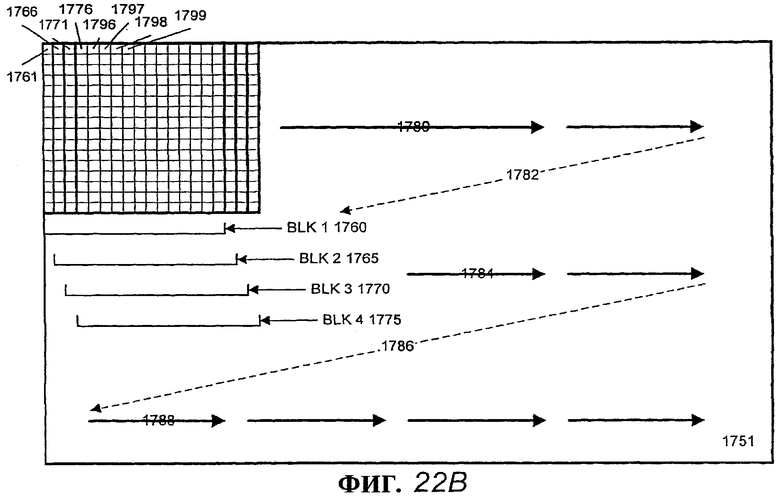

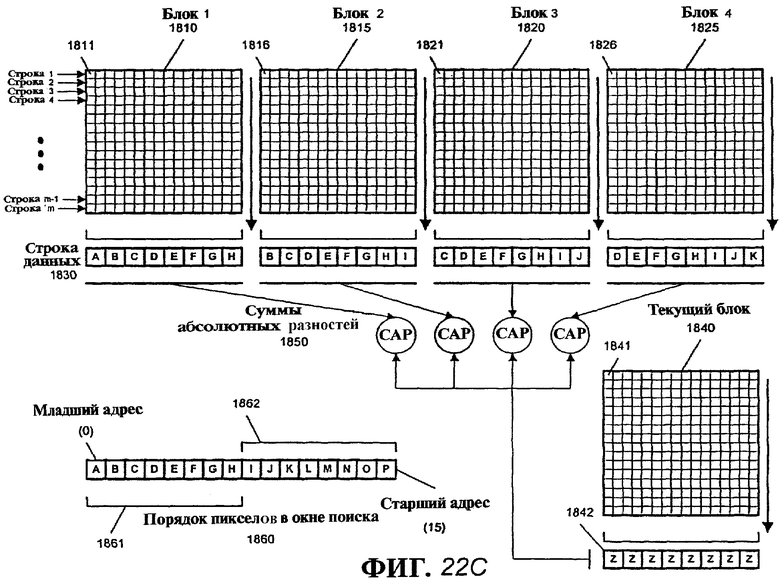

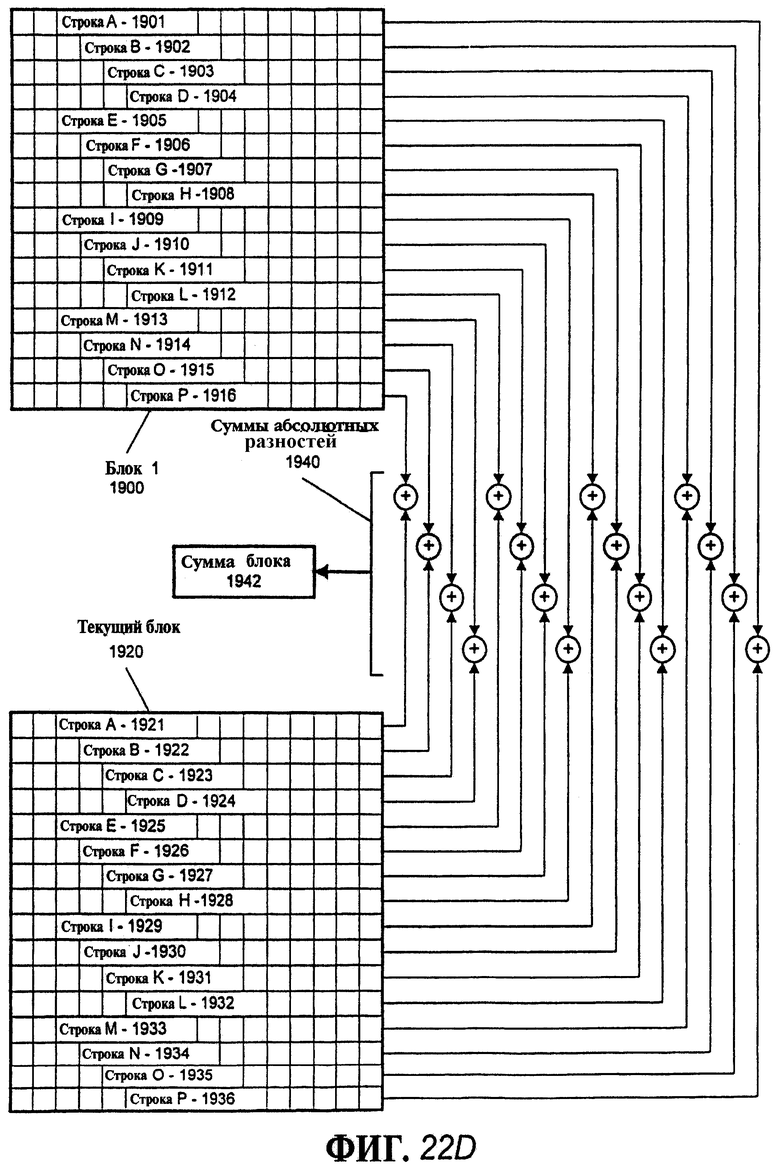

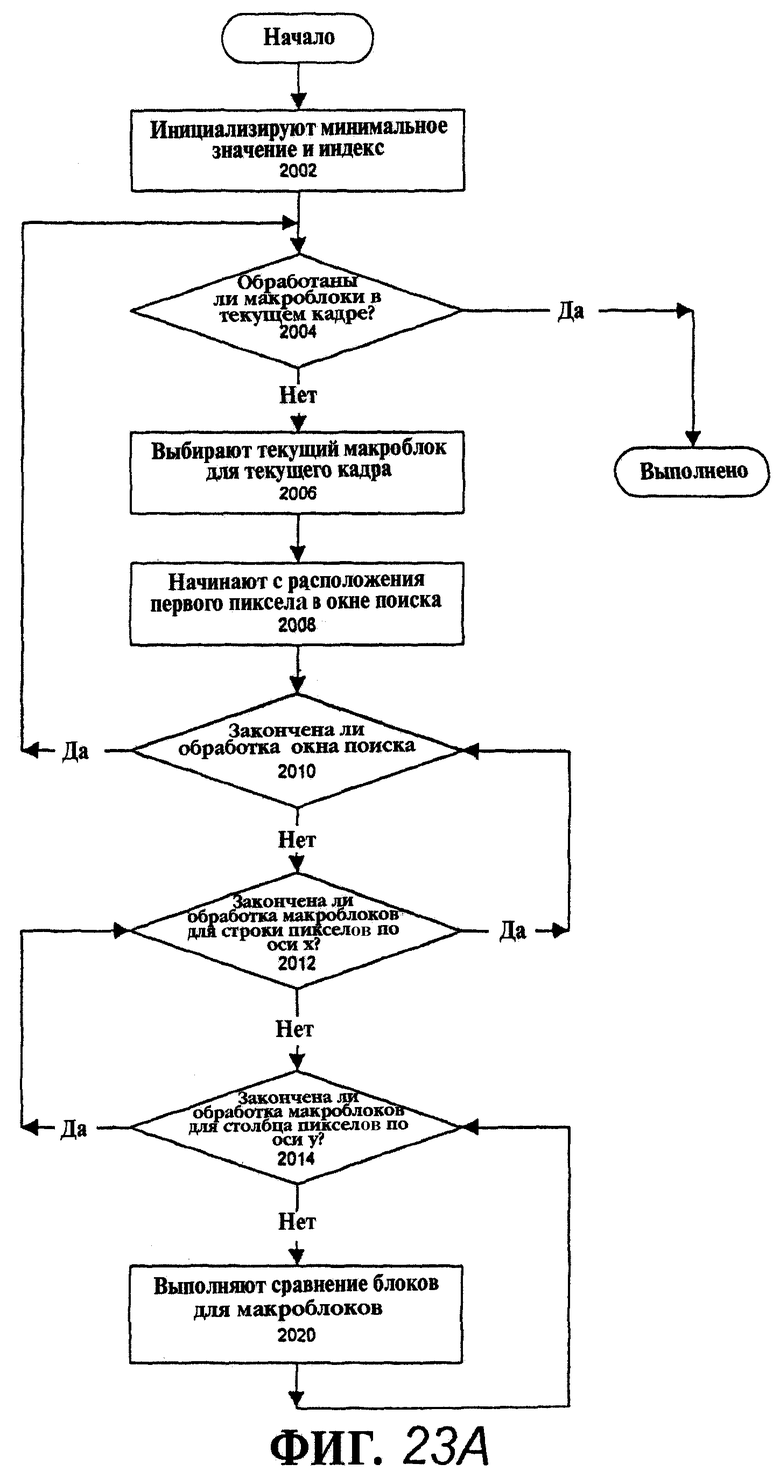

Фиг.22A-D - операции оценки движения в кадрах в соответствии с одним из вариантов осуществления настоящего изобретения; и

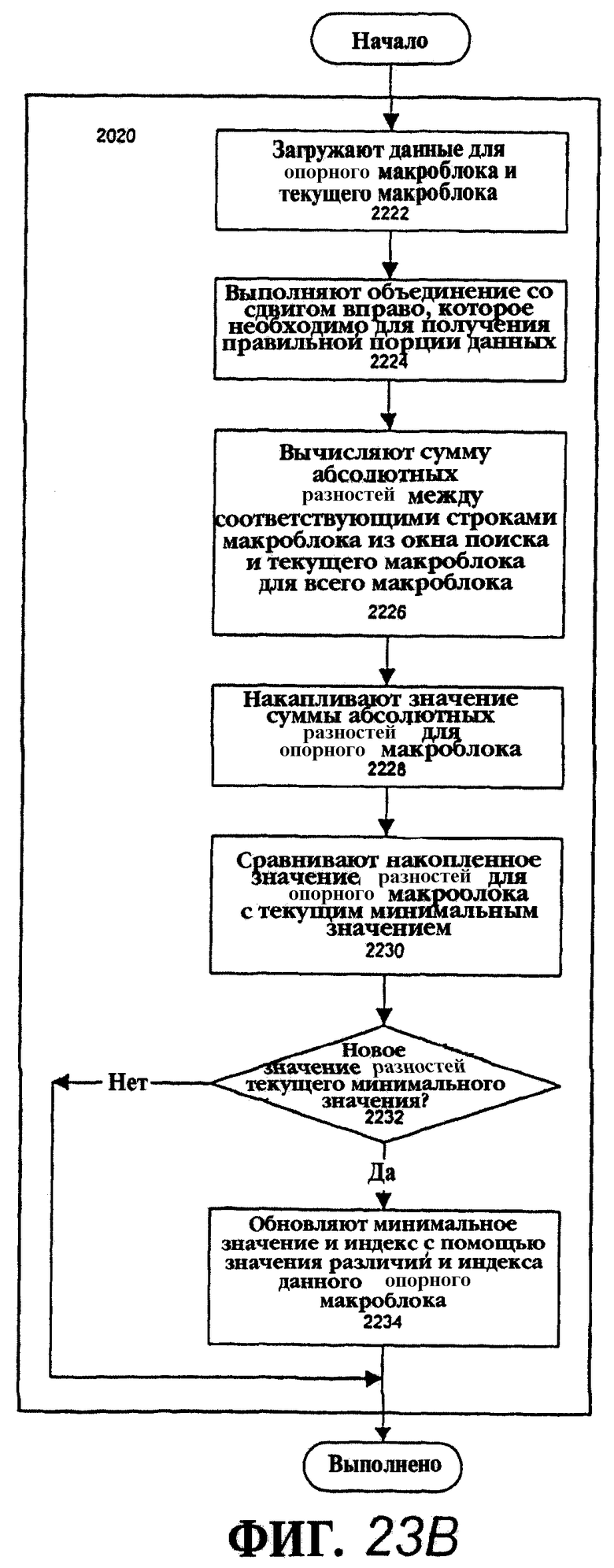

Фиг.23A-B - последовательность операций одного из вариантов осуществления способа предсказания и оценки движения.

ПОДРОБНОЕ ОПИСАНИЕ

Ниже описаны способ и устройство для выполнения параллельного объединения данных со сдвигом вправо. Также описаны способ и устройство для эффективной фильтрации и свертки данных содержимого. Также раскрыты способ и устройство для оценки движения быстрого полного поиска с помощью операций объединения SIMD. Описанные варианты осуществления описаны в контексте микропроцессора, но не ограничены им. Хотя последующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления могут применяться к другим типам интегральных схем и логических устройств. Те же самые методы и идеи настоящего изобретения могут легко применяться к другим типам полупроводниковых схем или устройств, которые могут использовать преимущества более высокой пропускной способности конвейера и улучшенной производительности. Принципы настоящего изобретения применимы к любому процессору или устройству, которые выполняют обработку данных. Однако настоящее изобретение не ограничено процессорами или устройствами, которые выполняют операции с 256-битными, 128-битными, 64-битными, 32-битными или 16-битными данными и могут применяться на любом процессоре и устройстве, в которых необходимо объединение данных со сдвигом вправо.

В последующем описании для целей объяснения многочисленные конкретные подробности изложены для обеспечения полного понимания настоящего изобретения. Однако специалистам должно быть ясно, что эти конкретные подробности не являются необходимыми для практической реализации настоящего изобретения. В других случаях известные электрические структуры и схемы не излагаются подробно, чтобы не затенять сущность настоящего изобретения. Кроме того, в последующем описании приведены примеры, и на чертежах показаны различные примеры для целей иллюстрации. Однако эти примеры не должны рассматриваться в качестве ограничения, поскольку они предназначены только для представления примеров настоящего изобретения, а не для обеспечения исчерпывающего списка всех возможных воплощений настоящего изобретения.

В одном из вариантов осуществления способы настоящего изобретения воплощены в командах, исполняемых компьютером. Команды могут использоваться для выполнения этапов настоящего изобретения в универсальном процессоре или в специализированном процессоре, который запрограммирован с помощью данных команд. Альтернативно, этапы настоящего изобретения могут выполняться определенными аппаратными компонентами, которые содержат логические схемы с постоянными соединениями для выполнения этапов, или комбинацией программируемых компьютерных компонентов и заказных аппаратных компонентов.

Настоящее изобретение может обеспечиваться как компьютерная программа или программное обеспечение, которое может включать в себя считываемый компьютером носитель, который имеет хранящиеся на нем команды, которые могут использоваться для программирования компьютера (или других электронных устройств) для выполнения способа согласно настоящему изобретению. Такое программное обеспечение может храниться в памяти системы. Точно так же код может распространяться через сеть или посредством другого считываемого компьютером носителя. Считываемый компьютером носитель может включать в себя гибкие дискеты, оптические диски, компакт-диски (CD-ROM) и магнитооптические диски, постоянное запоминающее устройство (ПЗУ), оперативную память (ОП), стираемое программируемое постоянное запоминающее устройство (СППЗУ), электрически стираемое программируемое постоянное запоминающее устройство (ЭСППЗУ), магнитные или оптические платы, флэш-память, передачу по Интернет или подобные им средства, но не ограничивается перечисленным.

Соответственно, считываемый компьютером носитель включает в себя любой тип среды передачи данных/машинно-считаемых носителей, которые подходят для хранения или передачи электронных команд или информации в форме, считываемой устройством (например, компьютером). Кроме того, настоящее изобретение может также загружаться как компьютерная программа. Также, программа может пересылаться с удаленного компьютера (например, сервера) на запрашивающий компьютер (например, клиент). Пересылка программы может быть выполнена посредством электрического, оптического, акустического сигналов передачи данных или сигналов передачи данных другой формы, воплощенных в несущей или другой среде распространения сигнала через канал связи (например, модем, сетевое соединение или иное подобное средство).

В современных процессорах используется множество различных исполнительных модулей для обработки и исполнения различных кодов и команд. Не все команды одинаковы, так некоторые быстрее завершаются, в то время как другие могут занимать огромное количество тактовых циклов. Чем быстрее выполняются команды, тем выше производительность в целом процессора. Таким образом было бы выгодно иметь максимально возможное количество команд, которые выполняются с максимально возможной скоростью. Однако существуют некоторые команды, которые отличаются высокой сложностью и требуют больше ресурсов процессора и времени выполнения. Например, существуют команды с плавающей запятой, операции загрузки/хранения, перемещения данных и т.д.

Поскольку все большее количество компьютерных систем используют в приложениях Интернет и мультимедиа, их дополнительная поддержка процессором увеличивается с течением времени. Например, целочисленные/с плавающей запятой команды для обработки в архитектуре с одной командой множеством потоков данных и (SIMD) и расширение для потоковых команд (SIMD) (SSE) являются командами, которые уменьшают общее количество команд, требуемых для выполнения конкретной задачи программы. Эти команды могут увеличивать производительность программного обеспечения, обрабатывая множество элементов данных параллельно. В результате можно достичь увеличения производительности в широком диапазоне приложений, которые включают в себя обработку видеоинформации, речи и изображений/фотографий. Выполнение команд SIMD в микропроцессорах и подобных типах логических схем обычно создает множество проблем. Кроме того, сложность операций SIMD часто требует дополнительных схем для правильной обработки и управления данными.

Варианты осуществления настоящего изобретения обеспечивают способ реализации параллельной команды сдвига вправо как алгоритм, который использует относящиеся к архитектуре SIMD аппаратные средства. Для одного из вариантов осуществления алгоритм основан на принципе сдвига вправо требуемого количества сегментов данных одного операнда в сторону наибольшей значимости второго операнда, когда то же самое количество сегментов данных сдвигают в сторону наименьшей значимости второго операнда. В принципеоперацию объединения со сдвигом вправо можно рассматривать как объединение двух блоков данных в один блок и сдвиг данного объединенного блока для выравнивания сегментов данных в требуемом положении для формирования новой комбинации данных. Таким образом, варианты осуществления алгоритма объединения со сдвигом вправо в соответствии с настоящим изобретением могут осуществляться в процессоре для эффективной поддержки операций SIMD без существенного снижения эффективности в целом.

ВЫЧИСЛИТЕЛЬНАЯ АРХИТЕКТУРА

Фиг.1 показывает компьютерную систему 100, в которой может быть воплощен вариант осуществления настоящего изобретения. Компьютерная система 100 содержит шину 101 для передачи информации и процессор 109, присоединенный к шине 101, для обработки информации. Компьютерная система 100 также включает в себя подсистему памяти 104-107, присоединенную к шине 101, предназначенную для хранения информации и команд для процессора 109.

Процессор 109 включает в себя модуль 130 исполнения, файл 200 регистров, кэш-память 160, декодер 165 и внутреннюю шину 170. Кэш-память 160 присоединена к модулю 130 исполнения и хранит часто используемую и/или недавно использованную информацию для процессора 109. Файл 200 регистров хранит информацию в процессоре 109 и присоединен к модулю 130 исполнения через внутреннюю шину 170. В одном из вариантов осуществления изобретения файл 200 регистров включает в себя регистры мультимедиа, например регистры SIMD, предназначенные для хранения мультимедийной информации. В одном из вариантов осуществления каждый из регистров мультимедиа хранит до ста двадцати восьми битов упакованных данных. Регистры мультимедиа могут быть специализированными регистрами мультимедиа или регистрами, которые используются для хранения мультимедийной и другой информации. В одном из вариантов осуществления регистры мультимедиа хранят данные мультимедиа при выполнении операций мультимедиа и хранят данные с плавающей запятой при выполнении операций с плавающей запятой.

Модуль 130 исполнения оперирует с упакованными данными согласно командам, принятым процессором 109, которые включены в набор 140 упакованных команд. Модуль 130 исполнения также оперирует со скалярными данными согласно командам, реагируемым в универсальных процессорах. Процессор 109 способен поддерживать набор команд микропроцессора Pentium® и набора 140 упакованных команд. За счет включения набора 140 упакованных команд в стандартный набор команд микропроцессора, такой как набор команд микропроцессора Pentium®, команды с упакованными данными могут быть легко помещены в существующее программное обеспечение (ранее написанное для стандартного набора команд микропроцессора). Другие стандартные наборы команд, такие как наборы команд процессоров PowerPC™ и Альфа™, могут также использоваться в соответствии с описанным изобретением. (Pentium® - зарегистрированный товарный знак корпорации Intel. PowerPC™ - товарный знак компаний IBM, APPLE COMPUTER и MOTOROLA. Alpha™ - товарный знак корпорации Digital Equipment.)

В одном из вариантов осуществления набор 140 упакованных команд включает в себя команды (как описано более подробно ниже) для операции 143 пересылки данных (MOVD) и операции 145 перемещения данных (PSHUFD) для организации данных в пределах устройства хранения данных; операцию упакованного умножения с накоплением для первого регистра-источника без знака и второго регистра-источника со знаком (операция 147 PMADDUSBW); операцию упакованного умножения с накоплением (операция 149 PMADDUUBW) для выполнения умножения с накоплением для первого регистра-источника без знака и второго регистра-источника без знака; операцию упакованного умножения с накоплением (операция 151 PMADDSSBW) для первого и второго регистров-источников со знаком, и стандартного умножения с накоплением (операция 153 PMADDWD) для первого и второго регистров-источников со знаком, содержащих 16-разрядные данные. Наконец, система упакованных команд включает в себя команду суммирования смежных значений для суммирования смежных байтов (операция 155 PAADDNB), слов (операция 157 PAADDNWD) и двойных слов (PAADDNDWD 159), двух значений слова (PAADDWD 161), двух слов для получения 16-разрядного результата (операция 163 PAADDNWW), двух учетверенных слов квадраслов для получения результата в виде квадраслова (операция 165 PAADDNDD) и операцию 167 объединения регистров.

За счет включения набора 140 упакованных команд в набор команд универсального процессора 109, вместе с соответствующими схемами для исполнения команд, операции, используемые многими существующими мультимедийными приложениями, могут выполняться с использованием упакованных данных в универсальном процессоре. Таким образом, многие мультимедийные приложения могут выполняться быстрее и эффективнее с использованием полной разрядности шины данных процессора для выполнения операций с упакованными данными. Это устраняет потребность перемещения небольших блоков данных по шине данных процессора для выполнения одной или более операций с одним элементом данных в определенный момент времени.

Согласно Фиг.1 компьютерная система 100, соответствующая настоящему изобретению, может включать в себя устройство 121 отображения, такое как монитор. Устройство 121 отображения может включать в себя промежуточное устройство, такое как буфер кадров. Компьютерная система 100 также включает в себя устройство 122 ввода данных, такое как клавиатура, и устройство 123 управления курсором, такое как «мышь», или шаровой манипулятор («трекбол»), или сенсорная панель. Устройство 121 отображения, устройство 122 ввода данных и устройство 123 управления курсором присоединены к шине 101. Компьютерная система 100 может также включать в себя средство 124 соединения с сетью, так что компьютерная система 100 является частью локальной сети (ЛС) или глобальной сети (ГС).

Дополнительно, компьютерная система 100 может быть присоединена к устройству 125 для записи и/или воспроизведения звука, такому как устройство преобразования в цифровую форму аудиоинформации, соединенное с микрофоном для записи речевого ввода для распознавания речи. Компьютерная система 100 может также включать в себя устройство 126 преобразования в цифровую форму видеоинформации, которое может использоваться для ввода видеоизображений, устройство 127 для создания твердой (документальной) копии, такое как принтер, и устройство 128 CD-ROM. Устройства 124 - 128 также присоединены к шине 101.

Процессор

Фиг.2 показывает подробную схему процессора 109. Процессор 109 может быть осуществлен на одной или более подложках, используя любую из множества технологий процесса, такую как BiCMOS (биполярная комплементарная структура металл-оксид-полупроводник (КМОП)), CMOS (КМОП) и NMOS (n-канальный металл-оксид-полупроводник). Процессор 109 содержит декодер 202 для декодирования сигналов управления и данных, используемых процессором 109. Затем данные могут сохраняться в файле 200 регистров через внутреннюю шину 205. Следует уточнить, что регистры варианта осуществления не ограничиваются конкретным типом схемы. Регистр в рассматриваемом варианте осуществления должен быть способен только обеспечивать хранение и передачу данных и выполнение описанных функций.

В зависимости от типа данных данные могут храниться в целочисленных регистрах 201, регистрах 209, регистрах 208 состояния или регистре 211 указателя команды. Файл 204 регистров может включать в себя другие регистры, например регистр с плавающей запятой. В одном из вариантов осуществления целочисленные регистры 201 хранят тридцатидвухбитные целочисленные данные. В одном из вариантов осуществления регистры 209 содержат восемь регистров мультимедиа R0 212a-R7 212h, например, регистры SIMD, содержащие упакованные данные. Каждый регистр в регистрах 209 имеет длину сто двадцать восемь битов. R1 212a, R2 212b и R3 212c - примеры отдельных регистров в регистрах 209. Тридцать два бита данных в регистрах 209 могут перемещаться в один из целочисленных регистров 201. Точно так же значение целочисленного регистра может быть перемещено в тридцать два бита одного из регистров 209.

Регистры 208 состояния указывают состояние процессора 109. Регистр 211 указателя команды хранит адрес следующей команды, которая будет выполняться. Целочисленные регистры 201, регистры 209, регистры 208 состояния и регистр 211 указатель команды, все они соединяются с внутренней шиной 205. Любые дополнительные регистры также соединяются с внутренней шиной 205.

В другом варианте осуществления некоторые из этих регистров могут использоваться для двух различных типов данных. Например, регистры 209 и целочисленные регистры 201 могут быть объединены, причем каждый регистр может хранить или целочисленные данные, или упакованные данные. В другом варианте осуществления регистры 209 могут использоваться как регистры с плавающей запятой. В данном варианте осуществления в регистрах 209 могут храниться упакованные данные или данные с плавающей запятой. В одном из вариантов осуществления объединенные регистры имеют длину сто двадцать восемь битов, и целые числа представлены как сто двадцать восемь битов. В данном варианте осуществления при хранении упакованных данных и целочисленных данных не требуется, чтобы регистры различали между собой эти два типа данных.

Функциональный модуль 203 выполняет операции, выполняемые процессором 109. Такие операции могут включать в себя сдвиг, сложение, вычитание и умножение и т.д. Функциональный модуль 203 соединяется с внутренней шиной 205. Кэш 160 - дополнительный элемент процессора 109 и может использоваться для кэширования данных и/или сигналов управления, например, из оперативной памяти 104. Кэш 160 соединен с декодером 202 и подсоединен с возможностью приема сигналов 207 управления.

Форматы данных и памяти

Фиг.3 иллюстрирует три типа упакованных данных: упакованный байт 221, упакованное слово 222 и упакованное двойное слово (dword) 223. Упакованный байт 221 имеет длину сто двадцать восемь битов и содержит шестнадцать элементов данных - упакованных байтов. В общем случае, элемент данных - отдельная часть данных, которая хранится в одном регистре (или ячейке памяти) с другими элементами данных той же самой длины. В упакованных последовательностях данных количество элементов данных, хранящихся в регистре, равно 128 битам, деленным на длину в битах элемента данных.

Упакованное слово 222 имеет длину 128 битов и содержит восемь элементов данных упакованного слова. Каждое упакованное слово содержит 16 битов информации. Упакованное двойное слово 223 имеет длину 128 битов и содержит четыре элемента данных упакованного двойного слова. Каждый элемент данных упакованного двойного слова содержит 32 бита информации. Упакованное квадраслово имеет длину 128 битов и содержит два элемента данных упакованного квадраслова.

Фиг.4A - 4C иллюстрируют представление в регистре хранения упакованных данных согласно одному из вариантов осуществления изобретения. Представление 310 в регистре упакованного байта без знака показывает хранение упакованного байта 201 без знака в одном из регистров 209 мультимедиа, который показан на Фиг.4A. Информация для каждого элемента данных - байта - хранится в битах с седьмого по нулевой (с 7 по 0) для нулевого байта, с 15 по 8 для первого байта, с 23 по 16 для второго байта и, наконец, с 120 по 127 для 15-го байта.

Таким образом, все доступные биты используются в регистре. Такая структура памяти увеличивает эффективность хранения данных процессора. Также, при обращении к 16 элементам данных теперь одна операция может одновременно выполняться с 16 элементами данных. Представление 311 в регистре упакованного байта со знаком показывает хранение упакованного байта 221 со знаком. Следует обратить внимание, что восьмой бит каждого элемента данных - байта - является индикатором знака.

Представление 312 в регистре упакованного слова без знака показывает, как слова с седьмого по нулевое хранятся в регистре 209 мультимедиа, который показан на Фиг.4B. Представление 313 в регистре упакованного слова со знаком подобно представлению 312 в регистре упакованного слова без знака. Следует обратить внимание, что 16 бит каждого элемента данных типа слова является индикатором знака. Представление 314 в регистре упакованного двойного слова без знака показывает регистр 209 мультимедиа, хранящий два элемента данных типа двойного слова, как показано на Фиг.4C. Представление 315 в регистре упакованного двойного слова со знаком подобно представлению 314 в регистре упакованного двойного слова без знака. Заметим, что знаковым разрядом является 32-й бит элемента данных типа двойного слова.

Эффективная фильтрация и свертка данных содержимого, как раскрывается в настоящем изобретении, начинаются с загрузки устройства-источника данных коэффициентами фильтрации/свертки и данными. Во многих случаях порядок данных или коэффициентов в устройстве хранения данных, таком, например, как регистр SIMD, требует изменения, прежде чем смогут быть выполнены арифметические вычисления. Соответственно, эффективные вычисления фильтрации и свертки требуют не только соответствующих арифметических команд, но также и эффективных способов организации данных, требуемых для вычислений.

Например, как упомянуто при описании предшествующего уровня техники, изображения фильтруются с помощью замены значения, например, заданного пиксела I на S [I]. Значения пикселов с обеих сторон от пиксела I используют при вычислении фильтра S [I]. Точно так же пикселы с обеих сторон от пиксела I+1 требуются для вычисления S [I+1]. Следовательно, чтобы вычислить результаты фильтрации для больше, чем одного пиксела в регистре SIMD, данные копируются и размещаются в регистре ОКМД для вычисления.

К сожалению, современные вычислительные архитектуры испытывают недостаток в эффективном способе упорядочения данных для всех соответствующих размеров данных в пределах вычислительной архитектуры. Соответственно, как изображено на Фиг.5, настоящее изобретение включает в себя команду перемещения байтов (PSHUFB) 145, которая эффективно упорядочивает данные любого размера. Операция 145 перемещения байтов упорядочивает данные, размеры которых больше, чем байт, поддерживая относительное расположение байтов в пределах больших данных во время операции перемещения. Кроме того, операция 145 перемещения байтов может изменять относительное расположение данных в регистре SIMD и может также копировать данные.

На Фиг.5 показан пример операции 145 перемещения байтов для фильтра с тремя коэффициентами. Используя обычные методы, коэффициенты фильтра (не показаны) применяют к трем пикселам, и затем коэффициенты фильтра перемещают к другому пикселу и снова применяют. Однако для параллельного выполнения этих операций настоящее изобретение описывает новую команду для упорядочения данных. Соответственно, как изображено на Фиг.5, данные 404 формируются в устройстве-адресате 406 хранения данных, которое в одном из вариантов осуществления является устройством-источником 404 хранения данных, используя маску 402 для определения адреса, по которому соответствующие элементы данных хранятся в регистре-адресате 406. В одном из вариантов осуществления конфигурация маски основана на требуемой операции обработки данных, которая может включать в себя, например, операцию фильтрации, операцию свертки или подобные им.

Соответственно, используя маску 402, обработка данных 406 вместе с коэффициентами может выполняться параллельно. В описанном примере запоминающим устройством-источником 404 данных является 128-битный регистр SIMD, который первоначально хранит 16 8-битных пикселов. При использовании фильтра пикселов с тремя коэффициентами четвертый коэффициент устанавливают в ноль. В одном из вариантов осуществления в зависимости от количества элементов данных в запоминающем устройстве-источнике 404 данных регистр-источник 404 может использоваться как устройство-адресат хранения данных, или регистр-адресат, таким образом сокращая количество регистров, которые необходимы в общем случае. Также, перезаписываемые данные в устройстве-источнике 404 хранения данных могут повторно загружаться из памяти или из другого регистра. Кроме того, множество регистров могут использоваться в качестве устройства-источника 404 хранения данных, причем их соответствующие данные формируются в устройстве-адресате 406 хранения данных, когда требуется.

Когда упорядочивание элементов данных, а также коэффициентов закончено, данные и соответствующие коэффициенты должны обрабатываться в соответствии с операцией обработки данных. Специалистам должно быть понятно, что для вычислений фильтрации необходимы операции с различной точностью так же, как для вычислений свертки с использованием различного количества коэффициентов фильтра и различных размеров данных. Базовая операция фильтрации умножает две пары чисел и суммирует их результаты. Эту операцию называют командой умножения с накоплением.

К сожалению, существующая вычислительная архитектура не обеспечивает поддержки эффективного вычисления умножения с накоплением для множества длин массива или фильтра и множества размеров данных с использованием коэффициентов без знака или со знаком. Кроме того, не поддерживаются операции с байтами. В результате, вычислительные системы обычной архитектуры должны преобразовывать 16-битные данные, используя команды распаковывания. Эти виды архитектур вычислительной системы в общем случае включают в себя поддержку операции умножения с накоплением, которые вычисляют произведения 16-разрядных данных в отдельных регистрах и затем складывают смежные произведения для получения 32-разрядного результата. Это решение приемлемо для коэффициентов фильтра для данных, которые требуют 16-разрядной точности, но для 8-битных коэффициентов фильтра для 8-битных данных (что является общим случаем для изображений и видеоинформации) параллелизм уровня команд и данных бесполезен.

Фиг.6 изображает первый регистр-источник 452 и второй регистр-источник 454. В одном из вариантов осуществления первый и второй регистры-источники являются регистрами SIMD длиной N-бит, такие, например, как 128-битные регистры XMM технологии SSE2 корпорации Intel®. Команда умножения с накоплением, выполненная с таким регистром, дает следующие результаты для двух векторов 452 и 454 пикселов, которые сохраняют в регистре-адресате 456. Соответственно, пример показывает команду умножения с накоплением 8-битного байта на 16 слов, которая называется операцией 147 PMADDUSBW (фиг.1), в которой символы U и S в команде относятся к байтам со знаком и без знака. В одном из регистров-источников байты используют со знаком, а в другом они без знака.

В одном из вариантов осуществления настоящего изобретения регистр с данными без знака является адресатом и содержит 16 результатов умножения с накоплением. Причиной для такого выбора является то, что в большинстве реализаций данные используют без знака, а коэффициенты - со знаком. Соответственно, предпочтительно перезаписать данные, потому что менее вероятно, что эти данные будут необходимы в будущих вычислениях. Дополнительные команды умножения с накоплением байтов, как показано на фиг.1, являются операцией 149 PMADDUUBW для байтов без знака в обоих регистрах и операцией 151 PMADDSSBW для байтов со знаком в обоих регистрах-источниках. Команды умножения с накоплением заканчиваются командой 153 PMADDWD, которая применяется к парам 16-разрядных слов со знаком для получения 32-разрядного произведения со знаком.

Как в общем случае операций фильтрации, второй вектор обычно содержит коэффициенты фильтра. Соответственно, чтобы подготовить регистр XMM, коэффициенты могут загружаться в часть регистра и копироваться в остальную часть регистра, используя команду 145 перемещения. Например, как изображено на Фиг.7A, устройство 502 хранения данных коэффициентов, такое, например, как 128-битный регистр XMM, первоначально загружают тремя коэффициентами в ответ на выполнение команды загрузки данных. Однако специалистам должно быть понятно, что коэффициенты фильтра могут быть сформированы в памяти до обработки данных. Также, коэффициенты могут первоначально загружаться, как показано на фиг.7B, на основе их организации в памяти, до операции фильтрации.

Регистр 502 коэффициентов включает в себя коэффициенты фильтра F3, F2 и F1, которые могут кодироваться как байты со знаком или без знака. Когда регистр 502 коэффициентов загружен, существующая команда PSHUFD может использоваться для копирования коэффициентов фильтра в оставшуюся часть регистра коэффициентов для получения следующего результата, как изображено на фиг.7B. Регистр 504 коэффициентов теперь включает в себя перемещенные (скопированные) коэффициенты, как требуется для параллельного выполнения операции обработки данных. Как известно специалистам, фильтры, которые включают в себя три коэффициента, являются обычными в алгоритмах обработки изображений. Однако специалистам должно быть понятно, что некоторые операции фильтрации, такие как JPEG 2000, используют девять и семь 16-разрядных коэффициентов. Соответственно, обработка такого коэффициента превышает емкость регистров коэффициентов, приводя к частично фильтрованному результату. Следовательно, обработка продолжается с использованием каждого коэффициента, пока конечный результат не будет получен.

Фиг.7C иллюстрирует расположение данных пикселов в регистре-источнике 506, которые первоначально содержались в регистре-источнике 404, как показано на Фиг.5, и были перемещены в регистр-адресат 406. Соответственно, в ответ на выполнение операции обработки данных команда PMADDUSBW может использоваться для вычисления суммы этих двух результатов перемножения с сохранением результата в регистре-адресате 510. К сожалению, для завершения вычисления и генерации результатов обработки данных для выбранной операции обработки данных необходимо суммировать смежные пары сумм результатов умножения в регистре-адресате 510.

Соответственно, если сумма команд умножения с накоплением длиннее, чем два пиксела, что имеет место в общем случае, то нужно сложить отдельные суммы. К сожалению, существующая вычислительная архитектура не обеспечивает эффективного способа сложения смежных сумм вследствие того, что смежные суммы находятся в пределах того же самого регистра-адресата. Соответственно, настоящее изобретение использует команды суммирования смежных элементов, результаты которых изображены на Фиг.8A - 8D.

Фиг.8A изображает регистр-адресат 552 после суммирования двух смежных 16-битных значений (операция 157 PADDD2WD) для получения 32-битной суммы. Также, Фиг.8A изображает два смежных 16-битных результата выполнения команды умножения с накоплением, которые суммируют для получения 32-битной суммы 4-байтовых произведений. Фиг.8B изображает команду суммирования смежных значений (операция 157 PAADDD4WD), которая суммирует 4 смежных 16-разрядных значения для получения 32-разрядной суммы. Также, 4 смежных 16-разрядных результата команды умножения с накоплением байтов суммируют для получения 32-разрядной суммы 8-байтовых произведений. Фиг.8C показывает команду суммирования смежных значений (операция 157 PAADD8WD), которая суммирует 8 смежных 16-разрядных значений для получения 32-разрядной суммы. Также, данный пример показывает 8 смежных 16-разрядных результатов операции умножения с накоплением байтов, которые суммируются для получения 32-разрядной суммы 16-байтовых произведений.

Соответственно, выбор команды для выполнения операции суммирования смежных значений основан на количестве звеньев в сумме (N). Например, используя фильтр с тремя коэффициентами, как изображено на Фиг.7A - 7C, первая команда (операция 157 PAADD2WD) получает результат, как показано на Фиг.8D. Однако из-за корреляции между двумя 16-битными векторами (например, первая строка макроблока) пикселов используется последняя команда (операция 157 PAADD8WD), как изображено на Фиг.8C. Такая операция становится все более важной для эффективной реализации, так как регистры ОКМД увеличиваются в размере. Без такой операции требуется много дополнительных команд.

Набор команд суммирования смежных элементов согласно настоящему изобретению поддерживает широкий диапазон количества смежных значений, которые можно суммировать, и весь диапазон обычных типов данных. В одном из вариантов осуществления суммирование смежных 16-битных значений включает в себя набор команд (операция 157 PAADDNWD), диапазон которых начинается с суммирования двух смежных значений (N=2) и количество слагаемых удваивается до четырех (N=4), затем до восьми (N=8) и до общего количества в регистре. Размер данных суммы 16-битных результатов суммирования смежных значений равен 32 битам. В другом варианте осуществления смежные 16-битные значения (операция 161 PAADDWD) суммируются для получения 32-битной суммы.

Этот вариант осуществления не включает в себя никакую другую команду с 16-битным размером данных, потому что команды суммирования смежных элементов с 32-битной входной информацией используются для сложения суммы, сформированной командой, с 16-битными входными значениями. Оба варианта осуществления включают в себя набор команд суммирования смежных 32-битных значений (операция 159 PAADDNDWD), диапазон которых начинается с суммирования двух смежных значений (N=2) и количество слагаемых удваивается до четырех (N=4), затем до восьми (N=8) и т.д. до общего количества в регистре. Размер данных суммы 32-битных результатов операции суммирования смежных значений равен 32 битам. В некоторых случаях результаты не заполняют регистр. Например, для команд, которые показаны на фиг.8A, 8B и 8C, суммирование трех различных смежных значений приводит к 4, 2 и 1 32-разрядному результату. В одном из вариантов осуществления результаты хранятся в младшей, наименее значимой части устройства-адресата хранения данных.

Соответственно, когда существуют два 32-разрядных результата, как показано на Фиг.8B, результаты хранятся в младших 64 битах. В случае одного 32-разрядного результата, как показано на Фиг.8C, результаты хранятся в младших 32 битах. Специалистам должно быть понятно, что некоторые приложения используют сумму смежных байтов. Настоящее изобретение поддерживает суммирование смежных байтов с помощью команды (операция 155 PAADDNB), которая суммирует два смежных байта со знаком, получая 16-разрядное слово, и команды, которая суммирует два смежных байта без знака, получая в результате 16-разрядное слово. Приложения, которые требуют суммирования более двух смежных байтов, суммируют 16-разрядную сумму двух байтов с соответствующим результатом 16-битной операции суммирования смежных значений.

Как только результаты операции обработки данных рассчитаны, следующая операция состоит в направлении результатов назад в запоминающее устройство. Как показано с помощью описанных выше вариантов осуществления, результаты могут кодироваться с 32-разрядной точностью. Поэтому результаты могут записываться назад в память, используя простые операции пересылки, оперирующие с двойными словами, например, описанную выше операцию 143 MOVD, а также логические операции сдвига вправо, действующие на целый регистр (PSRLDQ), логический сдвиг вправо двойного квадраслова. Для записи всех результатов назад в память нужно четыре операции MOVD и три операции PSRLDQ в первом случае (Фиг.8A), две операции MOVD и одна операция PSRLDQ во втором случае (Фиг.8B) и, наконец, только одна операция MOVD в последнем случае, как изображено на Фиг.8C.

К сожалению, хотя операции суммирования смежных значений, как изображено на Фиг.1C, могут выполняться параллельно, вычисления фильтрации в общем случае требуют наличия следующего пиксела изображения. Один или более пикселов должны быть загружены в устройство-источник хранения данных или в регистр. Чтобы избежать загрузки в регистры этих восьми пикселов каждый раз, предложены два решения для этой операции. В одном из вариантов осуществления настоящее изобретение описывает операцию 163 объединения регистров, как изображено на фиг.9A. Для обработки пикселов A1 - A8 в регистре-адресате 606 пикселы A7 - A1 соединяют с пикселем A8 для формирования пикселов A8 - A1 в регистре-адресате 606. Соответственно, операция объединения регистров использует определенное количество байтов для выбранных регистров, которое обеспечивается входным параметром.

Фиг.9B изображает альтернативный вариант осуществления для выполнения операции объединения регистров. Первоначально восемь пикселов загружают в первый регистр-источник 608 (MM0). Затем последующие восемь пикселов загружают во второй регистр-источник 610 (MM1). Затем выполняют операцию перестановки во втором регистре-источнике 610. После выполнения данный регистр 610 копируют в третий регистр-источник (MM2) 612. Затем первый регистр-источник 608 сдвигают вправо на восемь бит. Кроме того, второй регистр-источник 610 и регистр 614 маски объединяют в соответствии с командой упакованное «логическое И» и сохраняют в первом регистре-источнике 608. Затем выполняют операцию «логическое ИЛИ» со вторым регистром-источником 610 и первым регистром-источником 608 для получения следующего результата в регистре-адресате 620, что приводит к операции объединения регистров. Процесс продолжается, как показано, с помощью операции сдвига первого регистра-источника 608. Затем второй регистр-источник 610 сдвигают для получения значения регистра 612. Затем выполняют операцию «логическое И» для регистра 614 маски и второго регистра-источника 612, причем результаты сохраняют в регистре-адресате 622. Наконец, выполняют операцию упакованное «логическое ИЛИ» для второго регистра-источника 612 и первого регистра-источника 608, что приводит к последующей операции объединения регистров в регистре-адресате 624. Далее описаны способы процедур для реализации принципов настоящего изобретения.

Работа

Фиг.10 изображает схему, иллюстрирующую способ 700 для эффективной фильтрации и свертки данных содержимого, например, в компьютерной системе 100, которая изображена на Фиг.1 и 2. Как описано, данные содержимого относятся к данным изображения, аудио-, видеоинформации и речи. Кроме того, настоящее изобретение относится к устройствам хранения данных, которые, как понятно специалистам, включают в себя различные устройства хранения цифровых данных, которые включают в себя, например, регистры данных, такие как 128-битные регистры MMX архитектуры SSE2 Intel®.

Согласно фиг.10 способ начинается на этапе 702, на котором определяют, выполняется ли операция обработки данных. Как описано, операция обработки данных включает в себя операции свертки и фильтрации, которые выполняются с данными пикселов, но не ограничена ими. Если «да», то выполняется этап 704 процесса. На этапе 704 процесса выполняется команда загрузки данных. В ответ на выполнение команды загрузки данных на этапе 706 процесса входной поток данных загружается в устройство-источник 212A хранения данных и вторичное устройство 212B хранения данных, например, как изображено на Фиг.2.

На этапе 708 процесса определяют, выполнила ли операция обработки данных команду перемещения данных. В ответ на выполнение команды перемещения данных на этапе 710 процесса выбранная часть данных из, например, устройства-источника 212B хранения данных формируется в устройстве-адресате хранения данных или в соответствии с упорядочением коэффициентов - в устройстве хранения данных коэффициентов (см. фиг.5). Коэффициенты в устройстве хранения данных коэффициентов упорядочены согласно требуемым вычислениям операции обработки данных (например, как показано на фиг.7A и 7B). В одном из вариантов осуществления коэффициенты упорядочивают в памяти до каких-либо операций фильтрации. Соответственно, коэффициенты могут загружаться в запоминающее устройство данных коэффициентов без необходимости в перемещении (см. фиг.7B).

Как описано выше, упорядочение данных и коэффициентов требуется для реализации параллельных вычислений, как это требуется для операций обработки, как изображено на фиг.7A-7C. Однако так как коэффициенты известны до операции обработки данных, коэффициенты могут упорядочиваться в памяти для обеспечения загрузки в регистр коэффициентов, как упорядочено в памяти, не требуя перемещения коэффициентов во время операции обработки данных. Наконец, на этапе 720 процесса загруженные данные обрабатываются согласно операции обработки данных для получения одного или более результатов обработки данных. После получения результатов операции обработки данных они могут записываться назад в память.

Фиг.11 изображает схему, иллюстрирующую способ 722 обработки данных согласно операции обработки данных. На этапе 724 процесса определяется, выполнила ли операция обработки данных команду умножения с накоплением. В ответ на выполнение команды умножения с накоплением на этапе 726 процесса генерируются множество сумм пар произведений данных в запоминающем устройстве-адресате и коэффициентов в устройстве хранения данных коэффициентов, как изображено на Фиг.1C. Затем на этапе 728 процесса определяют, выполнила ли операция обработки данных команду суммирования смежных значений.

В ответ на выполнение команды суммирования смежных значений на этапе 730 процесса смежные суммы пар произведений в устройстве-адресате хранения данных 510 (фиг.7C) суммируются в ответ на выполнение команды суммирования смежных значений для формирования одного или более результатов операции обработки данных (см. фиг.8D). Однако в некоторых вариантах осуществления, когда количество коэффициентов превышает емкость регистра коэффициентов (см. этап 732 процесса), получают частичные результаты обработки данных. Следовательно, обработка и упорядочение коэффициентов (этап 734 процесса) и данных (этап 736 процесса) продолжается, пока не будут получены заключительные результаты операции обработки данных, как указано на дополнительных этапах процесса 732-736. В противном случае, на этапе 738 процесса сохраняют один или больше результатов операции обработки данных. Наконец, на этапе 790 процесса определяют, закончена ли обработка входного потока данных. Этапы 724-732 процесса повторяют до тех пор, пока обработка входного потока данных не будет закончена. Как только обработка закончена, последовательность операций возвращается к этапу 720 обработки, на котором способ 700 заканчивается.

Фиг.12 изображает схему, показывающую дополнительный способ 740 обработки дополнительных входных данных. На этапе 742 процесса определяется, имеются ли данные в устройстве-источнике 212A хранения данных, к которым не было обращения. Как уже описано, данные, к которым не было обращения, относятся к данным в устройстве-источнике 212A хранения данных, которые не перемещались в устройстве хранения данных для выполнения команды умножения с накоплением. Если устройство хранения данных содержит данные, к которым не было обращения, на этапе 744 процесса из устройства-источника хранения данных выбирают часть данных в качестве выбранных данных. После выбора выполняют этап 786 процесса.

В противном случае, на этапе 746 процесса один или более необработанных элементов данных выбирают из устройства-источника хранения данных, а также как один или более элементов данных из вторичного устройства хранения данных. Как уже описано, необработанные элементы данных относятся к элементам данных, для которых результат операции обработки данных еще не был вычислен. Затем на этапе 780 процесса выполняется команда объединения регистров (см. фиг.9A и 9B), которая соединяет необработанные элементы данных устройства-источника хранения данных с элементами данных, выбранными из вторичного устройства хранения данных для формирования выбранных данных. Затем на этапе 782 процесса данные от вторичного устройства хранения данных перемещаются в устройство-источник хранения данных.

По существу, данные в устройстве-источнике хранения данных больше не требуются, так как к ним всем уже обращались. Соответственно, вторичное устройство хранения данных, которое содержит данные, к которым не было обращения, может использоваться для перезаписи данных в устройство-источник хранения данных. На этапе 784 процесса вторичное устройство хранения данных загружается входным потоком данных из памяти, который требует дополнительной обработки данных, такой как фильтрация или свертка. Наконец, на этапе 786 процесса выбранные данные упорядочиваются в устройстве-адресате хранения данных или в соответствии с упорядочением коэффициентов - в устройстве хранения данных коэффициентов (см. Фиг.5). После выполнения последовательность операций управления возвращается на этап 790 обработки для продолжения обработки выбранных данных, как изображено на фиг.11.

Фиг.13 изображает дополнительный способ 748 для выбора необработанных элементов данных. На этапе 750 процесса определяется, содержит ли устройство-источник хранения данных необработанные данные. Если каждая часть данных в устройстве-источнике хранения данных обработана, выполняется этап 770 процесса. На этапе 770 процесса из вторичного устройства хранения данных выбирается часть данных, которая функционирует как выбранные данные, которые затем обрабатывают в соответствии с операцией обработки данных.

В противном случае, на этапе 752 процесса один или более необработанных элементов данных выбираются из устройства-источника хранения данных. Наконец, на этапе 766 процесса дополнительные элементы данных выбираются из вторичного устройства хранения данных согласно отсчету необработанных элементов данных для формирования выбранных данных. Данные, выбранные для перемещения в устройство-адресат хранения данных до выполнения операции обработки данных, ограничены отсчетом элементов данных на основе числа коэффициентов фильтра. Соответственно, с использованием этого отсчета элементов данных число необработанных элементов данных вычитается из отсчета элементов данных для определения числа элементов, которые надо выбрать из вторичного устройства хранения данных для выполнения операции объединения регистров.

Фиг.14 изображает дополнительный способ 754 для выбора необработанных элементов данных этапа 752 процесса, как изображено на Фиг.13. На этапе 756 процесса из устройства-источника хранения данных выбирают элемент данных. Затем на этапе 758 процесса определяют, был ли результат операции обработки данных вычислен для данного элемента данных. Если такой результат был вычислен, выбранный элемент данных игнорируется. В противном случае, на этапе 760 процесса выбранный элемент данных является необработанным элементом данных и сохраняется. Затем на этапе 762 процесса отсчет необработанных элементов данных получает приращение. Наконец, на этапе 764 процесса этапы 756 - 762 процесса повторяют до тех пор, пока каждый элемент данных в устройстве-источнике хранения данных не будет обработан.

Используя принципы настоящего изобретения, можно избежать ненужных изменений типа данных, что позволяет максимизировать число операций SIMD на одну команду. Кроме того, также достигается существенное сокращение числа тактовых циклов, требуемых для упорядочивания данных для арифметических операций. Соответственно, таблица 1 дает оценочные значения ускорения для различных приложений фильтрации с использованием принципов и команды, раскрытых в настоящем изобретении.

Альтернативные варианты осуществления

Выше описаны различные аспекты реализации вычислительной архитектуры для обеспечения эффективной фильтрации и свертки данных содержимого с использованием регистров SIMD. Однако различные реализации вычислительной архитектуры обеспечивают множество признаков, которые включают в себя, дополняют и/или заменяют описанные выше признаки. Признаки могут быть реализованы как часть вычислительной архитектуры или как часть конкретных программных или аппаратных компонентов в различных реализациях. Кроме того, в предшествующем описании для целей объяснения использована определенная терминология для обеспечения полного понимания изобретения. Однако специалистам будет очевидно, что данные конкретные подробности не требуются для практического использования данного изобретения.

Кроме того, хотя описанный вариант осуществления направлен на систему эффективной фильтрации и свертки данных содержимого с использованием регистров SIMD, специалистам должно быть понятно, что принципы настоящего изобретения могут быть применены к другим системам. Фактически, системы для обработки изображений, аудио и видеоданных охватываются настоящим изобретением без изменения сущности и объема настоящего изобретения. Описанные выше варианты осуществления были выбраны и описаны для наилучшего объяснения принципов изобретения и его практического применения. Эти варианты осуществления были выбраны для того, чтобы таким образом дать возможность другим специалистам лучшим образом использовать данное изобретение и различные варианты его осуществления с различными изменениями, которые подходят для конкретного рассматриваемого применения.

Варианты осуществления настоящего изобретения обеспечивают много преимуществ по сравнению с известными методами. Настоящее изобретение включает в себя возможность эффективного осуществления операции фильтрации/свертки для множества длин массивов и размеров данных и знаков коэффициентов. Эти операции выполняются с использованием небольшого количества команд, которые являются частью небольшой группы команд обработки в архитектуре SIMD. Соответственно, настоящее изобретение позволяет избежать ненужных изменений типа данных. В результате, настоящее изобретение увеличивает количество операций SIMD за одну команду, значительно сокращая количество тактовых циклов, требуемых для упорядочивания данных для арифметических операций, таких как операции умножения с накоплением.

На Фиг.15 представлена структурная схема микроархитектуры процессора одного из вариантов осуществления, который включает в себя логические схемы для выполнения параллельных операций объединения со сдвигом вправо в соответствии с настоящим изобретением. Операция объединения со сдвигом вправо может также упоминаться, как операция объединения регистров и команда объединения регистров, как в приведенном выше обсуждении. Для одного из вариантов осуществления команды объединения со сдвигом вправо (PSRMRG), команда дает те же самые результаты, что операция 167 объединения регистров на Фиг.1, 9A и 9B. Входной блок 1001 упорядоченной обработки является частью процессора 1000, которая выбирает макрокоманды, которые будут выполняться, и подготавливает их для последующего использования в конвейерной обработке процессора. Входной блок данного варианта осуществления включает в себя несколько модулей. Модуль 1026 предварительной выборки команд выбирает макрокоманды из памяти и передает их на декодер 1028 команд, который в свою очередь декодирует их в примитивы, которые называют микрокомандами или микрооперациями (также называют МОП), исполнение которых понятно машине. Трассировочный кэш 1030 берет декодированные микрооперации и транслирует их в программно упорядоченные последовательности, или трассы, в очереди 1034 микроопераций для исполнения. Когда трассировочный кэш 1030 обнаруживает сложную макрокоманду, ПЗУ 1032 микропрограмм обеспечивает микрооперации, которые нужны для завершения операции.

Многие макрокоманды преобразуются в одну микрооперацию, а другие нуждаются в нескольких микрооперациях для завершения всей операции. В данном варианте осуществления, если для завершения макрокоманды необходимы больше, чем четыре микрокоманды, то декодер 1028 обращается к ПЗУ 1032 микропрограммы для выполнения макрокоманды. В одном из вариантов осуществления команда для алгоритма параллельного объединения со сдвигом вправо может храниться в пределах ПЗУ 1032 микропрограмм, когда для выполнения операции необходимо множество микроопераций. Трассировочный кэш 1030 ссылается на точку входа в программируемую логическую матрицу (ПЛМ, PLA) для определения правильного указателя микрокоманды для считывания последовательности микропрограммы для разделенных алгоритмов в ПЗУ 1032 микропрограмм. После того как ПЗУ 1032 микропрограмм закончит упорядочивание микроопераций для текущей макрокоманды, входной блок 1001 устройства возобновляет выборку микроопераций из трассировочного кэша 1030.

Некоторые команды SIMD и другие мультимедийные типы команд рассматриваются как сложные команды. Большинство команд, относящихся к командам с плавающей запятой также являются сложными командами. Когда декодер 1028 команд обнаруживает сложную макрокоманду, осуществляется обращение в ПЗУ 1032 микропрограмм в соответствующие ячейки для извлечения последовательности микропрограммы для данной макрокоманды. Различные микрооперации, необходимые для выполнения этой макрокоманды, передаются на средство 1003 исполнения с изменением последовательности для исполнения в соответствующих модулях исполнения: целочисленном и с плавающей запятой.

В средстве 1003 исполнения с изменением последовательности микрокоманды подготавливаются к исполнению. Логические схемы исполнения с изменением последовательности имеют множество буферов для сглаживания и переупорядочивания потока микрокоманд для оптимизации производительности, когда они продвигаются вниз по конвейеру и планируются для исполнения. Логические схемы средства распределения распределяют машинные буфера и ресурсы, требуемые каждой микрооперации для исполнения. Логические схемы переименования регистров переименовывают логические регистры в записи в файле регистров. Средство распределения также распределяет запись для каждой микрооперации в одну из двух очередей микроопераций, одна - для операций с памятью и одна - для операций без обращения к памяти, перед следующими планировщиками команд: планировщик памяти, быстрый планировщик 1002, медленный/общий планировщик 1004 для операций с плавающей запятой и простой планировщик 1006 для операций с плавающей запятой. Планировщики 1002, 1004, 1006 микроопераций определяют, когда микрооперация готова для исполнения на основании готовности зависимых от них регистров-источников входных операндов и доступности ресурсов выполнения, требуемых микрооперации для завершения операции. Быстрый планировщик 1002 для данного варианта осуществления может выполнять планирование на каждую половину основного тактового цикла, в то время как другие планировщики могут выполнять планирование только один раз за основной тактовый цикл процессора. Планировщики решают конфликты для портов отправки при планировании микроопераций для выполнения.

Файлы 1008, 1010 регистров находятся между планировщиками 1002, 1004, 1006 и модулями 1012, 1014, 1016, 1018, 1020, 1022, 1024 исполнения в блоке 1011 исполнения. Существуют отдельные файлы 1008, 1010 регистров для операций с целыми числами и с плавающей запятой соответственно. Каждый файл 1008, 1010 регистров данного варианта осуществления также включает в себя сеть обхода, которая может обойти или передать только что завершенные результаты, которые еще не были записаны в файл регистров, к новой зависимой микрооперации. Файл 1008 целочисленных регистров и файл 1010 регистров с плавающей запятой также способны передавать данные друг другу. Для одного из вариантов осуществления файл 1008 целочисленных регистров разбит на два отдельных файла регистров, один файл регистров для младших 32 разрядов данных и второй файл регистров для старших 32 разрядов данных. Файл 1010 регистров с плавающей запятой одного из вариантов осуществления содержит записи длиной 128 битов, потому что команды с плавающей запятой в типовом случае имеют операнды длиной от 64 до 128 битов.

Блок 1011 исполнения содержит модули 1012, 1014, 1016, 1018, 1020, 1022, 1024 исполнения, где команды фактически исполняются. Эта часть включает в себя файлы 1008, 1010 регистров, которые хранят данные значений целочисленных операндов и операндов с плавающей запятой, которые необходимы для выполнения микрокоманд. Процессор 1000 данного варианта осуществления состоит из множества модулей исполнения: модуль генерации адресов (МГА, AGU) 1012, МГА 1014, быстродействующее арифметико-логическое устройство 1016, быстродействующее арифметико-логическое устройство 1018, медленнодействующее арифметико-логическое устройство 1020, арифметико-логическое устройство 1022 с плавающей запятой, модуль 1024 перемещения с плавающей запятой. Для данного варианта осуществления модули 1022, 1024 исполнения с плавающей запятой исполняют операции MMX, ОКМД и SSE с плавающей запятой. Арифметико-логическое устройство 322 с плавающей запятой данного варианта осуществления включает в себя модуль деления 64 бита на 64 бита с плавающей запятой для исполнения микроопераций деления, извлечения квадратного корня и определения остатка. Для вариантов осуществления настоящего изобретения любое действие с использованием значения с плавающей запятой осуществляется с использованием аппаратных средств с плавающей запятой. Например, преобразования из целочисленного формата в формат с плавающей запятой предусматривают использование файла регистров с плавающей запятой. Точно так же операция деления с плавающей запятой осуществляется в модуле деления с плавающей запятой. С другой стороны, числа, которые не являются числами с плавающей запятой, и целые числа обрабатываются с помощью целочисленных аппаратных средств. Простые, очень частые операции АЛУ направляются в быстродействующие модули 1016, 1018 исполнения АЛУ. Быстродействующие АЛУ 1016, 1018 данного варианта осуществления могут выполнять быстрые операции с эффективным временем ожидания, равным половине тактового цикла. Для одного из вариантов осуществления самые сложные целочисленные операции направляются в медленнодействующие АЛУ 1020, поскольку медленнодействующие АЛУ 1020 включает в себя целочисленные аппаратные средства выполнения для операций с длительным временем ожидания, таких как умножение, сдвиги, обработка логики флажков и обработка переходов. Операции загрузить/сохранить в памяти выполняют МГА 1012, 1014. Для данного варианта осуществления целочисленные АЛУ 1016, 1018, 1020 описаны в контексте выполнения целочисленных операций с 64-битными операндами данных. В альтернативных вариантах осуществления АЛУ 1016, 1018, 1020 могут быть реализованы для поддержки различной разрядности, включая 16, 32, 128, 256 битов и т.д. Точно так же модули 1022, 1024 для операций с плавающей запятой могут быть осуществлены для поддержки диапазона операндов с различным количеством битов. Для одного из вариантов осуществления модули 1022, 1024 для операций с плавающей запятой могут обрабатывать упакованные операнды данных длиной 128 битов во взаимосвязи с SIMD и мультимедийными командами.

В данном варианте осуществления планировщики 1002, 1004, 1006 микроопераций осуществляют диспетчеризацию зависимых операций прежде, чем порождающая загрузка закончит выполняться. Поскольку микрооперации в процессоре 1000 планируются и выполняются по предположению, процессор 1000 также включает в себя логические схемы для обработки пропусков в памяти. Если загружаемые данные отсутствуют в кэше данных, то в конвейерной обработке могут иметь место зависимые операции, которые вышли из планировщика с временно неправильными данными. Средство повторного исполнения отслеживает и повторно исполняет команды, которые используют неправильные данные. Должны повторно исполняться только зависимые операции, а независимые операции имеют возможность завершения. Планировщики и средство повторного исполнения одного из вариантов осуществления процессора также предназначены для исполнения последовательности команд для целочисленных операций деления с расширенной точностью.

Термин «регистры» используется для обращения к встроенным ячейкам памяти процессора, которые используются как часть макрокоманд для идентификации операндов. Другими словами, упоминаемые регистры «видимы» извне процессора (с точки зрения программиста). Однако описанные регистры могут быть реализованы с помощью схем в процессоре с использованием различных методов, например, выделенных физических регистров, динамически распределяемых физических регистров, использующих переименование регистра, комбинаций выделенных и динамически распределяемых физических регистров и т.д. Для последующего обсуждения понимается, что регистры являются регистрами данных, предназначенными для хранения упакованных данных, например, имеющие длину 64 бита регистры MMX™ (регистры mm) в микропроцессорах, реализованных по технологии MMX корпорации Intel, Санта-Клара, Калифорния. Эти регистры MMX, существующие и в целочисленной форме, и в форме с плавающей запятой, могут использоваться с упакованными элементами данных, которые сопровождают команды SIMD и SSE. Точно так же регистры XMM длиной 128 битов, относящиеся к технологии SSE2, могут использоваться для хранения таких операндов упакованных данных.

В примерах, представленных на следующих чертежах, описан ряд операндов данных. Для простоты, сегменты данных помечены от буквы А в алфавитном порядке, причем сегмент А находится в самом младшем адресе, а сегмент Z должен был бы находиться в самом старшем адресе. Таким образом, А может находиться по адресу 0, B - по адресу 1, C - по адресу 3 и т.д. Хотя последовательности данных в некоторых из примеров показаны буквами, размещаемыми в обратном алфавитном порядке, адресация все равно начинается с А в 0, B в 1 и т.д. В принципе, операция сдвига вправо, такая как объединение со сдвигом вправо для одного из вариантов осуществления, влечет за собой сдвиг вправо сегментов данных с младшим адресом, если последовательность соответствует D, C, B, A. Таким образом, сдвиг вправо просто сдвигает элементы данных блока данных направо относительно постоянной линии. Кроме того, операция объединения со сдвигом вправо может в принципе сдвинуть вправо крайние правые сегменты данных одного операнда в левую сторону другого операнда данных, как если бы эти два операнда были бы непрерывными.

Фиг.16A представлена структурная схема одного из вариантов осуществления логической схемы для выполнения параллельной операции объединения со сдвигом вправо с операндами данных в соответствии с настоящим изобретением. Команда (PSRMRG) для операции объединения со сдвигом вправо (также сдвиг регистра) для данного варианта осуществления начинается с трех частей информации: первый операнд 1102 данных, второй операнд 1104 данных и счетчик 1106 сдвига. В одном из вариантов осуществления команда сдвига PSRMRG декодируется в одну микрооперацию. В альтернативном варианте осуществления команда может декодироваться в различное количество микроопераций для выполнения операции объединения со сдвигом с операндами данных. Для данного примера операнды 1102, 1104 данных являются частями 64-битных данных, хранящихся в регистре/памяти, а отсчет 1106 сдвига является непосредственным значением длиной 8 битов. В зависимости от конкретной реализации операнды данных и отсчет сдвига могут иметь другие размеры, например, 128/256 битов и 16 битов соответственно. Первый операнд 1102 в данном примере состоит из восьми сегментов данных: P, O, N, М, L, K, J и I. Второй операнд 1104 состоит также из восьми сегментов данных: H, G, F, E, D, C, B и A. Сегменты данных имеют равную длину, и каждый содержит один байт (8 битов) данных. Однако другой вариант осуществления настоящего изобретения работает с более длинными 128-битовыми операндами, причем каждый из сегментов данных состоит из одного байта (8 битов), и операнд длиной 128 битов имеет шестнадцать сегментов данных длиной один байт. Точно так же, если каждый сегмент данных является двойным словом (32 бита) или квадрасловом (64 бита), то 128-битный операнд имеет четыре сегмента данных длиной в двойное слово или два сегмента данных длиной в квадраслово соответственно. Таким образом варианты осуществления настоящего изобретения не ограничены определенной длиной операндов данных, сегментов данных или отсчет сдвига и могут иметь размер, соответствующий каждой реализации.

Операнды 1102, 1104 могут находиться или в регистре, или в ячейке памяти, или файле регистров, или в комбинации указанных средств. Операнды 1102, 1104 данных и отсчет 1106 подаются на модуль 1110 исполнения в процессоре вместе с командой объединения со сдвигом вправо. Ко времени, когда команда объединения со сдвигом вправо достигает модуля 1110 исполнения, команда должна быть декодирована ранее в конвейере процессора. Таким образом команда объединения со сдвигом вправо может быть в форме микрооперации (МОП) или в некотором другом декодированном формате. Для данного варианта осуществления два операнда 1102, 1104 данных принимаются в логической схеме объединения и временном регистре. Логическая схема объединения объединяет/присоединяет сегменты данных для этих двух операндов и размещает новый блок данных во временном регистре. Новый блок данных состоит из шестнадцати сегментов данных: P, O, N, М, L, K, J, I, H, G, F, E, D, C, B, A. Поскольку данный пример работает с операндами длиной 64 бита, временный регистр должен содержать объединенные данные длиной 128 битов. Для операндов данных длиной 128 битов необходим временный регистр длиной 256 битов.

Логическая схема 1114 сдвига вправо в модуле 1110 исполнения берет содержимое временного регистра и выполняет логический сдвиг вправо блока данных на n сегментов данных, как запрашивается отсчетом 1106. В данном варианте осуществления отсчет 1106 указывает количество байтов, на которые будет выполнен сдвиг вправо. В зависимости от конкретной реализации отсчет 1106 может также использоваться для указания количества битов, полубайтов, слов, двойных слов, квадраслов и т.д., на которые будет выполнен сдвиг, в зависимости от степени детализации сегментов данных. Для данного примера значение n равно 3, так что содержимое временного регистра сдвигается на три байта. Если каждый сегмент данных имеет длину слова или двойного слова, то отсчет может указывать количество слов или двойных слов, на которые будет выполнен сдвиг, соответственно. Для данного варианта осуществления 0 сдвигаются с левой стороны временного регистра для заполнения освобождающегося пространства, по мере того как данные в регистре сдвигаются вправо. Таким образом, если отсчет 1106 сдвига больше, чем количество сегментов данных в операнде данных (в данном случае восемь), то один или более 0 могут появиться в результирующем значении 1108. Кроме того, если отсчет 1106 сдвига равен или превышает общее количество сегментов данных для обоих операндов, то результат будет содержать все 0, поскольку все сегменты данных будут сдвинуты и выведены. Логическая схема 1114 сдвига вправо выводит соответствующее количество сегментов данных из временного регистра в качестве результата 1108. В другом варианте осуществления схема может включать в себя мультиплексор вывода или регистр-защелку после логической схемы сдвига вправо для вывода результирующего значения. Для данного примера результат имеет длину 64 бита и включает в себя восемь байтов. При операции объединения со сдвигом вправо с этими двумя операндами 1102, 1104 данных результат состоит из следующих восьми сегментов данных: K, J, I, H, G, F, E и D. На фиг.16B представлена структурная схема другого варианта осуществления логической схемы для выполнения операции объединения со сдвигом вправо. Подобно предыдущему примеру на Фиг.16A, операция объединения со сдвигом вправо данного варианта осуществления начинается с трех частей информации: первый операнд 1102 данных длиной 64 бита, второй операнд 1104 данных длиной 64 бита и отсчет 1106 сдвига длиной 8 битов. Отсчет 1106 сдвига указывает, на сколько разрядов нужно сдвинуть сегменты данных. Для данного варианта осуществления отсчет 1106 устанавливается в количестве байтов. В альтернативном варианте осуществления отсчет может указывать количество битов, полубайтов, слов, двойных слов или квадраслов, на которые будет выполнен сдвиг данных. В данном примере первый операнд 1102 состоит из восьми имеющих одинаковую длину в один байт сегментов данных (H, G, F, E, D, C, B, A), и второй операнд 1104 состоит из восьми сегментов данных (P, O, N, М, L, K, J, I). Счетчик n равен 3. Другой вариант осуществления изобретения может работать с операндами и сегментами данных альтернативного размера, например, с операндами длиной 128/256/512 битов и сегментами данных размером бит/байт/слово/двойное слово/квадраслово и отсчет сдвига длиной 8/16/32 битов. Таким образом варианты осуществления настоящего изобретения не ограничены определенной длиной операндов данных, сегментов данных или счетчика сдвига и могут иметь размер, соответствующий каждой реализации.

Операнды 1102, 1104 данных и отсчет 1106 подаются на модуль 1120 исполнения в процессоре вместе с командой объединения со сдвигом вправо. Для данного варианта осуществления первый операнд 1102 данных и второй операнд 1104 данных принимаются логической схемой 1122 сдвига влево и логической схемой 1124 сдвига вправо соответственно. Отсчет 1106 также подается на логические схемы 1122, 1124 сдвига. Логическая схема 1122 сдвига сдвигает влево сегменты данных для первого операнда 1102 на количество сегментов, равное «количеству сегментов данных в первом операнде - n». По мере того как сегменты данных сдвигаются влево, с правой стороны вводятся 0 для заполнения освобождающегося пространства. В данном случае существует восемь сегментов данных, так что первый операнд 1102 сдвигается влево на восемь минус три, или пять разрядов. Первый операнд 1102 сдвигается на значение этой разницы для достижения правильного выравнивания данных для объединения в схеме 1126 «логическое ИЛИ». После сдвига влево первый операнд данных принимает вид: K, J, I, 0, 0, 0, 0, 0. Если отсчет 1106 больше количества сегментов данных в операнде, то вычисление сдвига влево может привести к отрицательному числу, указывая на отрицательный сдвиг влево. Логический сдвиг влево с отрицательным отсчетом интерпретируется как сдвиг в отрицательном направлении и по существу логический сдвиг вправо. Отрицательный сдвиг влево вводит 0 с левой стороны первого операнда 1102.

Точно так же логическая схема 1124 сдвига вправо сегментов данных сдвигает вправо второй операнд на n сегментов. По мере того как сегменты данных сдвигаются вправо, 0 вводятся с левой стороны для заполнения освобождающегося пространства. Второй операнд данных принимает вид: 0, 0, 0, H, G, F, E, D. Сдвинутые операнды выводятся из логических схем 1122, 1124 сдвига влево/вправо и объединяются в схеме 1126 «логическое ИЛИ». Схема «логическое ИЛИ» выполняет операцию «логическое ИЛИ» сегментов данных и обеспечивает результат 1108 длиной 64 бита для данного варианта осуществления. Осуществление операции «ИЛИ» для «K, J, I, 0, 0, 0, 0, 0» и «0, 0, 0, H, G, F, E, D» формирует результат 1108, содержащий восемь байтов: K, J, I, H, G, F, E, D. Этот результат такой же, как для первого варианта осуществления настоящего изобретения, показанного на Фиг.16A. Следует обратить внимание, что для отсчета 1106 n, превышающего количество элементов данных в операнде, соответствующее количество 0 может появиться в результате, начиная с левой стороны. Кроме того, если отсчет 1106 больше или равен общему количеству элементов данных в обоих операндах, то результат будет содержать все 0.