Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, рис.5.3 на стр.144 в книге Гутников B.C. Интегральная электроника в измерительных устройствах. Л.: Энергоатомиздат, 1988), которые реализуют простую симметричную булеву функцию τ2=х1x2∨x1x3∨x2x3, зависящую от трех аргументов - входных двоичных сигналов x1, х2, х3∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов x1, ...,xn∈{0,1}.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический вычислитель (см. рис.2 в статье Савченко Ю.Г., Хмелевая А.В. О методах последовательной реализации симметричных булевых функций // Автоматика и вычислительная техника. 1974. №3. С.24-29), который содержит n-1 элементов И, n-1 элементов ИЛИ и реализует n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов x1, ...,xn∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная структура, поскольку прототип имеет n информационных входов.

Техническим результатом изобретения является упрощение структуры за счет уменьшения количества информационных входов в n раз при сохранении функциональных возможностей прототипа.

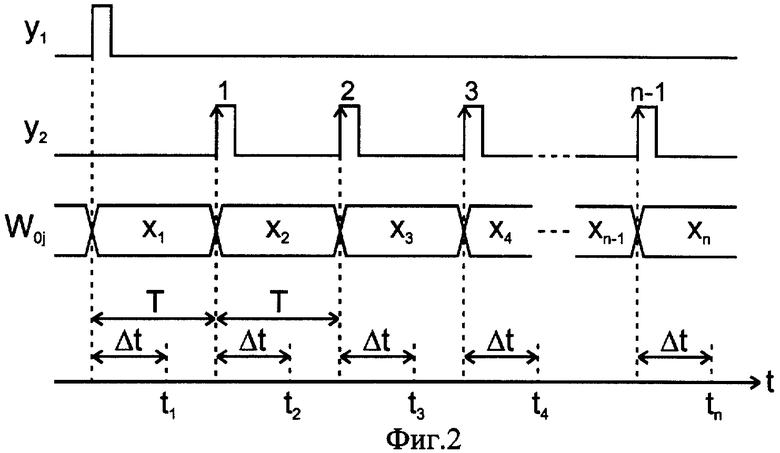

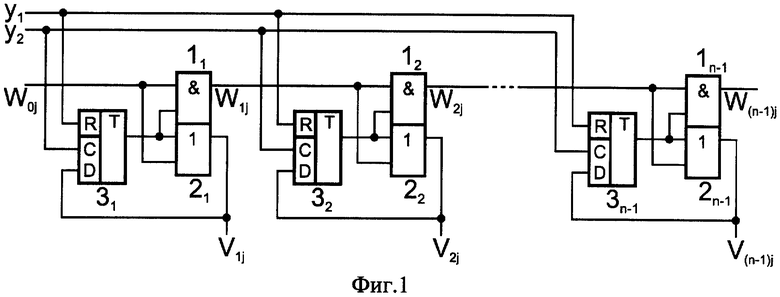

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n-1 элементов И и n-1 элементов ИЛИ, особенность заключается в том, что в него введены n-1 D-триггеров, причем неинвертирующий выход i-го  D-триггера соединен с вторым входом i-го элемента И и первым входом i-го элемента ИЛИ, подключенного вторым входом и выходом соответственно к первому входу i-го элемента И и входу данных i-го D-триггера, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-ым выходом соответственно к первому входу первого элемента И и выходу i-го элемента ИЛИ, выход каждого предыдущего элемента И соединен с первым входом последующего элемента И, а выход (n-1)-го элемента И является n-ым выходом логического вычислителя.

D-триггера соединен с вторым входом i-го элемента И и первым входом i-го элемента ИЛИ, подключенного вторым входом и выходом соответственно к первому входу i-го элемента И и входу данных i-го D-триггера, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-ым выходом соответственно к первому входу первого элемента И и выходу i-го элемента ИЛИ, выход каждого предыдущего элемента И соединен с первым входом последующего элемента И, а выход (n-1)-го элемента И является n-ым выходом логического вычислителя.

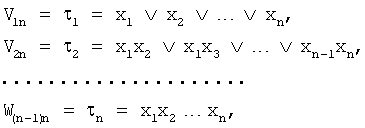

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы, поясняющие принцип его работы.

Логический вычислитель содержит элементы И 11, ...,1n-1, элементы ИЛИ 21, ...,2n-1, D-триггеры 31, ...,3n-1, причем неинвертирующий выход D-триггера 3i соединен с вторым входом элемента 1i и первым входом элемента 2i, подключенного вторым входом и выходом соответственно к первому входу элемента 1i и входу данных D-триггера 3i, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-ым выходом соответственно к первому входу элемента 11 и выходу элемента 2i, выход элемента 1k

соединен с вторым входом элемента 1i и первым входом элемента 2i, подключенного вторым входом и выходом соответственно к первому входу элемента 1i и входу данных D-триггера 3i, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-ым выходом соответственно к первому входу элемента 11 и выходу элемента 2i, выход элемента 1k соединен с первым входом элемента 1k+1, а выход элемента 1n-1 является n-ым выходом логического вычислителя.

соединен с первым входом элемента 1k+1, а выход элемента 1n-1 является n-ым выходом логического вычислителя.

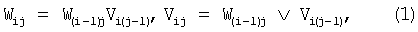

Работа предлагаемого логического вычислителя осуществляется следующим образом. На его первый, второй управляющие входы подаются соответственно импульсные сигналы y1, y2∈{0,1} (фиг.2), причем период Т сигнала y2 должен удовлетворять условию T>Δt, где Δt=ΔtТр+(n-1)ΔtИ, а ΔtТр и ΔtИ есть длительности задержек, вносимых D-триггером и элементом И. Синхронно с передним фронтом импульса сигнала y1 и передними фронтами первого, ..., (n-1)-го импульсов сигнала y2 на информационный вход логического вычислителя последовательно подаются двоичные сигналы х1 и х2, ..., хn соответственно (фиг.2). Тогда сигналы на выходах элементов 1i, 2i будут определяться рекуррентными выражениями

будут определяться рекуррентными выражениями

где  есть номер момента времени ti (фиг.2); Vi0=0; W0j=xj. В представленной ниже таблице приведены значения выражений (1) при n=4.

есть номер момента времени ti (фиг.2); Vi0=0; W0j=xj. В представленной ниже таблице приведены значения выражений (1) при n=4.

Таким образом, на первом, втором, ..., n-ом выходах предлагаемого логического вычислителя при j=n соответственно имеем

где τ1, ..., τn есть простые симметричные булевы функции (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель реализует n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, и обладает более простой по сравнению с прототипом структурой, так как имеет только один информационный вход.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2300138C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2282234C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2336555C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2003 |

|

RU2248036C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2284567C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2353967C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294558C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2011 |

|

RU2445679C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2003 |

|

RU2257608C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом изобретения является упрощение структуры за счет уменьшения количества информационных входов в n раз при сохранении функциональных возможностей прототипа. Указанный результат достигается за счет того, что логический вычислитель для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержит (n-1) элементов И, (n-1) элементов ИЛИ и (n-1) D-триггеров. 2 ил.

Логический вычислитель для реализации n простых симметричных булевых функций, зависящих от n аргументов - входных двоичных сигналов, содержащий n-1 элементов И и n-1 элементов ИЛИ, отличающийся тем, что в него введены n-1 D-триггеров, причем неинвертирующий выход i-го  D-триггера соединен с вторым входом i-го элемента И и первым входом i-го элемента ИЛИ, подключенного вторым входом и выходом соответственно к первому входу i-го элемента И и входу данных i-го D-тригтера, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-м выходом соответственно к первому входу первого элемента И и выходу i-го элемента ИЛИ, выход каждого предыдущего элемента И соединен с первым входом последующего элемента И, а выход (n-1)-го элемента И является n-м выходом логического вычислителя, на первый, второй управляющие входы которого подаются соответственно импульсные сигналы y1, y2∈{0,1}, причем период Т сигнала y2 удовлетворяет условию T>Δt, где Δt=ΔtTp+(n-1)ΔtИ, a ΔtТр и ΔtИ - длительности задержек, вносимых D-триггером и элементом И, первый и второй, ..., n-й входные двоичные сигналы последовательно подаются на информационный вход логического вычислителя синхронно с передним фронтом импульса сигнала y1 и передними фронтами первого, ..., (n-1)-го импульсов сигнала y2 соответственно.

D-триггера соединен с вторым входом i-го элемента И и первым входом i-го элемента ИЛИ, подключенного вторым входом и выходом соответственно к первому входу i-го элемента И и входу данных i-го D-тригтера, вход сброса и тактовый вход которого соединены соответственно с первым и вторым управляющими входами логического вычислителя, подключенного информационным входом и i-м выходом соответственно к первому входу первого элемента И и выходу i-го элемента ИЛИ, выход каждого предыдущего элемента И соединен с первым входом последующего элемента И, а выход (n-1)-го элемента И является n-м выходом логического вычислителя, на первый, второй управляющие входы которого подаются соответственно импульсные сигналы y1, y2∈{0,1}, причем период Т сигнала y2 удовлетворяет условию T>Δt, где Δt=ΔtTp+(n-1)ΔtИ, a ΔtТр и ΔtИ - длительности задержек, вносимых D-триггером и элементом И, первый и второй, ..., n-й входные двоичные сигналы последовательно подаются на информационный вход логического вычислителя синхронно с передним фронтом импульса сигнала y1 и передними фронтами первого, ..., (n-1)-го импульсов сигнала y2 соответственно.

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2002 |

|

RU2227931C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047892C1 |

| Устройство для вычисления симметрических булевых функций | 1987 |

|

SU1478208A1 |

| ПОСПЕЛОВ Д.А., Логические методы анализа и синтеза схем., Москва, Энергия, 1974, с.126. | |||

Авторы

Даты

2006-05-10—Публикация

2004-12-06—Подача