Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические вычислители (см., например, рис.1 в статье Музыченко О.Н. Однородные и регулярные структуры для реализации симметричных функций алгебры логики// Автоматика и телемеханика. 1998. №4. С.152-165), которые содержат вычислительные ячейки и реализуют любую из n пороговых равновесных функций, зависящих от n аргументов - входных двоичных сигналов х1,... ,xn∈{0,1}. Отметим, что в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 (см. стр.126) эти функции называются простыми симметричными. Именно это название применяется далее.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических вычислителей, относится не полная регулярность (повторяемость) связей между вычислительными ячейками.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, логический вычислитель (рис.2 в статье Музыченко О.Н. Однородные и регулярные структуры для реализации симметричных функций алгебры логики// Автоматика и телемеханика. 1998. №4. С.152-165), который содержит n-1 вычислительных ячеек и реализует любую из n простых симметричных функций, зависящих от n аргументов - входных двоичных сигналов x1,... ,xn∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится не полная регулярность межъячеечных связей.

Техническим результатом изобретения является упрощение устройства за счет обеспечения полной регулярности связей между вычислительными ячейками.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом вычислителе, содержащем n-1 вычислительных ячеек, каждая из которых содержит по одному элементу “И” и “ИЛИ”, особенность заключается в том, что в него дополнительно введена аналогичная упомянутым n-я вычислительная ячейка и в каждую вычислительную ячейку дополнительно введен D-триггер, неинвертирующий выход которого соединен с вторым входом элемента “И”, подключенного выходом к первому входу элемента “ИЛИ”, второй вход которого соединен с входом данных D-триггера, подключенного тактовым входом к управляющему входу вычислительной ячейки, первый, второй информационные входы и выход которой образованы соответственно первым входом элемента “И”, вторым входом и выходом элемента “ИЛИ”, выход каждой предыдущей вычислительной ячейки соединен с вторым информационным входом последующей вычислительной ячейки, а выход n-й вычислительной ячейки является выходом логического вычислителя, первый и второй настроечные входы которого образованы соответственно вторым информационным входом первой вычислительной ячейки и объединенными управляющими входами всех вычислительных ячеек.

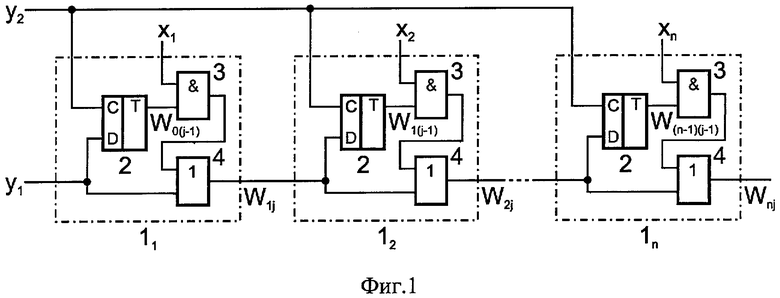

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого логического вычислителя и временные диаграммы управляющих сигналов.

Логический вычислитель содержит n вычислительных ячеек 11,... ,1n. Каждая вычислительная ячейка содержит D-триггер 2, элемент “И” 3 и элемент “ИЛИ” 4, причем неинвертирующий выход D-триггера 2 соединен с вторым входом элемента 3, подключенного выходом к первому входу элемента 4, второй вход которого соединен с входом данных D-триггера 2, подключенного тактовым входом к управляющему входу вычислительной ячейки, первый, второй информационные входы и выход которой образованы соответственно первым входом элемента 3, вторым входом и выходом элемента 4. Выход каждой предыдущей вычислительной ячейки соединен с вторым информационным входом последующей вычислительной ячейки, а выход ячейки 1n является выходом логического вычислителя, первый и второй настроечные входы которого образованы соответственно вторым информационным входом ячейки 11 и объединенными управляющими входами всех вычислительных ячеек.

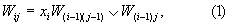

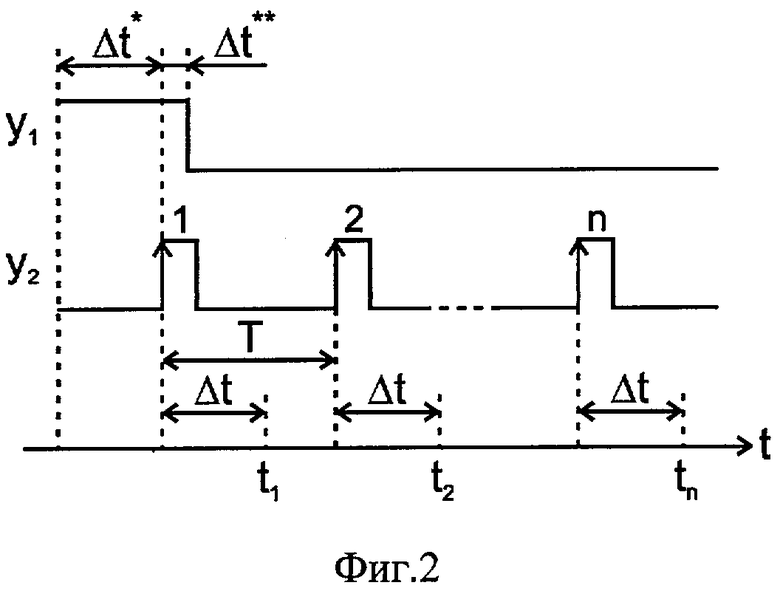

Работа предлагаемого логического вычислителя осуществляется следующим образом. На первые информационные входы вычислительных ячеек 11,... ,1n и первый, второй настроечные входы вычислителя подаются соответственно двоичные сигналы х1,... ,xn∈{0,1} и y1,y2∈{0,1} (фиг.2). Тогда сигнал на выходе ячейки 1i будет определяться рекуррентным выражением

будет определяться рекуррентным выражением

где  есть номер момента времени tj (фиг.2); W(i-1)0=1; W0j=0. Период Т сигнала y2 должен удовлетворять условию T>Δ t, где Δ t=Δ tТр+Δ tИ+nΔ tили, а Δ tТр, Δ tи и Δ tили есть длительности задержек, вносимых соответственно D-триггером 2, элементами 3 и 4. Длительность высокого уровня сигнала y1 определяется суммой Δ t*+Δ t**, где Δ t*≥nΔ tили; Δ t**≤ Δ tТр+Δ tи. В представленной ниже таблице приведены значения выражения (1) при n=4.

есть номер момента времени tj (фиг.2); W(i-1)0=1; W0j=0. Период Т сигнала y2 должен удовлетворять условию T>Δ t, где Δ t=Δ tТр+Δ tИ+nΔ tили, а Δ tТр, Δ tи и Δ tили есть длительности задержек, вносимых соответственно D-триггером 2, элементами 3 и 4. Длительность высокого уровня сигнала y1 определяется суммой Δ t*+Δ t**, где Δ t*≥nΔ tили; Δ t**≤ Δ tТр+Δ tи. В представленной ниже таблице приведены значения выражения (1) при n=4.

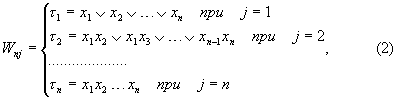

Таким образом, предлагаемый логический вычислитель на своем выходе воспроизводит функцию

где τ 1,... ,τ n есть простые симметричные функции (см. стр.126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974). Согласно (2) и фиг.2 настройка вычислителя (фиг.1) на воспроизведение функции τ j осуществляется соответствующим количеством j импульсов сигнала y2. При этом из фиг.1 видно, что все ячейки вычислителя одинаковым образом соединены между собой.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический вычислитель воспроизводит любую из n простых симметричных функций, зависящих от n аргументов - входных двоичных сигналов, и обладает в отличие от прототипа полной регулярностью межъячеечных связей.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИММЕТРИЧНЫЙ МОДУЛЬ | 2003 |

|

RU2248035C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2007 |

|

RU2335797C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2016 |

|

RU2626345C1 |

| ИДЕНТИФИКАТОР ЧИСЛА ЕДИНИЧНЫХ СИГНАЛОВ | 2005 |

|

RU2277260C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2003 |

|

RU2248036C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2004 |

|

RU2260205C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2276399C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2294009C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2006 |

|

RU2300138C1 |

| ЛОГИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2005 |

|

RU2284567C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления. Техническим результатом изобретения является упрощение устройства за счет обеспечения полной регулярности связей между вычислительными ячейками. Устройство содержит n вычислительных ячеек, каждая из которых содержит элемент "И", элемент "ИЛИ", D-триггер. 2 ил., 1 табл.

Логический вычислитель для воспроизведения простых симметричных функций, зависящих от n аргументов, состоящий из n-1 вычислительных ячеек, каждая из которых содержит по одному элементу И и ИЛИ, отличающийся тем, что в него дополнительно введена аналогичная упомянутым n-я вычислительная ячейка и в каждую вычислительную ячейку дополнительно введен D-триггер, неинвертирующий выход которого соединен с вторым входом элемента И, подключенного выходом к первому входу элемента ИЛИ, второй вход которого соединен с входом данных D-триггера, подключенного тактовым входом к управляющему входу вычислительной ячейки, первый, второй информационные входы и выход которой образованы соответственно первым входом элемента И, вторым входом и выходом элемента ИЛИ, выход каждой предыдущей вычислительной ячейки соединен с вторым информационным входом последующей вычислительной ячейки, а выход n-й вычислительной ячейки является выходом логического вычислителя, первый и второй настроечные входы которого образованы соответственно вторым информационным входом первой вычислительной ячейки и объединенными управляющими входами всех вычислительных ячеек.

| МУЗЫЧЕНКО О.Н | |||

| Однородные и регулярные структуры для реализации симметричных функций алгебры логики | |||

| Автоматика и телемеханика | |||

| Способ и аппарат для получения гидразобензола или его гомологов | 1922 |

|

SU1998A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СИММЕТРИЧЕСКИХ БУЛЕВЫХ ФУНКЦИЙ | 1992 |

|

RU2047893C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 1991 |

|

RU2045769C1 |

| МЕТАЛЛОПОРИСТЫЙ ПРОПИТАННЫЙ КАТОД ДЛЯ МАГНЕТРОНА | 2007 |

|

RU2342732C1 |

Авторы

Даты

2005-07-27—Публикация

2003-12-02—Подача