Изобретение относится к области вычислительной техники и может быть использовано при проектировании сверхбольших интегральных схем (СБИС), устройств и систем с перестраиваемой архитектурой.

Известна коммутационная матрица, изготовленная по субмикронной технологии с многослойной разводкой (не менее 3-х слоев металлизации). Электрические соединения в коммутационной матрице выполняют последовательным соединением фрагментов проводников путем коммутации двунаправленных ключей, расположенных на площади каждого слоя металлизации и между слоями металлизации, определенным оптимальным образом (httpr/www. Aptix.com. - информация по устройству FPIC фирмы Aptix).

Недостатками аналога являются ограниченный ресурс по количеству реализуемых электрических соединений, а также сложность технологии изготовления и сложность управления.

Известна коммутационная среда [патент РФ №2092896, МПК 6 G 06 F 15/163, бюл. №28, 10.10.97.], выбранная в качестве прототипа, содержащая первую группу из F матричных коммутаторов (V×V) и вторую группу из Q матричных коммутаторов (F×H), каждый из которых обеспечивает коммутацию информационных входов на информационные выходы по принципу *любой на любой*, одноименные i-e (i=1, P) информационные выходы матричных коммутаторов первой группы матричных коммутаторов объединены, одноименные j-e (j=V-P+1, V) информационные выходы матричных коммутаторов первой труппы матричных коммутаторов подключены соответственно к F информационным входам u-го (u=1, Q) матричного коммутатора второй группы матричных коммутаторов. Информационные входы матричных коммутаторов первой группы матричных коммутаторов являются N информационными входами коммутационной среды, i-e информационные выходы матричных коммутаторов первой группы матричных коммутаторов и информационные выходы матричных коммутаторов второй группы матричных коммутаторов являются информационными выходами коммутационной среды, а управляющие входы матричных коммутаторов первой и второй групп матричных коммутаторов являются управляющими входами коммутационной среды.

На множестве информационных выводов N коммутационной среды программированием матричных коммутаторов получают любые электрические соединения, имеющие случайный (неупорядоченный, нерегулярный) характер. Максимальное количество реализуемых электрических соединений равно числу информационных выходов.

Недостатком прототипа является ограниченное число реализуемых электрических соединений.

Задачей предлагаемого изобретения является увеличения количества реализуемых в коммутационной среде электрических соединений.

Поставленная задача решается за счет того, что в коммутационной среде, содержащей первую группу из F матричных коммутаторов (V×V), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, вторую группу из Q матричных коммутаторов (F×H), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, соединенных одноименными j-ми (j=(V-P+1), V) информационными выходами матричных коммутаторов первой группы матричных коммутаторов соответственно с F информационными входами u-го (u=1, Q) матричного коммутатора второй группы матричных коммутаторов, группами информационных входов матричных коммутаторов первой группы матричных коммутаторов соответственно с N информационными входами коммутационной среды, группами информационных выходов второй группы матричных коммутаторов соответственно с первой группой М информационных выходов коммутационной среды, группами управляющих входов матричных коммутаторов первой группы матричных коммутаторов и матричных коммутаторов второй группы матричных коммутаторов с управляющими входами коммутационной среды.

Новым является то, что коммутационная среда дополнительно содержит третью группу из Р матричных коммутаторов (F×H), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, причем одноименные i-e (i=1, Р) информационные выходы матричных коммутаторов первой группы матричных коммутаторов подключены соответственно к информационным входам r-го (r=1, Р) матричного коммутатора третьей группы матричных коммутаторов, при этом информационные выходы Р матричных коммутаторов третьей группы матричных коммутаторов являются второй группой информационных выходов коммутационной среды, а управляющие входы матричных коммутаторов третьей группы матричных коммутаторов являются дополнительными управляющими входами коммутационной среды.

В изобретении решается задача увеличения количества реализуемых в коммутационной среде электрических соединений, что позволяет в сравнении с прототипом увеличить общее количество, реализуемых на множестве информационных выводов N, электрических соединений на (Р×Н).

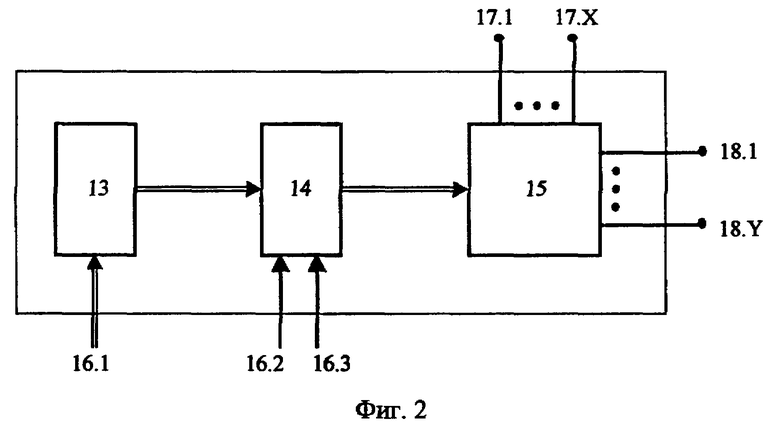

На фиг.1. представлена схема предлагаемой коммутационной среды.

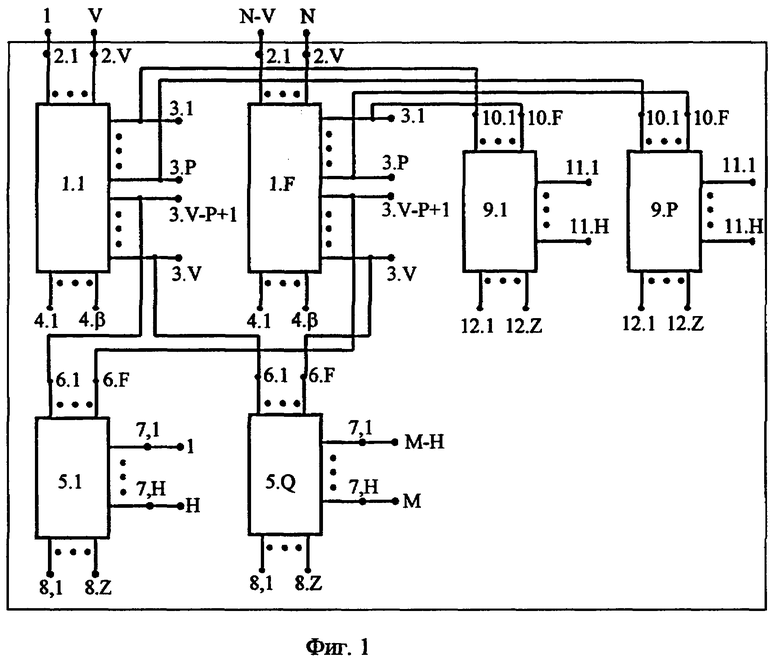

На фиг.2 представлена схема матричного коммутатора К590 КН14.

Коммутационная среда (фиг.1) содержит первую 1.1....1.F. группу из F матричных коммутаторов (V×V), каждый из которых содержит группу 2.1....2.V. информационных входов, группу 3.1....3.V. информационных выходов и группу 4.1....4.β. управляющих входов, вторую 5.1....5.Q. группу из Q матричных коммутаторов (F×Н), каждый из которых содержит группу 6.1....6.F. информационных входов, группу 7.1....7.Н. информационных выходов и группу 8.1....8.Z. управляющих входов, соединенных одноименными j-ми (j=(V-P+1), V) информационными выходами 3.(V-P+1)...3.V. матричных коммутаторов первой группы матричных коммутаторов соответственно с F информационными входами 6.1....6.F. u-го (u=1, Q) матричного коммутатора второй группы матричных коммутаторов, группами информационных входов 2.1....2.V. матричных коммутаторов первой группы матричных коммутаторов соответственно с N информационными входами коммутационной среды, группами информационных выходов 7.1....7.Н. второй группы матричных коммутаторов соответственно с первой группой из М информационных выходов коммутационной среды, группами управляющих входов 4.1....4.β. матричных коммутаторов первой группы матричных коммутаторов и 8.1...8.Z. матричных коммутаторов второй группы матричных коммутаторов с управляющими входами коммутационной среды, дополнительно содержит третью 9.1....9.Р. группу из Р матричных коммутаторов (F×H), каждый из которых содержит группу 10.1....10.F. информационных входов, группу 11.1....11.Н. информационных выходов и группу 12.1....12.Z. управляющих входов, причем одноименные i-e (i=1, Р) информационные выходы 3.1....3.Р. матричных коммутаторов первой группы матричных коммутаторов подключены соответственно к информационным входам 10.1....10.F r-го (r=1, Р) матричного коммутатора третьей группы матричных коммутаторов, информационные выходы 11.1....11.Н. Р матричных коммутаторов третьей группы матричных коммутаторов являются второй группой информационных выходов коммутационной среды, а управляющие входы 12.1....12.Z матричных коммутаторов третьей группы матричных коммутаторов являются дополнительными управляющими входами коммутационной среды.

Матричный коммутатор (фиг.2) содержит дешифратор 13, узел 14 хранения информации и матрицу 15 аналоговых (или двунаправленных) ключей, причем выходы дешифратора 13 соединены с адресными входами узла 14 хранения информации, выходы которого соединены соответственно с управляющими входами ключей матрицы аналоговых ключей. Адресные входы 16.1 дешифратора 13 и два информационных 16.2 и 16.3 входа узла 14 хранения информации являются управляющими входами матричного коммутатора. Вертикальные коммутируемые шины матрицы 15 являются информационными 17 входами матричного коммутатора, горизонтальные коммутируемые шины матрицы являются информационными 18 выходами матричного коммутатора.

Программирование матричного коммутатора (фиг.2) осуществляют записью программы настройки в узел хранения информации путем подачи соответствующих управляющих сигналов на входы матричного коммутатора.

Например, чтобы осуществить в матричном коммутаторе коммутацию информационного входа 17.1 на информационный выход 18.Y, необходимо в матрице 15 *замкнуть* аналоговый ключ, который находится на перекрестье вертикальной 17.1 и горизонтальной 18.Y коммутируемых шин. Для этого на вход 16.1 подают адрес элемента памяти узла 14, выход которого соединен с управляющим входом этого аналогового ключа, на вход 16.3 подают сигнал Лог.1, а на вход 16.2 подают синхроимпульс. По переднему фронту синхроимпульса в узел 14 хранения информации осуществляется запись информации, при этом соответствующий элемент памяти узла 14 устанавливается в такое состояние, при котором связанный с ним аналоговый ключ открывается и замыкает соответствующие вертикальную и горизонтальную коммутируемые шины.

Работу устройства (фиг.1) рассмотрим на следующих примерах.

Пример 1: Объединяемые в одну цепь информационные выводы на множестве N принадлежат одному из F матричных коммутаторов первой группы матричных коммутаторов.

Программируем соответствующий матричный коммутатор таким образом, чтобы соответствующие вертикальные коммутируемые шины, связанные с объединяемыми в одну цепь информационными выводами, были *замкнуты* на одну (любую) свободную горизонтальную коммутируемую шину этого матричного коммутатора.

В этом случае каждая реализуемая электрическая цепь содержит два последовательно соединенных ключа.

Пример 2: Объединяемые в одну цепь информационные выводы на множестве N принадлежат разным матричным коммутаторам из F матричных коммутаторов первой группы матричных коммутаторов.

Программируем соответствующие матричные коммутаторы первой группы матричных коммутаторов таким образом, чтобы соответствующие вертикальные коммутируемые шины, связанные с объединяемыми в одну цепь информационными выводами, были *замкнуты* на одноименные i-e или j-e горизонтальные коммутируемые шины. Затем программируем соответствующий матричный коммутатор второй или третьей группы матричных коммутаторов таким образом, чтобы соответствующие вертикальные коммутируемые шины этого матричного коммутатора, соединенные с i-ми или j-ми горизонтальными коммутируемыми шинами матричных коммутаторов первой группы матричных коммутаторов, были *замкнуты* на одну (любую) свободную горизонтальную коммутируемую шину.

В этом случае каждая реализуемая электрическая цепь содержит четыре последовательно соединенных ключа.

Программированием матричных коммутаторов первой, второй и третьей групп матричных коммутаторов реализуют все электрические соединения на множестве N информационных выводов.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОММУТАЦИОННАЯ СРЕДА | 1993 |

|

RU2092896C1 |

| ПРОСТРАНСТВЕННАЯ КОММУТАЦИОННАЯ СРЕДА (ВАРИАНТЫ) | 2009 |

|

RU2402061C1 |

| ПРОСТРАНСТВЕННАЯ КОММУТАЦИОННАЯ СТРУКТУРА | 2003 |

|

RU2270474C2 |

| Матричный коммутатор | 1985 |

|

SU1275753A1 |

| Коммутационное устройство | 1984 |

|

SU1246109A1 |

| Коммутационное устройство | 1989 |

|

SU1672464A1 |

| Коммутационное устройство | 1985 |

|

SU1307572A1 |

| Коммутационное устройство | 1985 |

|

SU1307573A1 |

| Коммутационное устройство | 1990 |

|

SU1730635A1 |

| Матричное коммутационное устройство | 1988 |

|

SU1569965A1 |

Изобретение относится к области вычислительной техники и может быть использовано при проектировании сверхбольших интегральных схем, устройств и систем с перестраиваемой архитектурой. Наличие в составе коммутационной среды трех групп матричных коммутаторов, каждый из которых содержит группу информационных входов, информационных выходов и управляющих входов, а одноименные j-ые информационные выходы первой группы матричных коммутаторов подключены к информационным входам матричных коммутаторов второй группы матричных коммутаторов, одноименные i-ые информационные выходы первой группы матричных коммутаторов подключены к информационным входам матричных коммутаторов третьей матричных коммутаторов, позволяет при осуществлении изобретения увеличить количество соединений, реализуемых в коммутационной среде. 2 ил.

Коммутационная среда, содержащая первую группу из F матричных коммутаторов (V×V), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, вторую группу из Q матричных коммутаторов (F×H), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, соединенных одноименными j-ми (j=(V-P+1), V) информационными выходами матричных коммутаторов первой группы матричных коммутаторов соответственно с F информационными входами u-го (u=1, Q) матричного коммутатора второй группы матричных коммутаторов, а также группами информационных входов матричных коммутаторов первой группы матричных коммутаторов соответственно с N информационными входами коммутационной среды, кроме того, группами информационных выходов второй группы матричных коммутаторов соответственно с первой группой М информационных выходов коммутационной среды, а группами управляющих входов матричных коммутаторов первой группы матричных коммутаторов и матричных коммутаторов второй группы матричных коммутаторов с управляющими входами коммутационной среды, отличающийся тем, что она дополнительно содержит третью группу из Р матричных коммутаторов (F×H), каждый из которых содержит группу информационных входов, группу информационных выходов и группу управляющих входов, причем одноименные i-e (i=1, P) информационные выходы матричных коммутаторов первой группы матричных коммутаторов подключены соответственно к информационным входам r-го (r=1, Р) матричного коммутатора третьей группы матричных коммутаторов, при этом информационные выходы Р матричных коммутаторов третьей группы матричных коммутаторов являются второй группой информационных выходов коммутационной среды, а управляющие входы матричных коммутаторов третьей группы матричных коммутаторов являются дополнительными управляющими входами коммутационной среды.

| КОММУТАЦИОННАЯ СРЕДА | 1993 |

|

RU2092896C1 |

| Трехкаскадная коммутирующая система | 1984 |

|

SU1226481A1 |

| US 3976979, 24.08.1976. | |||

Авторы

Даты

2006-07-27—Публикация

2001-12-06—Подача