Изобретение относится к измерительной технике и может быть использовано в системах контроля и регулирования параметров промышленных установок.

Известен фазовый компаратор, содержащий два формирователя, пять элементов ИЛИ, четыре элемента НЕ, четыре элемента И и элемент задержки [1].

Недостатками указанного устройства является низкая точность, узкий диапазон фаз сравниваемых сигналов и узкие функциональные возможности.

Известен фазовый компаратор, содержащий J-k-триггер, два элемента И-НЕ и интегратор [2].

Недостатками указанного устройства являются узкий диапазон фаз сравниваемых сигналов, узкие функциональные возможности и низкая точность.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому изобретению является фазовый компаратор, который содержит три интегратора, формирователь импульсов, источник опорного напряжения, два формирователя временных интервалов и два формирователя прямоугольных импульсов [3].

Недостатками указанного устройства являются узкий диапазон фаз сравниваемых сигналов и узкие функциональные возможности.

Заявляемое изобретение решает задачу создания фазового компаратора, лишенного перечисленных недостатков. Техническим результатом, достигаемым при использовании заявляемого изобретения, является расширение диапазона фаз сравниваемых сигналов и функциональных возможностей.

Поставленная цель достигается тем, что в фазовый компаратор, содержащий три интегратора, выходы первого и второго из которых подсоединены к первым входам первого и второго формирователей временных интервалов соответственно, вторые входы которых подключены одновременно к выходу источника опорного напряжения, формирователь импульсов, первый и второй входы которого подсоединены к входам первого и второго интеграторов соответственно, а выход подключен одновременно к управляющим входам первого и второго формирователей временных интервалов, выходы которых подсоединены к первому и второму входам третьего интегратора соответственно, выход которого является выходом фазового компаратора, введены два D-триггера, С-входы которых являются входами фазового компаратора, инверсный выход первого D-триггера подключен к его D-входу, а прямой выход подсоединен к входу первого интегратора, инверсный выход второго D-триггера подключен к его D-входу, а прямой выход подсоединен к входу второго интегратора, элемент И-НЕ, первый и второй входы которого подключены к выходам первого и второго формирователей временных интервалов соответственно, а выход подсоединен к управляющему входу формирователя импульсов.

Таким образом, заявляемое устройство соответствует критерию “новизна”.

Сравнение заявляемого технического решения не только с прототипом, но и с другими техническими решениями в данной области техники не позволило выявить в них признаки, отличающие заявляемое техническое решение от прототипа. Это позволяет сделать вывод о соответствии критерию “изобретательский уровень”.

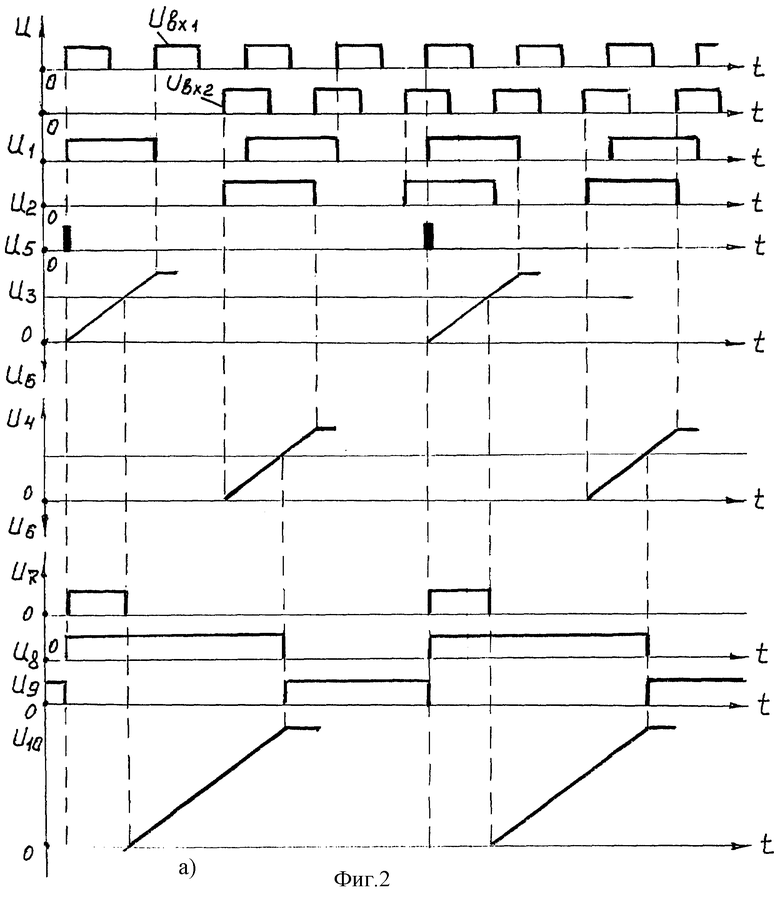

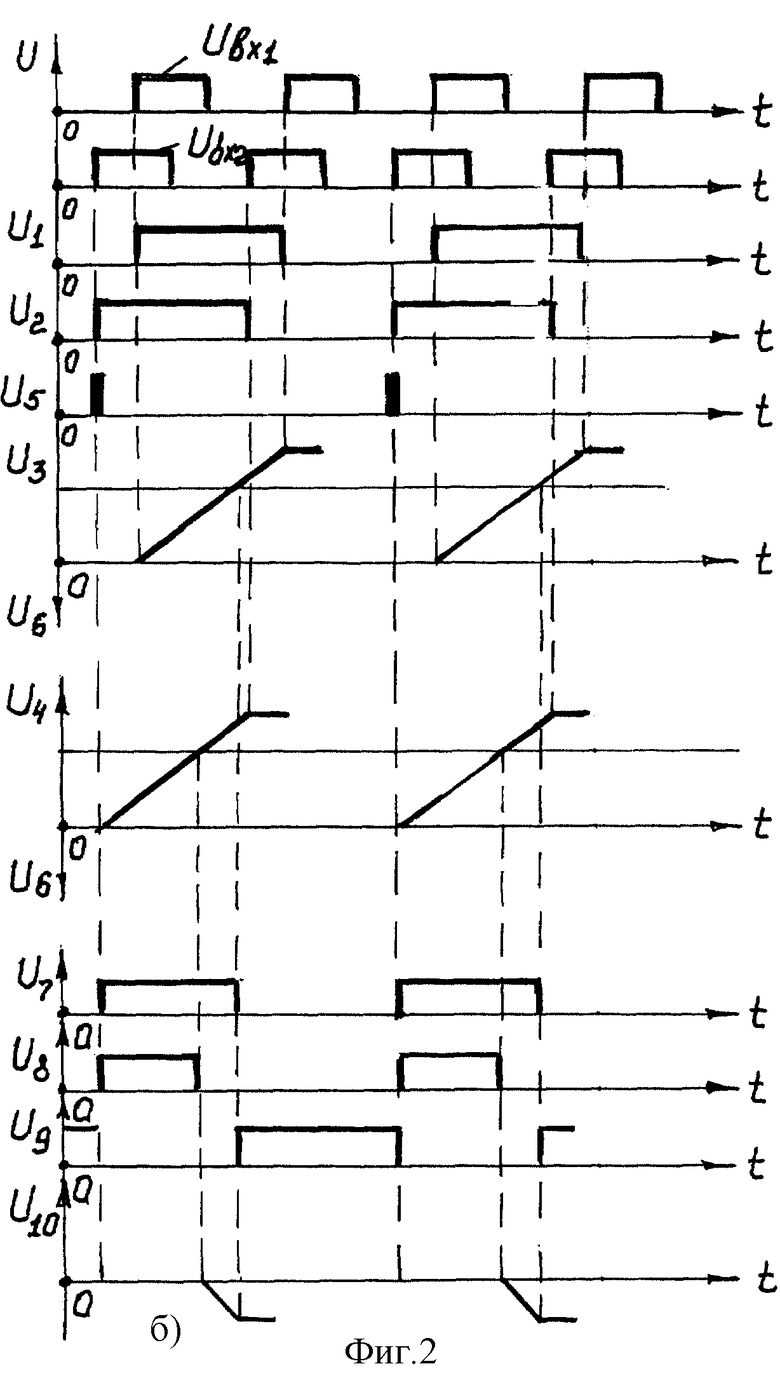

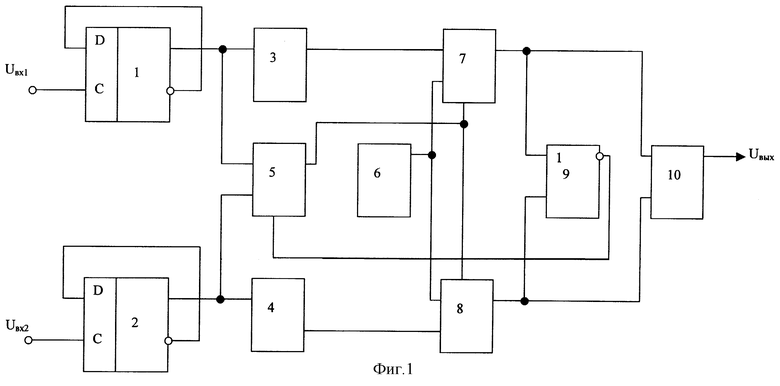

На фиг.1 приведена структурная электрическая схема фазового компаратора; на фиг.2а, б - временные диаграммы, поясняющие его работу, причем диаграмма фиг.2а соответствует случаю, когда фаза первого сравниваемого сигнала меньше фазы второго сравниваемого сигнала, а диаграмма фиг.2б - случаю, когда фаза первого сравниваемого сигнала больше фазы второго сигнала.

Фазовый компаратор содержит два D-триггера 1, 2, три интегратора 3, 4, 10, формирователь импульсов 5, источник опорного напряжения 6, два формирователя временных интеграторов 7, 8 и элемент ИЛИ-НЕ 9. С-входы первого и второго D-триггеров 1, 2 являются входами фазового компаратора. Инверсный выход первого D-триггера 1 подключен к его D-входу, а прямой выход подсоединен одновременно к входу первого интегратора 3 и первому входу формирователя импульсов 5. Инверсный выход второго D-триггера 2 подключен к его D-входу, а прямой выход подсоединен одновременно к входу второго интегратора 4 и второму входу формирователя импульсов 5. Выходы первого и второго интеграторов 3, 4 подключены к первым входам первого и второго формирователей временных интервалов 7, 8 соответственно. Выход источника опорного напряжения 6 подсоединен одновременно к вторым входам первого и второго формирователей временных интервалов 7, 8 соответственно. Выход первого формирователя временных интервалов 7 подключен одновременно к первому входу третьего интегратора 10 и первому входу элемента ИЛИ-НЕ 9, выход которого подсоединен к управляющему входу формирователя импульсов 5. Выход второго формирователя временных интервалов 8 подключен одновременно к второму входу элемента ИЛИ-НЕ 9 и второму входу третьего интегратора 10, выход которого является выходом фазового компаратора.

Фазовый компаратор работает следующим образом. Сигнал Uвx1 и Uвх2, фазы которых сравниваются между собой, поступают на С-входы первого и второго D-триггеров 1, 2 соответственно (информационным входом D-триггера будет вход С). D-триггеры 1 и 2 работают в режиме счета, т.е. как триггеры расчетным входом. В таком режиме D-триггер по фронту каждого входного импульса меняет свое логическое состояние на противоположное. В результате частота импульсов на выходе каждого триггера оказывается вдвое меньшей частоты входных импульсов. Деление частоты входных сравниваемых сигналов на два позволило расширить диапазон фаз сравниваемых сигналов, который находится в пределах 0...720° (0...-720°) и функциональные возможности фазового компаратора. Прямоугольные импульсы с прямых выходов D-триггеров 1, 2 поступают на входы интеграторов 3 и 4 и на первый и второй входы формирователя узких импульсов 5 соответственно. На управляющий вход формирователя узких импульсов 5 подается сигнал с выхода элемента ИЛИ-НЕ 9. На выходе формирователя импульсов 5 узкие импульсы формируются в моменты переходов сравниваемого входного сигнала меньшей фазы с низкого уровня на высокий и при поступлении на его управляющий вход выходного сигнала единичного уровня элемента ИЛИ-НЕ 9. После интегрирования сигнала с выходов интеграторов 3 и 4 поступают на первые входы формирователей временных интервалов 7 и 8 соответственно, на вторые входы которых сигнал подается с выхода источника опорного напряжения 6. Узкие импульсы с выхода формирователя импульсов 5 поступают одновременно на управляющие входы формирователей временных интервалов 7 и 8. На выходах формирователей временных интервалов 7 и 8 формируются прямоугольные импульсы, начала которых совпадают с моментами прихода управляющих импульсов на их управляющие входы, а концы совпадают с моментами переходов сигналов 3 и 4 с низкого уровня на высокий через уровень сигнала 6, которые поступают на первый и второй входы элемента ИЛИ-НЕ 9 соответственно. На выходе элемента ИЛИ-НЕ 9 формируется импульсный сигнал, который имеет единичный уровень, когда выходные сигналы формирователей временных интервалов 7 и 8 одновременно равны нулю. Выходные сигналы формирователей временных интервалов 7 и 8 подаются также на первый и второй входы интегратора 10, выходной сигнал которого несет однозначную информацию о соотношении фаз сравниваемых сигналов Uвx1 и Цвх2.

Фазовый компаратор может работать в трех режимах:

1. Фаза первого сравниваемого сигнала меньше фазы второго сигнала. В этом случае с выхода интегратора 10 снимается положительный сигнал.

2. Фаза первого сравниваемого сигнала больше фазы второго сигнала. В этом случае с выхода интегратора 10 снимается отрицательный сигнал.

3. Фазы первого и второго сравниваемых Сигналов равны. В этом случае выходной сигнал интегратора 10 равен нулю. Временные диаграммы для этого случая не приводятся.

Введение двух D-триггеров, которые работают в счетном режиме и делят на два частоту входных сравниваемых сигналов, и элемента ИЛИ-НЕ с соответствующими связями выгодно отличает предполагаемое техническое решение от прототипа, так как позволяет расширить диапазон фаз сравниваемых сигналов (-720°...0...720°) и функциональные возможности.

Источники информации

1. Авторское свидетельство СССР №525226, кл. Н 03 d 13/00.

2. Авторское свидетельство СССР №8494181, кл. Н 03 d 13/00.

3. Авторское свидетельство СССР №845279, кл. Н 03 d 9/06, 1981 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗОВЫЙ КОМПАРАТОР | 2005 |

|

RU2282935C1 |

| Фазовый компаратор | 1982 |

|

SU1094141A2 |

| ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 2006 |

|

RU2300170C1 |

| Фазовый компаратор | 1979 |

|

SU845279A1 |

| Частотно-фазовый детектор | 1990 |

|

SU1775844A1 |

| Частотный компаратор | 1978 |

|

SU830643A1 |

| Преобразователь углового перемещения в код | 1985 |

|

SU1279070A1 |

| Амплитудно-дифференциальный нуль-орган | 1977 |

|

SU687402A1 |

| Способ определения мгновенных значений фазового сдвига электрических сигналов | 1988 |

|

SU1559308A1 |

| Амплитудно-дифференциальный детектор | 1979 |

|

SU798687A1 |

Изобретение относится к измерительной технике и может быть использовано в системах контроля и регулирования параметров промышленных установок. Технический результат заключается в расширении диапазона фаз сравниваемых сигналов и функциональных возможностей. Устройство содержит два D-триггера 1, 2, три интегратора 3, 4, 10, формирователь импульсов 5, источник опорного напряжения 6, два формирователя временных интервалов 7-8 и элемент ИЛИ-НЕ 9. Фазовый компаратор работает в трех режимах: - фаза первого сравниваемого сигнала меньше фазы второго сигнала; - фаза первого сравниваемого сигнала больше фазы второго сигнала; - фазы сравниваемых сигналов равны. 2 ил.

Фазовый компаратор, содержащий три интегратора, выходы первого и второго из которых подсоединены к первым входам первого и второго формирователей временных интервалов соответственно, вторые входы которых подключены одновременно к выходу источника опорного напряжения, формирователь импульсов, первый и второй входы которого подсоединены к входам первого и второго интеграторов соответственно, а выход подключен одновременно к управляющим входам первого и второго формирователей временных интервалов, выходы которых подсоединены к первому и второму входам третьего интегратора соответственно, выход которого является выходом фазового компаратора, отличающееся тем, что в него введены два D-триггера, С-входы которых являются входами фазового компаратора, инверсный выход первого D-триггера подключен к его D-входу, а прямой выход подсоединен к входу первого интегратора, инверсный выход второго D-триггера подключен к его D-входу, а прямой выход подсоединен к входу второго интегратора, элемент ИЛИ-НЕ, первый и второй входы которого подключены к выходам первого и второго формирователей временных интервалов соответственно, а выход подсоединен к управляющему входу формирователя импульсов.

| Фазовый компаратор | 1979 |

|

SU845279A1 |

| Фазовый дискриминатор | 1977 |

|

SU849418A1 |

| Фазовый компаратор | 1986 |

|

SU1429288A1 |

| US 4264866, 28.04.1981 | |||

| Бетонная смесь | 1982 |

|

SU1102783A1 |

| US 4020422, 26.04.1977. | |||

Авторы

Даты

2004-11-20—Публикация

2003-02-03—Подача