(54) ЧЛСТОТНЫР КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2000 |

|

RU2178896C1 |

| УСТРОЙСТВО ПОИСКА И СОПРОВОЖДЕНИЯ СИГНАЛА СИНХРОНИЗАЦИИ В СПУТНИКОВЫХ СИСТЕМАХ СВЯЗИ ПО ПРИЕМУ | 1995 |

|

RU2093964C1 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2017 |

|

RU2647678C1 |

| УСТРОЙСТВО ДОПУСКОВОГО КОНТРОЛЯ ПЕРЕХОДНОГО ОТКЛОНЕНИЯ ЧАСТОТЫ ДВУНАПРАВЛЕННОЕ | 2024 |

|

RU2819573C1 |

| Автоматическое устройство для регистрации частотных характеристик | 1980 |

|

SU1002849A1 |

| ЦИФРОВОЕ РЕЛЕ ЧАСТОТЫ ВРАЩЕНИЯ С ФУНКЦИЕЙ РЕКОНСТРУКТИВНОЙ ДИАГНОСТИКИ | 2016 |

|

RU2618495C1 |

| Цифровой частотный демодулятор | 1984 |

|

SU1298845A1 |

| СПОСОБ ЧАСТОТНО-ИМПУЛЬСНОГО ПРЕОБРАЗОВАНИЯ НЕПРЕРЫВНОГО СИГНАЛА И ИНТЕГРАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2001 |

|

RU2199757C1 |

| Сравнивающее устройство | 1986 |

|

SU1370756A1 |

| ЧАСТОТНО-ФАЗОВЫЙ КОМПАРАТОР | 2011 |

|

RU2469461C1 |

1

Изобретение относится к измерительной технике и может быть использовано при создании устройств с частотными датчиками для контроля работы, компрессоров.

Известен частотный компаратор, который содержит элементы задержки, два элемента И, четыре ключа и триггер с обмоткой реле в анодной цепи 1.

Недостатками данного устройства являются низкая точность и низкое быстродействие.

Наиболее близким по технической сущности к изобретению является устройство, содержащее нить триггеров и пять элементов И 2.

Недостатками данного частотного компаратора являются низкая точность и низкое быстродействие.

Цель изобретения - повышение точности и быстродействия работы частотного компаратора.

Поставленная цель достигается тем, что в частотный компаратор, содержащий пять элементов И, первый выход первого из которых соединен с первым входом первого

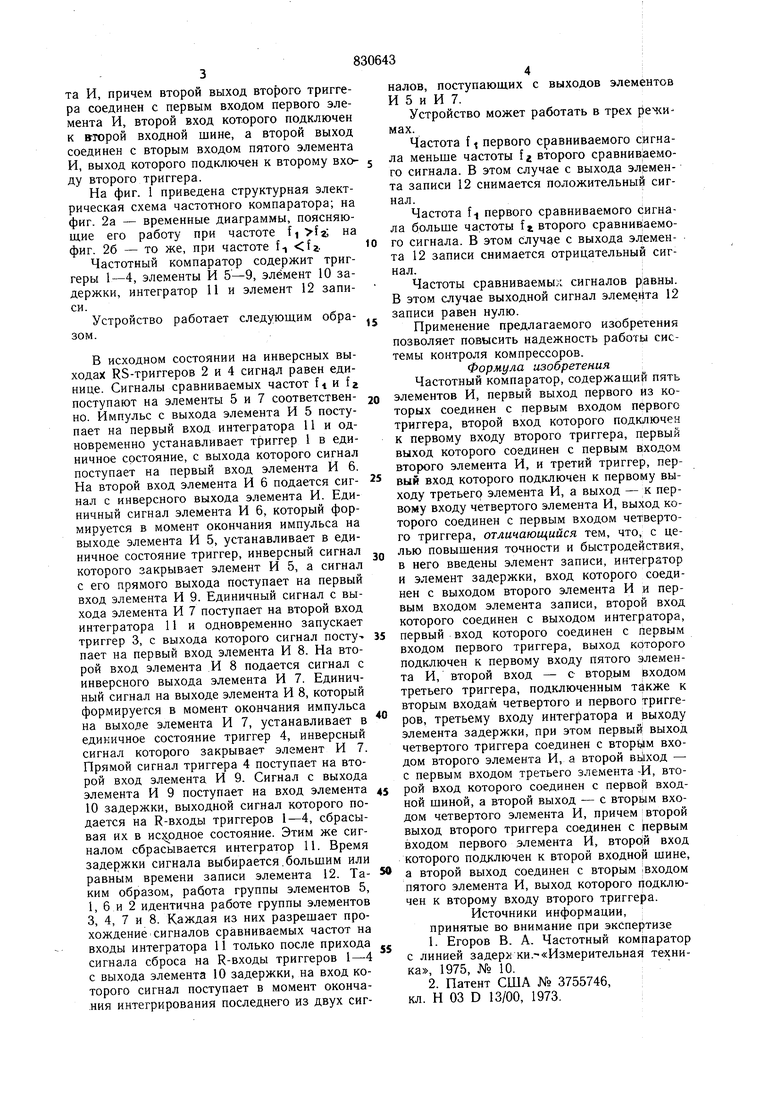

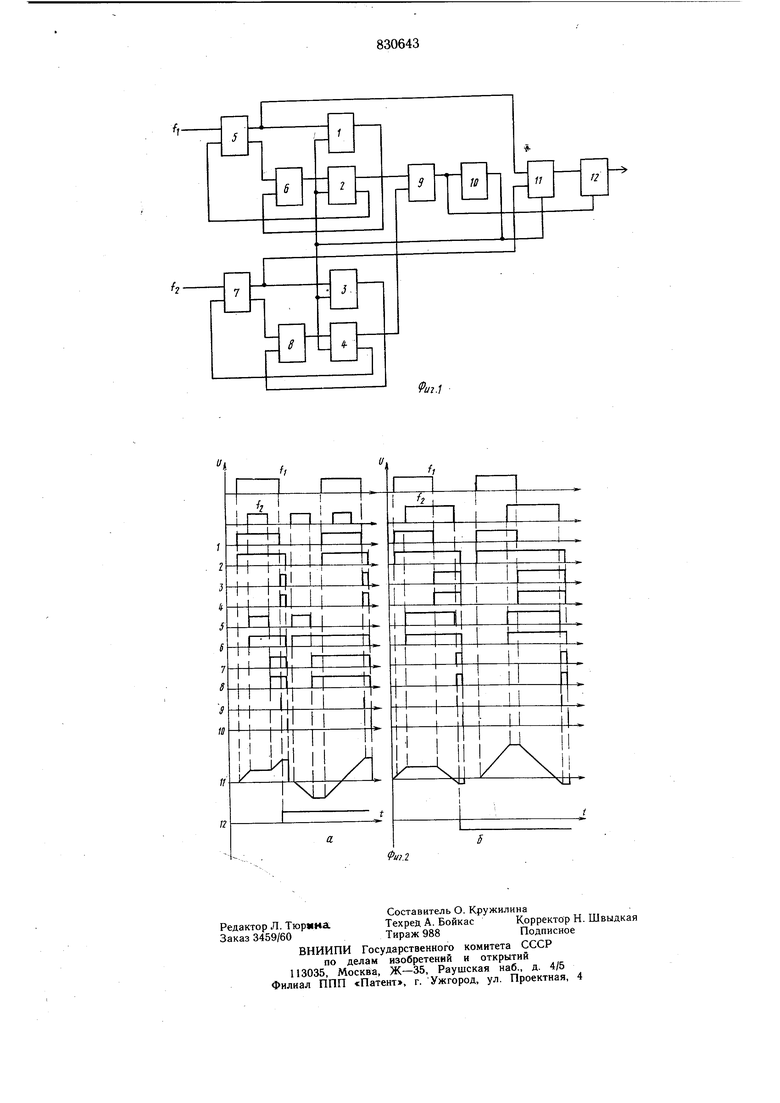

триггера, второй вход которого подключен к перво.му входу второго триггера, первый выход которого соединен с первым входом второго элементами, и третий триггер, первый вход которого подключен к первому выходу третьего элемента И, а выход - к перBoSiy входу четвертого элемента И, выход которого соединен с пербым входом четвертого триггера, введены элемент записи, интегратор и элемент задержки, вход которого соединен с выходом второго элемента И и первым входом элемента записи, второй вход которого соединен с выходом интегратора, первый вход которого соединен с первым входом первого триггера, выход которого подключен к первому входу пятого элемента И, второй вход с вторым входом третьего триггера, полчключенным, также к вторым входам четвертого и первого триггеров, третьему входу интегратора и выходу элемента задержки, при этом первый выход четвертого триггера соединен с вторым входом второго элемента И, а второй выход - с первым входом третьего элемента И, второй вход которого соединен с первой входной шиной, а второй выход - с вторым входом четвертого элемента И, причем второй выход второго триггера соединен с первым входом первого элемента И, второй вход которого подключен к второй входной шине, а второй выход соединен с вторым входом пятого элемента И, выход которого подключен к второму входу второго триггера. На фиг. 1 приведена структурная электрическая схема частотного компаратора; на фиг. 2а - временные диаграммы, поясняющие его работу при частоте fi fa на фиг. 26 - то же, при частоте f .гЧастотный компаратор содержит триггеры 1-4, элементы И 5-9, элемент 10 задержки, интегратор 11 и элемент 12 записи. Устройство работает следующим образом. В исходном состоянии на инверсных выходах RS-триггеров 2 и 4 сигнал равен единице. Сигналы сравниваемых частот fi и fa поступают на элементы 5 и 7 соответственно. Импульс с выхода элемента И 5 поступает на первый вход интегратора И и одновременно устанавливает триггер 1 в единичное состояние, с выхода которого сигнал поступает на первый вход элемента И 6. На второй вход элемента И 6 подается сигнал с инверсного выхода элемента И. Единичный сигнал элемента И 6, который формируется в момент окончания импульса на выходе элемента И 5, устанавливает в единичное состояние триггер, инверсный сигнал которого закрывает элемент И 5, а сигнал с его прямого выхода поступает на первый вход элемента И 9. Единичный сигнал с выхода элемента И 7 поступает на второй вход интегратора 11 и одновременно запускает триггер 3, с выхода которого сигнал посту-пает на первый вход элемента И 8. На второй вход элемента И 8 подается сигнал с инверсного выхода элемента И 7. Единичный сигнал на выходе элемента И 8, который формируется в момент окончания импульса на выходе элемента И 7, устанавливает в единичное состояние триггер 4, инверсный сигнал которого закрывает элемент И 7. Прямой сигнал триггера 4 поступает на второй вход элемента И 9. Сигнал с выхода элемента И 9 поступает на вход элемента 10 задержки, выходной сигнал которого подается на R-входы триггеров 1-4, сбрасывая их в исзсрдное состояние. Этим же сигналом сбрасывается интегратор 11. Время задержки сигнала выбирается.больщим или равным времени записи элемента 12. Таким образом, работа группы элементов 5, 1, 6 и 2 идентична работе группы элементов 3, 4, 7 и 8. Каждая из них разрешает прохождение сигналов сравниваемых частот на входы интегратора 11 только после прихода сигнала сброса на R-входы триггеров I-4 с выхода элемента 10 задержки, на вход которого сигнал поступает в момент окончания интегрирования последнего из двух сигналов, поступающих с выходов элементов И 5 и И 7. Устройство может работать в трех {Режимах. Частота f первого сравниваемого сигнала меньше частоты f второго сравниваемого сигнала. В этом случае с выхода элемента записи 12 снимается положительный сигнал. Частота f первого сравниваемого сигнала больше частоты f второго сравнив:аемого сигнала. В этом случае с выхода элемента 12 записи снимается отрицательный сигнал. Частоты сравниваемых сигналов р;авны. В этом случае выходной сигнал элеме.нта 12 записи равен нулю. Применение предлагаемого изобретения позволяет повысить надежность работы системы контроля компрессоров. Формула изобретения Частотный компаратор, содержащий пять элементов И, первый выход первого из которых соединен с первым входом первого триггера, второй вход которого подключен к первому входу второго триггера, первый выход которого соединен с первым входом второго элемента И, и третий триггер, первый вход которого подключен к первому выходу третьего элемента И, а выход - к первому входу четвертого элемента И, выход которого соединен с первым входом четвертого триггера, отличающийся тем, что, с целью повышения точности и быстродействия, в него введены элемент записи, интегратор и элемент задержки, вход которого соединен с выходом второго элемента И и первым входом элемента записи, второй вход которого соединен с выходом интегратора, первый вход которого соединен с первым входом первого триггера, выход которого подключен к первому входу пятого элемента И, второй вход - с вторым входом третьего триггера, подключенным также к вторым входам четвертого и первого триггеров, третьему входу интегратора и выходу элемента задержки, при этом первый выход четвертого триггера соединен с вторым входом второго элемента И, а второй выход - с первым входом третьего элемента -И, второй вход которого соединен с первой входной шиной, а второй выход - с вторым входом четвертого элемента И, причем второй выход второго триггера соединен с первым входом первого элемента И, второ:й вход которого подключен к второй входной щине, а второй выход соединен с вторым 1входом пятого элемента И, выход которого подключен к второму входу второго триггера. Источники информации, принятые во внимание при экспертизе 1.Егоров В. А. Частотный компаратор с линией задер ;ки.-«Измерительная техника, 1975, № 10. 2.Патент США № 3755746, кл. Н 03 D 13/00, 1973.

Авторы

Даты

1981-05-15—Публикация

1978-12-17—Подача