Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, рис.18.2а на стр.315 в книге Каяцкас А.А. Основы радиоэлектроники. М.: Высш. шк., 1988), которые реализуют простую симметричную булевую функцию τ2=х1х2∨x1х3∨х2х3, зависящую от трех аргументов - входных двоичных сигналов х1,х2,х3∈{0, 1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относится ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из четырех простых симметричных булевых функций, зависящих от четырех аргументов - входных двоичных сигналов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, логический модуль (патент РФ 2249844, кл. G 06 F 7/38, 2005 г.), который содержит два мажоритарных элемента, элемент "И", элемент "ИЛИ" и реализует любую из трех простых симметричных булевых функций τ1=х1∨х2∨х3, τ2=x1х2∨x1х3∨x2х3, τ3=х1х2х3, зависящих от трех аргументов - входных двоичных сигналов х1, х2, х3∈{0, 1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация любой из четырех простых симметричных булевых функций, зависящих от четырех аргументов - входных двоичных сигналов.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из четырех простых симметричных булевых функций, зависящих от четырех аргументов - входных двоичных сигналов.

Указанный технический результат при осуществлении изобретения достигается тем, что в логический модуль, содержащий два мажоритарных элемента, элемент "И" и элемент "ИЛИ", первый, второй входы которого соединены соответственно с первым, вторым входами элемента "И", а второй, первый входы и выход второго мажоритарного элемента подключены соответственно к выходу первого мажоритарного элемента, второму настроечному входу и выходу логического модуля, введены дополнительные элемент "И", элемент "ИЛИ" и третий мажоритарный элемент, выход и второй, третий входы которого соединены соответственно с третьим входом второго мажоритарного элемента и выходом элемента "ИЛИ", выходом дополнительного элемента "И", подключенного первым, вторым входами соответственно к первому, второму входам дополнительного элемента "ИЛИ", выход которого соединен с вторым входом первого мажоритарного элемента, подключенного третьим входом к выходу элемента "И", первый и второй входы которого соединены соответственно с первым и вторым информационными входами логического модуля, подключенного третьим, четвертым информационными и первым настроечным входами соответственно к первому, второму входам дополнительного элемента "ИЛИ" и объединенным первым входам первого, третьего мажоритарных элементов.

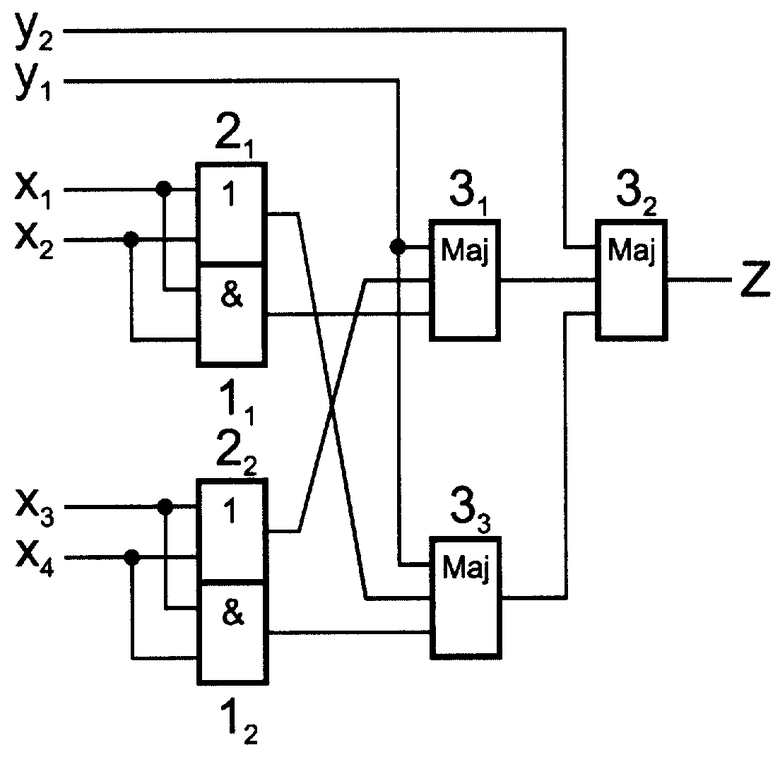

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит элемент "И" и дополнительный элемент "И" 11 и 12, элемент "ИЛИ" и дополнительный элемент "ИЛИ" 21 и 22, первый, второй и третий мажоритарные элементы 31, 32 и 33, причем первый, второй входы и выход элемента 11 соединены соответственно с первым, вторым входами элемента 21 и третьим входом элемента 31, подключенного вторым входом к выходу элемента 22, а первый, второй входы и выход элемента 12 соединены соответственно с первым, вторым входами элемента 22 и третьим входом элемента 33, подключенного вторым входом и выходом соответственно к выходу элемента 21 и третьему входу элемента 32, второй, первый входы и выход которого соединены соответственно с выходом элемента 31, вторым настроечным входом и выходом логического модуля, подключенного первым, вторым, третьим, четвертым информационными и первым настроечным входами соответственно к первому, второму входам элемента 21, первому, второму входам элемента 22 и объединенным первым входам элементов 31, 33.

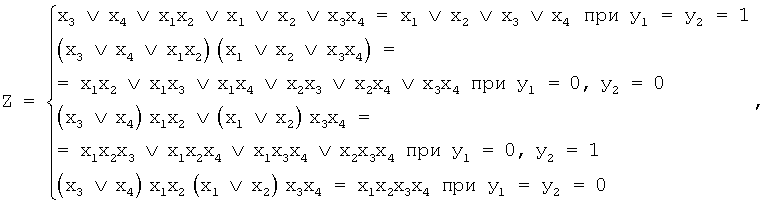

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый, ..., четвертый информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы х1, ..., х4∈{0, 1} и у1, у2∈{0, 1}. Сигнал на выходе мажоритарного элемента 3i(i∈{1, 2, 3}) равен "1" ("0") только тогда, когда на двух или на всех входах этого элемента действуют сигналы, равные "1" ("0"). Следовательно, если на первом входе элемента 3i присутствует "1" ("0"), то этот элемент будет выполнять операцию "ИЛИ" ("И") над сигналами, действующими на его втором и третьем входах. Таким образом, на выходе модуля имеем

где символами ∨ и · обозначены соответственно операции "ИЛИ" и "И".

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию любой из четырех простых симметричных булевых функций

τ1=x1∨x2∨x3∨x4, τ2=x1x2∨x1x3∨x1x4∨x2x3∨x2x4∨x3x4, τ3=x1x2x3∨x1x2x4∨x1x3x4∨x2x3x4, τ4=x1x2x3x4,

зависящих от четырех аргументов - входных двоичных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2004 |

|

RU2262733C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2005 |

|

RU2281545C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2417404C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2008 |

|

RU2398265C2 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2021 |

|

RU2776920C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2020 |

|

RU2758188C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2012 |

|

RU2472209C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2710871C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2703675C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2003 |

|

RU2249844C2 |

Изобретение относится к вычислительной технике. Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из четырех простых симметричных булевых функций, зависящих от четырех аргументов - входных двоичных сигналов. Он достигается тем, что в логическом модуле, содержащем два мажоритарных элемента, элемент "И" и элемент "ИЛИ", первый, второй входы которого соединены соответственно с первым, вторым входами элемента "И", а второй, первый входы и выход второго мажоритарного элемента подключены соответственно к выходу первого мажоритарного элемента, второму настроечному входу и выходу логического модуля, введены дополнительные элемент "И", элемент "ИЛИ" и третий мажоритарный элемент, выход и второй, третий входы которого соединены соответственно с третьим входом второго мажоритарного элемента и выходом элемента "ИЛИ", выходом дополнительного элемента "И", подключенного первым, вторым входами соответственно к первому, второму входам дополнительного элемента "ИЛИ", выход которого соединен с вторым входом первого мажоритарного элемента, подключенного третьим входом к выходу элемента "И", первый и второй входы которого соединены соответственно с первым и вторым информационными входами логического модуля, подключенного третьим, четвертым информационными и первым настроечным входами соответственно к первому, второму входам дополнительного элемента "ИЛИ" и объединенным первым входам первого, третьего мажоритарных элементов. 1 ил.

Логический модуль, предназначенный для реализации любой из четырех простых симметричных булевых функций, зависящих от четырех аргументов - входных двоичных сигналов, содержащий два мажоритарных элемента, элемент И и элемент ИЛИ, первый, второй входы которого соединены соответственно с первым, вторым входами элемента И, а второй, первый входы и выход второго мажоритарного элемента подключены соответственно к выходу первого мажоритарного элемента, второму настроечному входу и выходу логического модуля, отличающийся тем, что в него введены дополнительные элемент И, элемент ИЛИ и третий мажоритарный элемент, выход и второй, третий входы которого соединены соответственно с третьим входом второго мажоритарного элемента и выходом элемента ИЛИ, выходом дополнительного элемента И, подключенного первым, вторым входами соответственно к первому, второму входам дополнительного элемента ИЛИ, выход которого соединен с вторым входом первого мажоритарного элемента, подключенного третьим входом к выходу элемента И, первый и второй входы которого соединены соответственно с первым и вторым информационными входами логического модуля, подключенного третьим, четвертым информационными и первым настроечным входами соответственно к первому, второму входам дополнительного элемента ИЛИ и объединенным первым входам первого, третьего мажоритарных элементов.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2003 |

|

RU2249844C2 |

| МАЖОРИТАРНЫЙ МОДУЛЬ | 2003 |

|

RU2242044C1 |

| ЛОГИЧЕСКИЙ ПРОЦЕССОР | 2003 |

|

RU2251142C2 |

| US 5596763 А, 21.01.1997 | |||

| US 6150839 А, 21.11.2000 | |||

| US 5642304 А, 24.06.1997 | |||

| ЕР 0674356 А, 27.09.1995. | |||

Авторы

Даты

2006-10-27—Публикация

2005-07-08—Подача