Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, патент РФ 2704737, кл. G06F 7/57, 2019 г.), которые с помощью константной настройки реализуют любую из простых симметричных булевых функций τ2, τ0,5×(n+1), τn-1 зависящих от n аргументов - входных двоичных сигналов, при n=5.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация любой из функций τ2, τ0,5×(n+1), τn-1 при n=7.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (патент РФ 2709669, кл. G06F 7/57, 2019 г.), который содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре мажоритарных элемента и с помощью константной настройки реализует любую из простых симметричных булевых функций τ2, τ0,5×(n+1), τn-1, зависящих от n аргументов - входных двоичных сигналов, при n=5.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не обеспечивается реализация любой из функций τ2, τ0,5×(n+1), τn-1 при n=7.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации с помощью константной настройки любой из простых симметричных булевых функций τ2, τ0,5×(n+1), τn-1, зависящих от n аргументов - входных двоичных сигналов, при n=7.

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре мажоритарных элемента, i-й  вход j-го

вход j-го  и третий вход четвертого мажоритарных элементов соединены соответственно с i-ым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго мажоритарного элемента, а первый, третий входы третьего и i-й вход первого мажоритарных элементов соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым информационным входом логического модуля, особенность заключается в том, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и пятый, шестой мажоритарные элементы, i-й вход четвертого и второй вход пятого мажоритарных элементов соединены соответственно с i-ым входом и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход четвертого, третий вход пятого и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами первого, третьего и пятого, четвертого мажоритарных элементов, а второй вход третьего, первый, второй, третий входы второго и первый вход (i+3)-го мажоритарных элементов подключены соответственно к четвертому, пятому, шестому, седьмому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом шестого мажоритарного элемента.

и третий вход четвертого мажоритарных элементов соединены соответственно с i-ым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго мажоритарного элемента, а первый, третий входы третьего и i-й вход первого мажоритарных элементов соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым информационным входом логического модуля, особенность заключается в том, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и пятый, шестой мажоритарные элементы, i-й вход четвертого и второй вход пятого мажоритарных элементов соединены соответственно с i-ым входом и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход четвертого, третий вход пятого и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами первого, третьего и пятого, четвертого мажоритарных элементов, а второй вход третьего, первый, второй, третий входы второго и первый вход (i+3)-го мажоритарных элементов подключены соответственно к четвертому, пятому, шестому, седьмому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом шестого мажоритарного элемента.

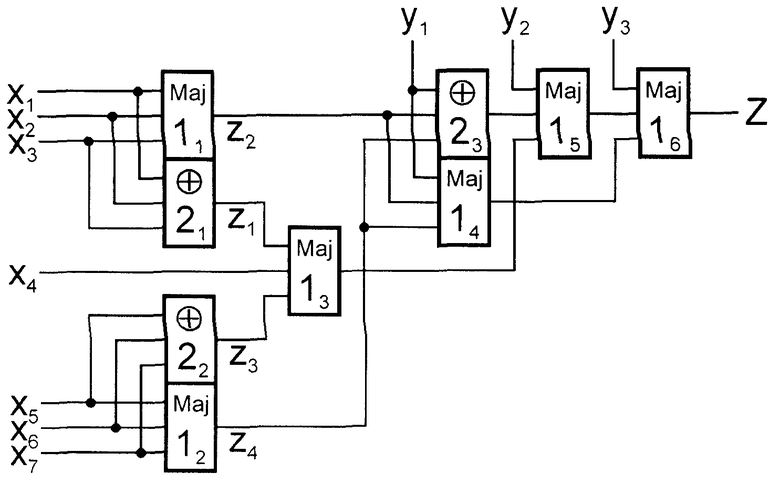

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит мажоритарные элементы 11, …, 16 и элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 21, 22, 23, причем i-й  вход элемента 1j

вход элемента 1j  и третий вход элемента 14, первый, третий входы элемента 13 соединены соответственно с i-ым входом элемента 2j и выходами элементов 12, 21, 22, i-й вход элемента 14 и второй вход элемента 15 соединены соответственно с i-ым входом и выходом элемента 23, второй вход элемента 14, третий вход элемента 15 и второй, третий входы элемента 16 соединены соответственно с выходами элементов 11, 13 и 15, 14, а первый, второй, третий входы элемента 1j, второй вход элемента 13 и первый вход элемента 1i+3 подключены соответственно к (4 × j-3)-му, (4 × j-2)-му, (4 × j-1)-му, четвертому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом элемента 16.

и третий вход элемента 14, первый, третий входы элемента 13 соединены соответственно с i-ым входом элемента 2j и выходами элементов 12, 21, 22, i-й вход элемента 14 и второй вход элемента 15 соединены соответственно с i-ым входом и выходом элемента 23, второй вход элемента 14, третий вход элемента 15 и второй, третий входы элемента 16 соединены соответственно с выходами элементов 11, 13 и 15, 14, а первый, второй, третий входы элемента 1j, второй вход элемента 13 и первый вход элемента 1i+3 подключены соответственно к (4 × j-3)-му, (4 × j-2)-му, (4 × j-1)-му, четвертому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом элемента 16.

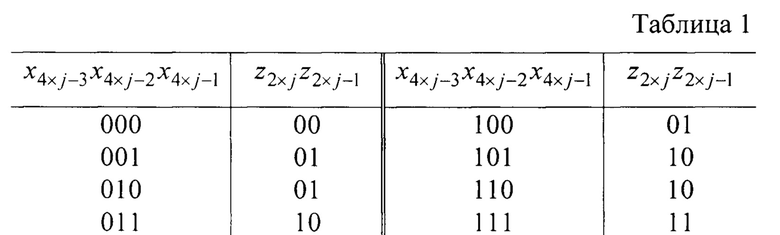

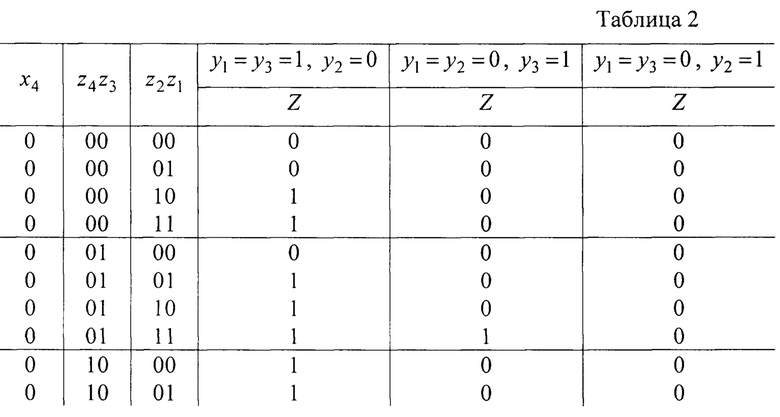

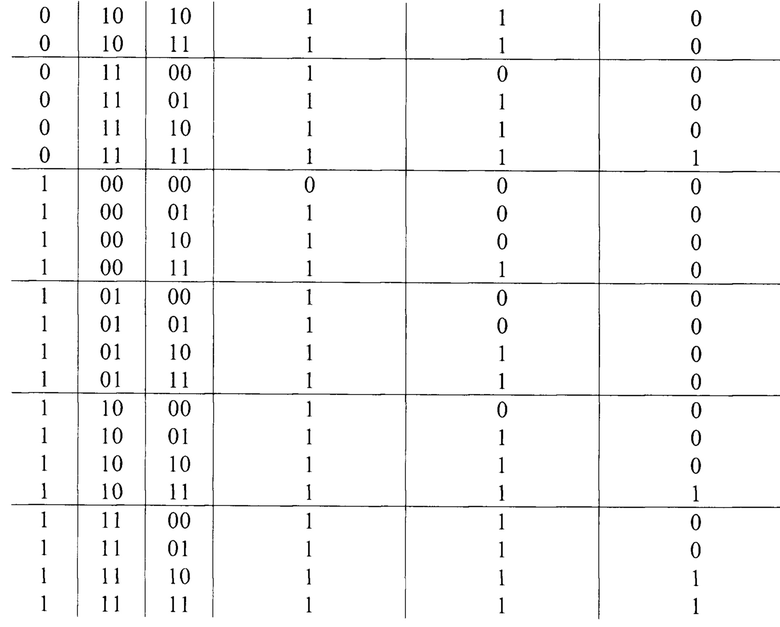

Работа предлагаемого логического модуля осуществляется следующим образом. На его первый, …, седьмой информационные и первый, второй, третий настроечные входы подаются соответственно двоичные сигналы х1, …, х7 ∈ {0,l} и сигналы y1, y2, y3 ∈ {0,1} константной настройки. В представленных ниже табл. 1 и табл. 2 приведены соответственно значения внутренних сигналов  z2×j предлагаемого логического модуля, полученные для всех возможных наборов значений сигналов x4×j-3, x4×j-2, x4×j-1, и значения его выходного сигнала Z, полученные для всех возможных наборов значений сигналов z1, …, z4,x4 при y1=y3=1, y2=0; y1=y3=0, y2=1.

z2×j предлагаемого логического модуля, полученные для всех возможных наборов значений сигналов x4×j-3, x4×j-2, x4×j-1, и значения его выходного сигнала Z, полученные для всех возможных наборов значений сигналов z1, …, z4,x4 при y1=y3=1, y2=0; y1=y3=0, y2=1.

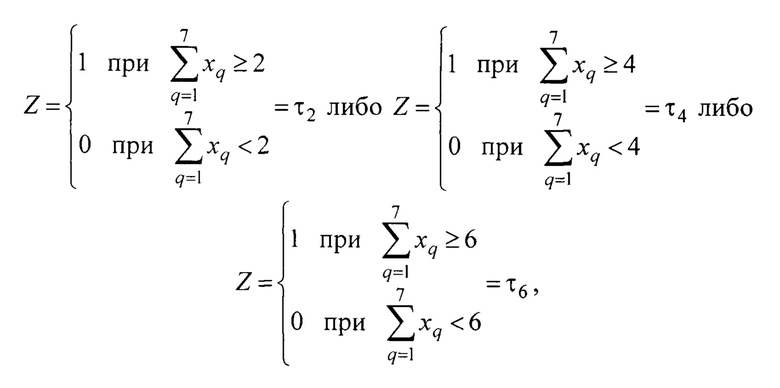

Если у1=у3=1, у2=0 либо y1=у2=0, y3=1 либо y1=у3=0, у2=1, то согласно табл. 1, табл. 2 имеем

где τ2, τ4, τ6 есть простые симметричные булевы функции семи аргументов х1, …, х7 (см. стр. 126 в книге Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974 г.).

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как с помощью константной настройки реализует любую из простых симметричных булевых функций τ2, τ0,5×(n+1), τn-1, зависящих от n аргументов - входных двоичных сигналов, при n=7.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2020 |

|

RU2757830C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2018 |

|

RU2704737C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2019 |

|

RU2710871C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2020 |

|

RU2758187C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2709669C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2758186C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2542895C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2017 |

|

RU2647639C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2016 |

|

RU2641454C2 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2757817C1 |

Изобретение относится к логическому модулю для реализации простых симметричных булевых функций. Технический результат заключается в расширении функциональных возможностей логического модуля. Логический модуль содержит шесть мажоритарных элементов и три элемента ИСКЛЮЧАЮЩЕЕ ИЛИ. За счет указанных элементов и новой схемы их соединения обеспечивается реализация любой из простых симметричных булевых функций τ2, τ0,5×(n+1), τn-1, зависящих от n аргументов - входных двоичных сигналов, при n=7. 1 ил., 2 табл.

Логический модуль, предназначенный для реализации простых симметричных булевых функций, содержащий два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четыре мажоритарных элемента, причем i-й  вход j-го

вход j-го  и третий вход четвертого мажоритарных элементов соединены соответственно с i-ым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго мажоритарного элемента, а первый, третий входы третьего и i-й вход первого мажоритарных элементов соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым информационным входом логического модуля, отличающийся тем, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и пятый, шестой мажоритарные элементы, i-й вход четвертого и второй вход пятого мажоритарных элементов соединены соответственно с i-ым входом и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход четвертого, третий вход пятого и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами первого, третьего и пятого, четвертого мажоритарных элементов, а второй вход третьего, первый, второй, третий входы второго и первый вход (i+3)-го мажоритарных элементов подключены соответственно к четвертому, пятому, шестому, седьмому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом шестого мажоритарного элемента.

и третий вход четвертого мажоритарных элементов соединены соответственно с i-ым входом j-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и выходом второго мажоритарного элемента, а первый, третий входы третьего и i-й вход первого мажоритарных элементов соединены соответственно с выходами первого, второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и i-ым информационным входом логического модуля, отличающийся тем, что в него введены третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и пятый, шестой мажоритарные элементы, i-й вход четвертого и второй вход пятого мажоритарных элементов соединены соответственно с i-ым входом и выходом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход четвертого, третий вход пятого и второй, третий входы шестого мажоритарных элементов соединены соответственно с выходами первого, третьего и пятого, четвертого мажоритарных элементов, а второй вход третьего, первый, второй, третий входы второго и первый вход (i+3)-го мажоритарных элементов подключены соответственно к четвертому, пятому, шестому, седьмому информационным и i-му настроечному входам логического модуля, выход которого соединен с выходом шестого мажоритарного элемента.

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2709669C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2018 |

|

RU2704737C1 |

| УНИВЕРСАЛЬНЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2015 |

|

RU2610678C1 |

| НАСТРАИВАЕМЫЙ ЛОГИЧЕСКИЙ МОДУЛЬ | 2016 |

|

RU2626343C1 |

Авторы

Даты

2022-07-28—Публикация

2021-06-17—Подача