Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны логические модули (см., например, рис.3.3 на стр.39 в книге Якубайтис Э.А. Асинхронные логические автоматы. Рига: Зинатне, 1966), которые реализуют простую симметричную булеву функцию τ1=x1∨x2∨x3, зависящую от трех аргументов - входных двоичных сигналов x1, x2, x3 ∈{0,1}.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных логических модулей, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация остальных простых симметричных булевых функций τ2=х1х2∨х2x3∨х2х3 и τ3=х1х2x3, зависящих от трех аргументов - входных двоичных сигналов х1, х2, х3 ∈{0,1}.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип логический модуль (см. рис.83 на стр.133 в книге Цифровые и аналоговые интегральные микросхемы: Справочник / С.В.Якубовский, Л.И.Ниссельсон, В.И.Кулешова и др. М.: Радио и связь, 1989), содержащий два мажоритарных элемента, каждый из которых реализует простую симметричную булеву функцию τ2=x1x2∨x1x3∨x2x3, где x1x2x3 - двоичные сигналы, действующие на входах элемента.

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относятся ограниченные функциональные возможности, обусловленные тем, что не выполняется реализация простых симметричных булевых функций τ1=х1∨x2∨x3 и τ3=x1x2x3.

Техническим результатом изобретения является расширение функциональных возможностей за счет обеспечения реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов.

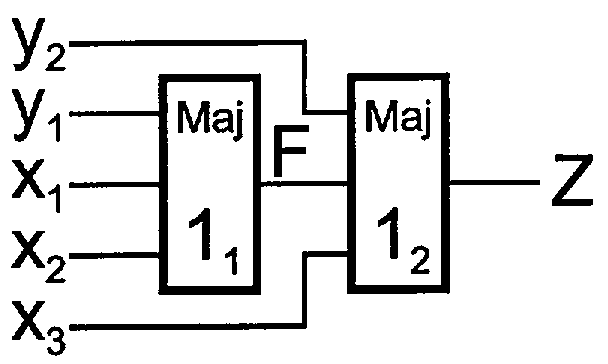

Указанный технический результат при осуществлении изобретения достигается тем, что в логическом модуле, содержащем два мажоритарных элемента, особенность заключается в том, что выход первого мажоритарного элемента соединен с вторым входом второго мажоритарного элемента, подключенного первым, третьим входами и выходом соответственно к второму настроечному, третьему информационному входам и выходу логического модуля, первый, второй информационные и первый настроечный входы которого образованы соответственно вторым, третьим и первым входами первого мажоритарного элемента.

На чертеже представлена схема предлагаемого логического модуля.

Логический модуль содержит первый и второй мажоритарные элементы 11 и 12, причем выход элемента 11 соединен с вторым входом элемента 12, подключенного первым, третьим входами и выходом соответственно к второму настроечному, третьему информационному входам и выходу логического модуля, первый, второй информационные и первый настроечный входы которого образованы соответственно вторым, третьим и первым входами элемента 11.

Работа предлагаемого логического модуля осуществляется следующим образом.

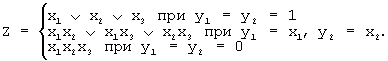

На его первый, второй, третий информационные и первый, второй настроечные входы подаются соответственно двоичные сигналы х1, х2, х3 ∈{0,1} и у1, у2 ∈{0,1}. Тогда сигнал на его выходе определяется выражением Z=y2F∨y2x3∨Fx3, где F=у1х1∨y1x2∨x1x2. Таким образом, предлагаемый модуль будет воспроизводить операцию

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый логический модуль обладает более широкими по сравнению с прототипом функциональными возможностями, так как обеспечивает реализацию любой из трех простых симметричных булевых функций τ1=х1∨x2∨x3, τ2=x1x2∨x1x3∨x2x3, τ3=x1x2x3, зависящих от трех аргументов - входных двоичных сигналов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2417404C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2005 |

|

RU2286594C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2005 |

|

RU2281545C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2518669C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2006 |

|

RU2303283C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2013 |

|

RU2542920C2 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2019 |

|

RU2718209C1 |

| ЛОГИЧЕСКИЙ МОДУЛЬ | 2003 |

|

RU2249844C2 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2003 |

|

RU2248034C1 |

| ЛОГИЧЕСКИЙ ПРЕОБРАЗОВАТЕЛЬ | 2020 |

|

RU2758186C1 |

Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др. Техническим результатом является расширение функциональных возможностей за счет реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов. Указанный результат достигается за счет того, что логический модуль содержит два мажоритарных элемента, причем выход первого мажоритарного элемента соединен с вторым входом второго мажоритарного элемента, подключенного первым, третьим входами и выходом соответственно к второму настроечному, третьему информационному входам и выходу логического модуля, первый, второй информационные и первый настроечный входы которого образованы соответственно вторым, третьим и первым входами первого мажоритарного элемента. 1 ил.

Логический модуль, предназначенный для реализации любой из трех простых симметричных булевых функций, зависящих от трех аргументов - входных двоичных сигналов, содержащий два мажоритарных элемента, отличающийся тем, что выход первого мажоритарного элемента соединен с вторым входом второго мажоритарного элемента, подключенного первым, третьим входами и выходом соответственно к второму настроечному, третьему информационному входам и выходу логического модуля, первый, второй информационные и первый настроечный входы которого образованы соответственно вторым, третьим и первым входами первого мажоритарного элемента.

| Д.А.Поспелов | |||

| Логические методы анализа и синтеза систем | |||

| - М.: Энергия, 1968, с.194 | |||

| Устройство для вычисления симметрических булевых функций | 1988 |

|

SU1517017A1 |

| Устройство для вычисления симметричных булевых функций | 1986 |

|

SU1396137A1 |

| Устройство для вычисления симметричных булевых функций | 1983 |

|

SU1179314A1 |

| US 5596763 A, 21.01.1997. | |||

Авторы

Даты

2005-10-20—Публикация

2004-03-05—Подача