Изобретение относится к автоматик и вычислительной технике и может быт использовано в управляющих вычислительных системах с времяраспределен- ными функциями, а также в средствах службы единого времени или системах подсчета ресурса работы устройства.

Цель изобретения - расширение области применения за счет обеспечения счета Б любой системе счисления.

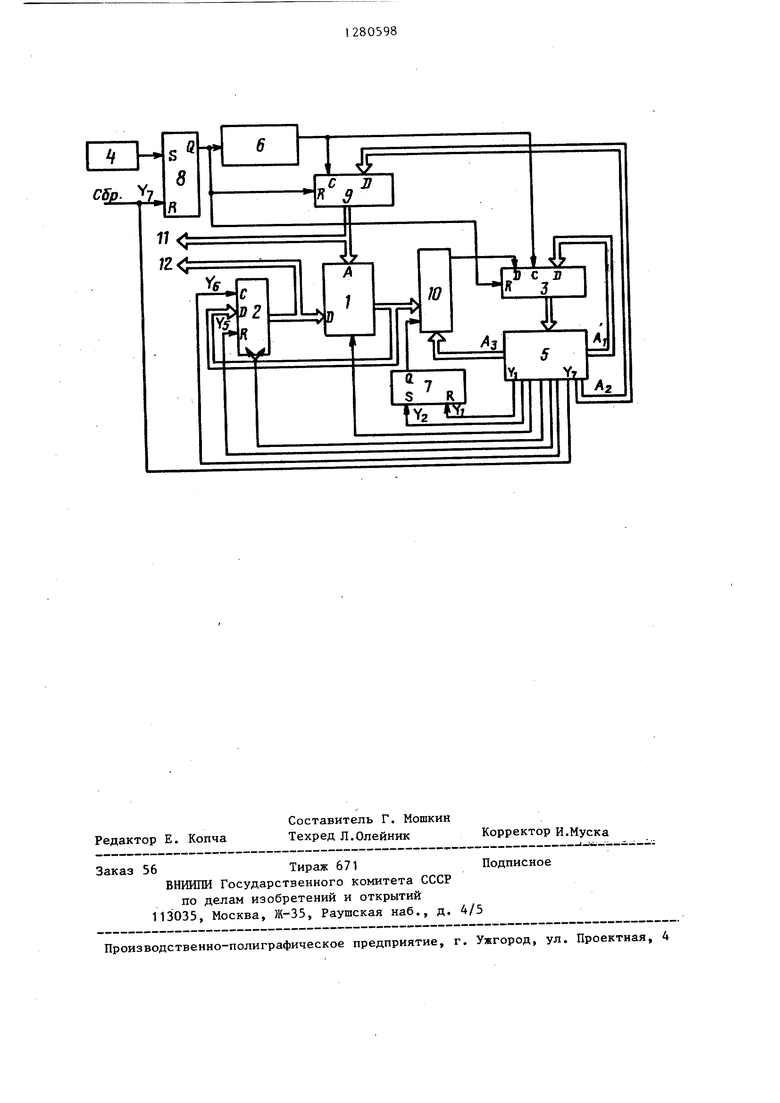

На чертеже изображена функциональная схема предлагаемого многоканального микропрограммного счетчика.

Многоканальный микропрограммный счетчик содержит блок 1 оперативной памяти, счетчик 2, регистр 3 адреса, генератор 4 импульсов, блок 5 памяти микропрограмм, ждущий мультивибратор 6, триггеры 7 и 8, буферный регистр 9, мультиплексор 10, группу выходов 11 номера коэффициента пересчета и группу выходов 12 значения коэффициента пересчета.

Блок 1 оперативной памяти предназначен для хранения значений всех параметров, причем каждому параметру соответствует определенная ячейка блока 1. Счетчик 2 предназначен для промежуточного запоминания соответствующего параметра, а также для изменения величины этого параметра. Регистр 3 адреса обеспечивает адресацию блока 5 памяти микропрограмм.

Генератор 4 импульсов необходим для формирования меток времени, определяющих точность измерения ресурса.

Блок 5 памяти микропрограмм предназначен для хранения микропрограмм, обеспечивающих обработку параметров (коэффициентов пересчета величин) в соответствии с алгоритмом работы счетчика.

Ждущий мультивибратор 6 обеспечивает формирование тактирующих импульсов, определяющих темп работы счетчика ресурса.

Триггер 7 обеспечивает запоминани сигнала переполнения младшего (по отношению к обрабатываемому) разряда

Триггер 8 обеспечивает отработку полного рабочего цикла счетчика.

Буферный регистр 9 предназначен для хранения адреса (номера) соответствующего параметра на время его обработки.

Мультиплексор 10 обеспечивает поразрядную коммутацию соответствую

5

щего параметра для его поразрядного анализа, а также анализ состояния триггера 7.

Выходные магистрали 11 и 12 предназначены для вывода информации с устройства, причем магистраль 11 указывает номер параметра, а магистраль 12 - его текущее значение.

Группы разрядов А и Aj блока 5 памяти микропрограммы (фиг. 1) предназначены для адресации соответственно блока 5 памяти микропрограмм и блока 1 оперативной памяти.

Группа разрядов блока 5 памяти микропрограмм А (фиг. 1) обеспечивает управление мультиплексором 10 для поразрядной коммутации значения соответствующего параметра при его анализе на равенство заданному коэф0 фициенту пересчета. Анализ ведется программным путем с помощью соответствующих микропрограмм, реализуемых блоком 5 памяти микропрограмм.

Микрокоманды Y, и Yj обеспечи вают управление триггером 7: соответственно сброс на О и установку его в единичное состояние.

Микрокоманда Yj обеспечивает рабочий режим ЗАПИСЬ/ЧТЕНИЕ блока 1 one0 ративной памяти. При этом при обеспечивается режим чтения информации из блока 1, а при Yj 1 - запись информации в блок 1. Микрокоманда Y обеспечивает инкремент счет5 чика 2, а микрокоманда Yj - его обнуление. Шкрокоманда Y. служит для

Ь

записи информации в счетчик 2. Микрокомандой Y осуществляется сброс в О содержимого триггера 8.

0 Многоканальный микропрограммный счетчик предназначен для определения длительности работы некоторой аппаратуры или ее основных узлов . (устройств). Подсчет ресурса произво5 ftитcя путем подсчета временных меток, формируемых генератором импульсов за время подачи питания на устройство.

Перед началом работы счетчик при0 водится в исходное состояние. Исходным считается нулевое состояние всех элементов оперативной памяти: ячеек блока 1, регистра 3 адреса, буферного регистра 9, счетчика 2, триггеров

5 7 и В.

Обнуление производится подачей внешнего сигнала Сброс на R-вход триггера 8, тогда нулевым значением своего Q-выхода триггер 8 обнуляет

буферный регистр 9 и регистр 3 адреса. В свою очередь, нулевым значением регистра 3 адреса считывается нулевое микропрограммное слово с блока 5 памяти микропрограмм, в котором зафик сированы микрокоманды Y и , обнуляющие состояния соответственно триггера 7 и счетчика 2,

По окончании обнуления сигналом от генератора 4 импульсов производится установка в единичное состояние триггера 8, сигналом с Q-выхода которого запускается ждущий мультивибратор 6, обеспечивающий формирование синхроимпульсов, осуществляющих синхронизацию работы устройства.

Всю работу устройства можно представить совокупностью частных циклов Туг, составляющих полный цикл Т . Каходому частному циклу соответствует подпрограмма обработки соответствующего параметра. Количество параметров обусловливается, с одной стороны точностью счетчика ресурса, а с другой стороны - величиной максимально- го коэффициента пересчета.

Каждый из циклов делится на щаги, и на каждом шаге выполняются соответствующие микрооперации.

Все циклы выполняются аналогично, кроме первого и последнего, которые отличаются лишь операторами входа и выхода соответствующих подпрограмм. Разница в представлении подпрограмм, реализующих соответствующий параметр заключается также в привязке их к соответствующим ячейкам (адресам) блока 5 памяти микропрограмм и размещении значений соответствующих параметров в блоке 1 оперативной памяти.

Под параметрами счетчика ресурса понимаются коэффициенты пересчета, служащие для подсчета количества единиц, десятков, сотен и десятков сотен миллисекунд,.единиц, десятков секунд, единиц, десятков минут, единиц, десятков, сотен, тысяч и т.д. часов.

Каждый параметр представляется двоично-десятичным кодом в соответствующей ячейке блока 1 оперативной памяти, начиная с нулевой.

Таким образом, количество ячеек блока 1 оперативной памяти, необходимое для реализации устройства, равно количеству коэффициентов пересчета параметров счетчика ресурса (п):

N п

(1)

5

0 5

0 5 0

5

0

5

Таким образом, работа счетчика складывается из п циклов, а каждый цикл состоит из га шагов (пит- натуральные целые числа).

Обобщенный алгоритм работы устройства на первом цикле можно представить следующим образом.

Из блока 1 оперативной памяти производится считывание содержимого соответствующей ячейки. Это содержимое представляет собой двоичный четырехразрядный код (так как пересчет ведется в двоично-десятичном коде), отображающий величину соответствующего пересчетного коэффициента.

Этот код поразрядно (расчленяется на мультиплексоре 10) с помощью соответствующей микропрограммы, реализу- гмой в блоке 5 памяти микропрограмм, адресуемом через регистр 3 адреса, анализируется на предмет равенства его пересчетному коэффициенту соответствующего параметра.

В случае равенства текущего и заданного значений пересчетного коэффициента производится запоминание единицы переноса в старший разряд на триггере 7 (триггер 7 в этом случае устанавливается в состояние 1). Счетчик 2, на котором зафиксировано текущее значение пересчетного коэффициента, обнуляется, и его нулевое содержимое записывается в блок 1 оперативной памяти по адресу, с которого пересчетный коэффициент считывался.

Если текущее и заданное значения коэффициента пересчета не равны, то производится увеличение содержимого счетчика 2 на единицу н запись нового значения в ячейку блока 1 оперативной памяти по установленному на буферном регистре 9 адресу.

Перечисленные действия повторяются и в других циклах с той лишь раз- ницей, что суммирование единицы к текущему значению пересчетного коэффициента, выбираемого из блока 1 оперативной памяти, производится перед анализом текущего значения пересчетного коэффициента в случае, если на предыдущем цикле триггер 7 был установлен в состояние 1, т.е. имел место перенос из предыдущего разряда, иначе - имело место переполнение предьщущего пересчетного коэффициента.

образом, что на каждом шаге с помощью группы разрядов А управление передается из предыдущего микропрограммно го слова в последующее.

При- выполнении последнего микропрограммного слова или при неравенстве заданному значению.первого из последовательно анализируемых коэффициентов пересчета производится обнуление триггера 8, который сигналом с Q-выхода обнуляет содержимое буферного регистра 9 и регистра i 3 адреса.

Процесс вычисления начинается вновь после поступления очередного импульса от генератора 4 импульсов. Формула изобретения

Многоканальный микропрограммный счетчик, содержащий блок оперативной

памяти, выходы которого соединены с информационными входами счетчика, регистр адреса, выходы счетчика соединены с информационными входами бло- 25 микроопераций группы блока памяти ка оперативной памяти, генератор им- микропрограмм соединены соответст-З апуска ждущего мультивибратора, а входы установки в 1 и О второго триггера соединены соответственно с выходом генератора импульсов и с входом сброса устройства, первый, второй, третий, четвертый, пя.тый,

.шестой И седьмой выходы группы поля

венно с входами установки в О и 1 первого триггера, входом запис чтения блока оперативной памяти, с счетным входом установки в О и в дом записи счетчика, с входом уста новки в О второго триггера, прям выход которого соединен также с вх дами установки в О буферного рег стра и регистра адреса, а информац онные выходы буферного регистра и счетчика подключены соответственно группе выходов номера коэффициента йересчета устройсугва и группе вьпсо

пульсов, блок памяти микропрограмм, группа выходов первого адресного поля которого подключена к первой группе информационных входов регистра адреса, выходы которого соединены с адресными входами блока памяти микропрограмм, отличающийся тем, что, с целью расширения области применения за счет обеспечения счета в любой системе счисления, в него введены ждущий мультивибратор, два триггера, буферный регистр и мультиплексор, п информационных входов которого соединены с п выходами блока 40 iflOB значения коэффициента пересчета

оперативной памяти, где п - разрядмикроопераций группы блока памяти микропрограмм соединены соответстные входы которого соединены с выходами буферного регистра, информационные входы которого соединены с . группой выходов второго адресного поля блока памяти микропрограмм,группа выходов поля анализа коэффициентов пересчета которого соединена с управляющими входами мультиплексора (п+1)-й информационный вход которого подключен к прямому выходу первого триггера, а выход мультиплексора соединен с вторым информационным, входом регистра адреса, синхро- вход которого соединен с выходом ждщего мультивибратора, прямой выход второго триггера соединен с входом

-З апуска ждущего мультивибратора, а входы установки в 1 и О второго триггера соединены соответственно с выходом генератора импульсов и с входом сброса устройства, первый, второй, третий, четвертый, пя.тый,

.шестой И седьмой выходы группы поля

микроопераций группы блока памяти микропрограмм соединены соответст

венно с входами установки в О и 1 первого триггера, входом записи чтения блока оперативной памяти, со счетным входом установки в О и входом записи счетчика, с входом уста- новки в О второго триггера, прямой выход которого соединен также с входами установки в О буферного регистра и регистра адреса, а информационные выходы буферного регистра и счетчика подключены соответственно к группе выходов номера коэффициента йересчета устройсугва и группе вьпсоустройства.

Редактор E. Копча

Составитель Г. Мошкин Техред Л,Олейник

Заказ 56Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Корректор И.Муска

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство для умножения | 1984 |

|

SU1176325A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Многоканальный микропрограммный умножитель частоты | 1983 |

|

SU1144107A1 |

| Устройство для ввода информации | 1986 |

|

SU1352479A1 |

| Многоканальное устройство для сопряжения двух ЭВМ | 1985 |

|

SU1312585A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1287155A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в управля- кщих вычислительных системах с времяраспределейными функциями, а также в средствах службы единого времени или системах подсчета ресурса работы устройств. Цель изобретения - расширение области применения за счет обеспечения счета в любой системе счисления. Устройство содержит блок оперативной памяти, счетчик, регистр адреса, генератор импульсов, блок памяти микропрограмм, ждущий мультивибратор, два триггера, буферный регистр и мультиплексор. Новым в ройстве является использование ждущего мультивибратора, двух триггеров, буферного регистра и мультиплексора, что Позволяет реализовать счет в любой, системе счисления. 1 ил. СЛ С

| Таймер | 1981 |

|

SU1038931A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР 1159435, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-12-30—Публикация

1985-07-04—Подача