Изобретение относится к устройствам вычислительной техники. Оно может быть использовано в электрически перепрограммируемых постоянных запоминающих устройствах, сохраняющих информацию при отключении источника питания, нашедших широкое применение в блоках памяти вычислительных машин, в устройствах автоматики.

Известен матричный накопитель для постоянного электрически перепрограммируемого запоминающего устройства на МОП-транзисторах [1] Низкая степень интеграции является основным недостатком этого матричного накопителя.

Наиболее близким техническим решением к предложенному является матричный накопитель для электрически перепрограммируемого постоянного запоминающего устройства [2] За счет использования двух транзисторных ячеек памяти (запоминающего транзистора с плавающим и управляющим затворами, ключевого МДП-транзистора) обеспечивается высокая надежность работы матричного накопителя, построчное стирание информации, более длительное хранение информации при отключении источника питания. Этот матричный накопитель принят за прототип.

Матричный накопитель содержит полупроводниковую подложку первого типа проводимости с углублениями в ней, в поверхностном слое которой размещена первая группа разрядных диффузионных шин второго типа проводимости, и между ними в углублениях полупроводниковой подложки первого типа проводимости расположен диффузионный слой первого типа проводимости.

На поверхности полупроводниковой подожки расположен первый диэлектрический слой с отверстиями, в которых на поверхности полупроводниковой подложки расположен второй диэлектрический слой, на поверхности которого расположен третий диэлектрический слой.

На поверхности второго диэлектрического слоя размещены поликремниевые электроды, на поверхности первого и третьего диэлектрических слоев расположена первая группа адресных поликремниевых шин. На поверхности поликремниевых электродов расположен четвертый диэлектрический слой, на поверхности которого расположена вторая группа адресных поликремниевых шин над поликремниевыми электродами между адресными поликремниевыми шинами первой группы.

На поверхности четвертого диэлектрического слоя и адресных поликремниевых шин второй группы расположен пятый диэлектрический слой с отверстиями, на поверхности которого и в отверстиях диэлектрического слоя на поверхности полупроводниковой подложки размещена вторая группа разрядных металлических шин перпендикулярно диффузионным шинам первой группы.

В приповерхностном слое полупроводниковой подложки между адресными поликремниевыми шинами первой группы размещены первая группа диффузионных шин второго типа проводимости, между поликремниевыми электродами и адресными шинами первой группы под вторым диэлектрическим слоем вторая группа диффузионного слоя второго типа проводимости.

В местах пересечения разрядных и адресных шин образованы ячейки памяти в виде последовательно соединенных запоминающих n-канальных МДП-транзисторов с плавающими и управляющими затворами с электрически изменяемым пороговым напряжением и n-канальных ключевых МДП-транзисторов с постоянным пороговым напряжением.

Разрядные диффузионные шины первой группы являются истоками запоминающих транзисторов, поликремниевые электроды их плавающими затворами, адресные поликремниевые шины второй группы управляющими затворами, вторая группа диффузионных шин второго типа проводимости стоками запоминающих транзисторов, истоками ключевых МДП транзисторов, затворами которых является первая группа адресных поликремниевых шин, стоками первая группа диффузионных шин второго типа проводимости, соединенная с разрядными металлическими шинами.

Недостатком матричного накопителя является низкая степень интеграции из-за наличия одного контактного соединения на каждые две ячейки памяти, первой и второй групп диффузионных шин второго типа проводимости.

Целью изобретения является повышение степени интеграции матричного накопителя.

Поставленная цель достигается тем, что в матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости с углублениями в ней, в приповерхностном слое которой размещена первая группа разрядных диффузионных шин второго типа проводимости, между ними в углублениях полупроводниковой подложки расположен диффузионный слой первого типа проводимости, на поверхности полупроводниковой подложки расположен первый диэлектрический слой с отверстиями, в которых на поверхности полупроводниковой подложки расположен второй диэлектрический слой, на поверхности которого расположен третий диэлектрический слой, на поверхности второго диэлектрического слоя размещены поликремниевые электроды, на поверхности первого и третьего диэлектрических слоев расположена первая группа адресных проводящих шин, на поверхности поликремниевых электродов размещен четвертый диэлектрический слой, на поверхности которого расположена вторая группа адресных проводящих шин над поликремниевыми электродами между адресными поликремниевыми шинами первой группы, пятый диэлектрический слой, вторую группу разрядных проводящих шин, введены шестой и седьмой диэлектрические слои, разрядные проводящие шины второй группы выполнены диффузионными второго типа проводимости и расположены в углублениях в приповерхностном слое полупроводниковой подложки параллельно разрядным проводящим шинам первой группы, адресные проводящие шины первой группы выполнены с выступами и размещены перпендикулярно разрядным диффузионным шинам первой и второй групп, на поверхности адресных проводящих шин первой группы расположен пятый диэлектрический слой, на поверхности торцов выступов которого расположен шестой диэлектрический слой, на поверхности первого, третьего, пятого и шестого диэлектрических слоев расположен седьмой диэлектрический слой с отверстиями, совпадающими с отверстиями в первом диэлектрическом слое. Пятый и шестой диэлектрические слои выполнены из двуокиси кремния толщиной в 5-10 раз более и в 10 раз менее толщины второго диэлектрического слоя соответственно.

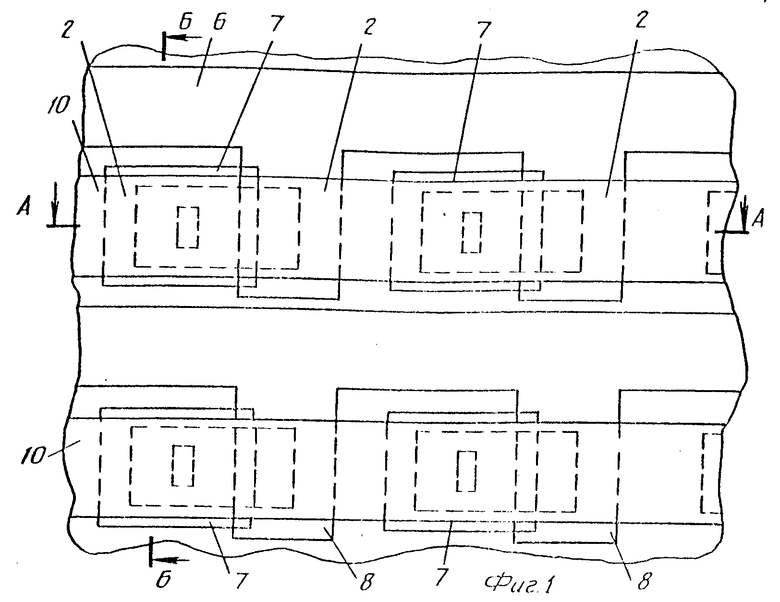

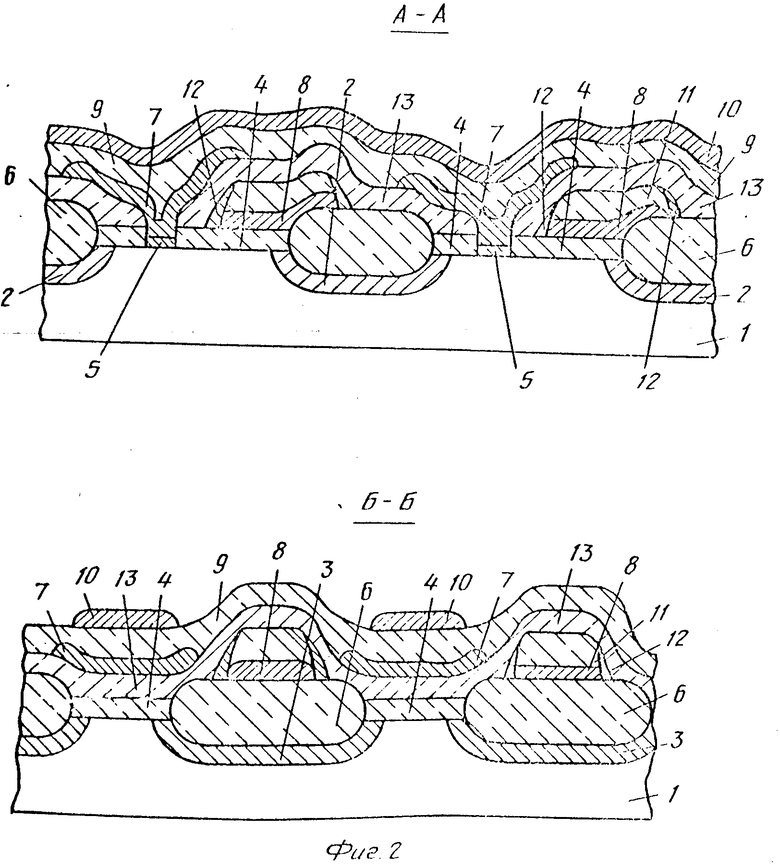

На фиг. 1 приведена схема матричного накопителя, на фиг. 2 то же, продольное сечение по А-А и поперечное сечение по Б-Б.

Матричный накопитель содержит полупроводниковую подложку 1 с углублениями в ней, первую и вторую группы разрядных проводящих шин 2, например диффузионных, второго типа проводимости, диффузионный слой 3 первого типа проводимости, первый, второй, третий диэлектрические слои 4, 5 и 6, поликремниевые электроды 7, первую групп адресных проводящих, например, поликремниевых, шин 5 с выступами, четвертый диэлектрический слой 9, вторую группу адресных проводящих, например, металлических, шин 10, пятый, шестой и седьмой диэлектрические слои 11, 12 и 13.

В углублениях в приповерхностном слое полупроводниковой подложки 1 размещены первая и вторая группы разрядных проводящих шин 2 параллельно друг другу, между ними диффузионный слой 3. На их поверхности расположен диэлектрический слой 6. На поверхности полупроводниковой подложки 1 расположены диэлектрические слой 4 и 5. На поверхности диэлектрического слоя 6 размещены адресные проводящие шины 8 первой группы перпендикулярно разрядным проводящим шинам 2, их выступы расположены на поверхностях диэлектрических слоев 4 и 6 с перекрытием с одной стороны краев разрядных проводящих шин 2 первой группы, на торцах шин 8 расположен диэлектрический слой 12, на их поверхности диэлектрический слой 11.

На поверхностях диэлектрических слоев 4, 6, 11 и 12 расположен диэлектрический слой 13 с отверстиями, совпадающими с отверстиями в диэлектрическом слое 4. На поверхности диэлектрических слоев 4, 5 и 13 размещены поликремниевые электроды 7 с перекрытием краев разрядных проводящих шин 2 второй группы, торцов проводящих шин 8. На поверхности поликремниевых электродов 7, диэлектрического слоя 13 расположен диэлектрический слой 9, на поверхности которого над поликремниевым и электродами 7 размещены проводящие адресные шины 10 второй группы.

В местах пересечения разрядных и адресных шин образованы ячейки памяти в виде последовательно соединенных запоминающих п-канальных МДП-транзисторов с плавающими и управляющими затворами с электрически изменяемым пороговым напряжением и п-канальных ключевых МДП-транзисторов с постоянным пороговым напряжением.

Разрядные диффузионные шины 2 первой группы являются истоками запоминающих транзисторов, поликремниевые электроды 7 их плавающими затворами, адресные проводящие шины 10 их управляющими затворами, адресные проводящие шины 8 затворами ключевых МДП-транзисторов, разрядные проводящие шины 2 второй группы их стоками, выступы адресных проводящих шин 8 первой группы являются стирающими затворами запоминающих транзисторов.

Сущность работы матричного накопителя заключается в следующем.

В режиме одновременного стирания информации на всех запоминающих транзисторах матричного накопителя на адресные шины 8 первой группы подают высокое положительное напряжение (20-25В) малой длительности (10 мс), на адресные шины 10 второй группы и разрядные шины 2 нулевое напряжение относительно полупроводниковой подложки 1.

Под действием падения напряжения на диэлектрических слоях 12, 13 создается высокая напряженность электрического поля в диэлектрических слоях, дырки инжектируются с торцов поликремниевых выступов 8, туннелируют через диэлектрические слоя 12, 13 и захватываются поликремниевыми электродами 7. В результате пороговые напряжения запоминающих транзисторов становятся отрицательными, что эквивалентно единичному состоянию в режиме считывания информации.

В режиме построчного стирания информации только на выбранную адресную шину 8 первой группы подают высокое напряжение, на остальные нулевое. В результате пороговые напряжения запоминающих транзисторов выбранной строки становятся отрицательными.

Программирование нулевого состояния проводят в заданные ячейки памяти в произвольной последовательности, при этом состояние невыбранных ячеек памяти сохраняется неизменным.

Для программирования нулевого состояния выбранной ячейки памяти (сохранения исходного состояния) на все адресные шины 8 первой группы подают нулевое напряжение, все ключевые МДП-транзисторы находятся в закрытом состоянии. На выбранную разрядную шину 2 подают нулевое напряжение, на остальные положительное напряжение (15-20 В). На выбранную адресную шину 10 второй группы подают положительное напряжение (25 В) малой длительности (1 мс), на остальное нулевое.

Под действием положительного напряжения на адресной шине 10 в приповерхностном слое полупроводниковой подложки 1 формируется (не формируется) инверсионный слой, примыкая к краям разрядных шин 2. Электроны инжектируются (не инжектируются) из разрядной шины 2 в инверсионный слой, туннелируют (не туннелируют) через диэлектрической слой 5, захватываются (не захватываются) поликремниевым электродом 7, увеличивая пороговое напряжение запоминающего транзистора, что эквивалентно нулевому состоянию в режиме считывания информации.

Состояние остальных запоминающих транзисторов сохраняется неизменным из-за нулевого напряжения на адресных шина 10 или малой разности потенциалов между разрядной шиной 2 и поликремниевым электродом 7, в результате чего отсутствует туннелирование электронов через диэлектрический слой 5.

В режиме считывания информации на адресные шины 10 подают нулевое напряжение, на выбранную адресную шину 8 низкое положительное напряжение (+5В), на остальные нулевое, между разрядными шинами 2 низкое положительное напряжение (+5В). При этом ключевые МДП-транзисторы выбранной строки находятся в открытом состоянии.

Через выбранные разрядные шины 2 протекает (не протекает) ток, если пороговое напряжение запоминающего транзистора отрицательное (положительное), что эквивалентно единичному (нулевому) состоянию. Через остальные разрядные шины 2 ток не протекает, т.к. или напряжение на адресных шинах 8, 10 равно нулю, или напряжение между разрядными шинами равно нулю.

Матричный накопитель может быть изготовлен на кремниевой полупроводниковой подложке типа КДБ 7, 5. Первый, второй, третий, пятый, шестой диэлектрические слои выполнены из двуокиси кремния толщиною соответственно 0,1, 0,02, 1-2, 0,5-1 и 0,002 мкм, четвертый и седьмой диэлектрические слои из нитрида кремния толщиной 0,06-0,08 мкм.

Разрядные диффузионные шины первой и второй групп легированы фосфором, ширина их 5 мкм, расстояние между ними 11 мкм. Адресные поликремниевые шины легированы фосфором, ширина их 4 мкм, расстояние между ними 4 мкм, ширина их выступов 12 мкм. Диффузионный слой легирован бромом. Размеры поликремниевого электрода 10 х 11 мкм2, отверстия в диэлектрическом первом слое 4 х 4 мкм2, площадь ячейки памяти 320 мкм2.

Седьмой диэлектрический слой выполнен из нитрида кремния для увеличения напряженности электрического поля в шестом диэлектрическом слое из двуокиси кремния из-за более высокой (в два раза) диэлектрической проницаемости, что позволяет увеличить ток инжекции дырок в режиме стирания информации. Для увеличения числа циклов перепрограммирования информации концентрация ловушек в диэлектрическом слое из нитрида кремния должно быть менее 101 см-3.

Если толщина седьмого диэлектрического слоя в 3-4 раза превышает толщину второго диэлектрического слоя, то увеличивается напряжение стирания и уменьшается крутизна запоминающего транзистора, если же толщина седьмого слоя меньше, то ухудшаются изолирующие свойства. Если толщина шестого диэлектрического слоя из двуокиси кремния в 10 раз меньше толщины второго диэлектрического слоя, уменьшается ток инжекции дырок.

Для уменьшения емкости перекрытия между адресной поликремниевой шиной и поликремниевым электродом, уменьшения величины напряжения стирания толщины пятого диэлектрического слоя должна быть в 5-10 раз больше толщины второго диэлектрического слоя. Увеличение его толщины усложняет технологический процесс изготовления.

Использование нитрида кремния в качестве четвертого диэлектрического слоя позволяет увеличить коэффициент передачи напряжения с адресной поликремниевой шины на поликремниевый электрод, крутизну ВАХ запоминающего транзистора из-за большей его диэлектрической проницаемости, чем у диэлектрика из двуокиси кремния, выполнять адресные шины металлическими для повышения быстродействия при считывании информации. Увеличение толщины четвертого диэлектрического слоя приведет к уменьшению крутизны запоминающего транзистора, увеличению площади ячейки памяти, увеличению напряжения программирования. Уменьшение толщины этого диэлектрического слоя приведет к уменьшению надежности работы из-за необходимости накопления заряда большей величины на поликремниевом электроде, ухудшения его изолирующих свойств.

Основными преимуществами матричного накопителя по отношению к прототипу являются:

повышение степени его интеграции в 1,4 раза за счет размещения поликремниевых электродов с перекрытием края адресных поликремниевых шин и выполнения разрядных шин диффузионными, что позволяет исключить диффузионный слой второго типа проводимости, контактные соединения с ним,

повышение надежности его работы за счет размещения второго диэлектрического слоя малой толщины над нелегированной поверхностью полупроводниковой подложки, что снижает дефектность этого диэлектрического слоя;

увеличение числа циклов перепрограммирования за счет уменьшения времени воздействия сильных электрических полей в диэлектрических слоях, так как перепрограммирование информации осуществляется через разные диэлектрические слои.

1. Матричный накопитель для постоянного запоминающего устройства, содержащий полупроводниковую подложку первого типа проводимости с углублениями в ней, в приповерхностном слое которой размещены первая группа разрядных диффузионных шин второго типа проводимости и между ними в углублениях полупроводниковой подложки первого типа проводимости диффузионный слой первого типа проводимости, на поверхности полупроводниковой подложки расположен первый диэлектрический слой с отверстиями, в которых на поверхности полупроводниковой подложки расположен второй диэлектрический слой, на поверхности которого расположен третий диэлектрический слой, на поверхности второго диэлектрического слоя размещены поликремниевые электроды, на поверхности первого и третьего диэлектрических слоев расположена первая группа адресных проводящих шин, на поверхности поликремниевых электродов размещен четвертый диэлектрический слой, на поверхности которого расположены вторая группа адресных проводящих шин над поликремниевыми электродами между адресными поликремниевыми шинами первой группы, пятый диэлектрический слой, вторую группу разрядных проводящих шин, отличающийся тем, что, с целью повышения степени интеграции матричного накопителя, он содержит шестой и седьмой диэлектрические слои, разрядные проводящие шины второй группы выполнены диффузионными второго типа проводимости и расположены в углублениях в приповерхностном слое полупроводниковой подложки параллельно разрядным проводящим шинам первой группы, адресные проводящие шины первой группы выполнены с выступами и размещены перпендикулярно разрядным диффузионным шинам первой и второй групп, на поверхности адресных проводящих шин первой группы расположен пятый диэлектрический слой, на поверхности торцов выступов которого расположен шестой диэлектрический слой, на поверхности первого, третьего, пятого и шестого диэлектрических слоев расположен седьмой диэлектрический слой с отверстиями, совпадающими с отверстиями в первом диэлектрическом слое.

2. Накопитель по п.1, отличающийся тем, что пятый и шестой диэлектрические слои выполнены из двуокиси кремния толщиной в 5 - 10 раз более и в 10 раз менее толщины второго диэлектрического слоя соответственно.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США N 4101921, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Электроника, N 5, 1980, с | |||

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

Авторы

Даты

1997-05-27—Публикация

1982-03-04—Подача