Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения.

Известны схемы дифференциальных операционных усилителей (ОУ), реализованных на основе входных каскадов с расширенным диапазоном активной работы - мостовых дифференциальных каскадов (ДК), а также каскадов на основе «бриллиантовых» транзисторов [1-32]. По такой архитектуре, на модификации которой и на ее применение выдано около 50 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.), а также многие ОУ с токовой обратной связью LM6181 и др.

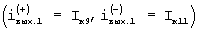

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный операционный усилитель, описанный в патенте США №5512859. Он содержит входной каскад 1 с расширенным диапазоном активной работы, имеющий первый выход 2, согласованный с шиной положительного источника питания 4, второй выход 5, согласованный с шиной отрицательного источника питания 6, двухтактный выходной каскад 7, имеющий первый вход 8, согласованный с шиной положительного источника питания 4, и второй вход 9, согласованный с шиной отрицательного источника питания 6.

Существенный недостаток известного ДУ состоит в том, что при достижении в нем предельно возможных значений максимальной скорости нарастания выходного напряжения в режиме большого сигнала  В/мкс он имеет низкую надежность из-за больших мощностей, выделяемых в транзисторах микросхемы и токопроводящих дорожках входного каскада во время длительных перегрузок по входу (см. Приложение 1). Поэтому для повышения надежности производители микросхем искусственно снижают

В/мкс он имеет низкую надежность из-за больших мощностей, выделяемых в транзисторах микросхемы и токопроводящих дорожках входного каскада во время длительных перегрузок по входу (см. Приложение 1). Поэтому для повышения надежности производители микросхем искусственно снижают  ОУ от предельно возможных значений

ОУ от предельно возможных значений  до

до  при котором входной каскад имеет допустимые уровни выходных импульсных токов. Это обеспечивается различными резистивно-диодными ограничителями на входе ОУ, ухудшающими ряд параметров ОУ, например входную емкость, шумы и т.д.

при котором входной каскад имеет допустимые уровни выходных импульсных токов. Это обеспечивается различными резистивно-диодными ограничителями на входе ОУ, ухудшающими ряд параметров ОУ, например входную емкость, шумы и т.д.

Основная цель предлагаемого изобретения состоит в повышении надежности работы ОУ при сохранении предельно возможного быстродействия, характерного для линейных режимов работы всех его каскадов.

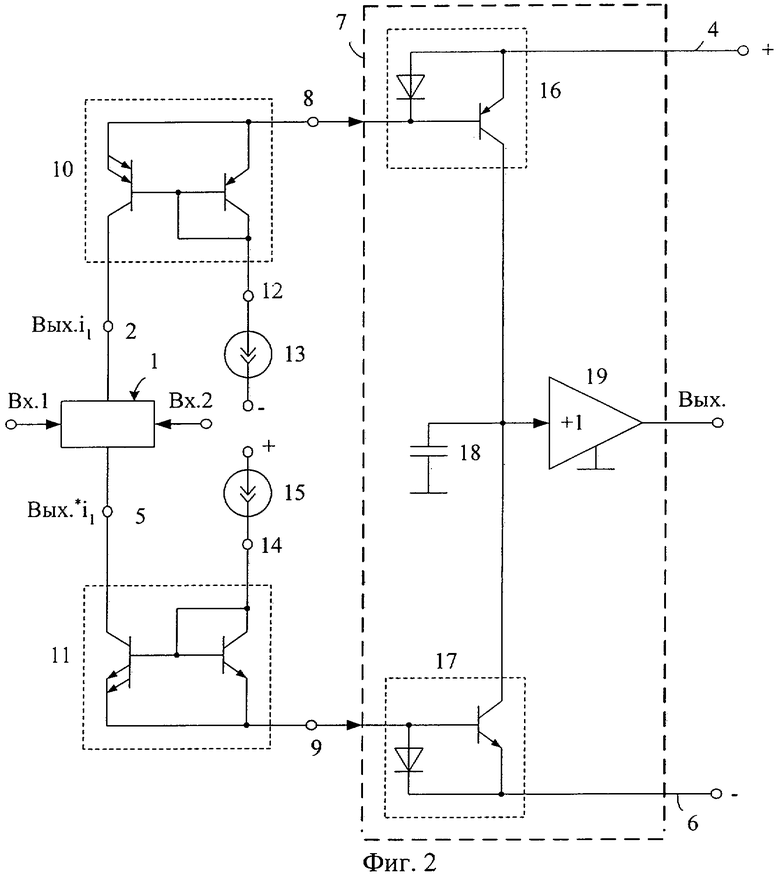

Поставленная цель достигается тем, что в быстродействующий операционный усилитель, содержащий входной каскад 1 с расширенным диапазоном активной работы, имеющий первый выход 2, согласованный с шиной положительного источника питания 4, второй выход 5, согласованный с шиной отрицательного источника питания 6, двухтактный выходной каскад 7, имеющий первый вход 8, согласованный с шиной положительного источника питания 4, второй вход 9, согласованный с шиной отрицательного источника питания 6, вводятся новые элементы и связи - первый выход 2 входного каскада 1 соединен с коллекторным выходом первого дополнительного токового зеркала 10, эмиттерный выход которого связан с первым входом 8 двухтактного выходного каскада 7, второй выход 5 входного каскада 1 соединен с коллекторным выходом второго дополнительного токового зеркала 11, эмиттерный выход которого связан со вторым входом 9 двухтактного выходного каскада 7, причем вход 12 первого токового зеркала 10 соединен с первым источником опорного тока 13, а вход 14 второго токового зеркала 11 соединен со вторым источником опорного тока 15.

Схема заявляемого устройства в соответствии с п.1-п.2 формулы изобретения показана на чертеже фиг.2.

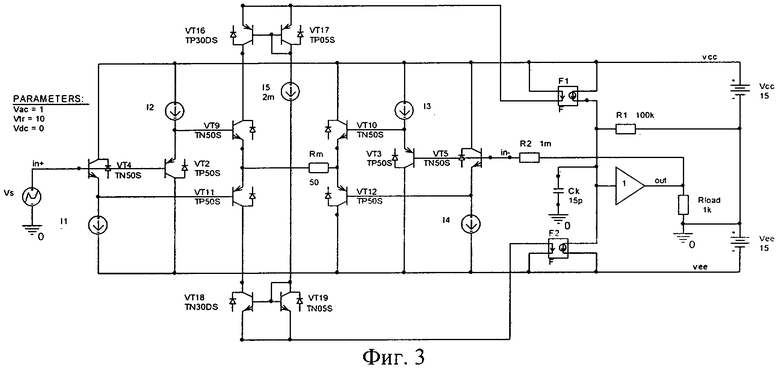

На чертеже фиг.3 показана схема исследованного ОУ фиг.2 в среде PSpice. На чертежах фиг.4, фиг.5, фиг.6, фиг.7 - результаты ее компьютерного моделирования в среде PSpice на моделях интегральных транзисторов ФГУ НПП «Пульсар».

На чертеже фиг.8 показан заявляемый ОУ для случая, когда в качестве входного каскада применяется так называемый «бриллиантовый» транзистор, а структура ОУ соответствует архитектуре ОУ с токовой отрицательной обратной связью.

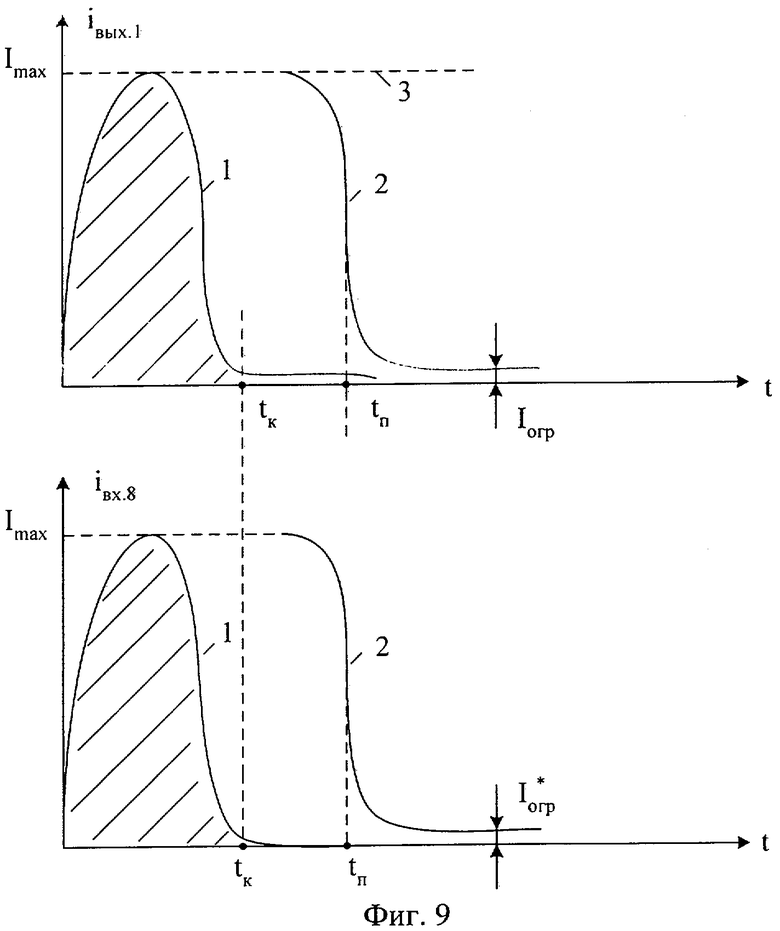

На чертеже фиг.9 представлены графики изменения токов в схеме заявляемого устройства.

Быстродействующий дифференциальный операционный усилитель фиг.2 содержит входной каскад 1 с расширенным диапазоном активной работы, имеющий первый выход 2, согласованный с шиной положительного источника питания 4, второй выход 5, согласованный с шиной отрицательного источника питания 6, двухтактный выходной каскад 7, имеющий первый вход 8, согласованный с шиной положительного источника питания 4, второй вход 9, согласованный с шиной отрицательного источника питания 6. Первый выход 2 входного каскада 1 соединен с коллекторным выходом первого дополнительного токового зеркала 10, эмиттерный выход которого связан с первым входом 8 двухтактного выходного каскада 7, второй выход 5 входного каскада 1 соединен с коллекторным выходом второго дополнительного токового зеркала 11, эмиттерный выход которого связан со вторым входом 9 двухтактного выходного каскада 7, причем вход 12 первого токового зеркала 10 соединен с первым источником опорного тока 13, а вход 14 второго токового зеркала 11 соединен со вторым источником опорного тока 15.

Рассмотрим работу заявляемого устройства (фиг.2) при импульсном изменении положительного входного напряжения uвх.

В статическом режиме при замкнутой 100% отрицательной обратной связи выходные транзисторы повторителей тока 10 и 11 находятся в режиме насыщения (имеют близкое к нулю дифференциальное сопротивление). Такой режим обеспечивается соответствующим выбором токов источников 13 и 15, а также площадей эмиттерных переходов выходных (Sвых) и входных (Sвх) транзисторов токовых зеркал 10 (11) (А=Sвых/Sвх≥1)

где I2=I5 - статические выходные токи в узлах 2 и 5 входного каскада 1.

Причем I2=Iвых.i1, I5=I*вых.i1, I0=I15=I3.

В зависимости от численных значений коэффициента  и токов I2=I5 необходимые (для обеспечения режима насыщения) значения тока I0 составляют 5÷50 % от токов I2=I5. Как следствие, входной ток токового зеркала 16 в заявляемом ОУ может незначительно отличаться от выходных токов входного каскада I2=I5.

и токов I2=I5 необходимые (для обеспечения режима насыщения) значения тока I0 составляют 5÷50 % от токов I2=I5. Как следствие, входной ток токового зеркала 16 в заявляемом ОУ может незначительно отличаться от выходных токов входного каскада I2=I5.

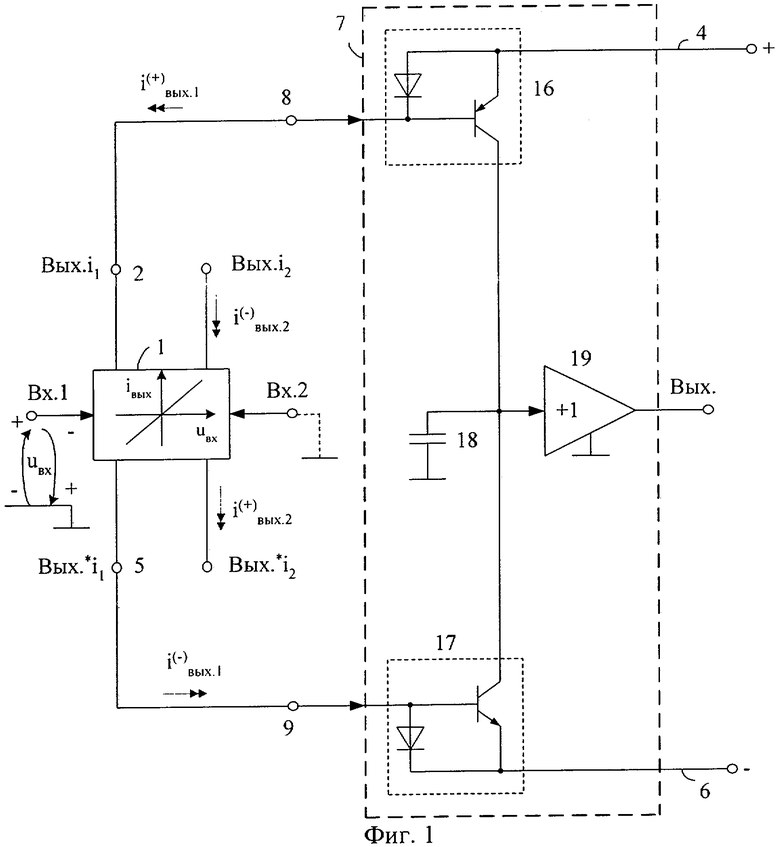

Одна из особенностей биполярных транзисторов - достаточно большое время переключения (tп) из насыщенного состояния в режиме отсечки. Как следствие, при возникновении в ОУ фиг.2 импульсных выходных токов входного каскада (токов в цепи узлов 2 и 5) (Imax.2≫AI0), длительность которых tк≪tп, они беспрепятственно передаются через токовые зеркала 10 и 11 на входы 8 и 9 и форсируют процессы перезаряда корректирующего конденсатора 18, повышая тем самым максимальную скорость нарастания выходного напряжения ОУ. Так как tк≪tп, то за время действия импульса выходного тока входного каскада 1 выходной транзистор токового зеркала 10 (11) не успевает выйти из насыщения, и поэтому токовые зеркала 10 и 11 не влияют на работу схемы. Поэтому форма импульса iвх.8(t) повторяет форму импульса iвых.1(t). Если выходной ток входного каскада (вследствие его длительной перегрузки) не уменьшается в течение времени t>tп (фиг.9, зависимость 2), то выходной транзистор токового зеркала 10(11) переходит в активный режим. При этом в насыщение входит выходной транзистор входного каскада, что ограничивает iвых.1 и входной ток iвх.8 подсхемы 7. В результате ОУ будет защищен от разрушения элементов схемы, связанного с тепловыми эффектами. По существу в заявляемом устройстве предлагается «интеллектуальная» динамическая защита по току, которая

- не влияет на прохождение "полезных" больших импульсов тока ВК малой длительности (tк≪tп);

- ограничивает выходной ток входного каскада на заданном уровне Iогр, если длительность выходного тока ВК tк превышает заданную tп.

Компьютерное моделирование ОУ фиг.3, приведенное на чертежах фиг.4, фиг.5, фиг.6, фиг.7, подтверждает эффективность заявляемого технического решения.

На чертеже фиг.4 показаны экспериментальные графики зависимости тока коллектора транзистора Iк9 (фиг.3), т.е. выходного тока входного каскада  (фиг.2), во время фронта переходного процесса (tф) выходного напряжения uвых(t) в замкнутом ОУ фиг.3. Из этих графиков следует, что в течение tф=4 нс выходной ток входного каскада достигает величины Imax>100 мА, что значительно превышает статический выходной ток этого каскада, но в то же время способствует существенному увеличению ϑвых.

(фиг.2), во время фронта переходного процесса (tф) выходного напряжения uвых(t) в замкнутом ОУ фиг.3. Из этих графиков следует, что в течение tф=4 нс выходной ток входного каскада достигает величины Imax>100 мА, что значительно превышает статический выходной ток этого каскада, но в то же время способствует существенному увеличению ϑвых.

На чертеже фиг.5 приведены графики зависимости медленно изменяющихся (статических) выходных токов входного каскада 1 от uвх заявляемого ОУ  при различных значениях токов I0=I13=I15. Из этих графиков следует, что в заявляемом ОУ "медленные" изменения входного напряжения uвх не приводят к чрезмерным выходным токам, которые могут, как это имеет место в прототипе, привести к тепловым разрушениям элементов микросхем. За счет выбора величины тока I0 можно уравнять порогом ограничения медленно изменяющегося выходного тока входного каскада (ВК). (Если I0=3 мА, то Iогр≈22 мА. При I0=2 мА, то Iогр≈l5 мА. Если I0=1 мА, то Iогр≈7 мА.) Однако это не приводит к ограничению быстроизменяющихся выходных токов ВК, которые способствуют существенному ускорению процесса перезаряда корректирующего конденсатора 18.

при различных значениях токов I0=I13=I15. Из этих графиков следует, что в заявляемом ОУ "медленные" изменения входного напряжения uвх не приводят к чрезмерным выходным токам, которые могут, как это имеет место в прототипе, привести к тепловым разрушениям элементов микросхем. За счет выбора величины тока I0 можно уравнять порогом ограничения медленно изменяющегося выходного тока входного каскада (ВК). (Если I0=3 мА, то Iогр≈22 мА. При I0=2 мА, то Iогр≈l5 мА. Если I0=1 мА, то Iогр≈7 мА.) Однако это не приводит к ограничению быстроизменяющихся выходных токов ВК, которые способствуют существенному ускорению процесса перезаряда корректирующего конденсатора 18.

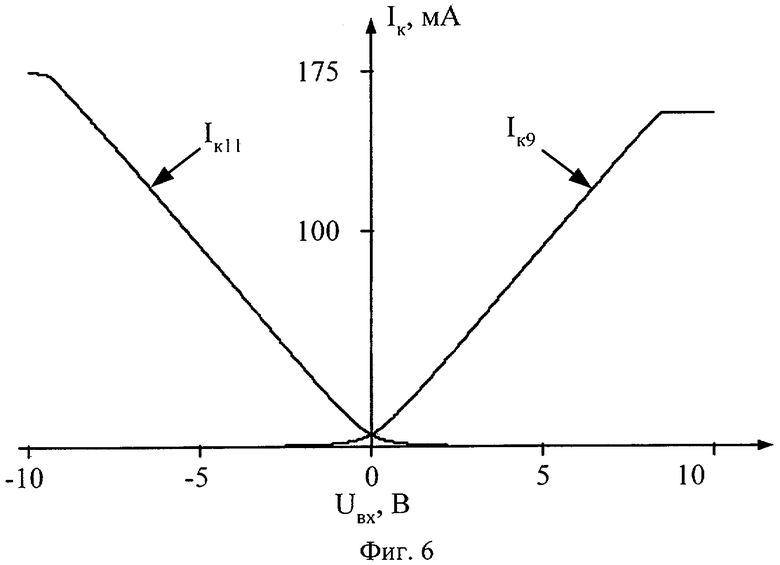

График фиг.6 показывает, что в ОУ-прототипе максимальные медленно изменяющиеся выходные токи входного каскада достигают 175 мА, что может привести к перегреву кристалла и разрушению токоведущих дорожек при обрыве элементов обратной связи ОУ, больших емкостях в цепи его обратной связи и т.п., т.е. при длительной перегрузке по входу.

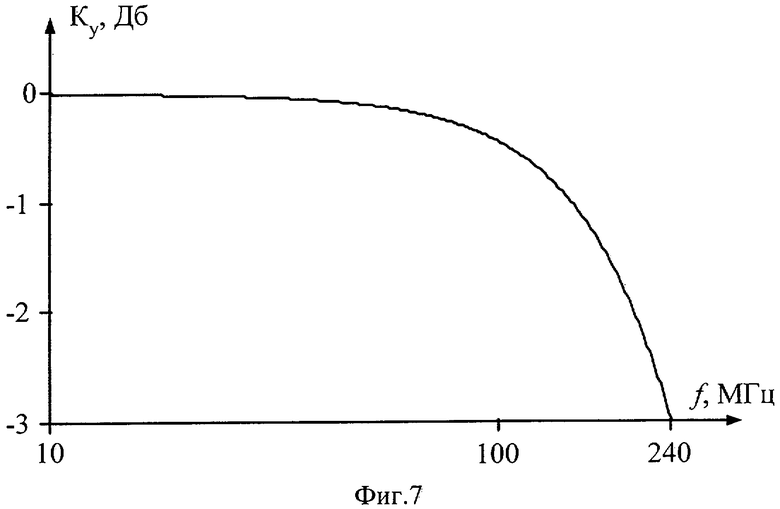

На чертеже фиг.7 показана амплитудно-частотная характеристика ОУ фиг.3, которая показывает, что верхняя граничная частота схемы фиг.3 f1=240 мГц.

Таким образом, заявляемое устройство имеет ряд существенных преимуществ по сравнению с прототипом.

Источники информации

1. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989.

2. Патент США №6538514.

3. Патент США №5351012.

4. Патент США №5512859.

5. Патент США №5352989.

6. Патент США №5557220.

7. Патент США №5623232.

8. Патент США №5103188.

9. Патент США №5907262.

10. Патент США №4833423.

11. Патент США №6262633.

12. Патент США №5150074.

13. Патент США №5736902.

14. Патент США №6492870.

15. Патент США №6281752.

16. Патент США №6429744.

17. Патент США №6188281.

18. Патент США №6459338.

19. Патент США №6278326.

20. Патент США №6163216.

21. Патент США №6181204.

22. Патент США №6489848.

23. Патент США №6542032.

24. Патент США №5399991.

25. Патент США №5510754.

26. Патент США №6542032.

27. Патент США №6492870.

28. Патент США №6262633.

29. Патент США №5512859.

30. Заявка US 2005/0024149.

31. Заявка US 2005/0128000.

32. Заявка US 2004/0212430.

| название | год | авторы | номер документа |

|---|---|---|---|

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2307455C1 |

| ВЫХОДНОЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2006 |

|

RU2311729C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450424C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ЦЕПЬЮ КОРРЕКЦИИ КОЭФФИЦИЕНТА УСИЛЕНИЯ | 2011 |

|

RU2459348C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2011 |

|

RU2462812C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2450425C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

Изобретение относится к радиотехнике и связи для использования в качестве устройства усиления импульсных сигналов в структуре аналоговых интерфейсов различного функционального назначения. Технический результат заключается в повышении надежности работы при сохранении предельно возможного быстродействия для линейных режимов работы. Операционный усилитель (фиг.2) содержит входной каскад (ВК) (1) с расширенным диапазоном активной работы, имеющий первый выход (2), согласованный с шиной положительного источника питания (ИП) (4), второй выход (5), согласованный с шиной отрицательного ИП (6), двухтактный выходной каскад (ДВК) (7), имеющий первый вход (8), согласованный с шиной положительного ИП (4), второй вход (9), согласованный с шиной отрицательного ИП (6). Первый выход (2) ВК (1) соединен с коллекторным выходом первого дополнительного токового зеркала (ТЗ) (10), эмиттерный выход которого связан с первым входом (8) ДВК (7), второй выход (5) ВК (1) соединен с коллекторным выходом второго дополнительного ТЗ (11), эмиттерный выход которого связан со вторым входом (9) ДВК (7), причем вход (12) первого ТЗ (10) соединен с первым источником опорного тока (13), а вход (14) второго ТЗ (11) соединен со вторым источником опорного тока (15). 1 з.п. ф-лы, 9 ил.

| US 5512859 A, 30.04.1996 | |||

| Усилитель тока | 1988 |

|

SU1631703A2 |

| Усилитель мощности низкой частоты | 1980 |

|

SU1073879A1 |

| US 6166603 A, 26.12.2000 | |||

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

Авторы

Даты

2007-09-27—Публикация

2006-02-20—Подача