Область техники

Изобретение относится к технологии цифровой обработки сигнала, конкретно к частотному фильтру и способу выполнения фильтрации в частотной области.

Уровень техники

В системах цифровой обработки сигнала часто используются фильтры для фильтрации помех, выделения полезных сигналов, формирования сигналов и т.д. В настоящее время дискретные цифровые сигналы линейной стационарной системы обрабатываются преимущественно двумя типами фильтров: временной свертки и частотного перемножения. Поскольку фильтр свертки сигнала во временной области использует вычислительные возможности более рационально благодаря высокоэффективному схемному варианту табличного поиска, то для фильтра с не изменяющейся характеристикой этот тип фильтрации часто используется при разработке микросхем. Вместе с тем, в ряде случаев требуется динамическое изменение формы отклика фильтра на единичный импульс, так что фильтр типа временной свертки вызывает затруднения при проектировании и требует дополнительных ресурсов. В этих случаях фильтрация может быть осуществлена следующим образом: сигнал из временной области преобразуется в частотную область посредством быстрого преобразования Фурье (БПФ), затем сигнал в частотной области умножается на частотный коэффициент фильтра для выполнения фильтрации; и затем отфильтрованный частотный сигнал преобразуется в сигнал во временной области посредством обратного БПФ (ОБПФ) и подается на выход.

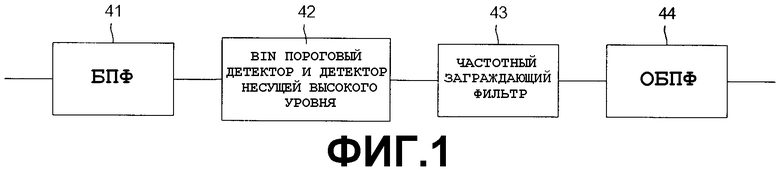

В патенте Китая CN 114 104 A на "Способ и аппаратуру широкополосной и узкополосной беспроводных телекоммуникаций" представлена схема частотной фильтрации на основе БПФ и ОБПФ. Как показано на Фиг.1, входной сигнал представляет собой сигнал несущей широкополосного CDMA (множественный доступ с кодовым разделением) и ряд узкополосных сигналов частотной модуляции (ЧМ). В этой схеме сигналы двух типов смешиваются и вводятся на блок БПФ 41 для непосредственного выполнения быстрого преобразования Фурье. Пороговый BIN детектор и детектор 42 несущей высокого уровня осуществляют эффективное детектирование ЧМ-сигналов в частотной области, а частотный заграждающий фильтр 43 фильтрует продетектированные ЧМ-сигналы и выводит оставшийся сигнал, не удаленный фильтрацией, на блок ОБПФ 44 для осуществления быстрого обратного преобразования Фурье с целью выделения несущей CDMA сигнала во временной области без ЧМ-сигналов.

Поскольку в вышеупомянутой схеме сигнал непосредственно обрабатывается с помощью БПФ и ОБПФ, то возможны скачки фазы в сигнале данных вблизи части заголовка и концевой части сегмента данных, прошедших преобразование Фурье после фильтрации сигнала, что весьма негативно влияет на фильтрацию и может привести к нелинейности фазы отфильтрованного сигнала, сильно сказывающейся на параметрах демодуляции в CDMA системе. Кроме того, поскольку преобразование Фурье и обратное преобразование Фурье приводят к длительной временной задержке, то групповая временная задержка фильтра в целом становится намного более длительной. В системе сотовой радиосвязи стандарта CDMA избыточная временная задержка при обработке сигнала будет иметь сильное влияние на некоторые параметры системы, такие как радиус сотовой ячейки, управление излучением и т.д. Поэтому необходимо эффективно управлять задержкой при обработке сигнала. Кроме того, частотный коэффициент фильтра в этой схеме не может быть динамически изменен извне.

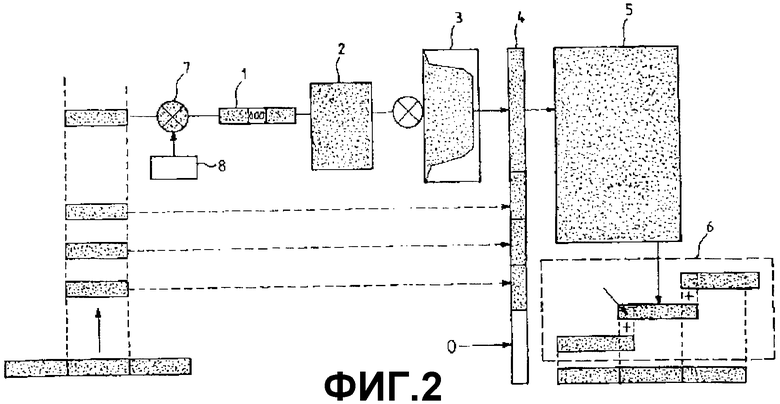

В патенте Китая CN 1354609 A на "Способ оптимизации передатчика мобильной радиосистемы" также рассматривается схема фильтрации в частотной области на основе БПФ и ОБПФ. Как показано на фиг.2, эта схема оптимизирует параметры передатчика со множеством несущих в мобильной радиосистеме с помощью некоторого способа обработки сигнала, такого как дискретное преобразование Фурье (ДПФ), фильтрация в частотной области, обратное дискретное преобразование Фурье (ОДПФ), обработка сигнала с перекрытием блока дискретизированных данных и дискретизация с повышенной частотой, причем длительность ДПФ и длительность ОДПФ выбираются так, что степень перекрытия и коэффициент дискретизации с повышенной частотой оказываются при этом оптимальными при данной входной частоте дискретизации, данном порядке величины выходной частоты дискретизации и данном порядке величины требуемого частотного разрешения.

В этой схеме длительности ДПФ и ОДПФ степень перекрытия и коэффициент дискретизации с повышенной частотой определяются в соответствии с требуемым частотным разрешением, полосой частот входного сигнала для ДПФ и полосой частот выходного сигнала для ОДПФ и т.д. Каждый несущий сигнал, выделенный по методу перекрытия и в соответствии со степенью перекрытия, обрабатывается частотными конвертерами 7 и 8 для коррекции частотного отклонения и для корректного установления центральной частоты каждого канала. Затем блок дискретизированных данных определенной степени перекрытия загружается в блок ДПФ 1 для компенсации нулевых битов и смещения для настройки длительности данных до нормального значения. Затем блок ДПФ 2 выполняет ДПФ; и частотный фильтр 3 осуществляет широкополосную формирующую фильтрацию сигнала несущей в частотной области. После этого устройство 4 объединения данных и компенсации нулевых битов объединяет данные в частотной области для каждой несущей и компенсирует нулевые биты для настройки длительности данных; затем блок ОДПФ 5 выполняет ОДПФ, и окончательно выходной блок 6 выполняет операцию суммирования перекрывающихся данных на восстановленных данных во временной области для получения окончательно отфильтрованных временных данных.

Поскольку схема нацелена на применение, объединение и формирование сигналов с множеством несущих, то этой схеме присущи некоторые недостатки при частотной фильтрации: во-первых, обработка перекрытия выполняется суммированием перекрытий и ограничена в отношении полосы частот сигнала, что ограничивает возможность улучшения показателя групповой задержки при фильтрации; и поскольку проблема скачка фазы решается не полностью, то требуется дополнительная схема подавления этого скачка; во-вторых, операции ДПФ и ОДПФ для различных сигналов совершенно различны по длительности и скорости, что приводит к невозможности реализации схемы мультиплексирования для арифметического устройства, так что требуются дополнительные ресурсы, трудности реализации многократно возрастают и существенно увеличивается стоимость; наконец, схема не обеспечивает также и способа динамического обновления извне частотного коэффициента фильтра.

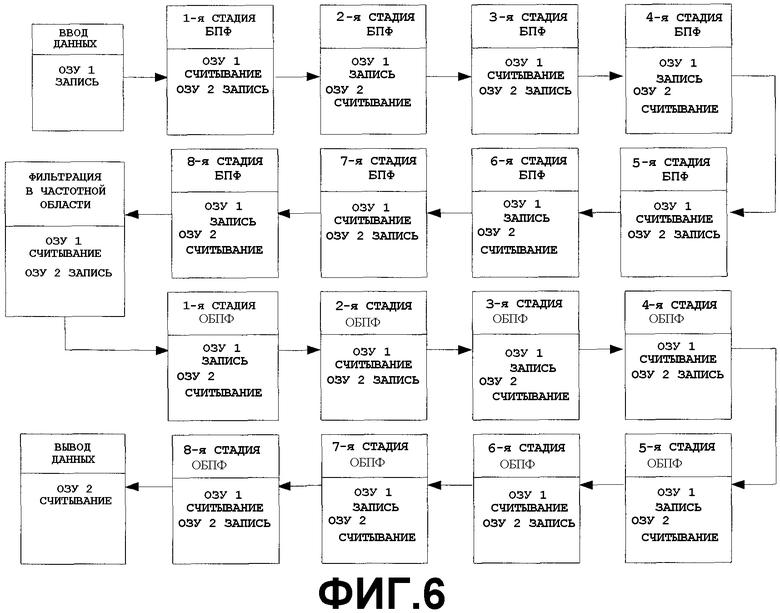

В общем случае временная задержка в частотном фильтре более длительна, и если сигнал сегментирован для преобразования Фурье, то часть заголовка и концевая часть сегмента данных плохо фильтруются, и имеют нелинейную фазу, что ограничивает применение и структуру фильтрации в частотной области. Однако обработка перекрытия и обращенного перекрытия во временной области, если ее добавить в операцию частотной фильтрации, будет способствовать решению указанных выше проблем. Принцип обработки перекрытия и обращенного перекрытия показан на Фиг.3. Предположим, что S1 есть входной сигнал во временной области, арифметическая длина S1 для БПФ есть N и длина перекрытия есть L, то, начиная от первой точки выборки S1, сегмент данных выборки длиной N берется на интервале данных (N-L), для которого данные длиной L, начиная от конца каждого сегмента данных, те же самые, что и первые данные длиной L следующего сегмента данных, т.е. длина перекрытия составляет L. Поэтому S1 последовательно делится на несколько сегментов, и каждый сегмент имеет длину N и длину перекрытия L. Таким образом выполняется обработка перекрытия временного сигнала S1. Поскольку длительность временного сигнала S1 теоретически не ограничена и при обработке перекрытия сигнала S1 учитываются первые F1 сегментов, то возможна обработка перекрытия и большего числа сегментов.

После обработки перекрытия сегменты данных F1 обрабатываются посредством БПФ фильтрации во временной области и ОБПФ соответственно. Затем обработанные таким образом временные сегменты данных F1 выводятся для обработки обращенного перекрытия, как описано ниже.

Имеются различные способы обработки обращенного перекрытия. Один из них заключается в следующем: каждый сегмент данных, для которого требуется такая обработка, добавляется и формируется непосредственно согласно той же последовательности, что и при обработке перекрытия, чтобы получить желаемые данные, которые были отфильтрованы в частотной области. Это называется перекрывающимся суммированием. Этот способ используется во втором из упомянутых патентов. Кроме того, имеется более эффективный способ обработки перекрытия, как показано на Фиг.3. В этом способе первые L/2 данные и последние L/2 данные каждого из F1 сегментов, которые требуют обработки обратного перекрытия, удаляются, а оставшиеся (N-L) данные каждого сегмента извлекаются и комбинируются исходя из порядка обработки перекрытия для получения желаемых данных после фильтрации в частотной области. Из Фиг.3 можно видеть, что выводимые после обработки перекрытия и обращенного перекрытия данные продвинуты на L/2 выборок данных по сравнению с входными данными до обработки; это означает, что групповая временная задержка частотной фильтрации соответственно понизилась. Вместе с тем, поскольку первые L/2 данные и последние L/2 данные каждого из сегментов удалены в обработке обратного перекрытия, то данные крайних частей сегмента не выводятся, и фильтрующий эффект значительно улучшен. При увеличенной длительности перекрытия L параметры фильтрации становятся лучше, но ресурсы для реализации и соответствующие затраты также значительно возрастает. Поэтому необходимо эффективное решение для управления ресурсами на реализацию при улучшении показателей фильтрации.

Сущность изобретения

Задачей изобретения является создание частотного фильтра и способа выполнения фильтрации в частотной области так, чтобы снизить затраты на реализацию при улучшении показателей фильтрации и снижении времени задержки в фильтре. Также задачей изобретения является создание решения для динамического обновления характеристик фильтрации частотного фильтра быстрым и удобным способом.

Указанные задачи решаются в изобретении следующим образом.

Частотный фильтр, содержащий управляющий блок, матрицу памяти, память коэффициентов фильтра, блок коммутации данных, блок табличного поиска для циклических множителей, блок формирования выходных данных и, по меньшей мере, одно общее высокоскоростное арифметическое устройство; причем

данные временной области, подлежащие фильтрации в частотной области, вводятся через шину данных в матрицу памяти; матрица памяти выводит отфильтрованные в частотной области данные временной области через шину данных на блок формирования выходных данных, и окончательно отфильтрованные данные временной области выводятся после регулировки уровня;

управляющий блок связан с матрицей памяти через линию сигнала считывания/записи и линии сигнала адресации;

управляющий блок связан с введенным извне синхросигналом данных временной области;

управляющий блок выводит сигнал управления объединением данных на блок формирования выходных данных для управления стробом и объединением отфильтрованных данных временной области;

управляющий блок выводит сигнал управления табличным поиском на блок табличного поиска для циклических множителей для управления табличным поиском, синхронизированным с преобразованием Фурье и обратным преобразованием Фурье, и подачей соответствующего циклического множителя на общее высокоскоростное арифметическое устройство;

управляющий блок выводит сигнал управления коммутацией данных на блок коммутации данных для управления стробом ввода/вывода данных матрицы памяти и коммутацией между данными для операции преобразования Фурье и данными для операции частотной фильтрации в общем высокоскоростном арифметическом устройстве; причем матрица памяти и блок коммутации данных соединены посредством двунаправленной шины, и блок коммутации данных и общее высокоскоростное арифметическое устройство также соединены посредством двунаправленной шины данных;

управляющий блок выводит сигнал управления состояниями на общее высокоскоростное арифметическое устройство для управления коммутацией между преобразованием Фурье и операцией фильтрации в частотной области;

память коэффициента фильтра получает управляющий синхросигнал извне и посылает на общее высокоскоростное арифметическое устройство значение коэффициента фильтра, или получает сигнал обновления коэффициента извне для обновления автономносохраненного коэффициента фильтра.

Матрица памяти состоит, по меньшей мере, из двух блоков памяти.

Матрица памяти представляет собой матрицу ОЗУ.

Блок памяти представляет собой группу ОЗУ, содержащую, по меньшей мере, две ячейки ОЗУ.

Память коэффициента фильтрации содержит, по меньшей мере, одну ячейку ОЗУ.

Общее высокоскоростное арифметическое устройство представляет собой устройство сходящихся ("butterfly") вычислений.

Блок коммутации данных содержит, по меньшей мере, селектор входных данных, селектор выходных данных, распределитель входных дынных, распределитель выходных данных и, по меньшей мере, два блока коммутации входных/выходных данных; число блоков коммутации входных/выходных данных равно числу блоков памяти в матрице памяти; блоки коммутации входных/выходных данных однозначно соответствуют блокам памяти; каждый блок коммутации входных/выходных данных соединен с соответствующим блоком памяти посредством двунаправленной шины данных; выход каждого блока коммутации входных/выходных данных соединен с селектором входных данных, и вход каждого блока коммутации входных/выходных данных соединен с распределителем выходных данных; выход селектора выходных данных соединен с распределителем входных данных; два выхода распределителя входных данных соединены с общим высокоскоростным арифметическим устройством; два входа селектора выходных данных соединены с общим высокоскоростным арифметическим устройством, и выход селектора выходных данных соединен с распределителем выходных данных.

Предпочтительно, управляющий блок выводит затем управляющий синхросигнал в память коэффициентов фильтра для приведения этой памяти в состояние, защищенное от записи, когда память работает, и для вывода из этого состояния, когда память находится в ожидании для обновления коэффициента фильтра.

Способ фильтрации в частотной области, содержит:

перекрытие и сохранение каждого сегмента временных данных для фильтрации в частотной области, в блоке памяти матрицы памяти, соответственно;

выполнение преобразования Фурье, операции частотной фильтрации и обратного преобразования Фурье для каждого перекрывающегося сегмента временных данных, сохраняемых в упомянутой матрице памяти в различные моменты времени в одном общем высокоскоростном арифметическом устройстве соответственно, и затем сохранение отфильтрованного сегмента временных данных снова в блоке памяти матрицы памяти;

выбор и считывание последовательности сегментов временных данных, отфильтрованных и сохраняемых в каждом блоке памяти матрицы памяти; выполнение обработки обратного перекрытия считанных сегментов данных, комбинирование и вывод сегментов данных для получения окончательных временных данных;

при этом до окончания сохранения одного сегмента временных данных в одном блоке памяти матрицы памяти, общее высокоскоростное арифметическое устройство завершает обратное преобразование Фурье для последнего сегмента временных данных, перекрывающихся и сохраняемых в последнем блоке памяти матрицы памяти.

Кроме того, способ частотной фильтрации содержит выполнение регулировки усиления для временных данных после обработки обратного перекрытия.

Операция частотной фильтрации содержит использование коэффициента фильтра для выполнения этой операции; и, кроме того, способ содержит динамическое обновление коэффициента фильтра для операции частотной фильтрации.

Этап выполнения в общем высокоскоростном арифметическом устройстве преобразования Фурье, операции частотной фильтрации и обратного преобразования Фурье для одного сегмента перекрывающихся временных данных, сохраняемых в одном блоке памяти матрицы памяти, содержит считывание данных для операции и запись в результате операции попеременно в двух ячейках памяти блока памяти.

Нацеленное на устранение недостатков традиционной схемы частотной фильтрации, характеризующейся недостаточным фильтрующим эффектом в начальной и конечной частях сегмента данных, а также более длительной временной задержкой в самом фильтре настоящее изобретение улучшает фильтрующий эффект и снижает временную задержку фильтра путем введения обработки сигнала перекрытия и обращенного перекрытия и соответствующего увеличения области перекрытия сегмента данных. Согласно настоящему изобретению БПФ, частотная фильтрация и ОБПФ для многократно перекрывающихся сегментов данных реализуются посредством мультиплексирования с разделением по времени и с помощью общего высокоскоростного арифметического устройства, такого как устройство сходящихся вычислений, что уменьшает количество арифметических устройств и снижает потребность в ресурсах, обеспечивая удобство реализации и снижение затрат. Кроме того, изобретение предусматривает память коэффициентов фильтрации, обеспечивающую удобное, быстрое и динамичное обновление коэффициентов фильтрации, что будет иметь многие приложения в системах, требующих адаптивной фильтрации.

Краткое описание чертежей

Фиг.1 - схема предшествующего уровня.

Фиг.2 - еще одна схема предшествующего уровня.

Фиг.3 - схема, иллюстрирующая принцип обработки сигнала с перекрытием и обращенным перекрытием согласно изобретению.

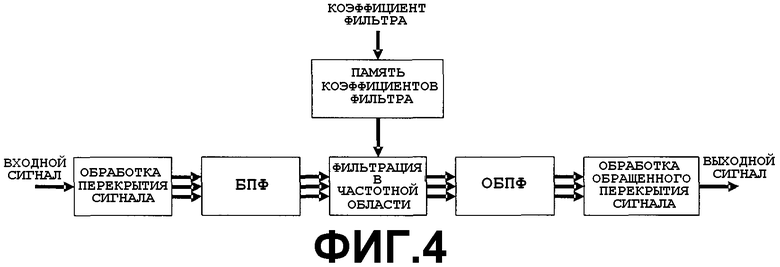

Фиг.4 - схема, иллюстрирующая принцип динамической частотной фильтрации согласно изобретению.

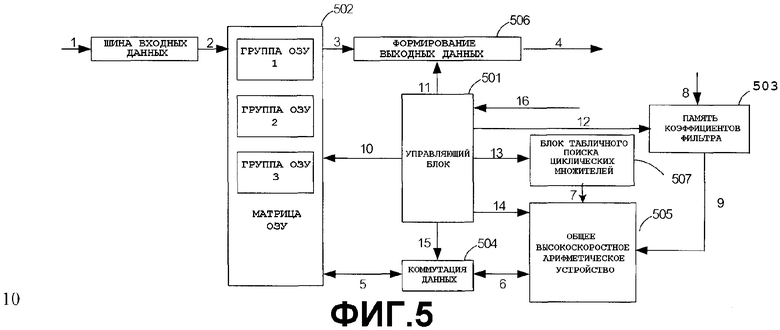

Фиг.5 - схема, иллюстрирующая реализацию динамического частотного фильтра согласно изобретению.

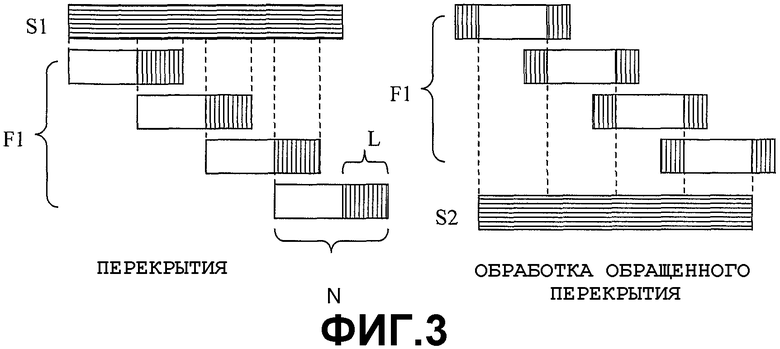

Фиг.6 - блок-схема последовательности операций при обработке данных группой ОЗУ согласно одной реализации изобретения.

Фиг.7 - схема, иллюстрирующая структуру блока коммутации данных в динамическом частотном фильтре согласно изобретению.

Фиг.8 - полная временная диаграмма обработки данных согласно одной реализации изобретения.

Варианты реализации изобретения

Изобретение рассматривается подробнее в связи с приведенными чертежами.

Принцип динамической фильтрации в частотной области согласно изобретению показан на Фиг.4, причем процесс фильтрации включает в себя следующие этапы:

Этап 401: входной сигнал временной области, т.е. входной поток данных перекрывается. Более конкретно входной поток данных делится на множество сегментов данных с определенной степенью перекрытия.

Этап 402: выполнение БПФ для каждого перекрывающегося сегмента соответственно.

Этап 403: каждый сегмент данных в частотной области после БПФ умножается на коэффициент фильтра для выполнения фильтрации в частотной области, причем коэффициент фильтра сохраняется в памяти коэффициентов фильтра, которая может быть обновлена в реальном времени программным образом или с помощью арифметической схемы для динамического обновления характеристик фильтра в частотной области.

Этап 404: выполняется ОБПФ для каждого сегмента данных, который был отфильтрован в частотной области, соответственно для восстановления сегмента данных во временной области.

Этап 405: выполнение обработки обращенного перекрытия сегментов данных во временной области, полученных на этапе 404, для получения на выходе потока данных во временной области.

Во время вышеупомянутой обработки перекрытия и обращенного перекрытия вместе с увеличением длины L перекрытия увеличиваются также и требуемые операционные ресурсы, т.е. соответственно растет и стоимость обработки. Для разрешения этой проблемы следует улучшить операционную эффективность и эффективно реализовать высокоуровневое мультиплексирование операционных и управляющих блоков. Поскольку данные во временной области требуется сохранять до преобразования Фурье, то БПФ может выполняться при сохраняемых данных во временной области так, что преобразование Фурье выполняется насколько это возможно, в то время как данные во временной области ожидают сохранения. Поскольку в обычных широкополосных системах связи скорость передачи временных данных базовой полосы часто больше, чем несколько МГц, то поэтому возможно увеличить скорость передачи в десятки раз для получения операционной скорости преобразования Фурье, таким образом обеспечивая полное использование операционного блока и различных ресурсов системы.

На основе низкоскоростных входных данных во временной области и высокоскоростного операционного блока преобразования Фурье возможно создание динамического фильтра в частотной области с превосходными параметрами при низких затратах, как показано на Фиг.5.

Главной отличительной чертой этой конструкции является использование матрицы памяти. Матрица содержит, по меньшей мере, два независимых блока памяти и используется для сохранения перекрывающихся сегментов данных, а также промежуточного результата БПФ и операции фильтрации. Матрица может состоять из матрицы ОЗУ. Рассмотрим матрицу ОЗУ, для примера. Каждый блок памяти в матрице ОЗУ обозначается как группа ОЗУ. Каждая группа ОЗУ содержит, по меньшей мере, два ОЗУ с функцией локального сохранения для операции с данными. В любой момент времени одно из двух ОЗУ находится в состоянии считывания, а другое ОЗУ - в состоянии записи. То ОЗУ, которое находится в состоянии считывания, считывает данные, вычисляемые как поток данных, и посылает данные на арифметическое устройство, а результат вычисления может быть сохранен в ОЗУ той же группы ОЗУ в состоянии записи.

Используя характеристику высокоскоростных интегральных схем, изобретение реализует общее высокоскоростное арифметическое устройство, такое как устройство сходящихся вычислений, которое способно реализовать мультиплексирование с разделением по времени, применяя вышеупомянутую матрицу памяти и блок коммутации данных, также предлагаемый настоящим изобретением, и, таким образом, обеспечить ресурсы для других операций.

Кроме того, изобретение предлагает память коэффициентов фильтра, управляемую внешним образом так, что параметры фильтрации фильтра во временной области могут быть динамически модифицированы, а внешнее обновление коэффициента фильтра синхронизировано с операцией фильтрации.

Используя матрицу ОЗУ в качестве примера, как показано на Фиг.5, предлагаемый настоящим изобретением динамический фильтр во временной области содержит управляющий блок 501, матрицу 502 памяти, память 503 коэффициентов фильтра, блок 504 коммутации данных, блок 506 формирования выходных данных, блок 507 табличного поиска для циклических множителей и, по меньшей мере, одно общее высокоскоростное арифметическое устройство 505. Управляющий блок 501 выводит шесть управляющих сигналов, подаваемых на матрицу 502 памяти, память 503 коэффициентов фильтра, блок 504 коммутации данных, общее высокоскоростное арифметическое устройство 505, блок 506 формирования выходных данных, блок 507 табличного поиска для циклических множителей соответственно. Кроме того, входной управляющий сигнал извне посылается на управляющий блок 501.

Управляющий сигнал 10 управляющего блока 501 обеспечивает сигналы управления считыванием/записью и управления стробом для матрицы памяти, чтобы управлять операциями считывания и записи в процессе ввода, вывода, перекрытия, обращенного перекрытия, сходящегося вычисления и фильтрации данных в частотной области. Управляющий сигнал 11 является сигналом управления формированием выходных данных, который управляет стробом и формированием окончательных выходных данных во временной области из различных блоков памяти. Управляющий сигнал 12 является синхронизирующим управляющим сигналом памяти коэффициентов фильтра, который управляет памятью коэффициентов фильтра, посылая коэффициент фильтра на общее высокоскоростное арифметическое устройство, тем самым осуществляя защиту от записи для памяти коэффициентов фильтра, когда коэффициент фильтра используется, но аннулирует защиту от записи в ждущем состоянии так, что коэффициент фильтра может быть обновлен. Управляющий сигнал 13 является управляющим сигналом табличного поиска, который обеспечивает синхронизацию табличного поиска с операциями БПФ/ОБПФ и управляет блоком табличного поиска для циклических множителей для выведения соответствующего циклического множителя при выполнении БПФ и ОБПФ. Управляющий сигнал 14 является сигналом управления состояниями общего высокоскоростного арифметического устройства, который управляет переключением между состоянием сходящегося вычисления и состоянием фильтрации в частотной области. Управляющий сигнал 15 является сигналом управления коммутацией данных, который управляет стробом ввода/вывода данных блоков памяти и общего высокоскоростного арифметического устройства для реализации мультиплексирования с разделением по времени общего высокоскоростного арифметического устройства в операции с данными множества блоков памяти, а также управляет коммутацией входных данных между сходящимся вычислением и операцией фильтрации в частотной области. Внешний управляющий сигнал 16 является синхронизирующим сигналом внешних данных во временной области, вводимым для синхронизации во времени управляющего блока и вводимых внешних данных.

Ниже описана работа показанного на Фиг.5 фильтра. Во-первых, управляющий модуль 501 посылает на матрицу 502 ОЗУ управляющий сигнал 10. Посредством управления этим сигналом адресом записи каждого ОЗУ, обработка перекрытия, показанная на Фиг.3, выполняется в течение процедуры 2 ввода, когда входные данные 1 во временной области вводятся в матрицу 502 ОЗУ через входную шину данных, и каждый из сегментов данных во временной области, созданных в течение обработки перекрытия, сохраняется последовательно в каждом блоке памяти, т.е. группе ОЗУ из матрицы 502 ОЗУ. Пространство памяти, требуемое в течение всей процедуры обработки каждого сегмента данных, обеспечивается группой ОЗУ, в которой находится сегмент данных.

Затем на основе управляющих сигналов 10, 13, 14 и 15, которые посылаются на матрицу 502 ОЗУ, блок 507 табличного поиска для циклических множителей, общее высокоскоростное арифметическое устройство 505, блок 504 коммутации данных, с помощью управляющего блока 501, соответственно каждая группа ОЗУ может обмениваться сохраняемыми в ней данными с высокоскоростным арифметическим устройством на высокой скорости через блок 504 коммутации данных (предположим, что общее высокоскоростное арифметическое устройство является устройством сходящегося вычисления, которое имеет четыре параллельных умножителя и шесть сумматоров), т.е. данные в группе ОЗУ считываются и вводятся в блок 504 коммутации данных через двунаправленную шину 5; переключенные в блоке 504 коммутации данных, данные для сходящегося вычисления вводятся в блок 505 сходящихся вычислений через двунаправленную шину данных 6; и затем выполняется сходящееся вычисление данных с соответствующим циклическим множителем, выведенным синхронно из блока 507 табличного поиска. После сходящегося вычисления данные выводятся на блок 504 коммутации данных через двунаправленную шину 6 для распределения, и затем записываются в соответствующую группу ОЗУ в матрице 502 ОЗУ через двунаправленную шину 5. На основе принципа БПФ вышеупомянутая процедура повторяется до тех пор, пока все входные данные во временной области не будут трансформированы в соответствующие данные в частотной области, завершив, таким образом, БПФ.

На основе управляющих сигналов 10, 12, 14 и 15, которые посылаются на матрицу 502 ОЗУ, память 503 коэффициентов фильтра, общее высокоскоростное арифметическое устройство 505, блок 504 коммутации данных с помощью управляющего блока 501 соответственно, данные в частотной области в соответствующих группах ОЗУ и соответствующий коэффициент фильтра в памяти 503 коэффициентов фильтра синхронно посылаются в устройство 505 сходящихся вычислений; они перемножаются в устройстве 505 сходящихся вычислений для выполнения операции фильтрации. Результат посылается в соответствующую группу ОЗУ в матрице ОЗУ через блок 504 коммутации данных и готов для выполнения ОБПФ.

Затем на основе управляющих сигналов 10, 13, 14 и 15, которые посылаются на матрицу 502 ОЗУ, блок 507 табличного поиска для циклических множителей, общее высокоскоростное арифметическое устройство 505, блок 504 коммутации данных с помощью управляющего блока 501 соответственно, каждая группа ОЗУ может обмениваться сохраняемыми в ней данными с устройством 505 сходящихся вычислений на высокой скорости через блок 504 коммутации данных, т.е. данные в группе ОЗУ считываются и вводятся в блок 504 коммутации данных через двунаправленную шину 5; данные для сходящегося вычисления, переключенные в блоке 504 коммутации данных, вводятся в блок 505 сходящихся вычислений через двунаправленную шину данных 6; и затем выполняется сходящееся вычисление на упомянутых данных с соответствующим циклическим множителем, для которого была выполнена операция сопряжения и который был выведен синхронно из блока 507 табличного поиска. После сходящегося вычисления данные выводятся на блок 504 коммутации данных через двунаправленную шину 6 для распределения, и затем записываются в соответствующую группу ОЗУ в матрице 502 ОЗУ через двунаправленную шину 5; вышеупомянутая процедура повторяется до тех пор, пока все входные данные в частотной области не будут трансформированы в соответствующие данные во временной области, завершив, таким образом, операцию ОБПФ.

На основе управляющих сигналов 10 и 11, которые посылаются на матрицу 502 ОЗУ и блок 506 формирования выходных данных с помощью управляющего блока 501 соответственно, выходные данные 3 для обработки обращенного перекрытия считываются из соответствующих групп ОЗУ, и обработка обращенного перекрытия выполняется на каждом из считанных сегментов данных, как показано на Фиг.3 в блоке 506 формирования выходных данных, затем выполняется регулировка уровня и окончательные выходные данные 4 получаются во временной области после фильтрации в частотной области.

Память 503 коэффициентов фильтра на Фиг.5 содержит, по меньшей мере, одно ОЗУ, и коэффициент фильтра в памяти может быть обновлен извне так, что параметры фильтра могут динамически обновляться, причем обновление может быть обеспечено программным образом или аппаратными средствами. Обновленный коэффициент 8 фильтра записывается в память коэффициентов фильтра, когда нет операции фильтрации, и готов для использования в следующей операции фильтрации.

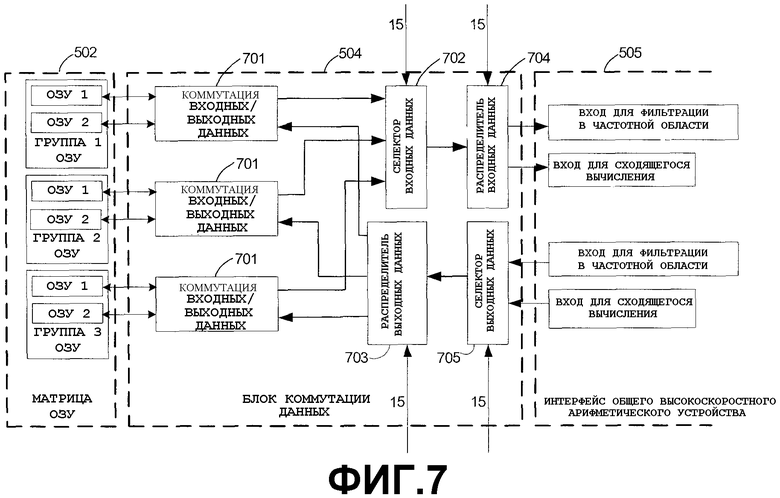

На Фиг.6 показана блок схема операций обработки данных в группе ОЗУ с двумя ОЗУ. Когда длина данных для преобразования Фурье составляет 2N точек данных, то преобразование Фурье и обратное преобразование Фурье требуют N раз сходящихся вычислений соответственно. На Фиг.6 показан пример с N=8 и длиной данных для преобразования Фурье, составляющих 256 точек данных, причем два ОЗУ в группе ОЗУ считываются и записываются поочередно, что обеспечивает высокую скорость выполняемой операции. В то время как выводятся окончательно отфильтрованные данные во временной области, выполняется только операция считывания ОЗУ2, так что ОЗУ1 может использоваться в это время для записи следующего сегмента входных данных. Повторением этой процедуры поток данных может обрабатываться с высокой скоростью, и степень перекрытия в обработке перекрытия может быть увеличена.

Блок 504 коммутации данных по Фиг.5 описан подробно на примере, в котором матрица 502 ОЗУ, соединенная с блоком 504, содержит три независимых блока памяти, т.е. три группы ОЗУ, как показано на Фиг.7.

На Фиг.7 каждая группа ОЗУ имеет два ОЗУ: ОЗУ1 и ОЗУ2; в каждый момент времени только одно ОЗУ находится в состоянии считывания, тогда как другое - в состоянии записи. ОЗУ в состоянии считывания считывает данные для вычисления как поток данных и посылает данные на арифметическое устройство, а результат вычисления сохраняется в другом ОЗУ, которое находится в состоянии записи в той же группе ОЗУ. Таким образом, два ОЗУ выполняют операции считывания и записи N раз, в соответствии с блок-схемой операций на Фиг.6, после чего преобразование Фурье для 2N данных завершается.

Как показано на Фиг.7, блок 504 коммутации данных включает в себя блок 701 коммутации входных/выходных данных, селектор 702 входных данных, распределитель 703 выходных данных, распределитель 704 входных данных и селектор 705 выходных данных. Число блоков 701 коммутации входных/выходных данных соответствует числу блоков памяти в матрице памяти, и блоки коммутации однозначно соответствуют группам памяти. В этом варианте реализации имеется три группы памяти в матрице 502 памяти, так что имеется три блока 701 коммутации входных/выходных данных, каждый из которых однозначно соответствует трем группам памяти в матрице 502 памяти; задача блока коммутации входных/выходных данных заключается в выполнении обмена данными между группой ОЗУ и селектором, а также в обеспечении того, что два ОЗУ из группы ОЗУ находятся в корректном состоянии считывания/записи. Селектор 702 входных данных является блоком с множеством входов и одним выходом. Если имеется три блока 701 коммутации входных/выходных данных, в блоке 504 коммутации данных, то селектор 702 входных данных может быть блоком с тремя входами и одним выходом. Остальное может быть выведено логически. Рассмотрим для примера селектор 702 входных данных с тремя входами и одним выходом («три-один»). Исходя из состояния мультиплексирования с разделением по времени общего арифметического устройства, управляющий сигнал 15 управляет селектором 702 входных данных для селектирования данных из одного из трех ОЗУ, передаваемых через 3 блока 701 коммутации входных/выходных данных, и пересылает данные на распределитель 704 входных данных. На основе управляющего сигнала 15, распределитель 704 входных данных определяет, предназначаются ли данные для сходящегося вычисления или для фильтрации в частотной области, и затем посылает данные на соответствующее устройство в общем арифметическом устройстве 505. Селектор 705 выходных данных является блоком селекции «два-один»; на основе управляющего сигнала 15 он определяет состояние общего арифметического устройства 505, а затем селектирует отфильтрованные выходные данные в частотной области или выходные данные сходящихся вычислений в качестве своих выходных данных для распределителя 703 выходных данных. На основе управляющего сигнала 15 распределитель 703 выходных данных определяет состояние мультиплексирования с разделением по времени общего арифметического устройства 505, а затем распределяет данные на соответствующий блок 701 коммутации входных/выходных данных, соединенный с группой ОЗУ в состоянии считывания и записи. Посредством коммутации входных/выходных данных с помощью соответствующего блока 701 коммутации входных/выходных данных, данные записываются в соответствующее ОЗУ, которое находится в состоянии записи в соответствующей группе ОЗУ. В рассмотренной выше процедуре управляющий сигнал 15 управляет блоком 504 коммутации данных для выполнения коммутации данных для мультиплексирования с разделением по времени и обеспечивает временную последовательность для переключения между операционными состояниями.

Приведенное выше описание блока коммутации данных относится к примеру, в котором матрица памяти представляет собой матрицу ОЗУ, содержащую три группы ОЗУ. Если матрица памяти состоит из групп памяти другого типа, или же матрица ОЗУ содержит две или более трех групп ОЗУ, то описанный выше способ все же применим, но соответствующие изменения должны быть внесены в структуру блока коммутации данных, учитывающие отличающиеся требования к коммутации данных. Поскольку структура каждого под-блока в блоке коммутации данных проста, то структурное изменение в пределах блока коммутации данных включает только адаптацию схемы в целом, учитывающую требования к сопряжению с матрицей ОЗУ и общим арифметическим устройством с мультиплексированием с разделением по времени.

Для динамического фильтра в частотной области, показанного на Фиг.5, на Фиг.8 приведена полная временная диаграмма обработки данных согласно одному варианту реализации настоящего изобретения, на которой точечное изображение представляет входные данные во временной области, изображение по вертикальной оси представляет БПФ, ОБПФ и операции фильтрации, и изображение по горизонтальной оси представляет отфильтрованные выходные данные во временной области. В этом варианте реализации скорость передачи входных данных во временной области составляет 2,4576 МГц; длина для быстрого преобразования Фурье составляет 256 точек данных, чтобы реализовать фильтрацию в частотной области; требуемая длина перекрытия данных составляет 140 точек данных; и скорость сходящегося вычисления в 25 раз больше скорости передачи данных во временной области, т.е. 61,44 МГц.

Как показано на Фиг.8, когда процесс фильтрации в частотной области начинается, то первый сегмент данных, т.е. первые 256 точек данных входного потока данных сохраняется в группе 1 ОЗУ, как показывает точечная область на 801. Когда первый сегмент данных сохранен в группе 1 ОЗУ, то данные пересылаются на высокоскоростное арифметическое устройство 505 для сходящегося вычисления преобразования Фурье, а в то же самое время блок 507 табличного поиска синхронно отыскивает необходимый циклический множитель для вычисления; после завершения сходящегося вычисления сегмент данных снова сохраняется в группе 1 ОЗУ, и высокоскоростное арифметическое устройство 505 переключается в состояние фильтрации в частотной области. В то же самое время память 503 коэффициентов фильтра синхронно выводит коэффициент фильтра для выполнения операции фильтрации данных в частотной области, для которых выполнены сходящиеся вычисления. Вышеназванный сегмент данных в частотной области посылается в высокоскоростное арифметическое устройство 505 через блок 504 коммутации данных из группы 1 ОЗУ, и отфильтрованный сегмент данных снова сохраняется в группе 1 ОЗУ. Когда операция фильтрации завершена, то общее высокоскоростное арифметическое устройство 505 переключается в состояние сходящегося вычисления для выполнения ОБПФ для отфильтрованных данных, сохраненных в группе 1 ОЗУ. После операции ОБПФ получаются результирующие данные во временной области, которые сохраняются в группе 1 ОЗУ. Изображение по вертикальной оси на 801 показывает данные после БПФ, ОБПФ и обработки фильтрацией в частотной области. Как только вышеназванная обработка завершена, результирующие данные в группе 1 ОЗУ посылаются в блок 506 формирования выходных данных, который выполняет селекцию данных и вывод данных после обработки обращенного перекрытия. Выводимые данные показаны изображением по горизонтальной оси на 801. Аналогичным образом обрабатывается каждый сегмент данных для 802, 803, 804 и 805. Выходные данные каждого сегмента данных, т.е. часть изображения на горизонтальной оси всех сегментов данных могут быть объединены для получения полного выходного потока отфильтрованных данных во временной области.

Для выполнения перекрытия данных и мультиплексирования с разделением по времени общего высокоскоростного арифметического устройства в момент времени, когда 117-я точка данных входного потока данных введена в группу 1 ОЗУ, второй сегмент данных, содержащий 256 точек данных от 117-ой точки данных включительно, одновременно сохраняется в группе 2 ОЗУ, как показано на точечном изображении 802; в момент времени, когда 233-я точка данных входного потока данных введена в группы 1 и 2 ОЗУ, третий сегмент данных, содержащий 256 точек данных, включая от 233-ей точки данных включительно, одновременно сохраняется в группе 3 ОЗУ, как показано на точечном изображении 803. Перед тем, как данные во временной областью полностью будут введены в группу 2 ОЗУ, общее высокоскоростное арифметическое устройство заканчивает обработку данных, сохраненных в группе 1 ОЗУ, так что оно сразу же начинает обрабатывать данные, сохраненные в группе 2 ОЗУ. В то же самое время группа 1 ОЗУ может принимать новые данные для сохранения, поскольку обработка данных, ранее сохраненных в группе 1 ОЗУ, завершена. Поэтому, в момент времени, когда 349-я точка данных входного потока данных введена в группы 2 и 3 ОЗУ, четвертый сегмент данных, содержащий 256 точек данных от 349-ой точки данных включительно, одновременно сохраняется в группе 1 ОЗУ, как показано на точечном изображении 804. Аналогично, перед тем, как данные во временной областью полностью будут введены в группу 3 ОЗУ, общее высокоскоростное арифметическое устройство заканчивает обработку данных, сохраненных в группе 2 ОЗУ, так что оно сразу же начинает обрабатывать данные, сохраняемые в группе 3 ОЗУ; в то же самое время группа 2 ОЗУ может принимать новые данные для сохранения, поскольку обработка данных, ранее сохраненных в группе 2 ОЗУ, завершена. Поэтому, в момент времени, когда 465-я точка данных входного потока данных введена в группы 3 и 1 ОЗУ, пятый сегмент данных, содержащий 256 точек данных, от 456-ой точки данных включительно, одновременно сохраняется в группе 2 ОЗУ, как показано на точечном изображении 805; и так же происходит с остальными данными. Таким образом, прогрессирующее перекрытие, с длительностью перекрытия в 140 точек данных, выполняется посредством последовательно чередующихся операций в группах ОЗУ матрицы ОЗУ. Поэтому три группы ОЗУ и одно общее высокоскоростное арифметическое устройство обеспечивают выполнение нормальной фильтрации повторением чередующихся операций фильтрации и, соответственно, мультиплексирование с разделением по времени общего высокоскоростного арифметического устройства.

В данном варианте осуществления БПФ, ОБПФ и фильтрация в частотной области всех сегментов данных выполняются одним блоком сходящихся вычислений методом мультиплексирования с разделением по времени, что обеспечивает экономию ресурсов схемы; и только с тремя независимыми блоками памяти выполняется обработка перекрытия и обращенного перекрытия при степени перекрытия в 55%, что полностью удовлетворяет требованию к параметрам фильтра с 140-ранговым единичным импульсным откликом; кроме того, групповая задержка фильтра в частотной области в данном варианте осуществления снижается на время выборки 70-ти точек данных, т.е. на 28,5 мкс.

Схемная реализация настоящего изобретения должна включать в себя рассмотренный выше вариант осуществления, но не ограничиваться им. При реализации изобретения для преобразования Фурье используется алгоритм Base 2 FFT. Однако в практических применениях могут использоваться и алгоритм Base 4, и другие алгоритмы БПФ, а также некоторые другие подходящие настройки внутренней структуры соответствующего блока сходящихся вычислений. Хотя в настоящем варианте реализации в качестве общего высокоскоростного арифметического устройства используется блок сходящихся вычислений, также могут использоваться арифметические устройства и другого типа; обработка перекрытия и обращенного перекрытия выполняется по способу, показанному на Фиг.3, но может использоваться и другой способ. Кроме того, на основе различной скорости передачи данных во временной области, различного требования по разрешению в частотной области, различной степени перекрытия и различной скорости сходящихся вычислений и т. д., длина данных для БПФ и перекрытия могут быть изменены, матрица памяти может иметь больше или меньше групп памяти, и может быть больше общих высокоскоростных арифметических устройств, обеспечивающих удовлетворительный компромисс между стоимостью реализации и качеством фильтрации. Электронные схемы в настоящем изобретении могут быть реализованы посредством ASIC (специальная прикладная интегральная схема) или FPGA (программируемая пользователем логическая схема). Изобретение применимо к различным случаям цифровой обработки сигналов, включая прием и передачу сигнала в системах связи.

Можно заключить, что на основе высокоскоростных интегральных схем, таких как ASIC и FPGA, настоящее изобретение преодолевает недостатки традиционного фильтра в частотной области при максимально возможной экономии ресурсов и сниженной стоимости реализации, предоставляя эффективный фильтр на основе БПФ и ОБПФ при динамически изменяемых параметрах фильтрации.

Выше описан вариант реализации изобретения, который не должен ограничивать объем изобретения. Любая модификация, замена и усовершенствование в рамках сущности и принципа изобретения должны включаться в объем настоящего изобретения.

Изобретение относится к технологии цифровой обработки сигнала и может быть использовано в системах цифровой обработки сигнала. Достигаемый технический результат - улучшение фильтрации и снижение времени задержки в фильтре. Частотный фильтр содержит управляющий блок, матрицу памяти, память коэффициентов фильтра, блок коммутации данных, блок формирования выходных данных, блок табличного поиска для циклических множителей и, по меньшей мере, одно высокоскоростное арифметическое устройство. В способе фильтрации в частотной области осуществляют перекрытие и сохранение каждого из сегментов данных временной области, подлежащих фильтрации, в высокоскоростном арифметическом устройстве в различные моменты времени осуществляют преобразования Фурье, операции фильтрации в частотной области и обратного преобразования Фурье для каждого перекрывающегося сегмента данных во временной области, сохраняемого в матрице памяти, сохранение сегментов данных временной области, которые были обработаны посредством операций фильтрации, в блоке памяти матрицы памяти, считывание в последовательности каждого сегмента данных временной области, обращенное перекрытие каждого считываемого сегмента данных временной области для формирования окончательно отфильтрованных выходных данных временной области. 2 н. и 10 з.п. ф-лы, 8 ил.

| US 5612978 А, 18.03.1997 | |||

| УСТРОЙСТВО АДАПТИВНОГО ПОДАВЛЕНИЯ ПОМЕХ | 1998 |

|

RU2160498C2 |

| ЕР 0999651 А2, 10.05.2000 | |||

| US 6459889 B1, 01.10.2002. | |||

Авторы

Даты

2007-10-10—Публикация

2004-07-05—Подача