Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов с широким динамическим диапазоном, в структуре аналоговых микросхем различного функционального назначения (например, быстродействующих операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ) на n-p-n и p-n-p транзисторах, предназначенные для работы с входными синфазными напряжениями, максимальное отрицательное значение которых равно или превышает напряжение отрицательного источника питания [1, 2]. Предлагаемое изобретение относится к данному подклассу ДУ.

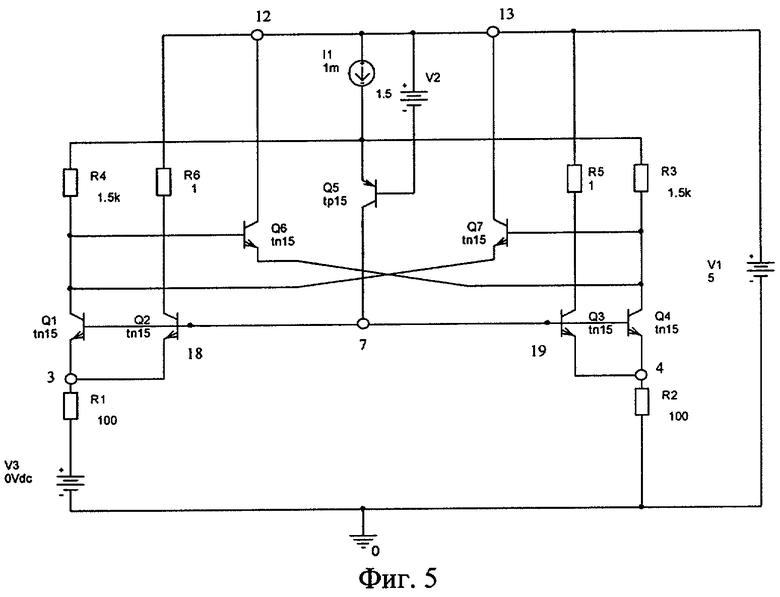

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в статье Дворникова О.В. "Схемотехника биполярно-полевых аналоговых микросхем", Chip News, №10 (103), 2005, стр.21, рис.15, www.chip-news.ru, а также в [2], содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены ко входам 3 и 4 дифференциального усилителя, коллекторы связаны со входом 5 неинвертирующего усилителя тока 6, базы объединены и подключены к выходу 7 неинвертирующего усилителя тока 6, а также первый 8 и второй 9 вспомогательные транзисторы.

Существенный недостаток известного ДУ состоит в том, что он имеет узкий динамический диапазон линейного усиления дифференциальных сигналов (uBX<|UГР|≈50÷200 мВ, фиг.3).

Основная цель предлагаемого изобретения состоит в расширении диапазона активной работы дифференциального усилителя, в пределах которого (при сохранении крутизны) обеспечивается пропорциональность между входным напряжением ДУ (uBX) и его выходным током (iH).

Поставленная цель достигается тем, что в дифференциальный усилитель (фиг.1), содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены ко входам 3 и 4 дифференциального усилителя, коллекторы связаны со входом 5 неинвертирующего усилителя тока 6, базы объединены и подключены к выходу 7 неинвертирующего усилителя тока 6, а также первый 8 и второй 9 вспомогательные транзисторы, вводятся новые элементы и связи - коллекторы первого 1 и второго 2 входных транзисторов связаны со входом 5 неинвертирующего усилителя тока 6 через первый 10 и второй 11 дополнительные резисторы, причем база первого вспомогательного транзистора 8 соединена с коллектором первого 1 входного транзистора, его эмиттер подключен к коллектору второго входного транзистора 2, а коллектор соединен с первым выходом 12 дифференциального усилителя, база второго вспомогательного транзистора 9 соединена с коллектором второго входного транзистора 2, его эмиттер подключен к коллектору первого входного транзистора 1, а коллектор соединен со вторым выходом 13 дифференциального усилителя.

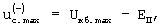

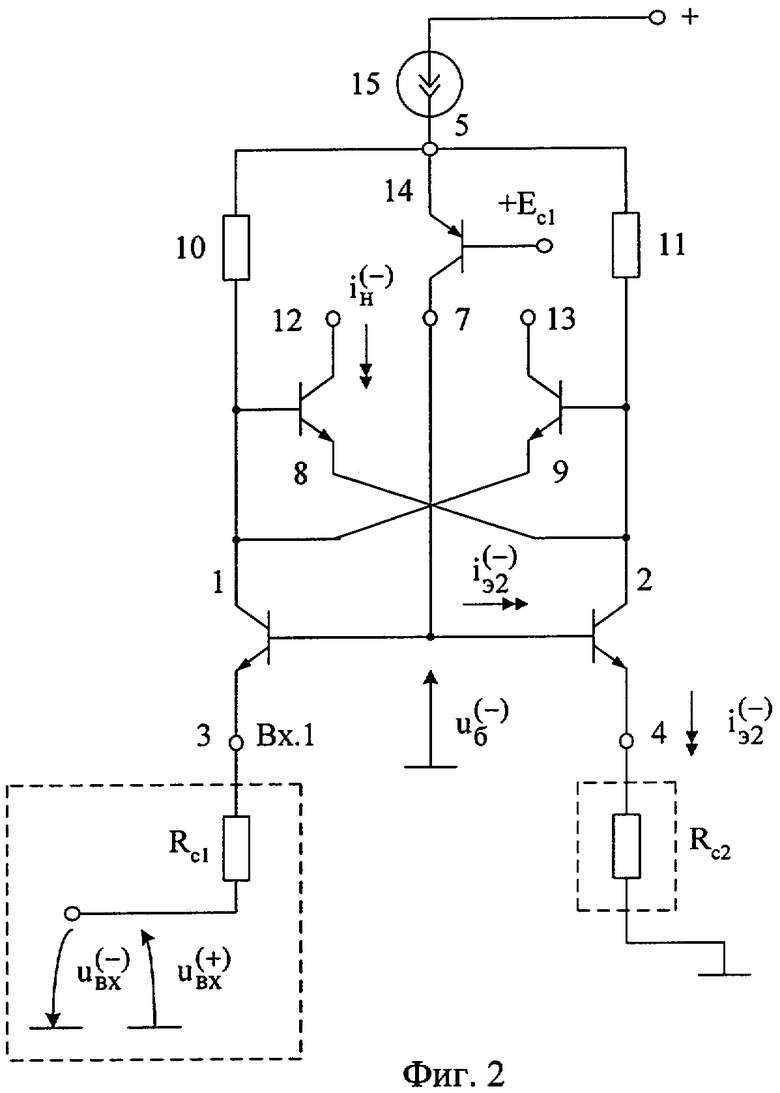

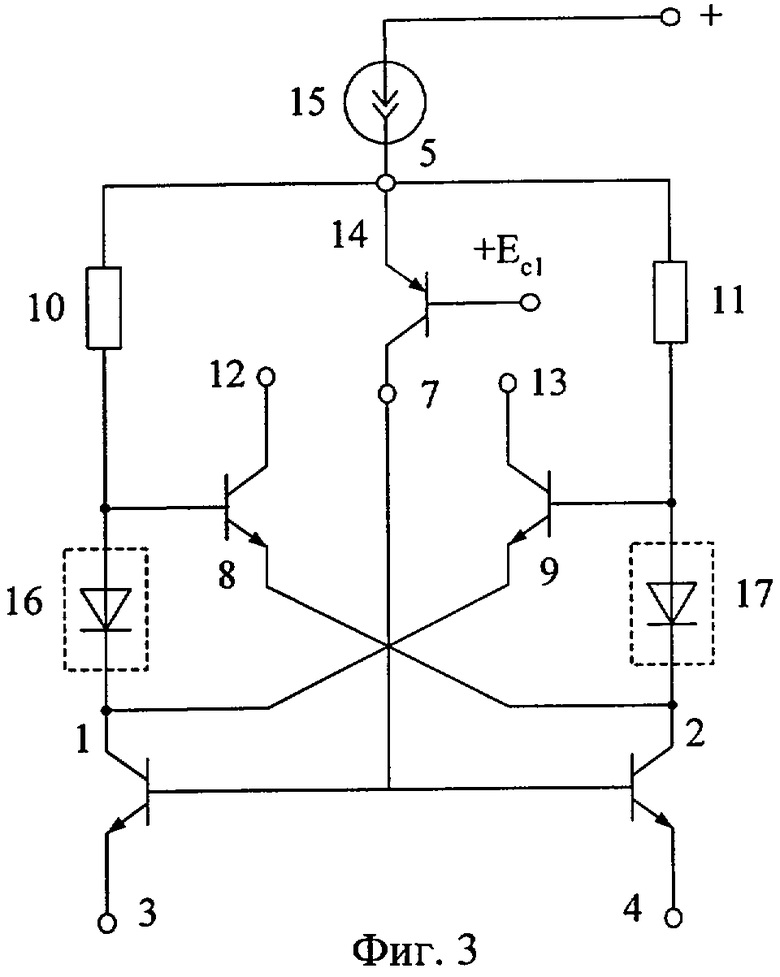

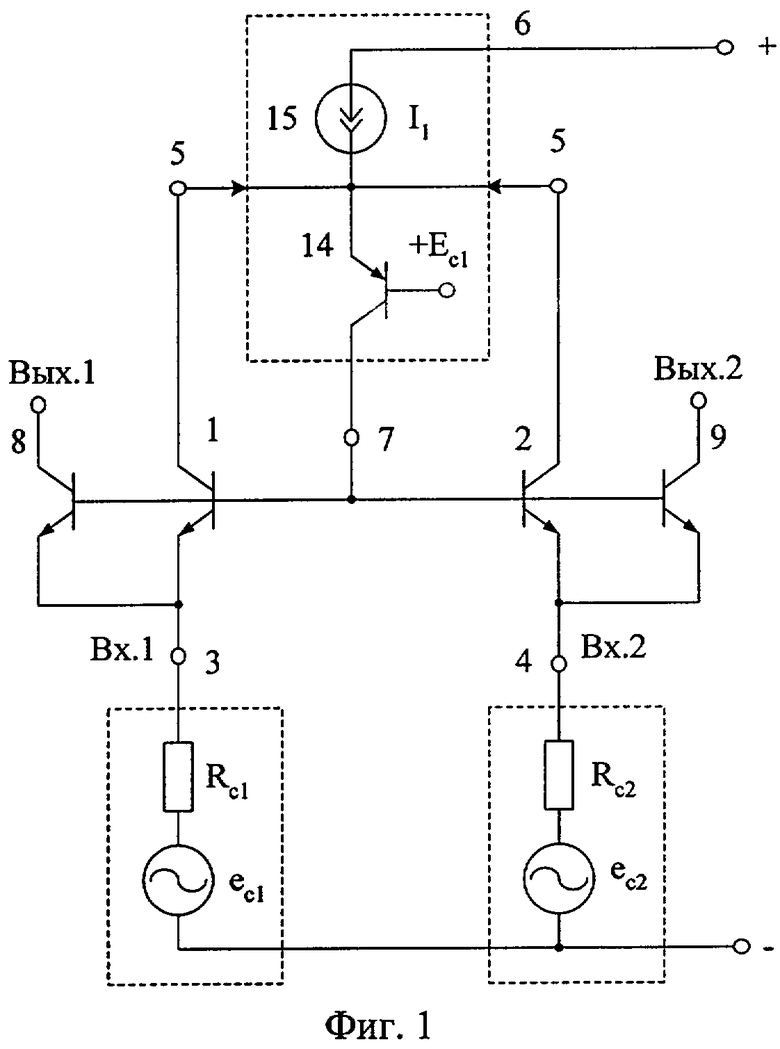

Схема усилителя-прототипа представлена на фиг.1. На фиг.2 показано заявляемое устройство в соответствии с п.1 формулы изобретения. На фиг.3 представлено заявляемое устройство в соответствии с п.3, а на фиг.4 - в соответствии с п.4 формулы изобретения.

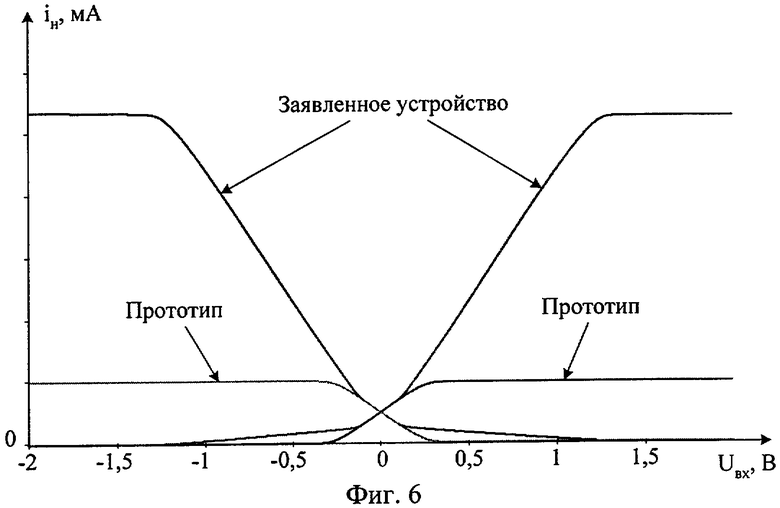

На фиг.5 показан заявляемый ДУ в соответствии с п.3 формулы изобретения в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар", а на фиг.6 - результаты его компьютерного моделирования в сравнении с прототипом, где выходной ток IH - суммарный коллекторный ток транзисторов Q2 и Q6 (левые графики) и Q3, Q7 (правые графики). Входное напряжение uBX=U3 изменялось в диапазоне +(0÷1,5) В и -(0÷1,5) В.

Дифференциальный усилитель (фиг.2) содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых подключены ко входам 3 и 4 дифференциального усилителя, коллекторы связаны со входом 5 неинвертирующего усилителя тока 6, базы - объединены и подключены к выходу 7 неинвертирующего усилителя тока 6, а также первый 8 и второй 9 вспомогательные транзисторы. Коллекторы первого 1 и второго 2 входных транзисторов связаны со входом 5 неинвертирующего усилителя тока 6 через первый 10 и второй 11 дополнительные резисторы, причем база первого вспомогательного транзистора 8 соединена с коллектором первого 1 входного транзистора, его эмиттер подключен к коллектору второго входного транзистора 2, а коллектор соединен с первым выходом 12 дифференциального усилителя, база второго вспомогательного транзистора 9 соединена с коллектором второго входного транзистора 2, его эмиттер подключен к коллектору первого входного транзистора 1, а коллектор соединен со вторым выходом 13 дифференциального усилителя.

Неинвертирующий усилитель тока 6 на фиг.2 выполнен на транзисторе 14, включенном по схеме с общей базой, эмиттер которого является входом 5, а коллектор - выходом 7 неинвертирующего усилителя тока 6.

В дифференциальном усилителе, представленном на фиг.3, между базой первого вспомогательного транзистора 8 и эмиттером второго вспомогательного транзистора 9 включена первая цепь смещения статического уровня 16, а между базой второго вспомогательного транзистора 9 и эмиттером первого вспомогательного транзистора 8 включена вторая цепь смещения статического уровня 17. Это позволяет уменьшить входное пороговое напряжение, при котором в работу включаются транзисторы 8 и 9.

В дифференциальном усилителе, представленном на фиг.4, в схему введены первый 18 и второй 19 дополнительные транзисторы, эмиттерно-базовые переходы которых включены параллельно эмиттерно-базовым переходам соответствующих первого 1 и второго 2 входных транзисторов, а коллекторы подключены к соответствующим первому 12 и второму 13 выходам дифференциального усилителя.

Рассмотрим работу заявляемого ДУ фиг.2.

В статическом режиме транзисторы 8 и 9 не влияют на работу схемы ДУ, т.к. напряжения на их эмиттерно-базовых переходах Uэб.89 близко к нулю. До тех пор, пока Uэб.89 не превысит величину 0,5÷0,6 В, эти транзисторы выключены, и поэтому заявляемый ДУ работает также как и ДУ-прототип - под действием входного сигнала коллекторный ток транзистора 1 уменьшается (увеличивается), а транзистора 2 - увеличивается (уменьшается). Однако сумма этих токов

По мере, например, уменьшения тока коллектора транзистора 1 уменьшается падение напряжения на резисторе 10 и увеличивается падение напряжения на резисторе 11. Как следствие, транзистор 8 открывается, что существенно изменяет токовые соотношения в схеме. Теперь, при дальнейшем увеличении входного напряжения uвх, запирающего транзистор 1, за счет отрицательной обратной связи

Это означает, что все входное напряжение uBX передается с единичным коэффициентом передачи на базы транзисторов 1 и 2

uб≈uвх.

Поэтому ток коллектора транзисторов 2 и 8 не ограничивается как в прототипе и может достигать больших значений

где β2 - коэффициент усиления по току базы транзистора 2.

При отрицательных uBX<0 схема работает аналогично.

Таким образом, в заявляемом устройстве существенно расширяется динамический диапазон, в пределах которого сохраняется пропорциональность между входной и выходной (токовой) координатами. Это является необходимым условием повышения быстродействия многих аналоговых устройств.

Если ввести цепи смещения статического уровня 16 и 17 (фиг.3), то момент перехода транзисторов 8 и 9 из закрытого состояния в активный режим сместится в область более малых значений uBX, что улучшит линейность проходной характеристики iH=f(uBX).

Введение транзисторов 10 и 19 также повышает линейность характеристики в области малых uBX, так как при uBX≈0 передача сигнала на выход 12 (13) обеспечивается транзисторами 18 (19). В это же время большие токи в нагрузке создаются за счет транзисторов 8 и 9.

Результаты компьютерного моделирования ДУ фиг.5, представленные на графиках фиг.6, подтверждают полученные выше теоретические выводы.

Предлагаемый ДУ может использоваться в структуре быстродействующих операционных усилителей и компараторов различного функционального назначения с экстремально высоким диапазоном изменения синфазного сигнала. Действительно максимальные амплитуды положительного и отрицательного uc в схеме фиг.2

где Uкб.max - наименьшее из напряжений пробоя коллекторно-базовых p-n переходов применяемых транзисторов;

EП - напряжение положительного источника питания.

Источники информации

1. Дворников О.В. Схемотехника биполярно-полевых аналоговых микросхем. Chip News, №10 (103), 2005, стр.21, рис.15, www.chip-news.ru

2. G.Horn, J.Huijsing. Extension of the Common-Mode Range of Bipolar Input stages Beyond the Supply Rails of OA and Comparators. IEEJ of Solid State Circuits, 1993, v.sc - 28, №7, P.750-756.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| ВЫСОКОЧАСТОТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2396697C2 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2007 |

|

RU2337470C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2394362C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421891C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С СИММЕТРИЧНОЙ НАГРУЗКОЙ | 2009 |

|

RU2394361C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПРИ НИЗКООМНОЙ НАГРУЗКЕ | 2010 |

|

RU2421885C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402154C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374760C1 |

Изобретение относится к области радиотехники и связи. Технический результат заключается в расширении диапазона активной работы дифференциального усилителя, в пределах которого (при сохранении крутизны) обеспечивается пропорциональность между входным напряжением ДУ (UBX) и его выходным током (IH). Для этого устройство содержит первый (1) и второй (2) входные транзисторы, эмиттеры которых подключены ко входам (3) и (4) дифференциального усилителя, коллекторы связаны со входом (5) неинвертирующего усилителя тока (6), базы объединены и подключены к выходу (7) неинвертирующего усилителя тока (6), а также первый (8) и второй (9) вспомогательные транзисторы. Коллекторы первого (1) и второго (2) входных транзисторов связаны со входом (5) неинвертирующего усилителя тока (6) через первый (10) и второй (11) дополнительные резисторы, причем база первого вспомогательного транзистора (8) соединена с коллектором первого (1) входного транзистора, его эмиттер подключен к коллектору второго входного транзистора (2), а коллектор соединен с первым выходом (12) дифференциального усилителя, база второго вспомогательного транзистора (9) соединена с коллектором второго входного транзистора (2), его эмиттер подключен к коллектору первого входного транзистора (1), а коллектор соединен со вторым выходом (13) дифференциального усилителя. 3 з.п. ф-лы, 6 ил.

| ДВОРНИКОВ О.В., Схемотехника биполярно-полевых аналоговых микросхем, Chip News, №10 (103), 2005, с.21, рис.15, www.chip-news.ru | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2257002C2 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2234797C1 |

| Дифференциальный усилитель | 1974 |

|

SU764099A1 |

| US 4390848, 28.06.1983 | |||

| Тампон для ликвидации поглощений промывочной жидкости и водопритоков | 1985 |

|

SU1258985A1 |

Авторы

Даты

2007-10-27—Публикация

2006-03-27—Подача