Изобретение относится к импульсной технике и может найти применение в высоконадежных цифровых синхронизирующих устройствах, построенных на быстродействующей элементной базе.

Известно мажоритарное счетное резервированное устройство (А.С. №834925, Н03K 21/34), содержащее источник импульсов и счетные каналы, каждый из которых содержит счетчик, триггер, элемент совпадения и мажоритарный элемент, выход которого соединен с входом установки счетчика, вход и выход которого соединены соответственно с входом данного канала и входом триггера того же канала, а входы всех каналов соединены с входами мажоритарных элементов всех каналов, выход мажоритарного элемента каждого канала соединен с первым входом элемента совпадения этого канала, выход и второй вход которого соединены соответственно с входом сброса триггера и счетным входом счетчика этого канала.

Недостатком этого устройства является отсутствие фиксированного сброса на выходе элемента совпадения, что приводит к понижению надежности устройства.

Наиболее близким к предлагаемому устройству является резервированный делитель частоты (А.С. №1265995, Н03K 23/00), содержащий три канала, каждый из которых состоит из счетчика импульсов, мажоритарного элемента и элемента эквивалентности, при этом счетный вход счетчика импульсов соединен с входной шиной данного канала, первый вход мажоритарного элемента соединен с выходом счетчика импульсов, первым входом элемента эквивалентности и с одним из двух других входов мажоритарных элементов соседних каналов, второй вход элемента эквивалентности подключен к выходной шине данного канала и к выходу мажоритарного элемента, D-триггер, элемент И и элемент ИЛИ-НЕ, а последний разряд счетчика импульсов выполнен в виде счетного триггера с возможностью установки его в «0» или «1», при этом информационный вход D-триггера и его вход установки в «1» соединены с выходом элемента эквивалентности, а счетный вход - с входной шиной, прямой выход D-триггера соединен с первым входом элемента ИЛИ-НЕ, второй вход которого соединен с выходом мажоритарного элемента и с первым входом элемента И, выходы элемента ИЛИ-НЕ и элемента И соединены с входами установки в «0» и в «1» счетного триггера последнего разряда счетчика импульсов, входы установки в «0» счетных триггеров остальных разрядов которого соединены со вторым входом элемента И и с инверсным выходом D-триггера.

К недостаткам данного устройства относится то, что длительность импульса сброса счетчика определяется задержками элемента эквивалентности, D-триггера, элемента И, элемента ИЛИ-НЕ, счетного триггера и не является фиксированной.

В устройствах же построенных на быстродействующей элементной базе, особенно устройствах, где все элементы находятся в одном кристалле матричной БИС (большой интегральной схемы), задержки на элемент составляют единицы или доли наносекунд. Одна и та же электрическая цепь в зависимости от места ее расположения обладает различными задержками. Поэтому длительность импульса сброса может быть недостаточной, что приводит к понижению надежности.

Таким образом, целью настоящего изобретения является повышение надежности работы устройства.

Указанная цель достигается тем, что в мажоритарном счетном резервированном устройстве, содержащем резервные каналы, каждый из которых содержит счетчик, счетный триггер, мажоритарный элемент, D-триггер, элемент И, входную и выходную шины, при этом входная шина соединена со счетным входом счетчика, выход которого соединен с синхровходом счетного триггера, входы мажоритарного элемента соединены с другими входами мажоритарных элементов других резервных каналов, а выход - с выходной шиной канала и первым входом элемента И, согласно изобретению в каждый резервный канал введены элемент задержки и второй D-триггер, при этом входная шина соединена с входом элемента задержки, первый выход которого соединен с синхровходом второго D-триггера, а второй выход - с синхровходом D-триггера, выход счетного триггера соединен с информационным входом второго D-триггера, выход которого соединен с первым входом мажоритарного элемента, выход мажоритарного элемента соединен также с информационным входом D-триггера, выход которого соединен с входом сброса счетного триггера, а инверсный выход соединен со вторым входом элемента И, выход которого соединен со входом сброса счетчика.

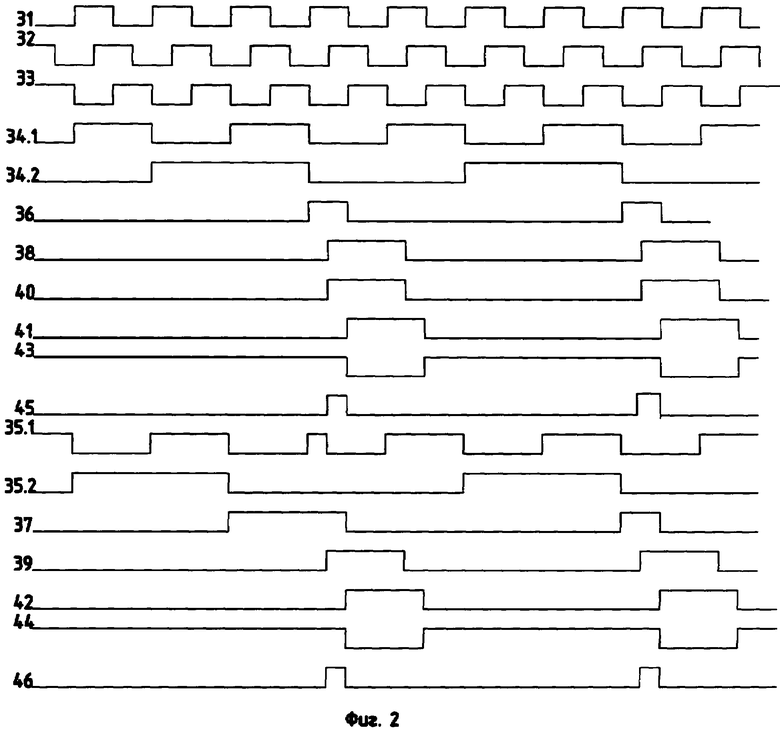

На фиг.1 представлена электрическая функциональная схема предлагаемого устройства.

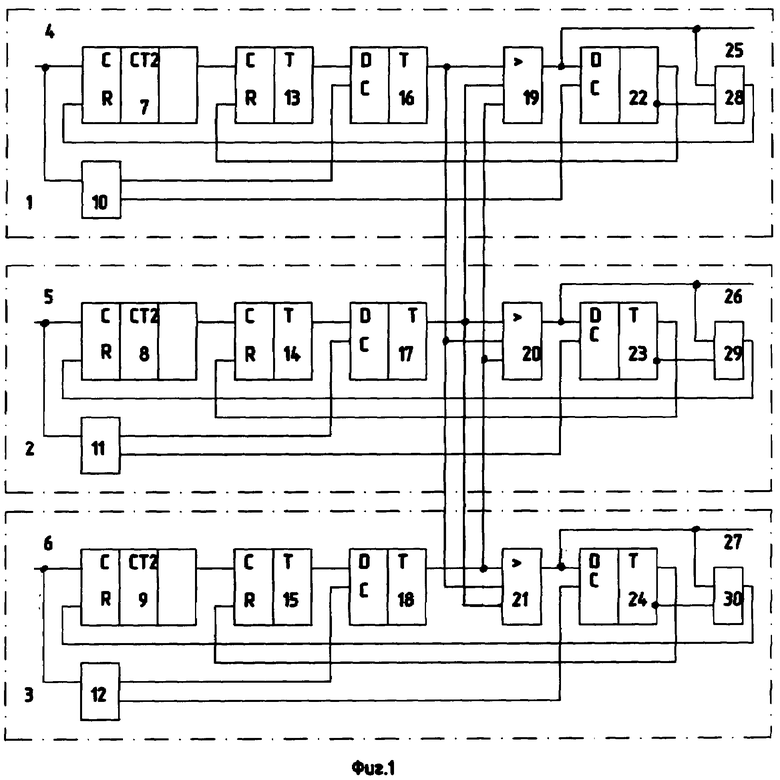

На фиг.2 представлены временные диаграммы, поясняющие принцип работы предлагаемого устройства.

Устройство (фиг.1) содержит резервные каналы (например, три) 1-3, каждый из которых содержит входные шины 4, 5, 6, счетчики 7, 8, 9, элементы задержки 10, 11, 12, счетные триггеры 13, 14, 15, вторые D-триггеры 16, 17, 18, мажоритарные элементы 19, 20, 21, D-триггеры 22, 23, 24, выходные шины каналов 25, 26, 27 (причем входные и выходные шины каналов являются также входными и выходными шинами устройства), элементы И 28, 29, 30.

Входная шина 4 резервного канала 1 соединена со счетным входом счетчика 7, выход которого соединен с синхровходом счетного триггера 13 и входом элемента задержки 10, первый выход которого соединен с синхровходом второго D-триггера 16, а второй выход - с синхровходом D-триггера 22. Выход счетного триггера 13 соединен с информационным входом второго D-триггера 16, выход которого соединен с первым входом мажоритарного элемента 19, выход мажоритарного элемента 19 соединен с информационным входом D-триггера 22, а также с выходной шиной канала 25 и первым входом элемента И 28. Выход D-триггера 22 соединен с входом сброса счетного триггера 13, а инверсный выход соединен со вторым входом элемента И 28, выход которого соединен со входом сброса счетчика 7. При этом входы мажоритарных элементов 19, 20, 21 всех резервных каналов соединены между собой.

Устройство остальных каналов 2 и 3 и связи между их элементами выполнены аналогичным образом.

Временные диаграммы, изображенные на фиг.2, обозначают следующее:

31 - сигналы на входных шинах 4, 5, 6

32, 33 - сигналы на выходах элементов задержек 10, 11, 12

34.1, 34.2 - сигналы на выходах счетчиков 7, 8

3 5.1, 35.2 - сигналы на выходах счетчика 9

36 - сигналы на выходах счетных триггеров 13, 14

37 - сигналы на выходе счетного триггера 15

38 - сигналы на выходах вторых триггеров 16, 17

39 - сигналы на выходе второго триггера 18

40 - сигналы на выходе мажоритарных элементов 19, 20, 21

41 - сигналы на выходах триггеров 22, 23

42 - сигналы на выходе триггера 24

43 - сигналы на инверсных выходах триггеров 22, 23

44 - сигналы на инверсном выходе триггера 24

45 - сигналы на выходах элементов И 28, 29

46 - сигналы на выходе элемента И 30

Устройство работает следующим образом. Предположим, что счетчик 9 канала 3 сбился.

По переполнению счетчика 9 на выходе счетного триггера 15 устанавливается единичное состояние (временная диаграмма 37), а через время, определяемое элементом задержки 12 (временная диаграмма 32), единичное состояние устанавливается на выходе второго триггера 18 (временная диаграмма 39). Аналогично, единичное состояние устанавливается на выходах счетных триггеров 13, 14 и вторых D-триггеров 16, 17 (временные диаграммы 36, 38). Так как входы мажоритарных элементов 19, 20, 21 установились в единичное состояние, то на их выходах также устанавливается единичное состояние. Так как на входах элементов И 28, 29, 30 установилось единичное состояние (инверсные выходы триггеров 22, 23, 24 - временные диаграммы 43, 44 также находятся в единичном состоянии), то и на выходах устанавливается единичное состояние (временные диаграммы 45, 46), которое устанавливает счетчик 9 в нулевое состояние (временные диаграммы 35.1, 35.2), а в счетчиках 7,8 подтверждается нулевое состояние (временные диаграммы 34.1, 34.2). Таким образом произошло фазирование счетчиков.

Далее, по следующему фронту сигнала с элементов задержек 10, 11, 12 (временная диаграмма 33) триггеры 22, 23, 24 переходят в единичное состояние (временные диаграммы 41, 42). Одновременно счетные триггеры 13, 14, 15 устанавливаются в нулевое состояние. На инверсных выходах триггеров 22, 23, 24 устанавливается нулевое состояние (временные диаграммы 43, 44). Заканчивается формирование импульса сброса на элементах И 28, 29, 30 (временные диаграммы 45, 46). Так как на информационных входах триггеров 16, 17, 18 устанавливается нулевое состояние, то по фронту с элементов задержек 10, 11, 12 триггеры 16, 17, 18 и мажоритарные элементы 19, 20, 21 переходят в нулевое состояние. Затем триггеры 22, 23, 24 переходят также в нулевое состояние. Все элементы предлагаемого устройства установились в исходное состояние.

Сигналы с выходов элементов И 28, 29, 30 периодически устанавливают (фазируют счетчики 7, 8, 9), а сигналы с выходов триггеров 22, 23, 24 периодически устанавливают счетные триггеры 13, 14, 15 в нулевое состояние. Величина установки фиксирована (задается элементом задержки) и не зависит от задержек элементов, что позволяет повысить надежность работы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1990 |

|

SU1780187A1 |

| Многоканальный резервированный генератор | 1989 |

|

SU1699028A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 2022 |

|

RU2785274C1 |

| Резервированный счетчик | 1982 |

|

SU1040603A1 |

| АСИНХРОННОЕ ВХОДНОЕ УСТРОЙСТВО | 2019 |

|

RU2738963C1 |

| Резервированный делитель частоты | 1983 |

|

SU1109910A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное устройство для управления пуском и рестартом при сбоях микропроцессорной системы | 1985 |

|

SU1247869A1 |

| Многоканальное резервированное счетное устройство | 1983 |

|

SU1099389A1 |

Изобретение относится к импульсной технике и может использоваться в высоконадежных цифровых синхронизирующих устройствах, построенных на быстродействующей элементной базе. Технический результат заключается в повышении надежности устройства. Устройство содержит резервные каналы (1-3), каждый из которых содержит счетчик (7-9), счетный триггер (13-15), мажоритарный элемент (19-21), D-триггер (16-18), элемент И (28-30), входную (4-6) и выходную шины. В каждый резервный канал включены элемент задержки (10-12) и второй D-триггер (22-24). 2 ил.

Мажоритарное счетное резервированное устройство, содержащее резервные каналы, каждый из которых содержит счетчик, счетный триггер, мажоритарный элемент, D-тригтер, элемент И, входную и выходную шины, при этом входная шина соединена со счетным входом счетчика, выход которого соединен с синхровходом счетного триггера, входы мажоритарного элемента соединены с другими входами мажоритарных элементов других резервных каналов, а выход - с выходной шиной канала и первым входом элемента И, отличающееся тем, что в каждый резервный канал введены элемент задержки и второй D-триггер, при этом входная шина соединена с входом элемента задержки, первый выход которого соединен с синхровходом второго D-триггера, а второй выход - с синхровходом D-триггера, выход счетного триггера соединен с информационным входом второго D-триггера, выход которого соединен с первым входом мажоритарного элемента, выход мажоритарного элемента соединен также с информационным входом D-триггера, выход которого соединен с входом сброса счетного триггера, а инверсный выход соединен со вторым входом элемента И, выход которого соединен с входом сброса счетчика.

| Резервированный делитель частоты | 1985 |

|

SU1265995A1 |

| Мажоритарное счетное резервированноеуСТРОйСТВО | 1979 |

|

SU834925A1 |

| Мажоритарное счетное резервированное устройство | 1986 |

|

SU1338120A1 |

| Мажоритарное счетно-резервированное устройство | 1989 |

|

SU1690190A1 |

| US 5450460 A, 12.09.1995. | |||

Авторы

Даты

2007-11-20—Публикация

2006-06-26—Подача