Изобретение относится к цифровой технике в сфере обмена информацией и может быть использовано в космической, авиационной, кораблестроительной и других отраслях в последовательных асинхронных интерфейсах.

Известно резервированное устройство для синхронизации сигналов (а.с. СССР №378830), содержащее в каждом из каналов триггера записи, хранения и выдачи информации, мажоритарный элемент и шину тактовых импульсов.

Недостатком этого устройства является возможность формирования его схемой ложных выходных сигналов при поступлении на входы асинхронной информации.

В асинхронных устройствах входные сигналы могут изменять свою длительность за счет произвольного расположения синхросигналов. Причем, изменение длительности может увеличиваться или уменьшаться на период синхросигналов. В распределителе уровней по а.с. СССР №1172002, содержащем регистр сдвига, выходы которого являются выходными шинами, шину синхронизации, которая соединена с С-входом основного регистра сдвига, шину тактирования, дополнительный регистр сдвига, элемент И-НЕ, RS-триггер, выход которого соединен с D-входом дополнительного регистра сдвига, выход первого разряда которого соединен с D-входом основного регистра сдвига, а инверсный выход последнего разряда - с первым входом элемента И-НЕ и R-входом RS-триггера, S-вход которого соединен с выходом элемента И-НЕ, второй вход которого соединен с шиной тактирования, причем С-вход дополнительного регистра сдвига соединен с шиной синхронизации. В этом устройстве длительность не изменяется и равна числу разрядов регистра, умноженному на период синхросигналов.

Недостатком этого устройства является то, что оно работоспособно для периодичных сигналов одной длительности. При изменении длительности по входной шине или по двум шинам, т.е. в асинхронных интерфейсах, устройство не работоспособно. Кроме того, при приеме информации по асинхронным высокочастотным интерфейсам появляется проблема в изменении длительности вследствие разности задержек включения и выключения на гальванической развязке, кабельной сети, интегральных схемах.

Задачей предлагаемого изобретения является повышение стабильности длительности в асинхронных устройствах, в том числе, в последовательных асинхронных интерфейсах.

Поставленная задача решается тем, что предложено асинхронное входное устройство, содержащее входные, выходные и синхронизирующую шины, регистр сдвига, триггер и элемент 2И-НЕ. Дополнительно в него введены дополнительный элемент 2И-НЕ, первый, второй и третий инверторы, элемент 2И, счетчик на вычитание, первый, второй, третий, четвертый и пятый Д-триггеры и шина сброса.

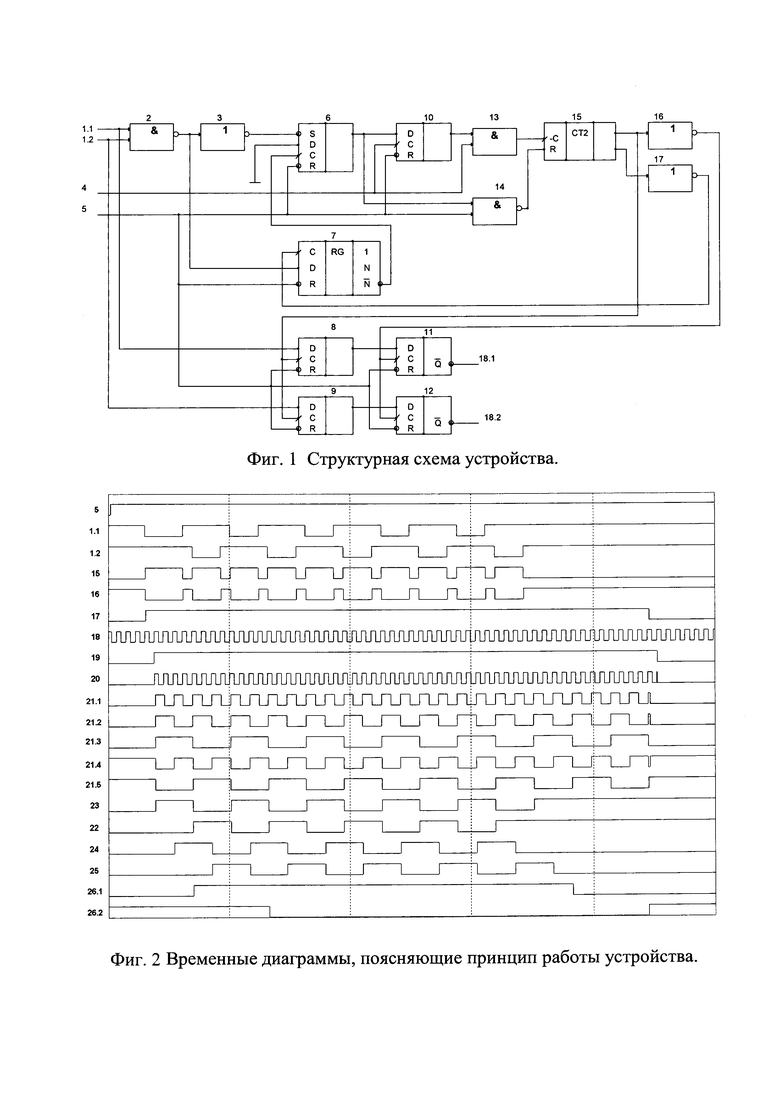

На фиг. 1 представлена структурная схема предлагаемого устройства,

где:

1.1, 1.2 - первая и вторая входные шины,

2 - дополнительный элемент 2И-НЕ,

3 - первый инвертор,

4 - синхронизирующая шина,

5 - шина сброса

6 - триггер,

7 - регистр сдвига,

8 - второй D-триггер,

9 - третий D-триггер,

10 - первый D-триггер,

11 - четвертый D-триггер,

12 - пятый D-триггер,

13 - элемент 2И,

14 - элемент 2И-НЕ,

15 - счетчик на вычитание,

16 - второй инвертор,

17 - третий инвертор,

18.1, 18.2 - первая и вторая выходные шины.

Первая входная шина (1.1) соединена с первым входом дополнительного элемента 2И-НЕ (2) и с D-входом второго триггера (8), а вторая входная шина (1.2) соединена со вторым входом дополнительного элемента 2И-НЕ (2) и с D-входом третьего Д-триггера (9). Выход дополнительного элемента 2И-НЕ (2) соединен с D-входом регистра сдвига (7) и через первый инвертор (3) с S-входом триггера (6). Шина сброса (5) соединена с входами сброса триггера (6), регистра сдвига (7), первого -пятого Д-триггеров (8-12) и первым входом элемента 2И-НЕ (14), выход которого соединен с входом сброса счетчика на вычитание (15). D-вход триггера (6) соединен с общей точкой, а выход соединен с D-входом первого триггера (10) и со вторым входом элемента 2И-НЕ (14). Синхронизирующая шина (4) соединена с синхровходом первого триггера (10) и первым входом элемента 2И (13). Выход первого триггера (10) соединен со вторым входом элемента 2И (13), выход которого соединен со счетным входом счетчика на вычитание (15), младший разряд которого соединен с синхровходами второго (8) и третьего (9) Д-триггеров и с входом второго инвертора (16), выход которого соединен с синхровходами четвертого (11) и пятого (12) Д-триггеров, выход старшего разряда счетчика на вычитание (15) через третий инвертор (17) соединен с синхровходом регистра сдвига (7), инверсный выход которого соединен с синхровходом триггера (6). Выходы второго (8) и третьего (9) Д-триггеров соединены соответственно с D-входами четвертого (11) и пятого (12) Д-триггеров, инверсные выходы которых соединены соответственно с первой и второй выходными шинами (18.1), (18.2).

На фиг. 2 представлены временные диаграммы, поясняющие принцип работы предлагаемого устройства.

Устройство работает следующим образом.

В исходном состоянии по шине сброса (5) все триггеры и счетчик на вычитание устанавливаются в нулевое состояние. По приходу первого импульса (нулевое состояние) по первой входной шине (1.1) на выходе дополнительного элемента 2И-НЕ (2) (временная диаграмма 15 устанавливается единичное состояние, на выходе первого инвертора (3) -нулевое (временная диаграмма 16) и на выходе триггера (6) (временная диаграмма 17) - единичное. Далее, по фронту с синхронизирующей шины (4) (временная диаграмма 18) на выходе первого D-триггера (10) (временная диаграмма 19) устанавливается единичное состояние и на выходе элемента 2И (13) (временная диаграмма 20) появляется импульс, который устанавливает все разряды счетчика на вычитание (15) (временные диаграммы 21.1, 21.2, 21,3) в единичное состояние, а на выходах второго (16) и третьего (17) инверторов устанавливается нулевое состояние (временные диаграммы 21.4, 21.5).

Так как на входе третьего Д-триггера (9) присутствовало единичное состояние, то и на выходе по фронту сигнала со счетчика на вычитание (15) третий Д-триггер переходит в единичное состояние (временная диаграмма 23).

Состояние второго Д-триггера (8) (временная диаграмма 22) остается без изменений.

Далее, по синхроимпульсам со счетчика на вычитание (15) (временная диаграмма 21.2) второй (8) и третий (9) Д-триггеры изменяют свое состояние, которое поступает на их D-входы (временные диаграммы 22, 23), а четвертый (11) и пятый (12) Д-триггеры повторяют состояние второго и третьего Д-триггеров (временные диаграммы 24, 25) по синхроимпульсам с выхода второго инвертора (16) (временная диаграмма 21.4). По первому синхроимпульсу с третьего инвертора (17) (временная диаграмма 21.5) первый разряд регистра (7) переходит в единичное состояние, а затем и инверсный выход второго разряда - в нулевое состояние, (временные диаграммы 26.1, 26.2).

Когда на первой и второй входных шинах (1.1), (1.2) прекращаются импульсы (единичное состояние) на выходе дополнительного элемента 2И-НЕ (2) устанавливается нулевое состояние. Так как на входах второго (8) и третьего (9) Д-триггеров установилось единичное состояние, то и на их выходах устанавливается единичное состояние. На инверсных выходах четвертого (11) и пятого (12) Д-триггеров и на первой и второй выходных шинах (18.1), (18.2) по синхроимпульсам со второго инвертора устанавливается единичное состояние, т.е. прекращается выработка сигналов.

После того как на выходе дополнительного элемента 2И-НЕ (2) установилось нулевое состояние, то на выходе первого разряда регистра (7) устанавливается нулевое состояние (временная диаграмма 26.1) по синхроимпульсу с третьего инвертора (17), а затем и на инверсном выходе второго разряда устанавливается единичное состояние (временная диаграмма 26.2). Так как информационный вход триггера (6) соединен с общей точкой, то по фронту с инверсного выхода регистра (7) триггер (6) устанавливается в нулевое состояние. Элемент 2И-НЕ (14) переходит в единичное состояние, происходит сброс счетчика на вычитание (15). Первый Д-триггер (10) по фронту с синхронизирующей шины (4) переходит в единичное состояние. На выходе элемента 2И (13) прекращается выработка импульсов. Устройство переходит в исходное состояние и ждет поступления следующих входных импульсов.

Таким образом предложено асинхронное входное устройство, содержащее первую входную, синхронизирующую и первую выходную шины, регистр сдвига, триггер и элемент 2И-НЕ. Дополнительно в него введены дополнительный элемент 2И-НЕ, первый, второй и третий инверторы, элемент 2И, счетчик на вычитание, первый, второй, третий, четвертый и пятый Д-триггеры вторая входная шина, вторая выходная шина и шина сброса. Первая входная шина соединена с первым входом дополнительного элемента 2И-НЕ и с D-входом второго триггера, а вторая входная шина соединена со вторым входом дополнительного элемента 2И-НЕ и с D-входом третьего Д-триггера. Выход дополнительного элемента 2И-НЕ соединен с D-входом регистра сдвига и через первый инвертор с S-входом триггера. Шина сброса соединена с входами сброса триггера, регистра сдвига, первого - пятого Д-триггеров и первым входом элемента 2И-НЕ, выход которого соединен с входом сброса счетчика на вычитание. D-вход триггера соединен с общей точкой, а выход соединен с D-входом первого триггера и со вторым входом элемента 2И-НЕ. Синхронизирующая шина соединена с синхровходом первого триггера и первым входом элемента 2И. Выход первого триггера соединен со вторым входом элемента 2И, выход которого соединен со счетным входом счетчика на вычитание, младший разряд которого соединен с синхровходами второго и третьего Д-триггеров и с входом второго инвертора, выход которого соединен с синхровходами четвертого и пятого Д-триггеров, выход старшего разряда счетчика на вычитание через третий инвертор соединен с синхровходом регистра сдвига, инверсный выход которого соединен с синхровходом триггера. Выходы второго и третьего Д-триггеров соединены соответственно с D-входами четвертого и пятого Д-триггеров, инверсные выходы которых соединены соответственно с первой и второй выходными шинами.

Техническим результатом предлагаемого устройства является повышение стабильности длительности входных сигналов в асинхронных устройствах.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Цифровой измеритель длительности одиночных импульсов | 1984 |

|

SU1257600A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для управления динамической памятью | 1990 |

|

SU1800481A1 |

| Устройство для сопряжения между абонентами | 1988 |

|

SU1594550A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ | 1989 |

|

RU2044405C1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к цифровой технике в сфере обмена информацией с использованием последовательных асинхронных интерфейсов. Технический результат - повышение стабильности длительности входных сигналов в асинхронных устройствах. Асинхронное входное устройство, содержащее входные, синхронизирующую и выходные шины, регистр сдвига, триггер и элемент 2И-НЕ. Отличительная особенность заключается в том, что дополнительно введены: дополнительный элемент 2И-НЕ, первый, второй и третий инверторы, элемент 2И, счетчик на вычитание, первый, второй, третий, четвертый и пятый Д-триггеры и шина сброса. 2 ил.

Асинхронное входное устройство, содержащее первую входную, синхронизирующую и первую выходную шины, регистр сдвига, триггер и элемент 2И-НЕ, отличающее тем, что в него дополнительно введены дополнительный элемент 2И-НЕ, первый, второй и третий инверторы, элемент 2И, счетчик на вычитание, первый, второй, третий, четвертый и пятый Д-триггеры, вторая входная шина, вторая выходная шина и шина сброса, причем первая входная шина соединена с первым входом дополнительного элемента 2И-НЕ и с D-входом второго триггера, а вторая входная шина соединена со вторым входом дополнительного элемента 2И-НЕ и с D-входом третьего Д-триггера, выход дополнительного элемента 2И-НЕ соединен с D-входом регистра сдвига и через первый инвертор с S-входом триггера, шина сброса соединена с входами сброса триггера, регистра сдвига, первого - пятого Д-триггеров и первым входом элемента 2И-НЕ, выход которого соединен с входом сброса счетчика на вычитание, D-вход триггера соединен с общей точкой, а выход соединен с D-входом первого триггера и со вторым входом элемента 2И-НЕ, синхронизирующая шина соединена с синхровходом первого триггера и первым входом элемента 2И, выход первого триггера соединен со вторым входом элемента 2И, выход которого соединен со счетным входом счетчика на вычитание, младший разряд которого соединен с синхровходами второго и третьего Д-триггеров и с входом второго инвертора, выход которого соединен с синхровходами четвертого и пятого Д-триггеров, выход старшего разряда счетчика на вычитание через третий инвертор соединен с синхровходом регистра сдвига, инверсный выход которого соединен с синхровходом триггера, выходы второго и третьего Д-триггеров соединены соответственно с D-входами четвертого и пятого Д-триггеров, инверсные выходы которых соединены соответственно с первой и второй выходными шинами.

| Распределитель уровней | 1984 |

|

SU1172002A1 |

| Устройство синхронизации работы граней в мажоритированных системах | 2018 |

|

RU2684198C1 |

| Параллельный асинхронный регистр на КМДП-транзисторах | 1988 |

|

SU1599899A1 |

| Устройство для передачи и приема информации | 1982 |

|

SU1176360A1 |

| Многоканальное асинхронное устройство приоритета | 1984 |

|

SU1174925A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Способ и аппарат для получения гидразобензола или его гомологов | 1922 |

|

SU1998A1 |

| Устройство для измерения давления | 1977 |

|

SU638858A1 |

Авторы

Даты

2020-12-21—Публикация

2019-12-25—Подача