Изобретение относится к области радиотехники и может использоваться в приемниках шумоподобных частотно-манипулированных сигналов с непрерывной фазой.

Известно устройство слежения за задержкой шумоподобных фазоманипулированных сигналов, содержащее временной дискриминатор, включающий два идентичных канала. состоящих из последовательно включенных перемножителя, полосового фильтра и детектора огибающей, причем на опорный вход перемножителя первого канала дискриминатора подается опережающая кодовая последовательность, на опорный вход перемножителя второго канала дискриминатора - задержанная кодовая последовательность, а выходы каналов подключены к вычитателю. последовательно соединенные петлевой фильтр, подключенный к выходу вычитателя. генератор тактовой частоты, генератор кодовой последовательности. выходы которого соединены с опорными входами перемножителей первого и второго каналов дискриминатора (Радиотехнические системы / Ю.П.Гришин, В.П.Ипатов, Ю.М.Казаринов и др. Под ред. Ю.М.Казаринова. - М.: Высшая школа, 1990, с.328, рис.15.3).

Однако известное устройство имеет недостаток, заключающийся в смещении нуля дискриминационной характеристики вследствие неидентичности каналов дискриминатора.

Наиболее близким техническим решением к предлагаемому является устройство слежения за задержкой шумоподобных фазоманипулированных сигналов, содержащее первый и второй перемножители, сигнальные входы которых объединены, а выходы подключены к цифровому временному дискриминатору, к выходу которого подключены последовательно соединенные петлевой фильтр и блок формирования кодовых последовательностей, выходы которого подключены к опорным входам цифрового временного дискриминатора, блок формирования опорных сигналов, выходы которого соединены с опорными входами первого и второго перемножителей (Сетевые спутниковые радионавигационные системы / В.С.Шебшаевич, П.П.Дмитриев, Н.В.Иванцевич и др. Под ред. В. С.Шебшаевича. - М.: Радио и связь, 1982, с.98, рис.8.10).

Недостаток устройства - потери в помехоустойчивости (примерно 3 дБ) по сравнению с устройством с двухканальным дискриминатором, обусловленные последовательным способом сравнения выходных сигналов «опережающего» и «задержанного» каналов.

В основу предлагаемого изобретения положено создание устройства слежения за задержкой шумоподобных частотно-манипулированных сигналов, что позволяет решить задачу повышения помехоустойчивости и точности синхронизации опорных сигналов.

Поставленная задача решается тем, что в устройство слежения за задержкой шумоподобных частотно-манипулированных сигналов, содержащее блок формирования опорных сигналов, соответствующие выходы которого соединены с опорными входами первого и второго перемножителей, сигнальные входы которых объединены, а выходы которых подключены к цифровому временному дискриминатору, содержащему первый и второй цифровые интеграторы и вычислительный блок, последовательно соединенные петлевой фильтр и блок формирования кодовых последовательностей, который содержит управляемый фазовращатель, опорный генератор и генератор псевдослучайной последовательности, при этом выход вычислительного блока подключен к петлевому фильтру, а на управляющий вход управляемого фазовращателя подается код с выхода петлевого фильтра, согласно изобретению в цифровой временной дискриминатор введены первый и второй оперативные запоминающие элементы, подключенные к выходам первого и второго цифровых интеграторов и объединенные по синхронизирующему входу друг с другом, а также с первым и вторым цифровыми интеграторами, третий, четвертый, пятый и шестой перемножители, вычитатель и сумматор, при этом к выходу первого оперативного запоминающего элемента подключены третий и пятый перемножители, к выходу второго оперативного запоминающего элемента - четвертый и шестой перемножители, причем выходы третьего и шестого, четвертого и пятого перемножителей попарно объединены через вычитатель и сумматор соответственно, первый и второй демультиплексоры, подключенные к вычитателю и сумматору соответственно, третий, четвертый, пятый и шестой цифровые интеграторы, причем к выходам первого демультиплексора подключены третий и пятый цифровые интеграторы, а к выходам второго демультиплексора - четвертый и шестой цифровые интеграторы, выходы которых подключены к вычислительному блоку, в блок формирования кодовых последовательностей введены делитель частоты на два, вход которого подключен к выходу управляемого фазовращателя, дешифратор, входы которого подключены к соответствующим выходам генератора псевдослучайной последовательности, последовательно соединенные аккумулятор фазы, третий оперативный запоминающий элемент и первый постоянный запоминающий элемент, второй постоянный запоминающий элемент, который подключен к опорному входу аккумулятора фазы, при этом управляющий вход аккумулятора фазы подключен к выходу генератора псевдослучайной последовательности, синхронизирующие входы первого постоянного запоминающего элемента, третьего оперативного запоминающего элемента и аккумулятора фазы соединены и подключены к выходу управляемого фазовращателя и к синхронизирующим входам первого и второго цифровых интеграторов, первого и второго оперативных запоминающих элементов и первого и второго демультиплексоров цифрового временного дискриминатора, вход генератора псевдослучайной последовательности подключен к выходу делителя частоты на два, выход дешифратора соединен с синхронизирующими входами третьего, четвертого, пятого и шестого цифровых интеграторов цифрового временного дискриминатора, соответствующие выходы первого постоянного запоминающего элемента соединены с опорными входами третьего, четвертого и пятого, шестого перемножителей цифрового временного дискриминатора, вычислительный блок осуществляет формирование сигнала ошибки путем сравнения квадратов модулей опережающего и задержанного сигналов, поступающих с выходов соответствующих цифровых интеграторов, при этом величина и знак сигнала ошибки определяются значением относительной задержки принятого и опорного сигналов, а выходом устройства является выход генератора псевдослучайной последовательности.

Введение перечисленных узлов с описанными связями позволяет по сравнению с прототипом повысить помехоустойчивость и точность синхронизации опорных сигналов.

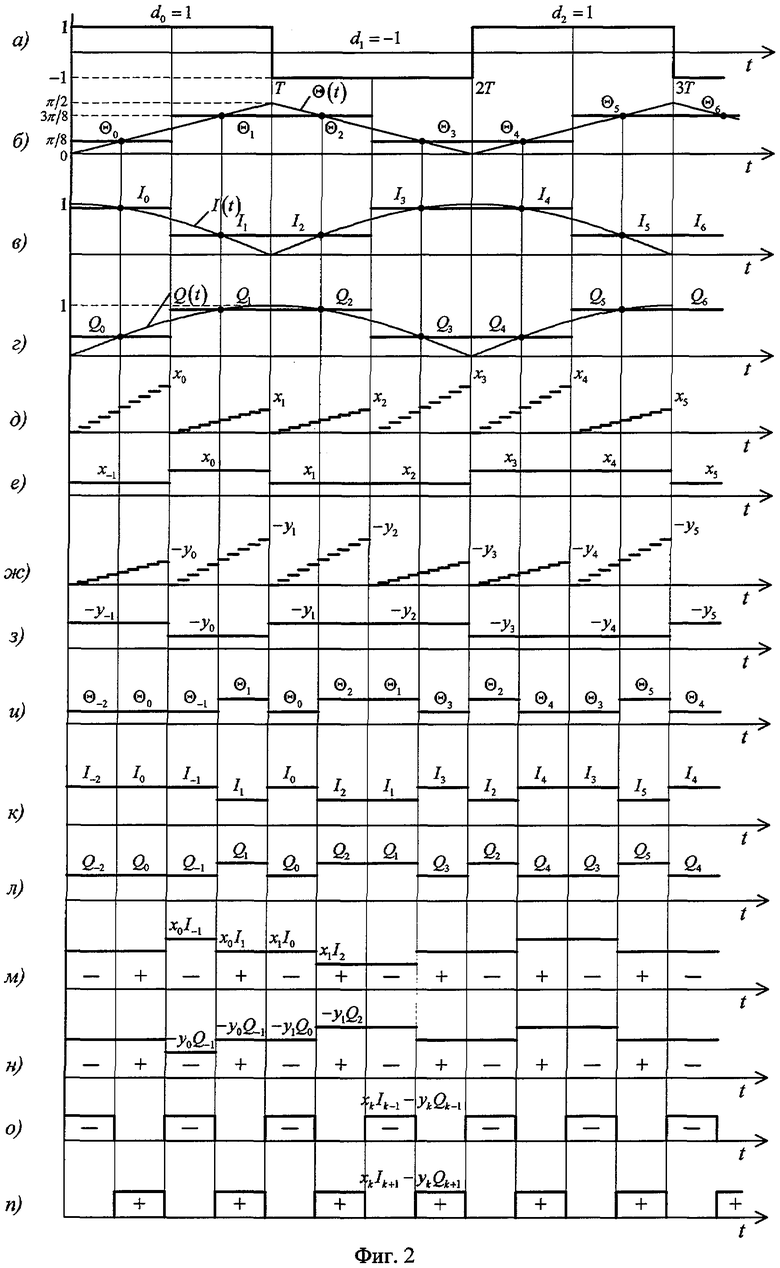

На фиг.1 приведена функциональная схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства.

Устройство слежения за задержкой шумоподобных частотно-манипулированных сигналов содержит аналого-цифровой преобразователь 1, первый 21, и второй 22 перемножители, сигнальные входы которых объединены и подключены к выходу аналого-цифрового преобразователя 1, а опорные входы - к выходу блока 3 формирования опорных сигналов. Заявляемое устройство содержит цифровой временной дискриминатор 4, включающий первый 51 и второй 52 цифровые интеграторы, соединенные соответственно с выходом первого 21 и второго 22 перемножителей, первый 61 и второй 62 оперативные запоминающие элементы, входами соединенные с выходами цифровых интеграторов 51, 52, соответственно, третий 23, четвертый 24, пятый 25, шестой 26, перемножители, при этом входы третьего и пятого перемножителей 23 и 25 соединены с выходом первого оперативного запоминающего элемента 61, входы четвертого и шестого перемножителей 24 и 26 - с выходом второго оперативного запоминающего элемента 62. В цифровом временном дискриминаторе 4 имеется вычитатель 7, входами соединенный с выходами третьего 23 и шестого 26 перемножителей, и сумматор 8, входы которого подключены к выходам четвертого 24 и пятого 25 перемножителей, первый демультиплексор 91, подключенный к выходу вычитателя 7, и второй демультиплексор 92, подключенный к выходу сумматора 8, третий 53, четвертый 54, пятый 55, шестой 56 цифровые интеграторы, подключенные соответственно 53 и 55 к выходам первого демультиплексора 91, а 54 и 56, - к выходам второго демультиплексора 92, и вычислительный блок 10, входами соединенный с выходами цифровых интеграторов 53, 54, 55, 56, а выходом - с петлевым фильтром 11, выход которого подключен к блоку 12 формирования кодовых последовательностей. Блок 12 формирования кодовых последовательностей содержит последовательно соединенные управляемый фазовращатель 13, делитель 14 частоты на два, генератор 15 псевдослучайной последовательности, аккумулятор 16 фазы, третий оперативный запоминающий элемент 63 и первый постоянный запоминающий элемент 171, а также опорный генератор 18, дешифратор 19 и второй постоянный запоминающий элемент 172, при этом опорный генератор 18 подключен ко второму входу управляемого фазовращателя 13, дешифратор 19 входами соединен с генератором 15 псевдослучайной последовательности, а выходом - с синхронизирующими входами цифровых интеграторов 53, 54, 55 и 56, второй постоянный запоминающий элемент 172 подключен к опорному входу аккумулятора 16 фазы. К выходу управляемого фазовращателя 13 подключены синхронизирующие входы аккумулятора 16 фазы, третьего оперативного запоминающего элемента 63, первого постоянного запоминающего элемента 171, а также - цифровых интеграторов 51, 52, оперативных запоминающих элементов 61, 62 и демультиплексоров 91, 92 цифрового временного дискриминатора 4. Один из выходов первого постоянного запоминающего элемента 171 соединен с опорными входами перемножителей 23, 24, другой выход - с опорными входами перемножителей 25, 26, цифрового временного дискриминатора 4, а выход генератора 15 псевдослучайной последовательности является и выходом заявляемого устройства.

Устройство работает следующим образом. Входной шумоподобный частотно-манипулированный сигнал (ШПС), преобразованный в цифровую форму, поступает на входные перемножители 21 и 22, где он перемножается с опорными гармоническими ортогональными сигналами частоты, равной средней частоте ШПС, вырабатываемыми блоком 3 формирования опорных сигналов. Квадратурные сигналы на выходах перемножителей 21 и 22 содержат низкочастотные составляющие (см. фиг.2, в, г), повторяющие по форме модулирующие кодовые последовательности и отличающиеся от них задержкой, а также - составляющие удвоенной средней частоты, которые подавляются при последующей обработке.

Временные диаграммы (см. фиг.2) приведены для установившегося режима синхронизации, когда временная расстройка принятого и опорного сигналов равна нулю (фазовая расстройка ради простоты также полагается равной нулю), где dj - элементы псевдослучайной последовательности (ПСП), определяющей закон частотной манипуляции, j=0, 1, ...; Θ(t) - закон угловой модуляции ШПС; I(t) и Q(t) - квадратурные модулирующие кодовые последовательности; хi и уi, - результаты поэлементной обработки ШПС в квадратурных каналах, i=..., -1, 0, 1, ....

В цифровых интеграторах 51 и 52 осуществляется накопление отсчетов квадратурных составляющих сигнала, поступающих с выходов перемножителей 21 и 22 соответственно (см. фиг.2, д, ж). Частота следования отсчетов определяется частотой дискретизации непрерывного сигнала в аналого-цифровом преобразователе 1, а время интегрирования равно Т/2, Т - длительность элемента ШПС, Результаты интегрирования запоминаются на время Т/2 в оперативных запоминающих элементах 61 и 62, после чего осуществляется сброс интеграторов 51 и 52 и интегрирование следующего полуэлемента ШПС длительностью Т/2. Запись результатов интегрирования в оперативные запоминающие элементы 61, 62 и сброс интеграторов 51, 52 производится с удвоенной тактовой частотой 2fT=2/Т (см. фиг.2, е, з).

В перемножителях 23, 24 и 25, 26, производится умножение результатов поэлементной обработки, хранящихся в оперативных запоминающих элементах 61 и 62 соответственно, на отсчеты опережающих и задержанных опорных квадратурных кодовых последовательностей, поступающих с выходов блока 12 формирования кодовых последовательностей поочередно (см. фиг.2, к, л). На опорные входы перемножителей 23, 24 поступают отсчеты Ik+1 и Ik-1, соответственно опережающей на Т/2 и отстающей на Т/2 кодовой последовательности относительно синхронной кодовой последовательности Ik=cosΘk, а на опорные входы перемножителей 25, 26 - отсчеты Qk+1 и Qk-1, сдвинутые на Т/2 и -Т/2 соответственно относительно отсчетов Qk=sinΘk, Θk=Θ(t=kT/2), k=0, 1, 2, .... Частота коммутации 4ƒT отсчетов опорных кодовых последовательностей в два раза превышает частоту поступления данных с выходов оперативных запоминающих элементов 61 и 62 на входы перемножителей 23, 24, 25, 26.

Сигналы с выходов перемножителей попарно объединяются в вычитателе 7 и сумматоре 8, образуя соответственно «косинусную» и «синусную» составляющие результатов поэлементной обработки ШПС, которые поступают на входы демультиплексоров 91 и 92 (см. фиг.2, м, н). На управляющие входы демультиплексоров подается сигнал частоты коммутации 4fT, обеспечивая синхронную работу демультиплексоров и блока 12 формирования кодовых последовательностей, благодаря чему к выходам вычитателя 7 и сумматора 8 подключаются цифровые интеграторы 53 и 54 «опережающего» канала дискриминатора, когда на опорные входы перемножителей 23, 24 и 25, 26 подаются отсчеты опережающих квадратурных кодовых последовательностей, или цифровые интеграторы 55, 56 «задержанного» канала, если на опорные входы перемножителей подаются отсчеты задержанных квадратурных кодовых последовательностей (см. фиг.2, о, n).

Цифровые интеграторы 53, 54, 55, 56 осуществляют когерентное накопление на интервале, равном периоду ТП повторения ШПС, соответствующих квадратурных составляющих результатов поэлементной обработки ШПС в «опережающем» и «задержанном» каналах дискриминатора. Результаты интегрирования за ТП поступают с выходов интеграторов 53, 54, 55, 56 в вычислительный блок 10, где осуществляется формирование сигнала ошибки путем сравнения квадратов модулей выходных сигналов «опережающего» и «задержанного» каналов: Z∂=Z2(1)-Z2(-1),

где ZI(±1) и ZQ(±1) - квадратурные составляющие выходных сигналов «опережающего» канала (аргумент 1) и «задержанного» канала (аргумент -1) для цифровых интеграторов 53, 54 и 55, 56 соответственно. Сигнал ошибки Z∂, величина и знак которого определяются значением относительной задержки принятого и опорного ШПС, поступает на петлевой фильтр 11, после чего производится сброс цифровых интеграторов 53, 54, 55, 56 синхронизирующим сигналом, вырабатываемым блоком 12 формирования кодовых последовательностей, и процесс формирования сигнала ошибки повторяется на следующем шаге с периодичностью ТП.

Блок 12 формирования кодовых последовательностей работает следующим образом. Опорный генератор 18 вырабатывает меандровый сигнал частоты 2fТ, который подается на вход управляемого фазовращателя 13. Формирование тактовых импульсов для генератора 15 псевдослучайной последовательности производится делителем 14 частоты на два. Управление задержкой ПСП осуществляется кодом, подаваемым на управляющий вход фазовращателя 13 с выхода петлевого фильтра 11. Формируемая генератором 15 ПСП (см. фиг.2, а) поступает на управляющий вход аккумулятора 16 фазы, определяя знак приращения фазы π/4, хранящегося во втором постоянном запоминающем элементе 172. Отсчеты фазы, взятые с частотой дискретизации 2fТ, хранятся в третьем оперативном запоминающем элементе 63 в течение интервала Т (см. фиг.2, б). Отсчеты квадратурных опорных кодовых последовательностей (см. фиг.2, в, г) формируются табличным способом с помощью первого постоянного запоминающего элемента 171, адреса отсчетов определяются значениями фазы, хранящимися в третьем оперативном запоминающем элементе 63. С выходов элемента 171 отсчеты квадратурных кодовых последовательностей (см. фиг.2, к, л) поступают на опорные входы перемножителей 23, 24 и 25, 26 цифрового временного дискриминатора 4. Дешифратор 19, подключенный к генератору 15 ПСП, формирует синхронизирующий сигнал частоты FП=1/ТП для цифровых интеграторов 53, 54, 55, 56 цифрового временного дискриминатора 4.

Предлагаемое устройство позволяет повысить помехоустойчивость и точность кодовой синхронизации приемника шумоподобных частотно-манипулированных сигналов с непрерывной фазой.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2548010C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2008 |

|

RU2374776C2 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЧАСТОТОЙ ШУМОПОДОБНЫХ СИГНАЛОВ | 2007 |

|

RU2325041C1 |

| КОРРЕЛЯЦИОННЫЙ ПРИЕМНИК ШУМОПОДОБНЫХ СИГНАЛОВ | 2010 |

|

RU2431919C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2357359C2 |

| СПОСОБ ПРИЕМА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2006 |

|

RU2307474C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| СПОСОБ ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2353064C1 |

Изобретение относится к радиотехнике и может использоваться в приемниках шумоподобных частотно-манипулированных сигналов с непрерывной фазой. Технический результат - повышение помехоустойчивости и точности синхронизации опорных сигналов. Устройство содержит два перемножителя, формирователь опорных сигналов, цифровой временной дискриминатор, петлевой фильтр и блок формирования кодовых последовательностей, который содержит два постоянных запоминающих элемента, управляемый фазовращатель, делитель частоты на два, генератор псевдослучайной последовательности, аккумулятор фазы, оперативный запоминающий элемент, опорный генератор, дешифратор, при этом цифровой временной дискриминатор содержит шесть цифровых интеграторов, два оперативных запоминающих элемента, четыре перемножителя, сумматор, вычитатель, два демультиплексора, вычислительный блок. 2 ил.

Устройство слежения за задержкой шумоподобных частотно-манипулированных сигналов, содержащее блок формирования опорных сигналов, соответствующие выходы которого соединены с опорными входами первого и второго перемножителей, сигнальные входы которых объединены, а выходы которых подключены к цифровому временному дискриминатору, содержащему первый и второй цифровые интеграторы и вычислительный блок, последовательно соединенные петлевой фильтр и блок формирования кодовых последовательностей, который содержит управляемый фазовращатель, опорный генератор и генератор псевдослучайной последовательности, при этом выход вычислительного блока подключен к петлевому фильтру, а на управляющий вход управляемого фазовращателя подается код с выхода петлевого фильтра, отличающееся тем, что в цифровой временной дискриминатор введены первый и второй оперативные запоминающие элементы, подключенные соответственно к выходу первого и второго цифровых интеграторов и объединенные по синхронизирующему входу друг с другом, а также с первым и вторым цифровыми интеграторами, третий, четвертый, пятый и шестой перемножители, вычитатель и сумматор, при этом к выходу первого оперативного запоминающего элемента подключены третий и пятый перемножители, к выходу второго оперативного запоминающего элемента - четвертый и шестой перемножители, причем выходы третьего и шестого, четвертого и пятого перемножителей попарно объединены через вычитатель и сумматор соответственно, первый и второй демультиплексоры, подключенные к вычитателю и сумматору соответственно, третий, четвертый, пятый и шестой цифровые интеграторы, причем к выходам первого демультиплексора подключены третий и пятый цифровые интеграторы, а к выходам второго демультиплексора - четвертый и шестой цифровые интеграторы, выходы которых подключены к вычислительному блоку, в блок формирования кодовых последовательностей введены делитель частоты на два, вход которого подключен к выходу управляемого фазовращателя, дешифратор, входы которого подключены к соответствующим выходам генератора псевдослучайной последовательности, последовательно соединенные аккумулятор фазы, третий оперативный запоминающий элемент и первый постоянный запоминающий элемент, второй постоянный запоминающий элемент, который подключен к опорному входу аккумулятора фазы, при этом управляющий вход аккумулятора фазы подключен к выходу генератора псевдослучайной последовательности, синхронизирующие входы первого постоянного запоминающего элемента, третьего оперативного запоминающего элемента и аккумулятора фазы соединены и подключены к выходу управляемого фазовращателя и к синхронизирующим входам первого и второго цифровых интеграторов, первого и второго оперативных запоминающих элементов и первого и второго демультиплексоров цифрового временного дискриминатора, вход генератора псевдослучайной последовательности подключен к выходу делителя частоты на два, выход дешифратора соединен с синхронизирующими входами третьего, четвертого, пятого и шестого цифровых интеграторов цифрового временного дискриминатора, соответствующие выходы первого постоянного запоминающего элемента соединены с опорными входами третьего, четвертого и пятого, шестого перемножителей цифрового временного дискриминатора, вычислительный блок осуществляет формирование сигнала ошибки путем сравнения квадратов модулей опережающего и задержанного сигналов, поступающих с выходов соответствующих цифровых интеграторов, при этом величина и знак сигнала ошибки определяются значением относительной задержки принятого и опорного сигналов, а выходом устройства является выход генератора псевдослучайной последовательности.

| Шебшаевич B.C | |||

| и др | |||

| /Под ред | |||

| В.С.Шебшаевича | |||

| Сетевые спутниковые радионавигационные системы | |||

| - М.: Радио и связь, 1982, с.98 | |||

| RU 2000666 С, 07.09.1993 | |||

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1991 |

|

RU2040858C1 |

| EP 1484855 A1, 08.12.2004 | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

Авторы

Даты

2007-12-20—Публикация

2006-04-12—Подача