Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например, операционных усилителях, драйверов линий связи.

Известны схемы двухтактных выходных каскадов на n-р-n и р-n-р транзисторах (буферных усилителей (БУ)), которые стали одним из базовых элементов многих аналоговых микросхем, широко используются в структуре различных УНЧ и операционных усилителях как в выходных, так и во входных цепях. Благодаря хорошим статическим и другим характеристикам такие БУ получили специальное название «бриллиантовые» транзисторы. Они выпускаются как в виде самостоятельных микросхем (BUF1, BUF600, LMH6321 и др.), так и в составе различных мостовых, входных и двухтактных выходных каскадов аналоговых устройств [1-24].

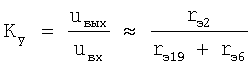

Ближайшим прототипом (фиг.1) заявляемого устройства является буферный усилитель, описанный в патенте США №5.557.238, содержащий первый n-р-n 1 и второй р-n-р 2 входные транзисторы, с объединенными базами, связанными со входом 3 устройства, причем эмиттер первого 1 входного n-р-n транзистора соединен с коллектором первого 4 вспомогательного n-р-n транзистора и базой первого 5 выходного р-n-р транзистора, эмиттер второго 2 входного р-n-р транзистора соединен с коллектором второго 6 вспомогательного р-n-р транзистора и базой второго выходного n-р-n транзистора 7, а эмиттеры первого 5 и второго 7 выходных транзисторов связаны с нагрузкой 8, эмиттер первого 4 вспомогательного n-р-n транзистора связан с шиной первого 9 источника питания через первый дополнительный резистор 10, а база соединена с первым 11 источником напряжения смещения, эмиттер второго 6 вспомогательного р-n-р транзистора связан с шиной второго 12 источника питания через второй 13 дополнительный двухполюсник, а база соединена со вторым 14 источником напряжения смещения.

Существенный недостаток известного устройства состоит в том, что оно имеет большое время установления переходного процесса (tф) при работе с быстроизменяющимися импульсными сигналами большой амплитуды, а также невысокие значения максимальной скорости нарастания выходного напряжения (ϑвых).

Основная цель предполагаемого изобретения состоит в повышении быстродействия буферного усилителя - уменьшении в 20÷30 раз времени установления переходного процесса (tф) для заданной зоны динамической ошибки ε0=10%, и увеличения максимальной скорости нарастания выходного напряжения ϑвых=20÷30 раз.

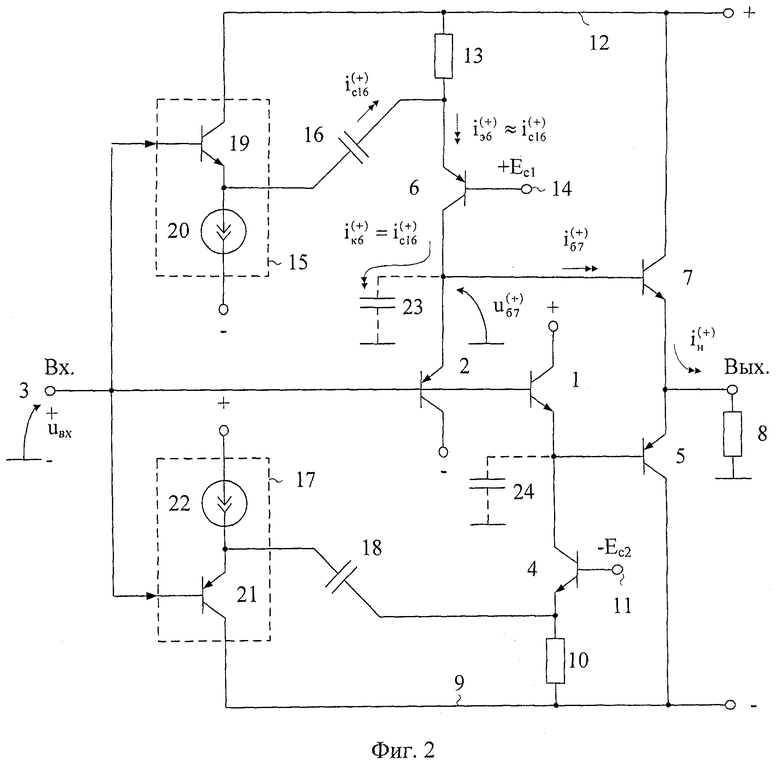

Поставленная цель достигается тем, что в буферном усилителе фиг.1, содержащем первый n-р-n 1 и второй р-n-р 2 входные транзисторы, с объединенными базами, связанными со входом 3 устройства, причем эмиттер первого 1 входного n-р-n транзистора соединен с коллектором первого 4 вспомогательного n-р-n транзистора и базой первого 5 выходного р-n-р транзистора, эмиттер второго 2 входного р-n-р транзистора соединен с коллектором второго 6 вспомогательного р-n-р транзистора и базой второго выходного n-р-n транзистора 7, а эмиттеры первого 5 и второго 7 выходных транзисторов связаны с нагрузкой 8, эмиттер первого 4 вспомогательного n-р-n транзистора связан с шиной первого 9 источника питания через первый дополнительный резистор 10, а база соединена с первым 11 источником напряжения смещения, эмиттер второго 6 вспомогательного р-n-р транзистора связан с шиной второго 12 источника питания через второй 13 дополнительный двухполюсник, а база соединена со вторым 14 источником напряжения смещения, предусмотрены новые элементы и связи - в схему введены первый 15 эмиттерный повторитель напряжения на n-р-n транзисторе, причем вход устройства 3 связан со входом первого 15 эмиттерного повторителя напряжения на n-р-n транзисторе, а выход данного повторителя напряжения 15 через первый 16 дополнительный конденсатор связан с эмиттером второго 6 вспомогательного транзистора, второй 17 эмиттерный повторитель напряжения на р-n-р транзисторе, причем вход 3 устройства связан со входом второго 17 повторителя напряжения на р-n-р транзисторе, а выход данного повторителя напряжения 17 через второй 18 дополнительный конденсатор связан с эмиттером первого 4 вспомогательного транзистора.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения приведена на фиг.2.

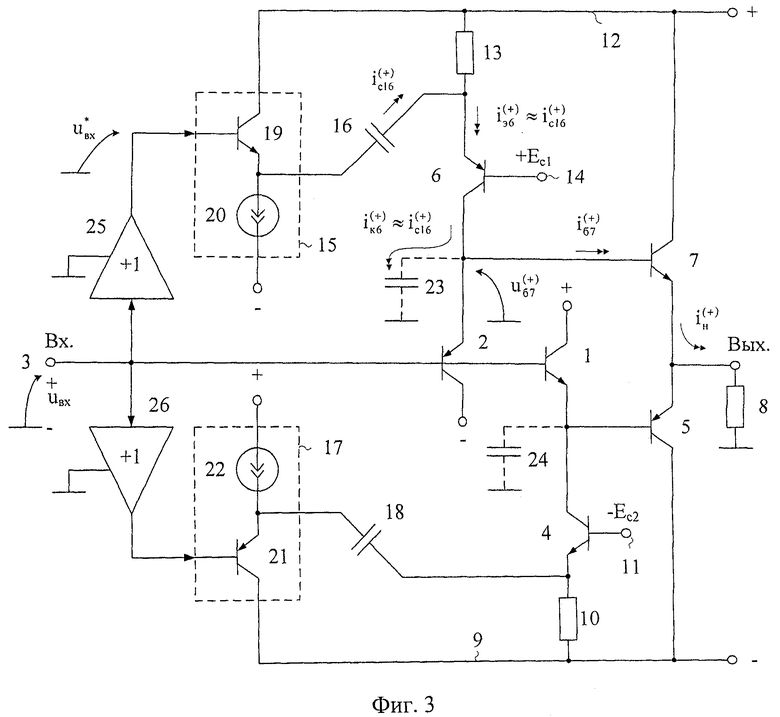

На фиг.3 показан заявляемый БУ в соответствии с п.2 формулы изобретения.

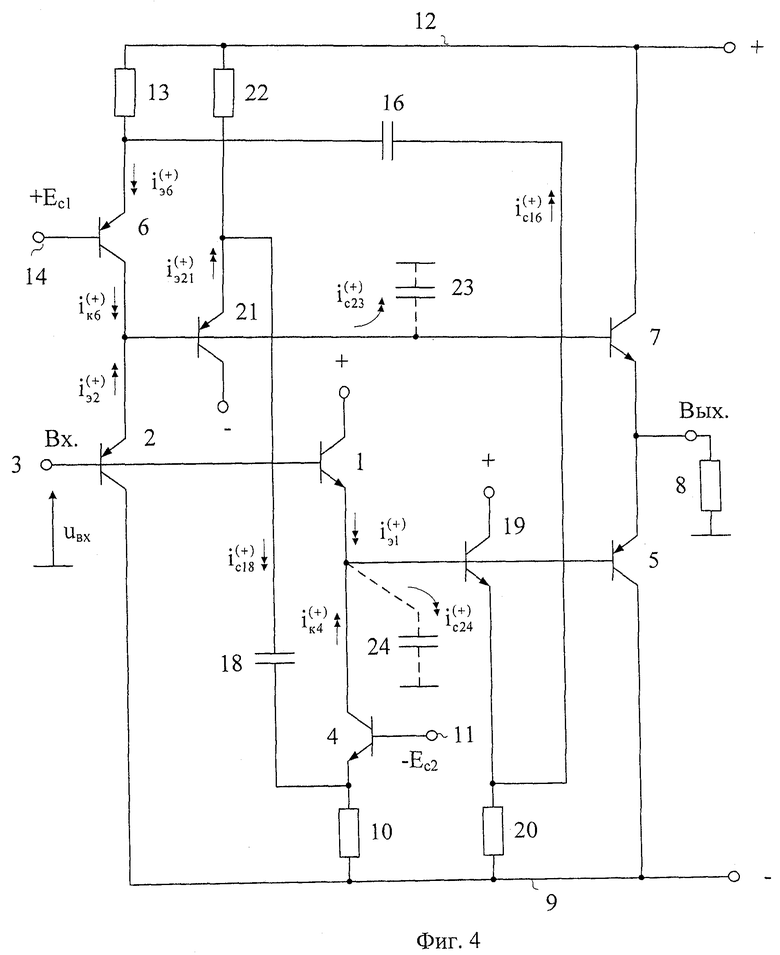

На фиг.4 показан частный случай БУ фиг.3.

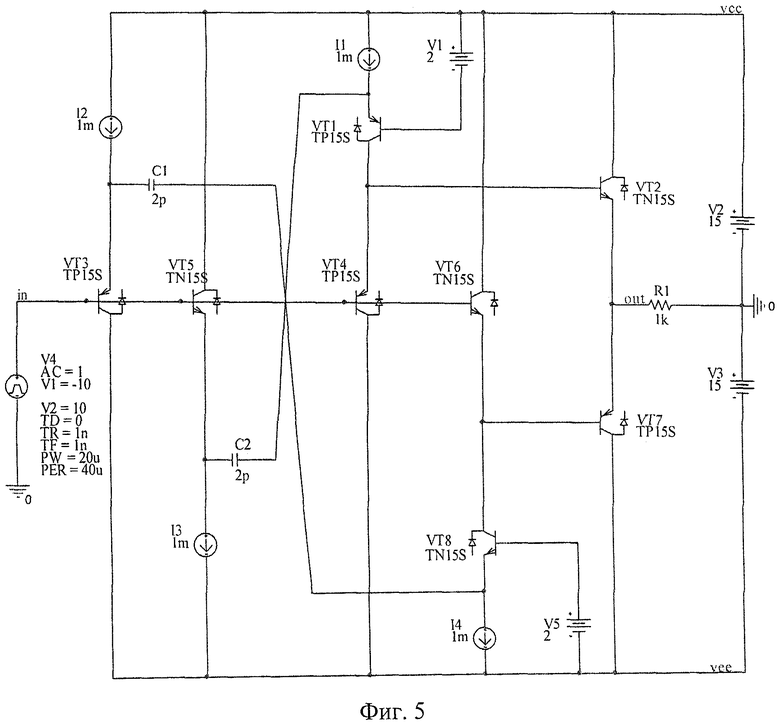

На фиг.5 приведена схема фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

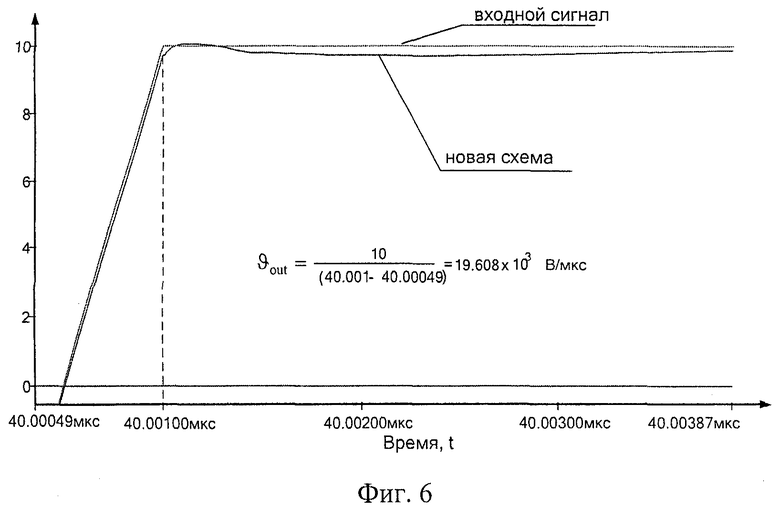

На фиг.6 показан нарастающий переходный процесс на выходе заявляемого устройства при емкостях дополнительных конденсаторов 16 и 18 C16=C18=2 пФ, полученный в результате компьютерного моделирования схемы фиг.5. Максимальная скорость нарастания выходного напряжения на фиг.6 - 19,6·103 В/мкс.

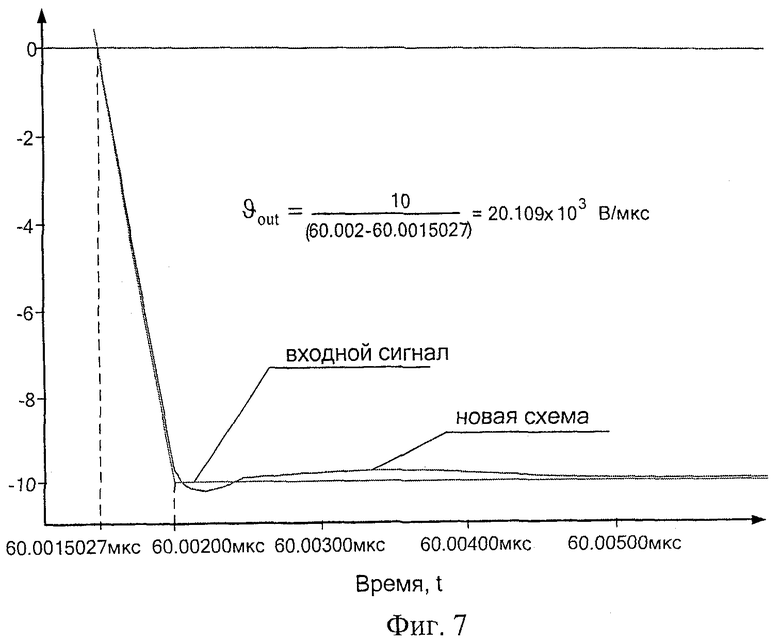

На фиг.7 показан спадающий фронт переходного процесса в заявляемом устройстве. Максимальная скорость нарастания выходного напряжения на фиг.7 - 20,1·103 В/мкс.

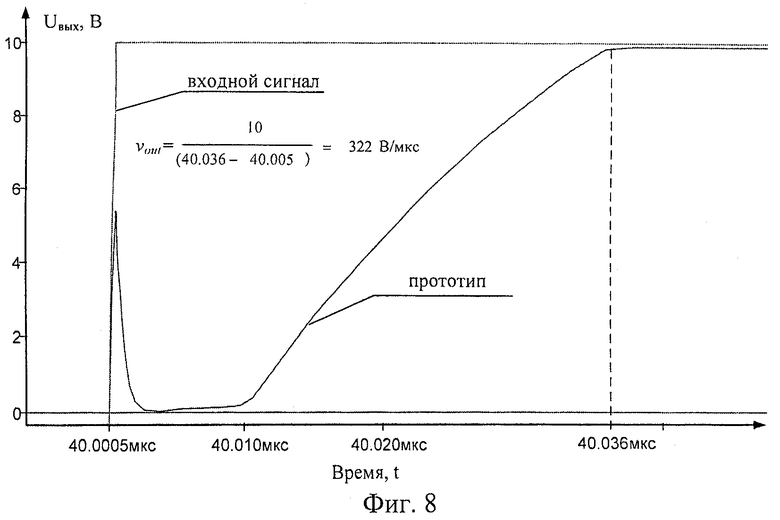

На фиг.8 показан нарастающий переходный процесс на выходе БУ-прототипа, полученный в результате компьютерного моделирования схемы фиг.5 при C1=C2=0. Максимальная скорость нарастания выходного напряжения 322 В/мкс.

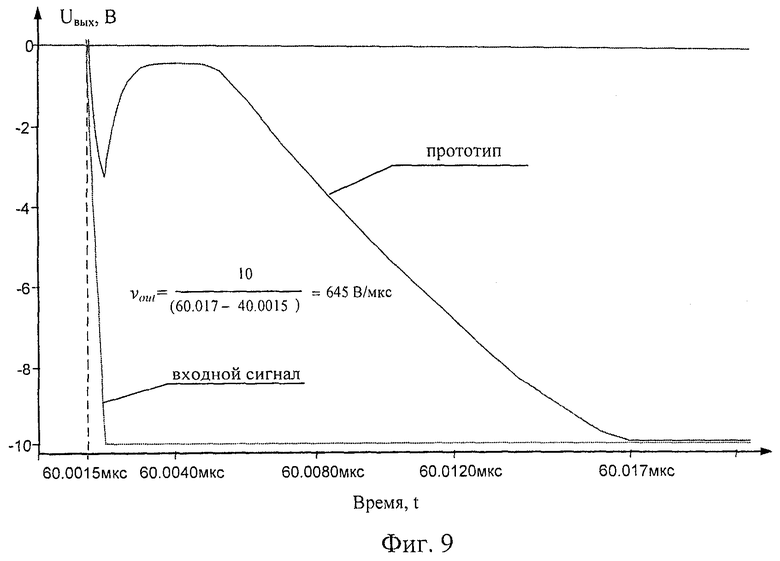

На фиг.9 показан спадающий фронт переходного процесса на выходе БУ-прототипа, полученный в результате компьютерного моделирования схемы фиг.5 при С1=С2=0. Максимальная скорость нарастания выходного напряжения 645 В/мкс.

Представленные результаты компьютерного моделирования фиг.4-7, которые показывают, что заявляемое устройство имеет (в сравнении с прототипом) в 20-30 раз большую среднюю скорость нарастания выходного напряжения и в значительно меньшее время установления переходного процесса.

Буферный усилитель фиг.2 содержит первый n-р-n 1 и второй р-n-р 2 входные транзисторы, с объединенными базами, связанными со входом 3 устройства, причем эмиттер первого 1 входного n-р-n транзистора соединен с коллектором первого 4 вспомогательного n-р-n транзистора и базой первого 5 выходного р-n-р транзистора, эмиттер второго 2 входного р-n-р транзистора соединен с коллектором второго 6 вспомогательного р-n-р транзистора и базой второго выходного n-р-n транзистора 7, а эмиттеры первого 5 и второго 7 выходных транзисторов связаны с нагрузкой 8, эмиттер первого 4 вспомогательного n-р-n транзистора связан с шиной первого 9 источника питания через первый дополнительный резистор 10, а база соединена с первым 11 источником напряжения смещения, эмиттер второго 6 вспомогательного р-n-р транзистора связан с шиной второго 12 источника питания через второй 13 дополнительный двухполюсник, а база соединена со вторым 14 источником напряжения смещения. В схему введены первый 15 эмиттерный повторитель напряжения на n-р-n транзисторе, причем вход устройства 3 связан со входом первого 15 эмиттерного повторителя напряжения на n-р-n транзисторе, а выход данного повторителя напряжения 15 через первый 16 дополнительный конденсатор связан с эмиттером второго 6 вспомогательного транзистора, второй 17 эмиттерный повторитель напряжения на р-n-р транзисторе, причем вход 3 устройства связан со входом второго 17 повторителя напряжения на р-n-р транзисторе, а выход данного повторителя напряжения 17 через второй 18 дополнительный конденсатор связан с эмиттером первого 4 вспомогательного транзистора. Емкости в базовой цепи транзисторов 7 и 5 моделируются на схеме фиг.2 конденсаторами 23 и 24.

В схеме фиг.3, в соответствии с п.2 формулы изобретения, вход 3 устройства связан со входами первого 15 и второго 17 эмиттерных повторителей напряжения через первый 25 и второй 26 дополнительные эмиттерные повторители на основе соответствующих n-р-n 25 и р-n-р 26 транзисторов.

В схеме фиг.4, в соответствии с п.2 формулы изобретения, в качестве первого 25 и второго 26 дополнительных эмиттерных повторителей используются эмиттерные повторители на базе первого n-р-n 1 и второго р-n-р 2 входных транзисторов.

Рассмотрим работу заявляемого устройства фиг.2.

В статическом режиме эмиттерные токи транзисторов 1 и 2 равны коллекторным токам транзисторов 4 и 6. Их численные значения определяются двухполюсниками 13 и 10, а также источниками Ec1 и Ес2.

Если на вход БУ подается импульс положительного входного напряжения, близкий к напряжению питания, то это вызывает практически мгновенное запирание транзистора 2. При этом входной импульс поступает также на вход эмиттерного повторителя 15 и через емкость 16 передается в эмиттер транзистора 6, создавая "скачок" тока коллектора транзистора 6. Это вызывает быстрый перезаряд суммарной эквивалентной емкости (C23) в эмиттерной цепи транзистора 2. Данная емкость складывается из емкостей коллектор-база транзисторов 6 и 7, а также их емкости на подложку. Типовые значения С23=С24=1÷3 пФ (для микронных технологий).

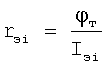

Большое значение для эффективной работы БУ с небольшими импульсными сигналами имеет выбор статического режима транзисторов 19, 6 и 2, так как он оказывает существенное влияние на малосигнальный коэффициент передачи (Ку) входного напряжения uвх на выход БУ:

,

,

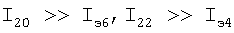

где  - дифференциальное сопротивление эмиттерного перехода i-го транзистора при статическом токе эмиттера Iэi.

- дифференциальное сопротивление эмиттерного перехода i-го транзистора при статическом токе эмиттера Iэi.

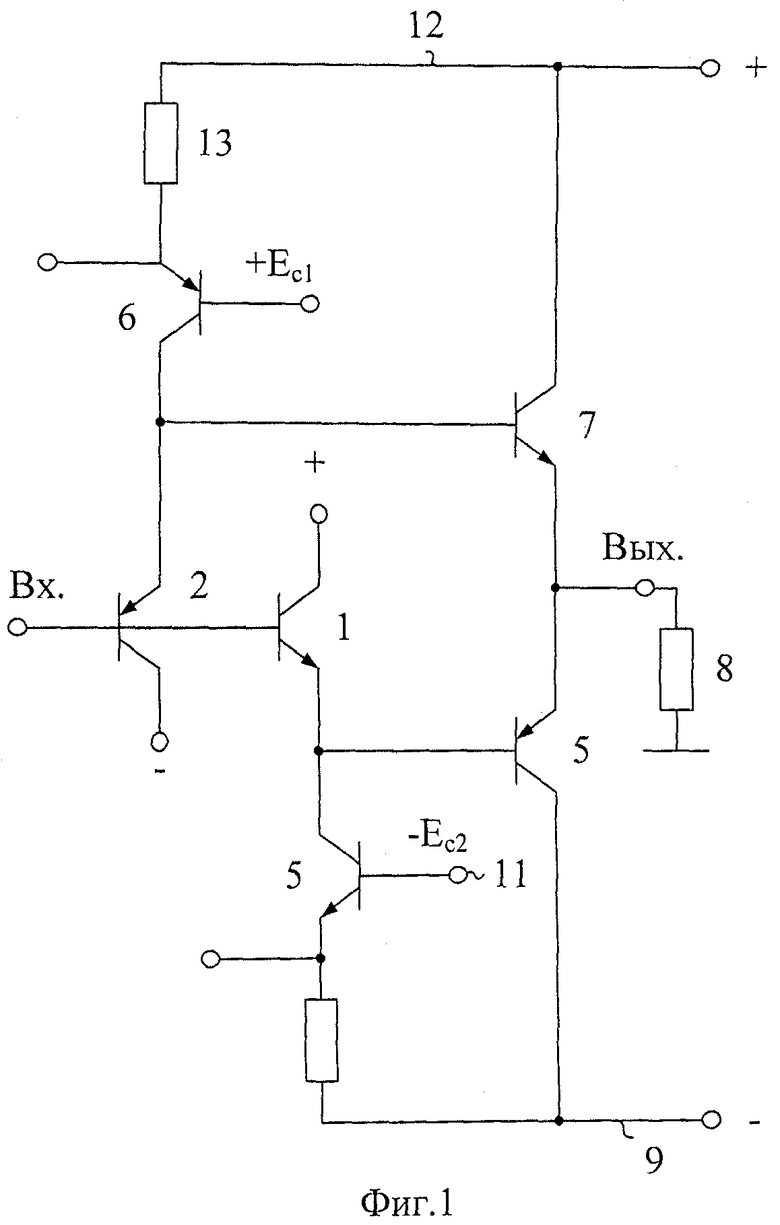

Для «выравнивания» коэффициентов передачи в области низких и высоких частот необходимо обеспечить Ку≈1, то есть выбрать:

,

,

или установить в эмиттерной цепи транзисторов 2, 4, 7, 5 дополнительные p-n переходы (на фиг.2 они не показаны).

Как показывает компьютерное моделирование схем фиг.5, форсирование тока перезаряда паразитной емкости С23 повышает быстродействие БУ в 20÷30 раз. При этом данный эффект обеспечивается без ухудшения стабильности его статического режима БУ.

Применение схемы БУ фиг.4 обеспечивает повышение быстродействия без увеличения входной емкости БУ.

Источники информации

1. Патент США №5.557.238, fig.6.

2. Патент США №5.479.133 fig.1.

3. Патент ЕР 0716502.

4. Патент ЕР 0786858.

5. Патент Японии JP 11251846.

6. Патент США №4.639.685.

7. Патент США №5.323.122.

8. Патент США №5.963.065.

9. Патент США №6.420.933.

10. Патент США №5.515.007.

11. Патент США №4.502.020, fig.3.

12. Патентная заявка US 2006/0186958, fig.3.

13. Патентная заявка US 2005/0264358.

14. Патентная заявка US 2004/0263252, fig.3.

15. Патентная заявка US 2004/019101.

16. Патентная заявка US 2003/0102921, fig.l.

17. Патентная заявка US 2002/0121934.

18. Патентная заявка US 2007/0159255.

19. Патентная заявка 5.179.355.

20. Патентная заявка 5.049.653.

21. Патентная заявка 4.837.523.

22. Патент РФ 1.160.530.

23. Патентная заявка 5.374.897.

24. Новый 30-вольтный буферный усилитель фирмы National gemiconductor LMN 6321. Новости электроники, №8, 2006. стр.8 (vвых=1800 в/мкс).

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2401507C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| КОМПЛЕМЕНТАРНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2444115C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2368066C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374757C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419186C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2412528C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКООМНЫМИ ВХОДАМИ | 2008 |

|

RU2383099C2 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного устройства для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя - БУ), в структуре входных каскадов аналоговых микросхем различного функционального назначения, например, операционных усилителях, драйверов линий связи. Технический результат: повышение быстродействия. БУ содержит первый n-p-n (1) и второй p-n-p (2) входные транзисторы (Т) с объединенными базами, связанными со входом (3) БУ, причем эмиттер Т (1) соединен с коллектором первого (4) вспомогательного n-p-n Т и базой первого (5) выходного p-n-p Т, эмиттер Т (2) соединен с коллектором второго (6) вспомогательного p-n-p Т и базой второго (7) выходного n-p-n Т, а эмиттеры Т (5) и Т (7) связаны с нагрузкой (8); эмиттер Т (4) связан с шиной первого (9) источника питания (ИП) через первый дополнительный двухполюсник (10), а база соединена с первым (11) источником напряжения смещения (ИНС), эмиттер Т (6) связан с шиной второго (12) ИП через второй (13) дополнительный двухполюсник, а база Т (6) соединена с ИНС (14). В схему введены первый (15) эмиттерный повторитель (ЭП) напряжения на n-p-n Т, причем вход (3) БУ связан со входом ЭП (15), а выход ЭП (15) - через первый (16) дополнительный конденсатор (К) связан с эмиттером Т (6); второй (17) ЭП на p-n-p Т, причем вход (3) БУ связан со входом второго (17) ЭП, а выход ЭП (17) - через второй (18) дополнительный К связан с эмиттером Т (4). 2 з.п. ф-лы, 9 ил.

1. Быстродействующий буферный усилитель (6), содержащий первый n-p-n (1) и второй p-n-p (2) входные транзисторы с объединенными базами, связанными со входом (3) устройства, причем эмиттер первого (1) входного n-p-n транзистора соединен с коллектором первого (4) вспомогательного n-p-n транзистора и базой первого (5) выходного p-n-p транзистора, эмиттер второго (2) входного p-n-p транзистора соединен с коллектором второго (6) вспомогательного p-n-p транзистора и базой второго выходного n-p-n транзистора (7), а эмиттеры первого (5) и второго (7) выходных транзисторов связаны с нагрузкой (8), эмиттер первого (4) вспомогательного n-p-n транзистора связан с шиной первого (9) источника питания через первый дополнительный двухполюсник (10), а база соединена с первым (11) источником напряжения смещения, эмиттер второго (6) вспомогательного p-n-p транзистора связан с шиной второго (12) источника питания через второй (13) дополнительный двухполюсник, а база соединена со вторым (14) источником напряжения смещения, отличающийся тем, что в схему введены первый (15) эмиттерный повторитель напряжения на n-p-n транзисторе, причем вход устройства (3) связан со входом первого (15) эмиттерного повторителя напряжения на n-p-n транзисторе, а выход данного повторителя напряжения (15) через первый (16) дополнительный конденсатор связан с эмиттером второго (6) вспомогательного транзистора, второй (17) эмиттерный повторитель напряжения на p-n-p транзисторе, причем вход (3) устройства связан со входом второго (17) повторителя напряжения на p-n-p транзисторе, а выход данного повторителя напряжения (17) через второй (18) дополнительный конденсатор связан с эмиттером первого (4) вспомогательного транзистора.

2. Устройство по п.1, отличающееся тем, что вход (3) устройства связан со входами первого (15) и второго (17) эмиттерных повторителей напряжения через первый (25) и второй (26) дополнительные эмиттерные повторители на основе n-p-n (25) и p-n-p (26) транзисторов.

3. Устройство по п.2, отличающееся тем, что в качестве первого (25) и второго (26) дополнительных эмиттерных повторителей используются эмиттерные повторители на базе первого n-p-n (1) и второго p-n-p (2) входных транзисторов.

| ПОВТОРИТЕЛЬ НАПРЯЖЕНИЯ | 2000 |

|

RU2168263C1 |

| US 5578967 A, 26.11.1996 | |||

| US 5557238 A, 17.09.1996 | |||

| US 4827223 A, 02.05.1989. | |||

Авторы

Даты

2010-05-27—Публикация

2009-03-24—Подача