Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных и выходных усилителей мощности различных аналоговых устройств (операционных усилителей, драйверов линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем микроэлектронных двухтактных буферных усилителей (БУ), которые реализуются на комплементарных биполярных (BJT) или полевых (КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-29]. Благодаря высокой симметрии, простоте и малому напряжению смещения нуля вышеназванные схемотехнические решения БУ наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-29].

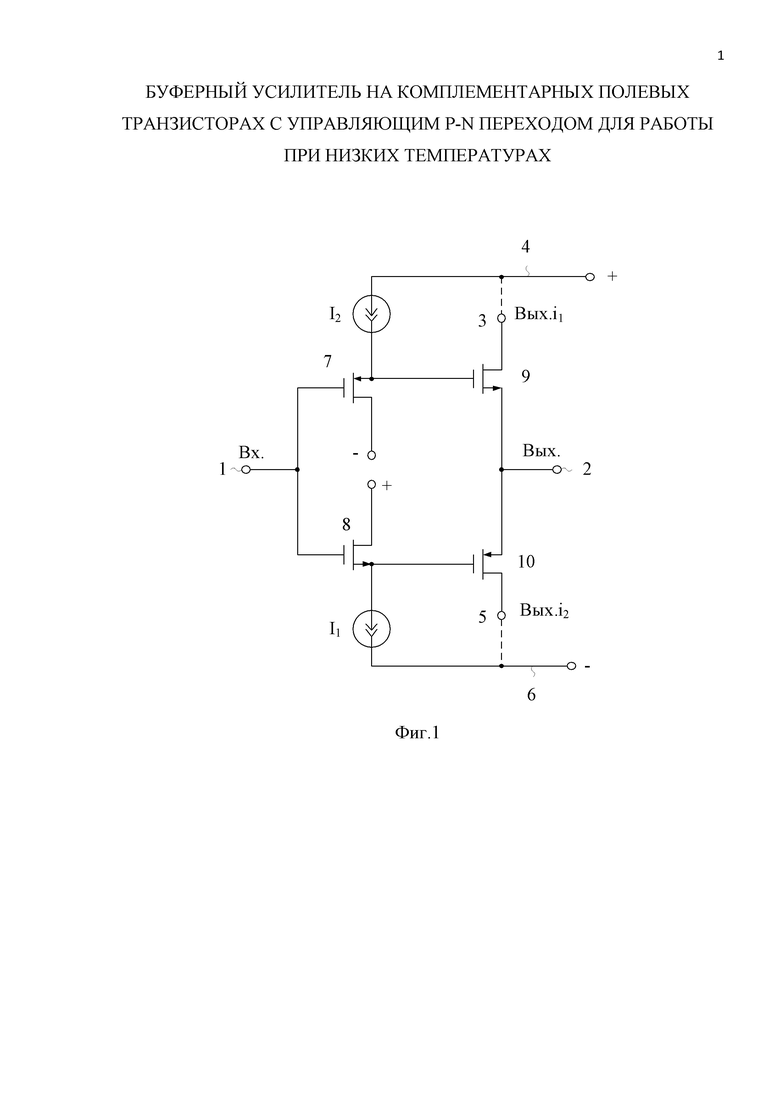

Ближайшим прототипом заявляемого устройства является буферный усилитель на комплементарных полевых транзисторах, представленный в патенте US № 7.764.123, fig. 3, 2010 г. Данная схема рассмотрена и в других патентах (US № 5.351.012, 1994 г.; US № 6.215.357 fig. 3, 2001 г.; US № 5.973.534), а также в ряде публикаций, например [28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347]. Схема БУ-прототипа фиг. 1 содержит потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, а сток соединен со вторым 5 токовым выходом устройства. БУ-прототип является основой различных входных и выходных каскадов ОУ с потенциальной отрицательной обратной связью [29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154], а также ОУ с токовой отрицательной обратной связью [28,29]. Кроме этого, данный БУ выпускается многими фирмами в виде серийных микросхем.

Существенный недостаток известного буферного усилителя состоит в том, что статический режим транзисторов его схемы определяется двумя независимыми источниками опорного тока (I1, I2, фиг. 1). Это отрицательно сказывается на работе БУ в условиях низких температур, а также затрудняет управление нагрузочной способностью БУ при изменении сопротивления его нагрузки в широких пределах. В практических схемах БУ (фиг. 1) высококачественные источники опорного тока I1, I2, существенно влияющие на параметры БУ, выполняются по достаточно сложным транзисторным схемам, что отрицательно влияет на общее энергопотребление. Таким образом, схема БУ-прототипа имеет ограниченное применение.

Основная задача предполагаемого изобретения состоит в создании радиационно-стойкого и низкотемпературного схемотехнического решения БУ на комплементарных полевых транзисторах, обеспечивающего (при высокой линейности амплитудной характеристики) повышенную стабильность статического режима транзисторов и низкий уровень шумов, в том числе при работе в диапазоне низких температур.

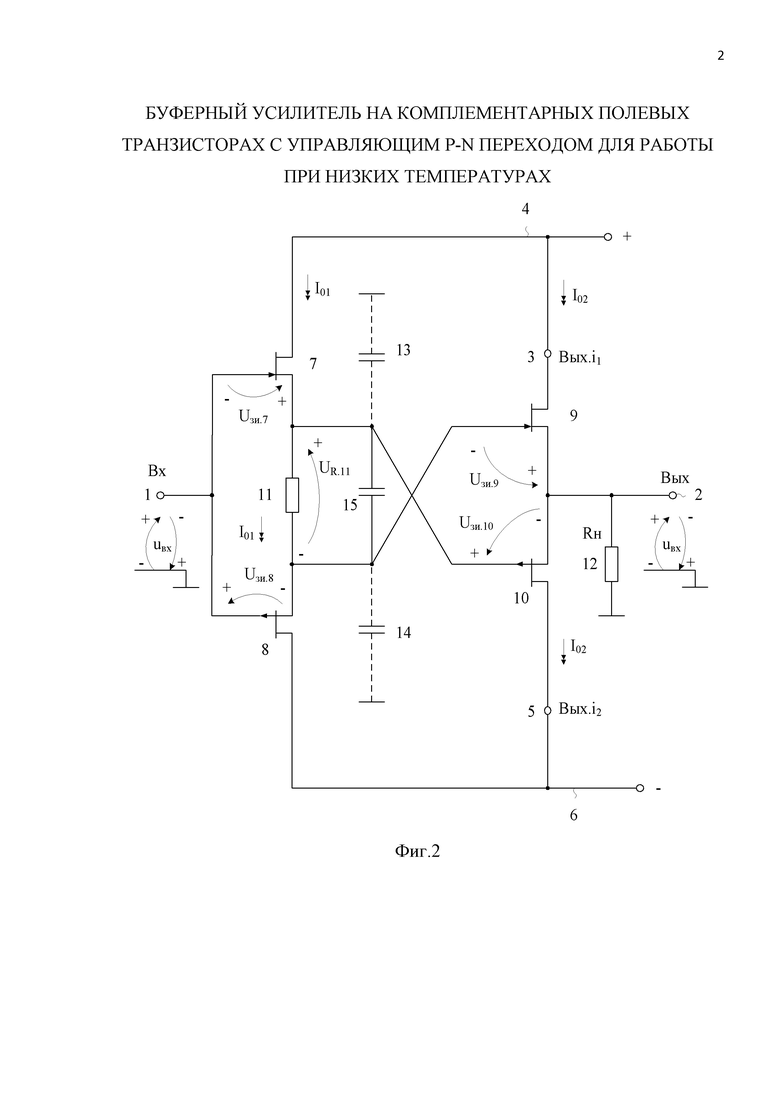

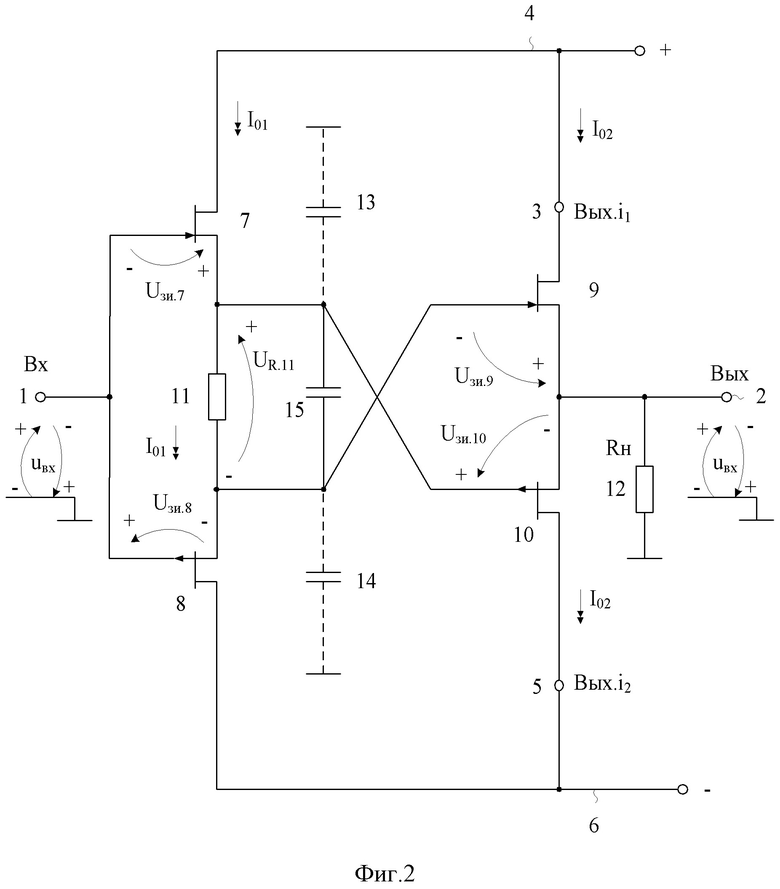

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, а сток соединен со вторым 5 токовым выходом устройства, предусмотрены новые элементы и связи – в качестве полевых транзисторов схемы БУ применены полевые транзисторы с управляющим p-n переходом, между истоками первого 7 и второго 8 входных полевых транзисторов включен токостабилизирующий двухполюсник 11, сток первого 7 входного полевого транзистора связан с первой 4 шиной источника питания, сток второго 8 входного полевого транзистора связан со второй 6 шиной источника питания, затвор первого 9 выходного полевого транзистора подключен к истоку второго 8 входного полевого транзистора, а затвор второго 10 выходного полевого транзистора подключен к истоку первого 7 входного полевого транзистора.

В схеме фиг. 2 к потенциальному выходу 2 может подключаться нагрузка 12. Конденсаторы 13 и 14 моделируют паразитные емкости в цепи затворов первого 9 и второго 10 выходных транзисторов.

В соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства соединен с первой 4 шиной источника питания, а второй 5 токовый выход устройств соединен со второй 6 шиной источника питания.

В соответствии с п. 3 формулы изобретения, параллельно токостабилизирующему двухполюснику 11 включен корректирующий конденсатор 15, который уменьшает влияние паразитных конденсаторов 13 и 14 на быстродействие БУ в режиме большого сигнала.

На чертеже фиг. 1 представлена схема БУ-прототипа, а на чертеже фиг. 2 – схема заявляемого буферного усилителя в соответствии с п.1, п.2, п.3 формулы изобретения.

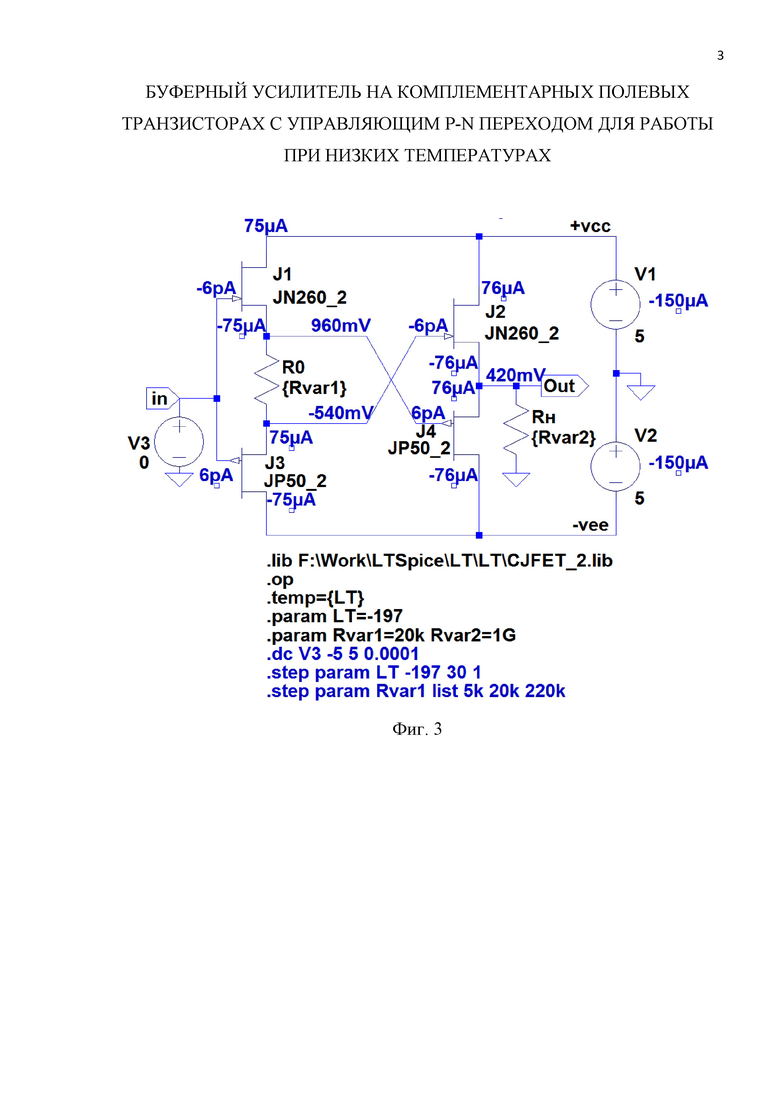

На чертеже фиг. 3 приведен статический режим схемы БУ фиг. 2 в среде моделирования LTSpice на комплементарных полевых транзисторах CJFET_2 ОАО «Интеграл» (г. Минск) при температуре -197ᵒС и сопротивлении токостабилизирующего двухполюсника 11, равном 20 кОм (R11=R0=Rvar1=20кОм), а также с сопротивлением нагрузки 12 равном бесконечности (R12=Rн=Rvar2=∞).

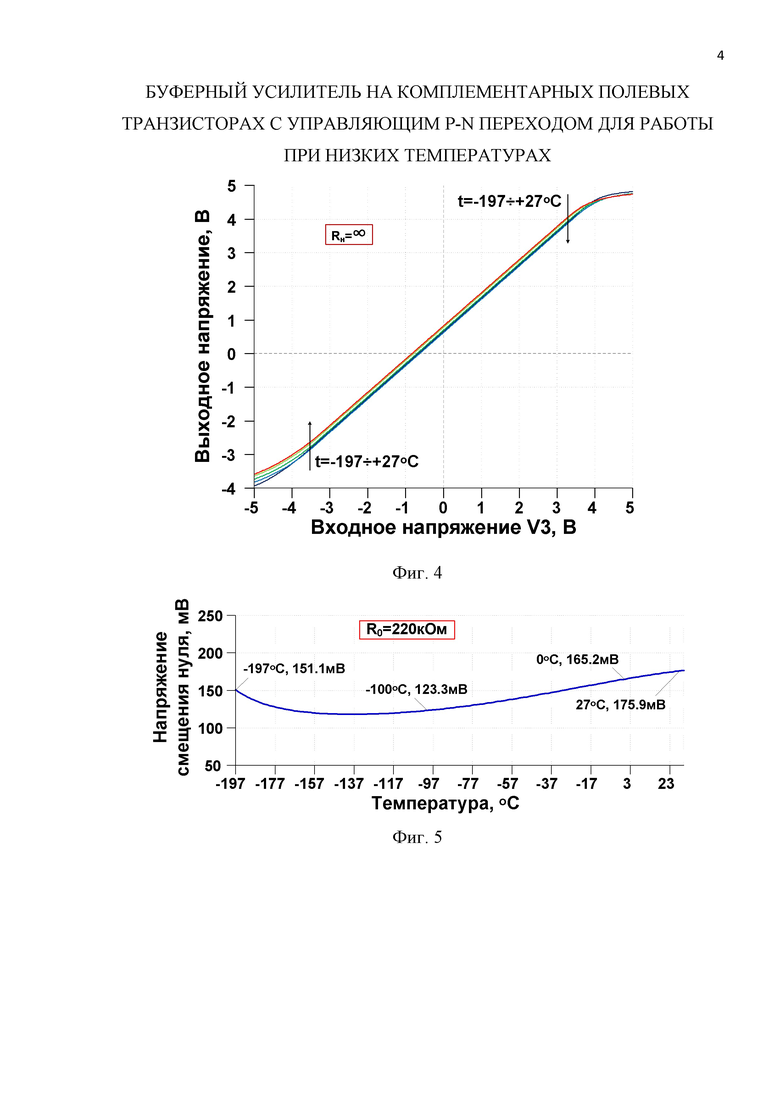

На чертеже фиг. 4 представлены зависимости выходного напряжения БУ (фиг. 3) от входного V3 в диапазоне температур t=-197÷27ᵒC при сопротивлениях токостабилизирующего двухполюсника 11 R11=R0=Rvar1=5кОм и нагрузки 12 R12=Rн=Rvar2=∞. Из данных графиков следует, что амплитудная характеристика заявляемого БУ изменяется незначительно.

На чертеже фиг. 5 приведен график зависимости напряжения смещения нуля БУ (фиг. 3) от температуры в диапазоне -197÷27ᵒС при сопротивлении резисторов R11=R0=Rvar1=220кОм и R12=Rн=Rvar2=∞. Таким образом, погрешность передачи входных сигналов с частотой fн=0 в заявленном БУ не превышает 175 мВ, что достаточно для многих применений.

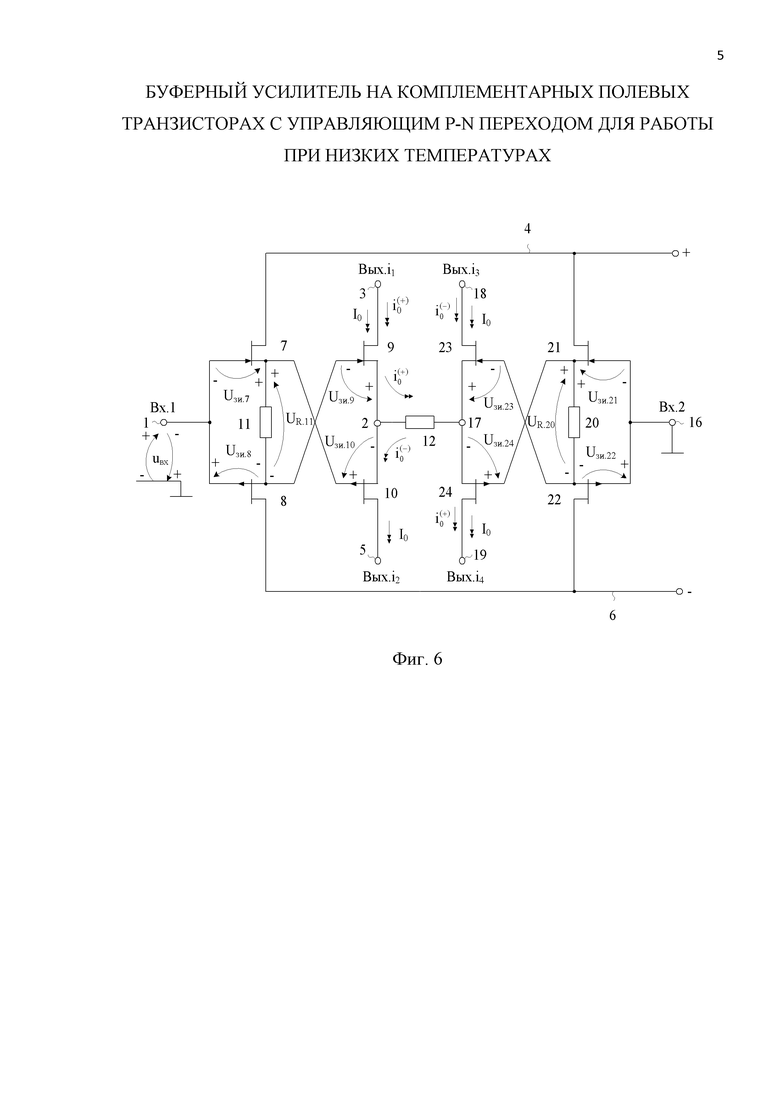

На чертеже фиг. 6 представлена схема включения заявляемого буферного усилителя (фиг. 2) в так называемом мостовом дифференциальном каскаде (МДК), который собирается из двух идентичных БУ фиг. 2. Следует заметить, что МДК является базовым функциональным узлом современной аналоговой схемотехники.

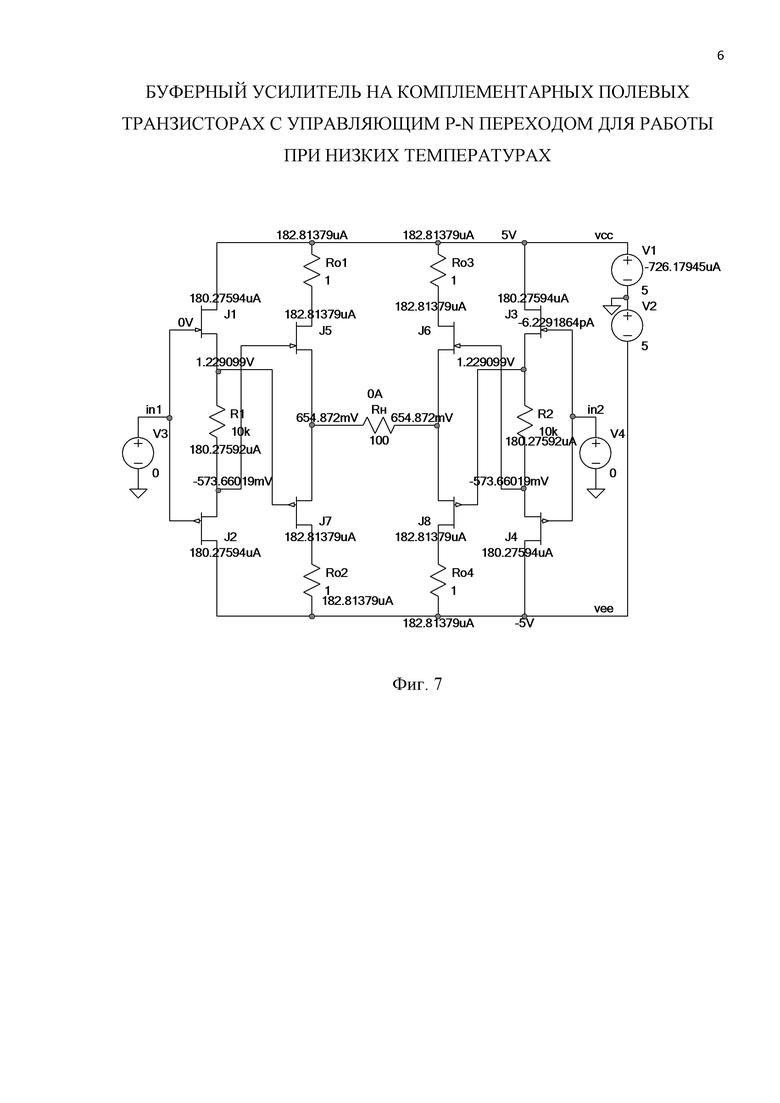

На чертеже фиг. 7 приведен статический режим БУ фиг. 6 в среде моделирования LTSpice на комплементарных полевых транзисторах CJFET_2 при температуре 27ᵒС и сопротивлении нагрузки 12 R12=Rн=100 Ом.

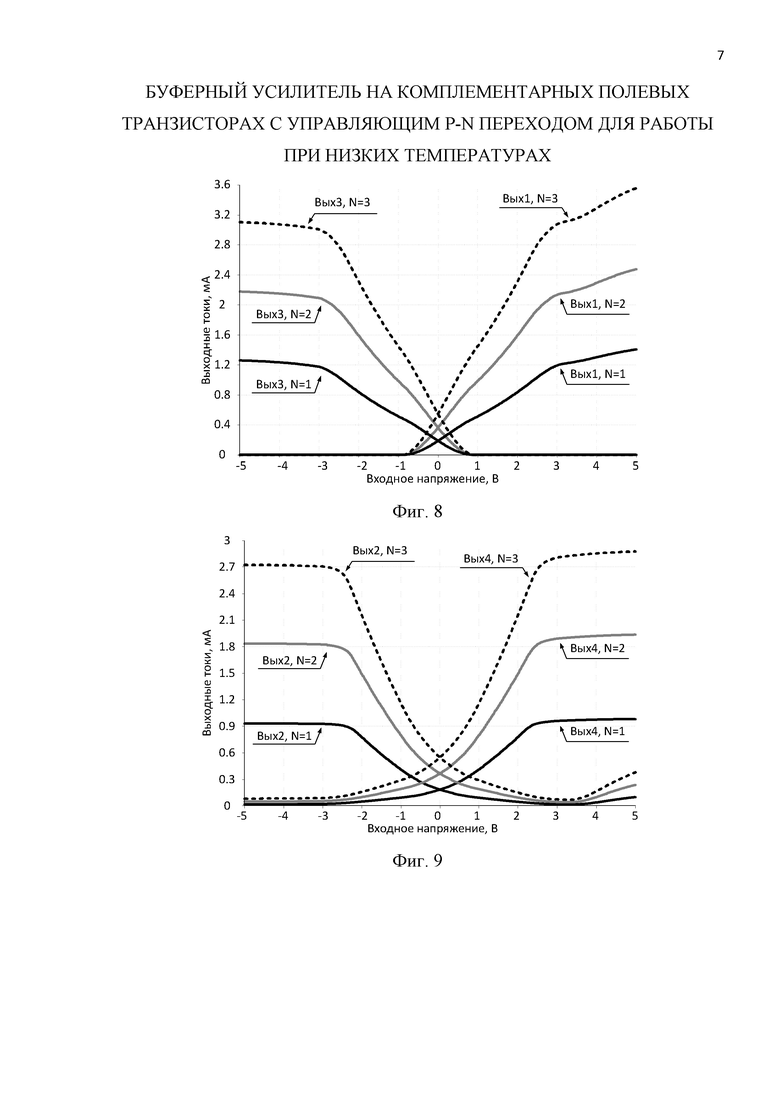

На чертеже фиг. 8 представлены графики зависимости выходных токов БУ фиг. 7 для первого 3 (iвых.1) и третьего 18 (iвых.3) токовых выходов устройства от входного дифференциального напряжения при разном количестве параллельно включенных полупроводниковых приборов в структуре первого 9, второго 10, третьего 23 и четвертого 24 выходных транзисторов (N=1-3).

На чертеже фиг. 9 представлена зависимость выходных токов БУ фиг. 7 для второго 5 (iвых.2) и четвертого 19 (iвых.4) токовых выходов от входного дифференциального напряжения при разном количестве параллельно включенных полупроводниковых приборов в структуре первого 9, второго 10, третьего 23 и четвертого 24 выходных транзисторов (N=1-3).

Буферный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах, содержащий потенциальный вход 1 и потенциальный выход 2 устройства, первый 3 токовый выход устройства, согласованный с первой 4 шиной источника питания, второй 5 токовый выход устройства, согласованный со второй 6 шиной источника питания, первый 7 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, второй 8 входной полевой транзистор, затвор которого соединен с потенциальным входом 1 устройства, первый 9 выходной полевой транзистор, исток которого связан с потенциальным выходом 2 устройства, а сток соединен с первым 3 токовым выходом устройства, второй 10 выходной полевой транзистор, исток которого соединен с потенциальным выходом 2 устройства, а сток соединен со вторым 5 токовым выходом устройства. В качестве полевых транзисторов схемы БУ применены полевые транзисторы с управляющим p-n переходом, между истоками первого 7 и второго 8 входных полевых транзисторов включен токостабилизирующий двухполюсник 11, сток первого 7 входного полевого транзистора связан с первой 4 шиной источника питания, сток второго 8 входного полевого транзистора связан со второй 6 шиной источника питания, затвор первого 9 выходного полевого транзистора подключен к истоку второго 8 входного полевого транзистора, а затвор второго 10 выходного полевого транзистора подключен к истоку первого 7 входного полевого транзистора.

В частном случае на чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства соединен с первой 4 шиной источника питания, а второй 5 токовый выход устройств соединен со второй 6 шиной источника питания.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, параллельно токостабилизирующему двухполюснику 11 включен корректирующий конденсатор 15, который уменьшает влияние паразитных емкостей 13 и 14 на быстродействие БУ в режим большого сигнала.

Рассмотрим работу предлагаемого БУ фиг. 2.

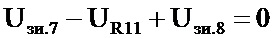

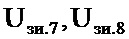

Особенность и уникальностью схемы заявляемого БУ состоит в том, что статический режим её транзисторов по току определяется одним токостабилизирующим двухполюсником 11, в качестве которого рекомендуется использовать резистор. Статический ток через токостабилизирующий двухполюсник 11 (резистор) определяется уравнениями на основе второго закона Кирхгофа:

где

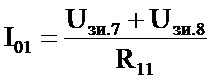

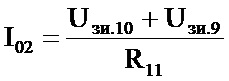

Аналогично, статический ток первого 9 и второго 10 выходных полевых транзисторов определяется уравнениями

Если первый 7 входной и второй 9 выходной полевые транзисторы, а также второй 8 входной и второй 10 выходной полевые транзисторы идентичны, то из уравнений (2) и (4) следует, что токи истоков всех транзисторов схемы БУ фиг. 2 одинаковы I01=I02, и определяются током через токостабилизирующий двухполюсник 11.

Таким образом, в заявляемом БУ имеется единственный элемент - токостабилизирующий двухполюсник 11 (резистор), определяющий токовый статический режим схемы. Другие известные схемы БУ таким свойством не обладают.

Если при нулевой емкости корректирующего конденсатора 15 (С15=0) на потенциальный вход 1 БУ (фиг. 2) подается большой положительный импульсный сигнал, то второй 8 входной полевой транзистор практически мгновенно «запирается» и ток через двухполюсник 11, который может иметь высокое сопротивление, начинает медленно заряжать паразитный конденсатор 14. Как следствие, потенциал на затворе первого 9 выходного полевого транзистора и, следовательно, выходное напряжение БУ будут медленно изменятся по линейному закону. В отсутствии корректирующего конденсатора 15 – это отрицательно сказывается на динамической погрешности БУ в режиме большого сигнала.

Рассмотрим далее работу БУ фиг. 2 в соответствии с п. 3 формулы изобретения - для случая, когда емкость корректирующего конденсатора 15 не равна нулю и превышает паразитную емкость 14. В этом случае, большой импульсный сигнал на потенциальном входе 1 БУ передается через первый 7 входной полевой транзистор в цепь истока запертого второго 8 входного полевого транзистора. Благодаря конденсатору 15 изменения напряжения на истоке второго 8 входного полевого транзистора способствуют более быстрому перезаряду паразитного конденсатора 14, что ускоряет переходный процесс и уменьшает динамическую погрешность заявляемого БУ при работе с импульсными сигналами большой амплитуды.

Схема мостового усилителя фиг. 6, в которой используется два однотипных заявляемых буферных усилителя фиг. 2, позволяет сформировать выходные токи, пропорциональные входному дифференциальному напряжению в широком диапазоне его изменения (фиг. 8, фиг. 9). Это является обязательным условием существенного быстродействия операционных усилителей с использованием мостового усилителя фиг. 6.

Таким образом, компьютерное моделирование (фиг. 4, фиг. 5, фиг. 8, фиг. 9) показывает, что предлагаемый буферный усилитель, схемотехника которого адаптирована на применение в диапазоне низких температур и воздействия проникающей радиации [28], имеет существенные достоинства в сравнении с известными вариантами построения БУ при их реализации в рамках КМОП технологического процесса.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154.

30. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферный усилитель для работы при низких температурах | 2018 |

|

RU2687161C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2677401C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2712410C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве двухтактных буферных и выходных усилителей мощности различных аналоговых устройств (операционных усилителей, драйверов линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур. Технический результат: создание радиационно стойкого и низкотемпературного схемотехнического решения БУ на комплементарных полевых транзисторах, обеспечивающего при высокой линейности амплитудной характеристики повышенную стабильность статического режима транзисторов и низкий уровень шумов, в том числе при работе в диапазоне низких температур. Для достижения результата предложено схемное решение, характеризующееся использованием единственного токостабилизирующего двухполюсника (резистора), определяющего токовый статический режим работы. 2 з.п. ф-лы, 9 ил.

1. Буферный усилитель (БУ) на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах, содержащий потенциальный вход (1) и потенциальный выход (2) устройства, первый (3) токовый выход устройства, согласованный с первой (4) шиной источника питания, второй (5) токовый выход устройства, согласованный со второй (6) шиной источника питания, первый (7) входной полевой транзистор, затвор которого соединен с потенциальным входом (1) устройства, второй (8) входной полевой транзистор, затвор которого соединен с потенциальным входом (1) устройства, первый (9) выходной полевой транзистор, исток которого связан с потенциальным выходом (2) устройства, а сток соединен с первым (3) токовым выходом устройства, второй (10) выходной полевой транзистор, исток которого соединен с потенциальным выходом (2) устройства, а сток соединен со вторым (5) токовым выходом устройства, отличающийся тем, что в качестве полевых транзисторов схемы БУ применены полевые транзисторы с управляющим p-n переходом, между истоками первого (7) и второго (8) входных полевых транзисторов включен токостабилизирующий двухполюсник (11), сток первого (7) входного полевого транзистора связан с первой (4) шиной источника питания, сток второго (8) входного полевого транзистора связан со второй (6) шиной источника питания, затвор первого (9) выходного полевого транзистора подключен к истоку второго (8) входного полевого транзистора, а затвор второго (10) выходного полевого транзистора подключен к истоку первого (7) входного полевого транзистора.

2. Буферный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах по п. 1, отличающийся тем, что первый (3) токовый выход устройства соединен с первой (4) шиной источника питания, а второй (5) токовый выход устройства соединен со второй (6) шиной источника питания.

3. Буферный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом для работы при низких температурах по п. 1, отличающийся тем, что параллельно токостабилизирующему двухполюснику (11) включен корректирующий конденсатор (15).

| US 7764123 B2, 27.07.2010 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2621286C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2624585C1 |

| US 5973534 A1, 26.10.1999 | |||

| US 6215357 B1, 10.04.2001. | |||

Авторы

Даты

2019-04-09—Публикация

2018-06-08—Подача