Настоящее изобретение в общем относится к области процессоров, а в частности к способу исправления ошибочных предварительно декодированных данных ассоциативно связанных с инструкцией, посредством применения процедуры коррекции ветвлений с целевым адресом инструкции.

Микропроцессоры выполняют вычислительные задачи в широком разнообразии приложений. Улучшенная производительность процессора почти всегда желательна для того, чтобы предоставить более быструю работу и/или улучшенную функциональность посредством изменений программного обеспечения. Во многих внедренных применениях, таких как портативные электронные устройства, сохранение энергии также является важной задачей в конструкции и осуществлении процессора.

Самые современные процессоры могут использовать конвейерную архитектуру, где последовательные инструкции перекрываются в выполнении для того, чтобы увеличить общую производительность процессора. Сохранение гладкого выполнения через конвейер является критическим для того, чтобы достичь высокой производительности. Самые современные процессоры также используют иерархическую память с быстрыми расположенными на кристалле процессора модулями кэш-памяти, хранящими локальные копии данных и инструкций, к которым недавно осуществлялся доступ. Одной из технологий оптимизации конвейера, известной в области техники, является предварительное декодирование инструкций. То есть инструкции рассматриваются, когда они считываются из памяти, частично декодируются, и некоторая информация об инструкциях - известная как информация предварительного декодирования - сохраняется в кэш-памяти вместе с ассоциативно связанными инструкциями. Когда инструкции позже вызываются из кэша, информация предварительного декодирования также вызывается и используется, чтобы помочь полностью декодировать инструкции.

Порой информация предварительного декодирования содержит ошибки. Эти ошибки могут быть обнаружены во время стадий декодирования в конвейере. Когда ошибка обнаружена, происходит исключение и конвейер должен быть очищен и все инструкции, включающие в себя ошибочно предварительно декодированную инструкцию, должны быть выбраны повторно. Этот процесс привносит значительное ухудшение в производительность и управление энергией.

Сущность изобретения

Настоящее изобретение в одном варианте осуществления относится к способу коррекции неправильно предварительно декодированной инструкции. Обнаруживается ошибка предварительного декодирования. Вызывается процедура коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение ошибки.

Настоящее изобретение в другом варианте осуществления относится к процессору. Процессор включает в себя предварительный декодер, размещенный на пути вызова инструкций, предварительный декодер формирует информацию предварительного декодирования, ассоциативно связанную с отдельной инструкцией. Процессор также включает в себя детектор ошибок предварительного декодирования и корректор, обнаруживающий некорректную информацию предварительного декодирования, ассоциативно связанную с инструкцией, и инициирующий выполнение инструкции как неправильно предсказанного ветвления с целевым адресом ветвления из адреса инструкции.

Краткое описание чертежей

Фиг.1 является функциональной блок-схемой процессора.

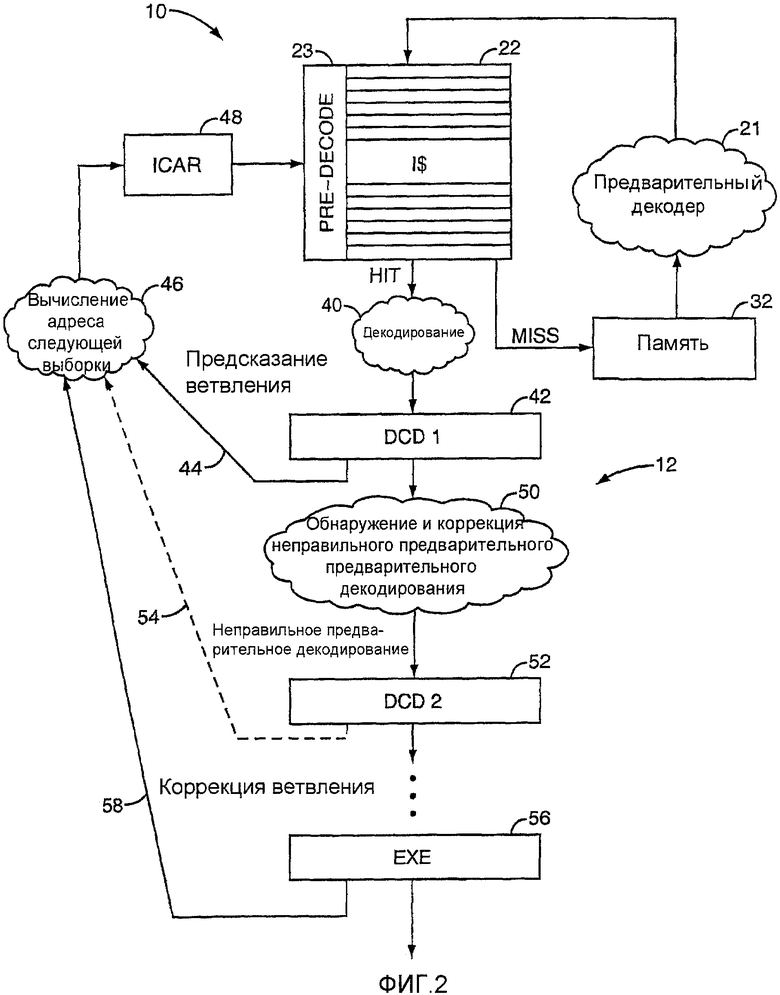

Фиг.2 является функциональной блок-схемой памяти, предварительного декодера, кэша инструкций и части процессорного конвейера.

Фиг.3 является функциональной блок-схемой логики коррекции ветвления.

Подробное описание изобретения

Конвейерные архитектуры процессоров эксплуатируют параллелизм, перекрывая выполнение множества последовательных инструкций, каждая из которых имеет множественные этапы выполнения. Типичные этапы выполнения включают в себя вызов инструкции, декодирование, выполнение и обратную запись. Каждый этап выполняется в конвейере одним или более ступенями конвейера, содержащими логику и элемент памяти, такой как триггер-защелка или регистр. Ступени конвейера соединены вместе, чтобы сформировать конвейер. Инструкции вводятся в конвейер и последовательно выполняются по ступеням. Дополнительные инструкции вводятся в конвейер прежде, чем завершится выполнение предыдущих инструкций, следовательно, множество инструкций может быть обработано в конвейере в любой данный момент времени. Эта способность эксплуатировать параллелизм среди инструкций в последовательном потоке инструкций значительно способствует улучшению производительности процессора. В идеальных условиях и в процессоре, который завершает каждую ступень конвейера в одном цикле, следом за кратким первоначальным процессом заполнения конвейера, выполнение инструкции может завершаться в каждом цикле. Многочисленные реальные ограничения препятствуют выдерживанию этого идеального условия; однако сохранение конвейера полным и его работы плавно протекающей является общей целью при разработке процессора.

Обычно современные процессоры также используют иерархию памяти, которая размещает небольшое количество быстрой, дорогостоящей памяти ближе к процессору и которая поддерживается большим количеством более медленной, дешевой памяти. Типичная иерархия памяти процессора может содержать регистры в процессоре на верхнем уровне, поддерживаемые одним или более расположенными на кристалле процессора модулями кэш-памяти (например, SRAM); возможно, модулем кэш-памяти вне кристалла, именуемым как кэш уровня 2 или L2 (например, SRAM); главную память (обычно DRAM); запоминающее устройство на дисках (магнитный носитель) и ленту или CD (магнитный или оптический носитель) на самом медленном уровне. Во внедренных применениях, таких как портативные электронные устройства, может быть ограничено, если необходимо, запоминающее устройство на диске, и, следовательно, главная память (обычно ограниченная по размеру) может быть наиболее медленным уровнем в иерархии памяти.

Фиг.1 изображает функциональную блок-схему типичного процессора 10, использующего и конвейерную архитектуру, и структуру иерархической памяти. Процессор 10 выполняет инструкции в конвейере 12 выполнения инструкций согласно логике 14 управления. Конвейер включает в себя различные регистры или триггеры-защелки 16, организованные в ступени конвейера, и один или более арифметико-логических устройств (ALU) 18. Комплект 20 регистров общего назначения (GPR) предоставляет регистры, содержащие вершину иерархии памяти. Конвейер выбирает инструкции из кэша 22 инструкций с адресацией памяти и разрешениями, управляемыми буфером быстрого преобразования адресов со стороны инструкций (ITLB) 24, и некоторое первоначальное декодирование инструкций выполняется предварительным декодером 21. Данные являются доступными из кэша 26 данных с адресацией памяти и разрешениями, управляемыми главным буфером быстрого преобразования адресов (TLB) 28. В различных вариантах осуществления ITLB может содержать копию части TLB. Альтернативно, ITLB и TLB могут быть объединены. Подобным образом, в различных вариантах осуществления процессора 10, I-кэш 22 и D-кэш 26 могут быть объединены или унифицированы. Доступы, которые не представлены в I-кэше 22 и/или D-кэше 26 (пропуски), вызывают доступ к главной (вне кристалла) памяти 32 под управлением интерфейса 30 памяти. Процессор 10 может включать в себя интерфейс 34 ввода/вывода (I/O), управляющий доступом к различным периферийным устройствам 36. Специалисты в области техники признают, что возможны многочисленные вариации процессора 10. Например, процессор 10 может включать в себя кэш второго уровня (L2) либо для одного из двух, либо для обоих I- и D-кэшей. Кроме того, один или более из функциональных блоков, изображенных в процессоре 10, может быть опущен в отдельном варианте осуществления.

Одна известная технология увеличения производительности процессора и снижения потребления энергии известна как предварительное декодирование. Предварительный декодер 21 содержит логику, размещенную на пути между главной памятью 32 и кэшем 22 инструкций. Некоторые из инструкций, вызванных из памяти, могут быть предварительно декодированы с информацией о предварительном декодировании, сформированной и записанной в I-кэш 22 вместе с инструкцией. Информация предварительного декодирования может помочь одной или более ступеням конвейера в декодировании инструкции, когда она вызывается из кэша для выполнения. Например, предварительный декодер может определить длину переменных по длине инструкций и записать информацию о предварительном декодировании в кэш, которая помогает ступени декодирования конвейера найти правильное число битов для переменной по длине инструкции. Разнообразная информация может быть предварительно декодирована и сохранена в I-кэше 22.

Предварительный декодер 21 улучшает производительность, удаляя логику из одной или более ступеней декодирования конвейера, позволяя раньше использовать логику и, возможно, предоставляя возможность для более короткого цикла машинного времени. Предварительный декодер 21 также уменьшает потребление энергии, выполняя операции предварительного декодирования один раз. Так как коэффициенты совпадения I-кэша 22 обычно являются в максимуме 90%, значительные сбережения энергии могут быть реализованы посредством устранения необходимости выполнять логические операции каждый раз, когда инструкция выполняется из I-кэша 22.

Порой предварительный декодер 21 делает ошибки. Например, если данные, такие как параметры или непосредственные значения, были сохранены в памяти вместе с инструкциями, операция предварительного декодирования, которая определяет длину инструкции, просто считая байты от начала строки кэша, может ошибочно идентифицировать байты одного или более таких параметров или непосредственных значений как инструкцию следующей далее строки. Возможны другие типы ошибок, включающие в себя случайные ошибки по битам, либо в предварительном декодере 21, либо в I-кэше 22. Эти ошибки будут обнаружены на одной или более ступенях декодирования конвейера и будут в типичном варианте приводить к исключительной ситуации, требующей, чтобы конвейер был очищен и повторно запущен, таким образом привнося дополнительные расходы по производительности и потреблении энергии.

Существуют способы скорректировать ошибки предварительного декодирования, которые предотвращают возникновение исключительной ситуации и ассоциативно связанную очистку конвейера 12. Фиг.2 является функциональной блок-схемой, изображающей части процессора 10 и конвейера 12. Фиг.2 также изображает регистр адреса кэша инструкций (ICAR) 48, который формирует индекс I-кэша 22. Адрес, загруженный в ICAR 48, формируется и/или выбирается схемой 46 вычисления адреса следующей выборки. Когда инструкции выбираются из памяти 32 (или кэша L2), они предварительно декодируются предварительным декодером 21 и информация 23 о предварительном декодировании сохраняется в кэше 22 инструкций вместе с соответствующими инструкциями.

В конвейере 12 инструкции и ассоциативно связанная информация 23 предварительного декодирования выбираются из I-кэша 22, по меньшей мере, частично декодированными логикой 40 декодирования, а результаты сохраняются в триггере-защелке 42 ступени DCD1 конвейера. Во многих процессорах 10 ступень

DCD1 конвейера включает в себя устройство предсказания ветвления. В случаях, когда устройство предсказания ветвления предсказывает ветвление, которое будет получено, ступень конвейера может вычислять целевой адрес ветвления и предоставлять его логике 46 вычисления адреса следующей выборки по адресному тракту 44 предсказания ветвления. Это один пример адресного тракта от ступени конвейера к логике 46 вычисления адреса следующей выборки (ветвление, предсказанное как непринятое, просто позволит продолжиться выборке последующей инструкции).

Выбранная и частично декодированная инструкция затем движется, в примерном варианте осуществления, к ступени DCD2 конвейера, которая включает в себя логику 50 обнаружения и исправления неправильного предварительного декодирования. Если обнаружена ошибка в информации предварительного декодирования, ступень DCD2 конвейера может сигнализировать об исключительной ситуации и очистить конвейер 12, как обсуждалось выше.

Альтернативно, ошибка предварительного декодирования может быть исправлена повторной выборкой инструкции из памяти 32. Одним способом выполнить это является сделать недействительной инструкцию в кэше 22 и предоставить адрес инструкции по маршруту 54 схеме 46 адресации следующей выборки. Этот адрес будет затем загружен в ICAR 48. Так как инструкция была признана недействительной в кэше 22, доступ к кэшу будет отсутствовать, вызывая обращение к главной памяти 32. Инструкция, выбранная из главной памяти 32, затем должна быть корректно предварительно декодирована предварительным декодером 21 и помещена обратно в кэш 22 инструкций. Инструкция может затем быть повторна выбрана из кэша 22 вместе с корректной информацией 23 предварительного декодирования.

Схема 46 вычисления адреса следующей выборки обычно находится на критическом маршруте большей части потоков данных процессора и, таким образом, ограничивает время машинного цикла. Добавление маршрута 54 для адреса инструкции, ассоциативно связанного с неправильным предварительным декодированием, добавит логику к вычислению 46 адреса следующей выборки, увеличивая время машинного цикла и уменьшая производительность. Этот всплеск производительности является особенно очевидным, принимая во внимание то, что предварительно декодированная информация 23 является исключительно неправильной. Оптимизация производительности для редкого случая ценой обычного случая обыкновенно уменьшает общую производительность процессора.

Согласно одному варианту осуществления настоящего изобретения устраняется неправильный маршрут 54 предварительного декодирования к устройству 46 вычисления адреса следующей выборки (как указано штриховой линией на фиг.2). Скорее, чем предоставить предназначенный маршрут устройству 46 вычисления адреса следующей выборки, логика 50 обнаружения и коррекции неправильного предварительного декодирования заставляет конвейер 12 оценить неправильно предварительно декодированную инструкцию как инструкцию ветвления. Логика 50 коррекции предварительного декодирования может изменить семантику неправильно предварительно декодированной инструкции на семантику инструкции ветвления или альтернативно может установить флаг, который переносится по конвейеру, флаг указывает ступеням выполнения конвейера, какая инструкция должна быть трактована как ветвление.

В частности, неправильно предварительно декодированная инструкция оценивается как ветвление, которое было предсказано как непринятое и оценено как принятое, с целевым адресом ветвления, являющимся адресом неправильно предварительно декодированной инструкции. В некоторой точке вниз по конвейеру 12 (зависит от деталей осуществления) инструкция оценивается выполнением ступени 56 конвейера, которая оценивает условие "ветвление принято" и формирует целевой адрес ветвления. Целевой адрес ветвления предоставляется устройству 46 вычисления следующей выборки по маршруту 58 коррекции ветвления. Логика оценки условия ветвления, логика формирования целевого адреса ветвления и маршрут 58 коррекции ветвления и ассоциативно связанная управляющая логика в устройстве 46 вычисления адреса следующей выборки уже существуют в каждом конвейерном процессоре 10, который предсказывает поведение ветвления.

Фиг.3 является функциональной схемой одного возможного осуществления логики коррекции ветвления. В триггере-защелке 56 EXE-ступени конвейера существуют бит 60 принятого предсказанного ветвления (BPT) и бит 62 оценки условия ветвления (COND). Бит 60 BPT равен единице, если ветвление было предсказано так, чтобы быть принятым устройством предсказания ветвления ранее в конвейере 12, и равен нулю, если ветвление было предсказано непринятым. Бит 62 COND равен единице, если ветвление оценивается как принятое, и равен нулю, если ветвление оценивается как непринятое. Эти два бита могут быть сложены по модулю два, как указано вентилем 66, чтобы формировать выбор мультиплексора или похожий сигнал управления, который предоставляется устройству 46 вычисления адреса следующей выборки, указывающий, что маршрут 58 коррекции ветвления должен быть выбран в качестве адреса следующей выборки. Таблица 1 ниже изображает таблицу истинности для XOR 66.

Бит 62 оценки условия может дополнительно служить в качестве входных данных для выбора мультиплексора 68, который выбирает между последовательным адресом и вычисленным целевым адресом 64 ветвления, чтобы сформировать адрес, помещенный по маршруту 58 коррекции ветвления.

Согласно одному варианту осуществления настоящего изобретения, чтобы управлять неправильно предварительно декодированной инструкцией, бит 60 BPT может быть установлен или принудительно скорректирован в ноль, а бит 62 COND может быть установлен или принудительно скорректирован в единицу, чтобы вызывать ситуацию "ветвление неправильно предсказанное как непринятое". В этом случае вычисленный целевой адрес 64 ветвления будет направлен схеме 46 адресации следующей выборки через маршрут 58 коррекции ветвления.

Согласно одному варианту осуществления настоящего изобретения неправильно предварительно декодированная инструкция оценивается как ПК-связная инструкция ветвления с полем замены ветвления, равным нулю. Когда эта инструкция оценивается в EXE-ступени 56 конвейера, вычисленный целевой адрес ветвления будет содержать адрес ошибочно предварительно декодированной инструкции (с нулевым смещением). В другом варианте осуществления настоящего изобретения неправильно предварительно декодированная инструкция оценивается как инструкция регистрового ветвления и, дополнительно, регистр целевого адреса ветвления загружается адресом неправильно предварительно декодированной инструкции. Когда регистр с целевым адресом ветвления загружается посредством арифметической операции, регистры операндов могут быть загружены так, чтобы сформировать адрес неправильно предварительно декодированной инструкции. Многочисленные другие способы оценки неправильно предварительно декодированной инструкции, такие как инструкция неправильно предсказанного непринятого ветвления, имеющая целевой адрес самой инструкции, будут легко видимы специалистам в области техники и включены в рамки настоящего изобретения.

Обращаясь опять к фиг.2, инструкция принудительного неправильно предсказанного непринятым ветвления выполняется в EXE-ступени 56, и целевой адрес ветвления, содержащий адрес неправильно предварительно декодированной инструкции, расположен по маршруту 58 коррекции ветвления. Этот адрес выбирается устройством 46 вычисления адреса следующей выборки, загружается в ICAR 48, и выборка инструкции выполняется в I-кэше 22.

Так как логика 50 обнаружения и коррекции неправильного предварительного декодирования отключает строку кэша, содержащую неправильно предварительно декодированную инструкцию, доступ к I-кэшу 22 будет отсутствовать, обуславливая выбор инструкции из памяти 32 (или кэша L2). Инструкция затем будет правильно предварительно декодирована предварительным декодером 21 и помещена вместе с информацией 23 правильного предварительного декодирования в I-кэш 22. Инструкция и информация 23 предварительного декодирования могут затем быть повторно выбраны из I-кэша 22, правильно декодированы и правильно выполнены в конвейере 12. Ошибка смещения, например, из-за того, что данные разбросаны с инструкциями, повторно не произойдет в предварительном декодере 21, так как обращение к памяти осуществляется по точному адресу инструкции, а не по началу строки кэша.

Отметим, что вышеуказанное описание обращений к памяти является концептуальным. В любом данном осуществлении доступ к памяти 32 может происходить параллельно с доступом к I-кэшу 22; промах I-кэша 22 может быть предсказан и, следовательно, доступ к I-кэшу 22 отменен; результаты обращения к памяти 32 могут идти непосредственно в конвейер 12 параллельно с записью в I-кэш 22; и подобное. Вообще, настоящее изобретение заключает в себе оптимизации производительности всей памяти и/или кэша, которые в работе могут отклониться от вышеуказанного описания.

Хотя настоящее изобретение было описано в данном документе относительно отдельных признаков, аспектов и вариантов его осуществления, будет очевидно, что многочисленные изменения, модификации и другие варианты осуществления возможны в широких рамках настоящего изобретения, и, соответственно, все изменения, модификации и варианты осуществления должны рассматриваться как находящиеся в рамках изобретения. Настоящие варианты изобретения поэтому должны быть истолкованы во всех аспектах как иллюстративные, а не ограничительные, и все изменения, делающиеся в пределах смысла и эквивалентности прилагаемой формулы изобретения, предполагаются быть охваченными ею.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭНЕРГОЭФФЕКТИВНЫЙ МЕХАНИЗМ УПРЕЖДАЮЩЕЙ ВЫБОРКИ ИНСТРУКЦИЙ | 2006 |

|

RU2375745C2 |

| КЭШИРОВАНИЕ ЦЕЛЕВОГО АДРЕСА ПЕРЕХОДА С УПРЕЖДАЮЩЕЙ ВЫБОРКОЙ | 2006 |

|

RU2358310C1 |

| СХЕМА ОТЛАДКИ, СРАВНИВАЮЩАЯ РЕЖИМ ОБРАБОТКИ НАБОРА КОМАНД ПРОЦЕССОРА | 2007 |

|

RU2429525C2 |

| ПРЕДВАРИТЕЛЬНОЕ ДЕКОДИРОВАНИЕ ИНСТРУКЦИЙ ПЕРЕМЕННОЙ ДЛИНЫ | 2007 |

|

RU2412464C2 |

| ОЧИСТКА СЕГМЕНТИРОВАННОГО КОНВЕЙЕРА ДЛЯ НЕВЕРНО ПРЕДСКАЗАННЫХ ПЕРЕХОДОВ | 2008 |

|

RU2427889C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПРЕДСКАЗАНИЯ ВЕТВЛЕНИЙ | 2012 |

|

RU2602335C2 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| СПОСОБЫ И УСТРОЙСТВА ДЛЯ СОКРАЩЕНИЯ ПОИСКОВ В КЭШЕ ЦЕЛЕВЫХ АДРЕСОВ ВЕТВЛЕНИЙ | 2007 |

|

RU2419835C2 |

| СИСТЕМЫ И СПОСОБЫ ПРОВЕРКИ АДРЕСА ВОЗВРАТА ПРОЦЕДУРЫ | 2014 |

|

RU2628163C2 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

Изобретение относится к процессорам с конвейерной архитектурой. Техническим результатом является улучшение производительности процессора. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых обнаруживают ошибку предварительного декодирования и вызывают процедуру коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение упомянутой ошибки, при этом упомянутую предварительно декодированную инструкцию оценивают как инструкцию, соответствующую неправильно предсказанному ветвлению. 7 н. и 15 з.п. ф-лы, 3 ил., 1 табл.

1. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых:

обнаруживают ошибку предварительного декодирования и вызывают процедуру коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение упомянутой ошибки, при этом упомянутую предварительно декодированную инструкцию оценивают как инструкцию, соответствующую неправильно предсказанному ветвлению.

2. Способ по п.1, дополнительно содержащий этап, на котором делают недействительной упомянутую неправильно предварительно декодированную инструкцию в кэше прежде, чем вызывать упомянутую процедуру коррекции ветвления.

3. Способ по п.2, дополнительно содержащий этап, на котором выбирают упомянутую инструкцию из памяти в ответ на упомянутую процедуру коррекции ветвления.

4. Способ по п.3, дополнительно содержащий этапы, на которых предварительно декодируют упомянутую инструкцию и сохраняют упомянутую инструкцию и информацию предварительного декодирования, ассоциированную с упомянутой инструкцией, в упомянутом кэше.

5. Способ по п.1, в котором при вызове процедуры коррекции ветвления задают условие истинности (TRUE) ветвления и задают ложность (FALSE) предсказания ветвления.

6. Способ по п.1, в котором при вызове процедуры коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции сохраняют упомянутый адрес в регистре целевого адреса и вызывают коррекцию инструкции регистрового ветвления.

7. Способ по п.6, в котором при сохранении упомянутого адреса в регистре целевого адреса в упомянутый регистр целевого адреса загружают результаты арифметической операции в отношении содержимого двух регистров операндов, сохраняют вычисленные значения в упомянутых регистрах операндов, причем упомянутые значения вычисляются для получения упомянутого адреса, исходя из упомянутой арифметической операции.

8. Способ по п.1, в котором при вызове процедуры коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции вызывают коррекцию связанной с программным счетчиком (PC) инструкции ветвления с нулевым смещением ветвления.

9. Процессор, содержащий:

предварительный декодер, вставленный на пути выборки инструкций, причем данный предварительный декодер формирует информацию предварительного декодирования, ассоциированную с инструкцией; и

детектор и корректор ошибок предварительного декодирования, обнаруживающий некорректную информацию предварительного декодирования, ассоциированную с упомянутой инструкцией, и предписывающий упомянутой инструкции выполняться как неправильно предсказанное ветвление с адресом упомянутой инструкции в качестве целевого адреса ветвления.

10. Процессор по п.9, дополнительно содержащий кэш-память, хранящую упомянутую инструкцию и упомянутую информацию предварительного декодирования, при этом упомянутый детектор и корректор ошибки предварительного декодирования дополнительно делают недействительной упомянутую инструкцию в упомянутой кэш-памяти при обнаружении упомянутой ошибки предварительного декодирования.

11. Процессор по п.9, дополнительно содержащий устройство предсказания ветвления и маршрут коррекции ветвления, доставляющий скорректированный целевой адрес ветвления для выборки инструкции в ответ на условное ветвление, оцененное принятым, которое было предсказано непринятым.

12. Процессор по п.11, в котором упомянутый детектор и корректор ошибки предварительного декодирования использует упомянутый маршрут коррекции ветвления для предписания упомянутой неправильно предварительно декодированной инструкции выполняться в качестве инструкции, соответствующей неправильно предсказанному непринятому ветвлению.

13. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых:

обнаруживают ошибку предварительного декодирования,

в ответ на обнаружение упомянутой ошибки предварительного декодирования предписывают неправильно предварительно декодированной инструкции выполняться как неправильно предсказанное ветвление с адресом упомянутой инструкции в качестве целевого адреса ветвления и

корректируют упомянутую ошибку предварительного декодирования посредством выборки упомянутой инструкции из памяти и предварительного декодирования упомянутой инструкции.

14. Способ по п.13, в котором при выборке упомянутой инструкции из памяти делают недействительной упомянутую инструкцию в кэш-памяти и пытаются выбрать упомянутую инструкцию из упомянутой кэш-памяти после того, как упомянутая инструкция сделана недействительной.

15. Способ по п.13, в котором при выборке упомянутой инструкции из памяти оценивают упомянутую инструкцию как ветвление с упомянутым адресом инструкции в качестве целевого адреса ветвления.

16. Способ по п.15, в котором при оценке упомянутой инструкции в качестве ветвления оценивают упомянутую инструкцию как неправильно предсказанное непринятое ветвление.

17. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых:

обнаруживают ошибку предварительного декодирования и

вызывают процедуру коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение упомянутой ошибки,

при этом при вызове процедуры коррекции ветвления задают условие истинности (TRUE) ветвления и задают ложность (FALSE) предсказания ветвления.

18. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых:

обнаруживают ошибку предварительного декодирования и

вызывают процедуру коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение упомянутой ошибки,

при этом при вызове процедуры коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции сохраняют целевой адрес в регистре целевого адреса и инициируют коррекцию инструкции регистрового ветвления.

19. Способ по п.18, в котором при сохранении в регистре целевого адреса загружают в регистр целевого адреса результаты арифметической операции в отношении содержимого двух регистров операндов, сохраняют вычисленные значения в этих регистрах операндов и определяют целевой адрес, исходя из этой арифметической операции.

20. Способ коррекции неправильно предварительно декодированной инструкции, содержащий этапы, на которых:

обнаруживают ошибку предварительного декодирования и

вызывают процедуру коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции в ответ на обнаружение упомянутой ошибки,

при этом при вызове процедуры коррекции ветвления с целевым адресом неправильно предварительно декодированной инструкции вызывают программный счетчик (PC) относительно коррекции инструкции ветвления с нулевым смещением ветвления.

21. Процессор, содержащий:

предварительный декодер, вставленный на пути выборки инструкций, причем данный предварительный декодер формирует информацию предварительного декодирования, ассоциированную с инструкцией, имеющей адрес;

детектор и корректор ошибок предварительного декодирования для обнаружения некорректной информации предварительного декодирования, ассоциированной с упомянутой инструкцией, и предписания данной инструкции выполняться как неправильно предсказанное ветвление с адресом упомянутой инструкции в качестве целевого адреса ветвления, блок предсказания ветвления для подачи скорректированного целевого адреса ветвления для выборки инструкции в ответ на условное ветвление, оцененное принятым, которое было предсказано непринятым.

22. Процессор по п.21, в котором детектор и корректор ошибок предварительного декодирования использует маршрут коррекции ветвления для предписания упомянутой неправильно предварительно декодированной инструкции выполняться в качестве инструкции, соответствующей неправильно предсказанному непринятому ветвлению.

| US 2002194460 A1, 19.12.2002 | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| СПОСОБ ИЗМЕРЕНИЯ ВРЕМЕНИ РАСПРОСТРАНЕНИЯ ЗВУКОВОГО СИГНАЛА В ТЕКУЧЕЙ СРЕДЕ И СПОСОБ ИЗМЕРЕНИЯ СКОРОСТИ ПОТОКА ТЕКУЧЕЙ СРЕДЫ | 1997 |

|

RU2182335C2 |

| Способ измерения диэлектрическихпАРАМЕТРОВ МАТЕРиАлОВ | 1977 |

|

SU798632A1 |

Авторы

Даты

2009-09-10—Публикация

2005-11-18—Подача