Область техники

Настоящее изобретение, в общем, относится к области процессоров, а, в частности, к способу улучшения прогнозирования ветвлений за счет сокращения поисков в кэше целевых адресов ветвлений.

Уровень техники

Микропроцессоры выполняют вычислительные задачи во множестве приложений. Улучшенная производительность процессора почти всегда желательна для того, чтобы обеспечить более быструю работу и/или повышенную функциональность посредством изменений программного обеспечения. Во многих внедренных применениях, таких как портативные электронные устройства, экономия энергии и увеличение пропускной способности также являются целями конструирования и реализации процессоров.

Многие современные процессоры используют конвейерную архитектуру, где последовательные команды, каждая из которых имеет несколько шагов исполнения, перекрываются при исполнении. Для повышенной производительности команды должны протекать непрерывно через конвейер. Любая ситуация, которая приводит к тому, что команды останавливаются в конвейере, может негативно влиять на производительность. Если команды очищаются из конвейера и затем повторно выбираются, ухудшается как производительность, так и потребление энергии.

Большинство программ включает в себя команды ветвления с косвенной адресацией, где фактический режим ветвления не известен до тех пор, пока команда ветвления с косвенной адресацией не будет оценена глубоко в конвейере. Чтобы исключить останов, который может происходить в результате ожидания фактической оценки команды ветвления с косвенной адресацией, современные процессоры могут использовать определенную форму прогнозирования ветвлений, посредством которой характер ветвления команд с косвенной адресацией прогнозируется на ранней стадии в конвейере. На основе спрогнозированной оценки ветвления процессор эмпирически извлекает (предварительно извлекает) и обрабатывает команды из спрогнозированного адреса - либо целевого адреса ветвления (если спрогнозировано, что ветвление должно быть принято), либо следующего последовательного адреса после команды ветвления (если спрогнозировано, что ветвление не должно быть принято). Определение того, должна или нет команда ветвления с косвенной адресацией быть принята, упоминается как определение направления ветвления.

Традиционные методы прогнозирования ветвлений включают в себя кэш целевых адресов ветвлений (BTAC), размещенный на стадии выборки процессорного конвейера и логики прогнозирования ветвлений. BTAC сохраняет целевой адрес ранее выбранной команды и индексируется посредством адреса команды. I-кэши традиционно заполняются командами различных типов команд, которые извлечены из кэша верхнего уровня или запоминающего устройства. BTAC традиционно заполняются после того, как команда ветвления с косвенной адресацией фактически разрешена далее ниже в процессорном конвейере.

При работе традиционные методы прогнозирования ветвлений выполняют адресные поиски для предварительно выбранных команд как в BTAC, так и в I-кэше параллельно. Если имело место неудачное обращение в BTAC, эти традиционные методы ветвления, таким образом, потребили мощность на поиск BTAC, не найдя совпадения. Если имело место удачное обращение в BTAC, искомый адрес может рассматриваться как команда ветвления с косвенной адресацией. После поиска BTAC традиционные методы вызывают логику прогнозирования ветвлений, чтобы определять то, должен ли целевой адрес ветвления, извлеченный от BTAC, прогнозироваться как принятый или нет. Если логика прогнозирования ветвлений прогнозирует принятие, логика прогнозирования ветвлений перенаправляет поток команд посредством извлечения команд, начинающихся с целевого адреса ветвления.

Все последовательные команды, которые поступили в процессорный конвейер, начиная с команды ветвления, типично сбрасываются из конвейера. Путь, определенный посредством поиска BTAC и последующего прогнозирования ветвлений, типично является критическим по скорости путем, потому что, чем короче время этого пути, тем меньше количество команд, которые должны быть сброшены из процессорного конвейера перед перенаправлением потока команд. Следовательно, желательно для этого пути быть максимально коротким, чтобы минимизировать мощность, расходуемую на сброс команд.

Традиционные методы для уменьшения времени критического пути включают в себя сокращение размера BTAC и/или организацию BTAC в многоканальном формате. Тем не менее, за счет сокращения размера BTAC число потенциальных удачных обращений и, таким образом, вероятность нахождения целевого адреса ветвления в BTAC уменьшается, понижая эффективность BTAC в целом. Кроме того, посредством организации BTAC в многоканальном формате индексация в BTAC может стать более быстрой, но время, потраченное на сравнение, может быть увеличено. В этих ситуациях BTAC может быть медленнее, чем I-кэш, таким образом, становясь ограничивающим фактором в части параллельного поиска критического пути. Следовательно, требуются устройства и способы, чтобы уменьшать время перенаправления потока команд, когда команда ветвления с косвенной адресацией обнаружена в процессорном конвейере, без снижения эффективности прогнозирования ветвлений.

Раскрытие изобретения

Настоящее изобретение исходит из того, что традиционные методы прогнозирования ветвлений часто без необходимости потребляют мощность, когда поиски осуществляются в I-кэше и BTAC параллельно и поиски завершаются ошибкой в BTAC. Этот вывод более очевиден, когда есть удачное обращение в I-кэш и неудачное обращение в BTAC, которое, вероятно, обусловлено тем, что I-кэш типично хранит все типы команд, а BTAC типично хранит адреса команд ветвления.

Согласно одному варианту осуществления раскрыт способ сокращения поисков в кэше целевых адресов ветвлений (BTAC). В этом способе целевой адрес ветвления извлекается от BTAC в ответ на неудачное обращение при поиске адреса команды в кэше команд (I-кэше). Целевой адрес ветвления ассоциируется с адресом команды. Целевой адрес ветвления, извлеченный из BTAC, сохраняется в I-кэше. С помощью этих раскрытых методов, последующие адреса команд преимущественно отыскиваются в I-кэше, непараллельно с BTAC, таким образом экономя мощность за счет сокращения бесполезных поисков в BTAC.

Согласно другому варианту осуществления раскрывается способ сохранения команд ветвления в кэш команд. Этот способ включает в себя поиск адреса команды ветвления в кэше команд (I-кэше), извлечение целевого адреса ветвления из кэша целевых адресов ветвлений (BTAC) в ответ на неудачное обращение в I-кэш и сохранение целевого адреса ветвления в записи I-кэша.

Другой вариант осуществления относится к системе для сокращения поисков в кэше целевых адресов ветвлений (BTAC). Система включает в себя BTAC и кэш команд (I-кэш), выполненный с возможностью извлекать целевой адрес ветвления от BTAC в ответ на неудачное обращение в кэш при поиске первого адреса команды ветвления. I-кэш дополнительно выполнен с возможностью сохранять целевой адрес ветвления.

Следует понимать, что другие варианты осуществления настоящего изобретения должны стать понятными специалистам в данной области техники из последующего подробного описания, в котором различные варианты осуществления изобретения показаны и описаны в качестве иллюстрации. Следует принимать во внимание, что изобретение допускает другие и отличающиеся варианты осуществления, и его определенные детали допускают модификацию в различных других отношениях без отступления от настоящего изобретения. Следовательно, чертежи и подробное описание должны рассматриваться как иллюстративные, а не ограничительные по своей природе.

Краткое описание чертежей

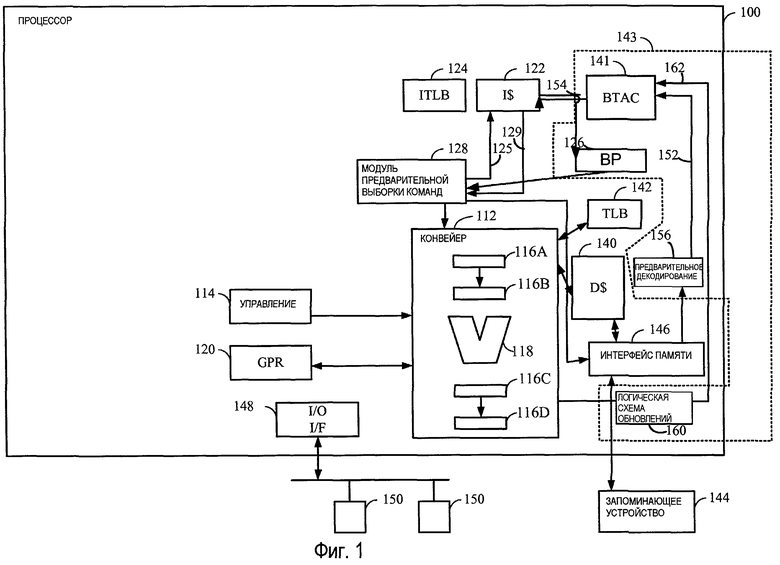

Фиг.1 - функциональная блок-схема примерного процессора.

Фиг.2A-2C (совместно фиг.2) иллюстрируют распечатку примерного кодового сегмента и примерного содержимого I-кэша и BTAC, когда I-кэш не содержит команду ветвления из кодового сегмента.

Фиг.3 иллюстрирует примерное содержимое I-кэша по фиг.1 после того, как I-кэш заполнен данными команд из BTAC.

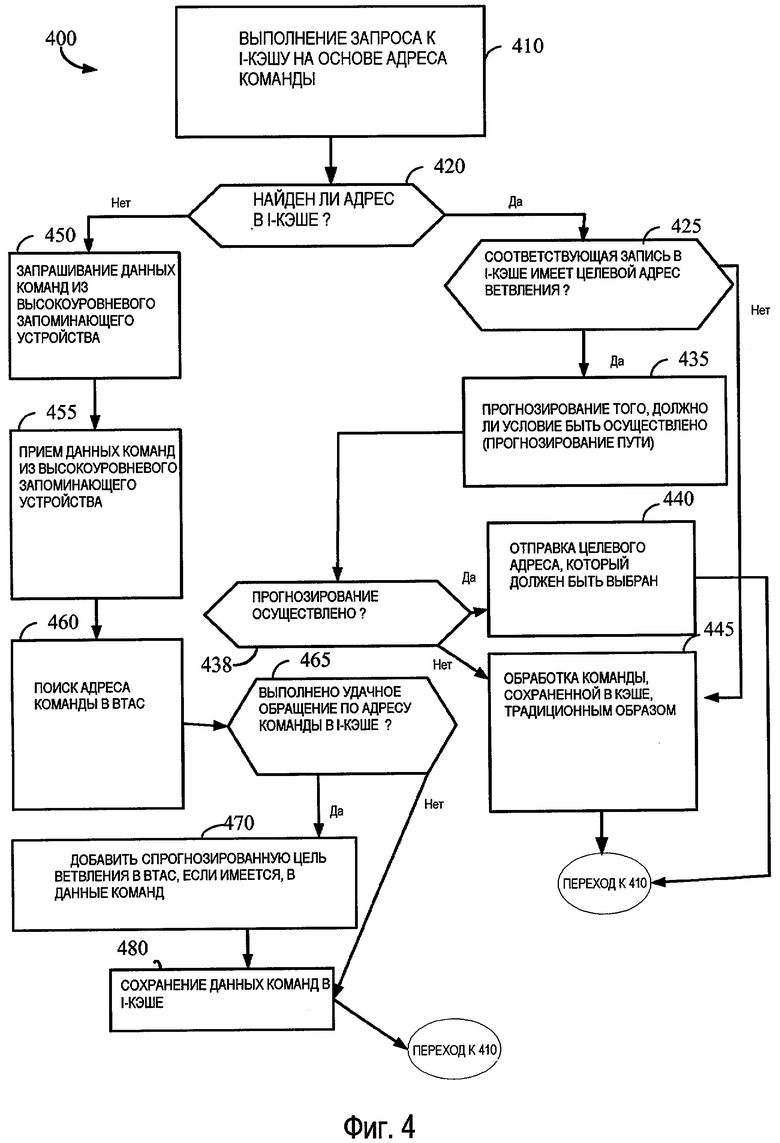

Фиг.4 - блок-схема, иллюстрирующая способ сохранения команды ветвления с косвенной адресацией в I-кэш и извлечения команды из I-кэша по фиг.1.

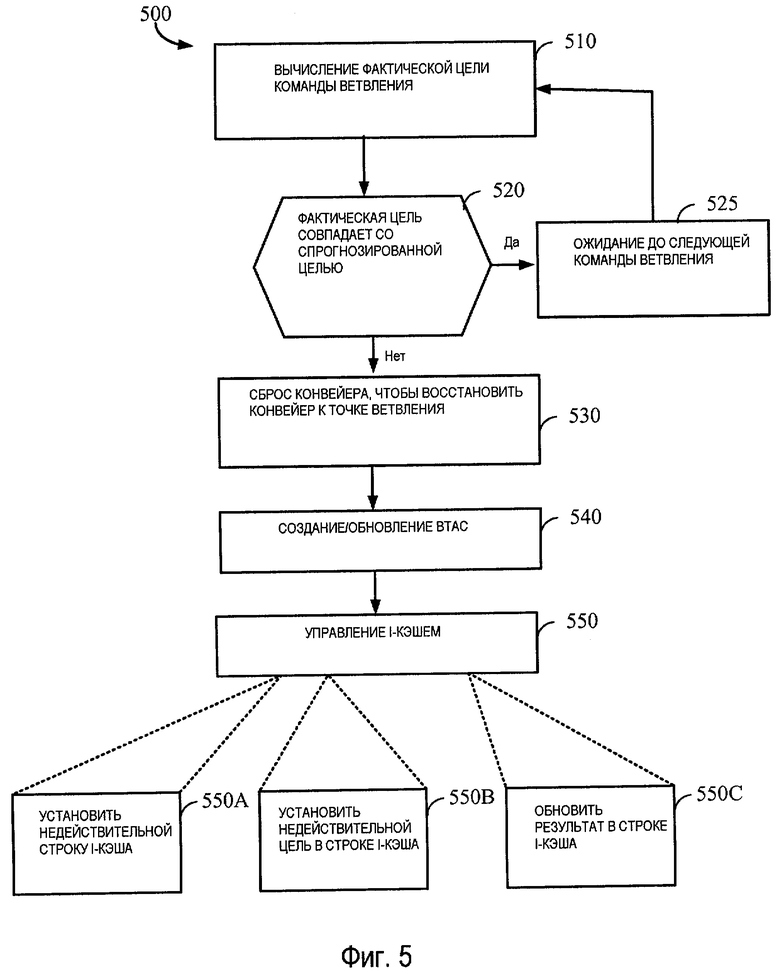

Фиг.5 - блок-схема, иллюстрирующая способ управления I-кэшем для фактической реализации ветвления.

Фиг.6 - функциональная блок-схема двух процессоров, совместно использующих BTAC.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Фиг.1 иллюстрирует функциональную блок-схему примерного процессора 100. Процессор 100 исполняет команды в конвейере 112 исполнения команд согласно управляющей логике 114. В некоторых вариантах осуществления конвейер 112 может иметь суперскалярную архитектуру с несколькими параллельными конвейерами, как подробнее описано в связи с фиг.6. Конвейер 112 включает в себя различные регистры или триггеры-защелки 116A-D, организованные в ступени конвейера, и один или более модулей исполнения, таких как арифметико-логическое устройство (ALU) 118. Файл 120 регистров общего назначения (GPR) предоставляет регистры, составляющие вершину иерархии памяти.

Доступ к данным осуществляется из кэша данных (D-кэша) 140, причем трансляция адресов памяти и разрешения управляются посредством основного буфера быстрого преобразования адреса (TLB) 142. В различных вариантах осуществления ITLB 124 может содержать копию части TLB 142. Альтернативно, ITLB 124 и TLB 142 могут быть интегрированы. Аналогично, в различных вариантах осуществления процессора 100 I-кэш 122 и D-кэш 140 могут быть интегрированы или объединены. Неудачные обращения в I-кэш 122 и/или D-кэш 140 вызывают доступ к основной (вне микросхемы) памяти 144 под управлением интерфейса 146 памяти. Неудачные обращения в I-кэш 122 подробнее описываются в связи с обсуждением фиг.4.

Процессор 100 может включать в себя интерфейс 148 ввода/вывода (I/O), управляющий доступом к различным периферийным устройствам 150. Специалистам в данной области техники должно быть понятно, что возможны многочисленные вариации процессора 100. Например, процессор 100 может включать в себя кэш второго уровня (L2) либо для одного из двух, либо для обоих I- и D-кэшей 122, 140. Помимо этого, один или более функциональных блоков, проиллюстрированных в процессоре 100, могут быть опущены в конкретном варианте осуществления.

Процессор 100 включает в себя систему 143 прогнозирования ветвлений. Система 143 прогнозирования ветвлений включает в себя BTAC 141, схему 126 модуля прогнозирования ветвлений (BP), логическую схему 160 обновлений и необязательную схему 156 предварительного декодирования. BTAC 141 выполнен с возможностью сохранять одну или более записей, где каждая запись содержит адрес команды ветвления и адрес результата ветвления, соответствующий адресу выборки. BTAC 141 может сохранять комбинацию адресов команд ветвления с прямой и косвенной адресацией.

I-кэш 122 и BTAC 141 заполняются по пути 152 заполнения, когда адрес команды отсутствует в I-кэше 122, и запрос, чтобы принять соответствующую команду из высокоуровневого запоминающего устройства по интерфейсу 146 памяти, выполнен. Как только команда принята из интерфейса 146 памяти, в первом варианте осуществления необязательная логическая схема 156 предварительного декодирования выполнена с возможностью определять, является ли принимаемая команда инструкцией ветвления с косвенной адресацией. Если является, адрес принимаемой команды отыскивается в BTAC 141 по пути 152, чтобы просмотреть, есть ли целевой адрес, ассоциированный с адресом принимаемой команды. Если выполнено удачное обращение в BTAC 141, принимаемая команда и соответствующий целевой адрес записываются в I-кэш 122. Неудачное обращение в I-кэш 122 и удачное обращение в BTAC 141 может произойти в случае, если команда ветвления с косвенной адресацией ошибочно спрогнозирована, таким образом вызывая некоторую недостоверность в I-кэше 122. Типы недостоверности I-кэша поясняются подробнее в связи с пояснением по фиг.5. Если адрес принимаемой команды не находится в BTAC 141 (к примеру, неудачное обращение), принимаемая команда записывается в I-кэш 122.

Второй вариант осуществления исключает логическую схему 156 предварительного декодирования. Во втором варианте осуществления команды, принимаемые через интерфейс 146 памяти, должны отыскиваться в BTAC 141 независимо от того, является ли принимаемая команда инструкцией ветвления с косвенной адресацией. В этом втором варианте осуществления команды, аналогично первому варианту осуществления, перенаправляются в I-кэш 122 для сохранения. Однако в первом варианте осуществления поиски BTAC ограничиваются командами ветвления с косвенной адресацией. В любом варианте осуществления, если целевой адрес ветвления сохраняется в BTAC 141, он также сохраняется в I-кэше 122.

Логика управления 160 обновлением добавляет целевой адрес к записи в BTAC 141 после того, как фактическая реализация ветвления осуществляется на более поздних стадиях конвейера 112 по пути 162. BTAC 141 обновляет I-кэш 122 по пути 154, чтобы включить и команду ветвления с косвенной адресацией, и ее соответствующий целевой адрес. Термин "прогноз не принят" упоминается как прогнозирование посредством BP-схемы 126 не перенаправлять конвейер 112 в соответствии с целевым адресом ветвления.

При управлении преобразования адресов памяти и разрешений посредством командного буфера быстрого преобразования адреса (ITLB) 124 модуль 128 предварительной выборки команд выбирает команды из кэша команд (I-кэша или I$) 122 по пути 125. Если выбранная команда обнаружена (к примеру, удачное обращение) в I-кэше 122, и выбранная команда ассоциирована с соответствующим целевым адресом ветвления, BP-схема 126 прогнозирует то, принять или нет путь выполнения кода, начинающийся с целевого адреса. Если BP-схема 126 прогнозирует, что целевой адрес должен быть принят, модуль 128 предварительной выборки команд корректирует свой счетчик команд, чтобы начать выборку команд из целевого адреса, тем самым перенаправляя конвейер 112 в соответствии с целевым адресом ветвления. Если BP-схема 126 прогнозирует, что целевой адрес не следует принимать, счетчик команд увеличивается, чтобы начать выборку команд из следующего последовательного адреса. Работа системы 143 прогнозирования ветвлений подробнее описывается в связи с обсуждением фиг.4 и 5.

Настоящее раскрытие изобретения рассматривает вариант осуществления комбинирования BTAC 141 и I-кэша 122 в интегральный компонент. Однако есть несколько причин для разделения BTAC и I-кэша на различные компоненты. Внешний BTAC, подобный описанному, опрашивается или считывается только в ходе заполнений в I-кэш. К традиционному BTAC, который размещается параллельно с I-кэшем, осуществляют доступ каждый раз, когда осуществляется доступ к I-кэшу. За счет ограничения обращения к BTAC, как раскрыто в данном документе, настоящее изобретение обеспечивает экономию энергии за счет сокращения действий в BTAC. Кроме того, этот нечастый доступ к BTAC позволяет BTAC 141 быть устройством с одним портом, тем самым уменьшая конструктивную сложность.

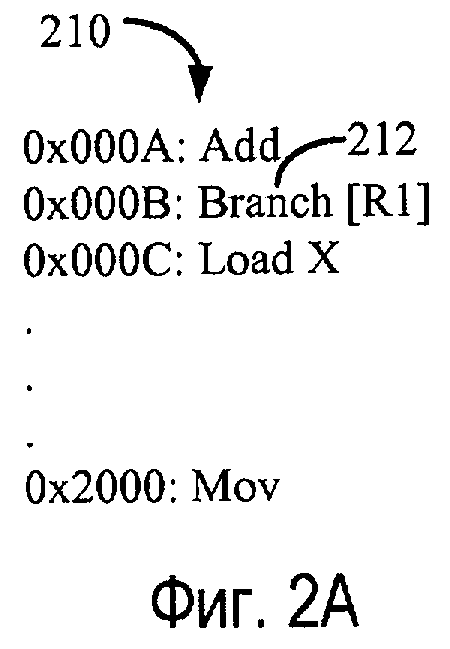

Фиг.2A иллюстрирует распечатку 210 примерного кодового сегмента, содержащего команду 212 ветвления с косвенной адресацией по адресу 0x000B. Как иллюстрировано, цель команды 212 ветвления с косвенной адресацией определяется содержимым регистра 1 (R1). Поскольку содержимое R1 может варьироваться каждый раз, когда команда 212 ветвления с косвенной адресацией выполняется, система 143 прогнозирования ветвлений используется для того, чтобы определять, следует ли перенаправлять процессорный конвейер 112, начиная с адреса, как указано содержимым R1.

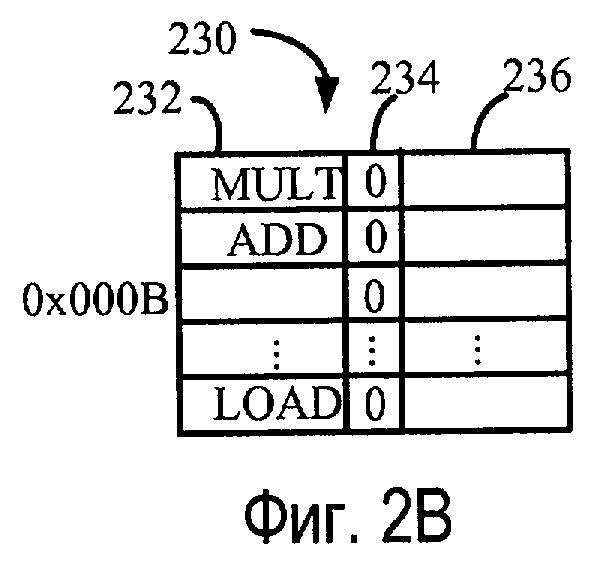

Фиг.2B иллюстрирует примерное содержимое I-кэша 230. I-кэш 230 может соответственно быть аналогичен I-кэшу 122. I-кэш 230 включает в себя столбец 232 команды, столбец 234 допустимых битов и столбец 236 целевого адреса ветвления. Запись в столбце 232 представляет команду. Согласно условному обозначению значение "0" в столбце 234 указывает то, что цель ветвления, если имеется, в столбце 236 недействительна, тогда как значение "1" в столбце 234 указывает то, что цель ветвления в столбце 236 далее в той же самой строке действительна. Как показано, I-кэш 230 в момент времени, когда счетчик команд указывает на адрес 0x000B, не содержит записи для команды 212 ветвления с косвенной адресацией по адресу 0x000B.

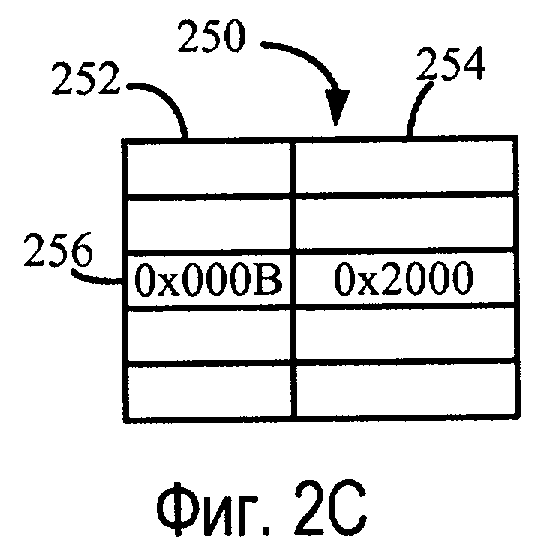

Фиг.2C иллюстрирует примерное содержимое BTAC 250. BTAC 250 может соответственно быть аналогичным BTAC 141. BTAC 250 включает в себя столбец 252 адреса команды ветвления и столбец 254 целевого адреса. Столбец 252 может включать в себя адреса команды ветвления с прямой адресацией, адреса команды ветвления с косвенной адресацией или любую комбинацию указанного. В момент времени, когда счетчик команд указывает на адрес 0x000B, BTAC 250 содержит адрес 256 команды ветвления с косвенной адресацией и ее соответствующий целевой адрес. Следовательно, логика 114 управления будет предписывать команде 256 ветвления и ее соответствующему целевому адресу в BTAC 250 сохранить I-кэш 230 при неудачном обращении в I-кэш. Следует отметить, что другая информация может быть сохранена и в I-кэше 230, и в BTAC 250, и что различные организации I-кэша 230 и BTAC 250 допускаются настоящим раскрытием.

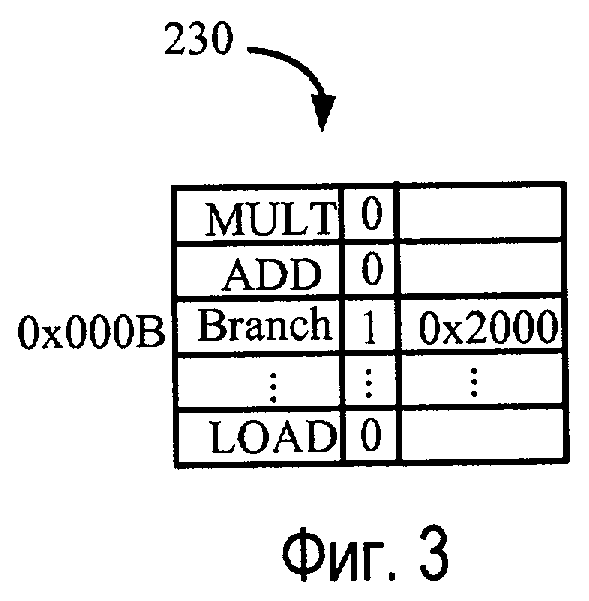

Фиг.3 иллюстрирует I-кэш 230 после того, как команда ветвления с косвенной адресацией, ассоциированная с адресом 256 команды ветвления с косвенной адресацией, и ее соответствующий целевой адрес (0x2000) сохраняются в I-кэше 230 по адресу 0x000B. Следовательно, следующий раз, когда счетчик команд процессора указывает на адрес 0x000B, поиск в I-кэше является удачным обращением, и целевой адрес 0x2000 назначается счетчику команд процессора, чтобы начать перенаправление конвейера 112 с командами по адресу 0x2000. По сравнению с традиционными BTAC, поиск в I-кэше в настоящем изобретении выполняется для предварительно выбранной команды без выполнения поиска в BTAC, экономя потребляемую мощность за счет сокращения количества поисков BTAC. Как продемонстрировано, поиски в BTAC 250 ограничены ситуациями, когда конкретная команда ветвления с косвенной адресацией не обнаружена в I-кэше 230.

Фиг.4 - это блок-схема, иллюстрирующая способ 400 сохранения команды ветвления с косвенной адресацией в I-кэше и извлечения целевого адреса ветвления из I-кэша по фиг.1. Этапы 410, 420, 450, 455, 460, 465, 470 и 480 определяют процесс, чтобы сохранять команду ветвления с косвенной адресацией и целевой адрес ветвления в I-кэше, таком как I-кэш 122 по фиг.1. Этапы 410, 420, 425, 435, 438, 440 и 445 определяют процесс извлечения целевого адреса ветвления из I-кэша. На этапе 410 выполняется запрос к I-кэшу для команды на основе адреса команды. Например, адрес команды, сохраненный в счетчике команд процессора, может быть использован для того, чтобы выполнить запрос к I-кэшу. На этапе 420 способ 400 определяет, есть ли удачное обращение в I-кэш. Если нет (неудачное обращение в кэш), способ 400 переходит к этапу 450, чтобы извлечь соответствующие данные команд из высокоуровневого запоминающего устройства. На этапе 450 данные команд запрашиваются из высокоуровневого запоминающего устройства, такого как кэш второго уровня (L2) или запоминающее устройство вне микросхемы. На этапе 455 принимаются извлеченные данные команд из высокоуровневого запоминающего устройства. На этапе 460 адрес команды отыскивается в BTAC. На этапе 465 способ 400 определяет, является ли адрес команды удачным обращением в BTAC, или, другими словами, совпадает ли он с адресом команды, сохраненным в BTAC. Если адрес команды является удачным обращением в BTAC, способ 400 переходит к этапу 470, где спрогнозированная цель ветвления, если имеется, сохраненная в BTAC, добавляется к данным команды. При удачном обращении в BTAC спрогнозированная цель ветвления, вероятно, сохраняется в BTAC так долго, как целевой адрес ветвления предыдущего экземпляра команды ветвления с косвенной адресацией был разрешен. Способ 400 переходит к этапу 480, где данные команд сохраняются в I-кэш.

В соответствии с этапом 465, если адрес команды является неудачным обращением в BTAC, способ 400 переходит к этапу 480. Этот переход от этапа 465 к этапу 480 указывает случай, когда запрошенный адрес команды не находится ни в I-кэше, ни в BTAC. В этом случае целевой адрес ветвления должен быть сохранен в BTAC после разрешения фактической цели ветвления для извлеченных данных команд, которое выполняется позднее в процессорном конвейере, как пояснено подробнее в связи с фиг.6. Когда фактическая цель ветвления разрешена, например, логическая схема 160 обновлений будет предписывать как BTAC, так и I-кэшу сохранять разрешенную цель ветвления.

Оба этапа 465 и 475 переходят к этапу 480, где данные команд сохраняются в I-кэш. Иначе, счетчик команд последовательно увеличивается. Способ 400 затем переходит к этапу 410, чтобы выполнить запрос следующего адреса, как указано счетчиком команд.

Возвращаясь к этапу 420, если есть удачное обращение в I-кэш, что означает наличие соответствующей записи в I-кэше, способ 400 переходит к этапу 425. На этапе 425 способ 400 определяет, есть ли у соответствующей записи в I-кэше целевой адрес ветвления. В одном варианте осуществления этап 425 может быть выполнен посредством опроса соответствующего допустимого бита, такого как сохраненный в столбце 234 допустимых битов по фиг.2. Если нет действительного целевого адреса ветвления, ассоциированного с удачным обращением в I-кэш, адрес команды не является инструкцией ветвления с косвенной адресацией. Таким образом, способ 400 переходит к этапу 445, где команда без ветвления извлекается из I-кэша и обрабатывается традиционным способом. Способ 400 переходит к этапу 410 для выполнения запроса следующего адреса из I-кэша, как указано счетчиком команд.

Если есть действительный целевой адрес ветвления, соответствующий записи, способ 400 переходит к этапу 435. На этапе 435 способ 400 прогнозирует, должен ли приниматься целевой адрес ветвления, хранимый в соответствующей записи. В одном варианте осуществления схема 126 прогнозирования ветвлений выполняет это прогнозирование. Следует отметить, что специалистам в данной области техники должно быть понятно, что методы прогнозирования ветвлений могут использовать статистику, эвристику, заранее определенные параметры и т.п. На этапе 438 способ 400 проверяет, должно ли быть осуществлено прогнозирование. Если должно, способ 400 переходит к этапу 440, на котором целевой адрес ветвления отправляется счетчику команд, такому как модуль 128 предварительной выборки команд, чтобы команды начали выбираться из целевого адреса ветвления. Способ 400 переходит к этапу 410, чтобы выполнить запрос следующего адреса, как указано счетчиком команд, которым в этом пути через блок-схему последовательности операций является целевой адрес ветвления.

Возвращаясь к этапу 438, если путь прогнозируется как не принятый, способ 400 переходит к этапу 445, чтобы обработать команду, сохраненную в кэше традиционным способом. После этапа 445 способ 400 переходит к этапу 410 для выполнения запроса следующего адреса в счетчике команд, которым в этой ветви блок-схемы является последовательный адрес после команды ветвления с косвенной адресацией, такой как, к примеру, адрес 0x000C на фиг.2A.

Фиг.5 - это блок-схема, иллюстрирующая способ 500 управления I-кэшем для разрешения фактического ветвления. Способ 500 выполняется для случаев, когда фактическая цель ветвления команды ветвления с косвенной адресацией вычисляется первый раз, и когда механизм прогнозирования, такой как схема 126 прогнозирования ветвлений, ошибочно прогнозирует цель команды ветвления с косвенной адресацией. На этапе 510 разрешается фактическая цель команды ветвления с косвенной адресацией. Такое разрешение ветвления может быть выполнено, поскольку команда ветвления с косвенной адресацией обрабатывается позже в процессорном конвейере.

На этапе 520 способ 500 определяет, совпадает ли фактическая цель со спрогнозированной целью или, для случая, когда фактическая цель вычисляется первый раз, что нет никакого спрогнозированного результата. Если фактическая цель ветвления действительно совпадает со спрогнозированной целью ветвления, ни BTAC, ни I-кэш не должны обновляться. Способ 500 переходит к этапу 525, на котором он ждет следующую команду ветвления перед переходом назад к этапу 510.

Если фактическая цель ветвления не совпадает со спрогнозированной целью, способ 500 обнаруживает ошибочное прогнозирование и переходит к этапу 530. По меньшей мере, две ситуации могут приводить к несовпадению. Первая ситуация может возникать, когда команда ветвления с косвенной адресацией выполняется в первый раз после сохранения перед этим в BTAC и I-кэше без результата ветвления. В первой ситуации следующая последовательная команда после команды ветвления с косвенной адресацией, возможно, загружена в процессорный конвейер. Вторая ситуация может возникнуть, если спрогнозированный целевой адрес отличается от фактического разрешенного целевого адреса. Во второй ситуации следующая команда, указанная в спрогнозированном целевом адресе, возможно, загружена в процессорный конвейер.

На этапе 530 процессорный конвейер в любом случае сбрасывает свои команды из конвейера, чтобы восстановить конвейер к точке ветвления, которой является в данном случае адрес команды ветвления с косвенной адресацией. Следовательно, команды, загруженные в процессорный конвейер после команды ветвления с косвенной адресацией независимо от того, загружены эти команды, начиная со спрогнозированного целевого адреса или со следующего последовательного адреса после команды ветвления с косвенной адресацией, будут сброшены из процессорного конвейера. На этапе 540 BTAC обновляется, чтобы сохранить фактический целевой адрес ветвления в своем поле целевого адреса ветвления, таком как столбец 254.

На этапе 550 управляется I-кэш. Например, логическая схема 114 управления может включать в себя логику, чтобы реализовать этапы 550A-550C. Этапы 550A-550C являются альтернативными вариантами осуществления этапа 550. На этапе 550A строка кэша, соответствующая спрогнозированному целевому адресу, устанавливается недействительной. На этапе 550B цель ветвления строки кэша, соответствующей спрогнозированному целевому адресу, устанавливается недействительной. На этапе 550C целевой адрес ветвления строки кэша, соответствующей спрогнозированному целевому адресу, обновляется так, чтобы отразить фактический целевой адрес. Этап 550C предпочтителен, когда команда ветвления с косвенной адресацией выполняется в первый раз после сохранения перед этим в BTAC и I-кэше без цели ветвления.

Фиг.6 - это функциональная блок-схема двух процессоров 601 и 602, совместно использующих общий BTAC 611. Совместно используемый BTAC 611 и процессоры 601 и 602 предпочтительно осуществлены в одной интегральной микросхеме. Процессор 601 включает в себя собственный многостадийный процессорный конвейер 620, I-кэш 610 и схему 615 прогнозирования ветвлений. На стадии 625 фактическое разрешение ветвления осуществляется, чтобы обновить BTAC 611 и I-кэш 610 с помощью команды ветвления с косвенной адресацией и целевого адреса ветвления, как ранее описано на фиг.4 и 5, соответственно. Процессор 602 включает в себя собственный многостадийный процессорный конвейер 640, I-кэш 630 и схему 635 прогнозирования ветвлений. На стадии 645 фактическое разрешение ветвления осуществляется, чтобы обновить BTAC 611 и I-кэш 630 с помощью команды ветвления с косвенной адресацией и целевого адреса ветвления, как ранее описано на фиг.4 и 5, соответственно. Как проиллюстрировано, фактическое разрешение ветвления может быть выполнено на различных стадиях в процессорном конвейере. Хотя фиг.6 иллюстрирует общий BTAC, совместно используемый между двумя процессорами, следует отметить, что настоящее раскрытие допускает совместное использование общего BTAC между тремя или более процессорами. При работе, когда адрес выбирается из I-кэша 610 или из I-кэша 630, который содержит действительный целевой адрес ветвления, соответствующие конвейеры 620 и 640 начинают упреждающую выборку команд, начиная с целевого адреса ветвления.

Различные иллюстративные логические блоки, модули, схемы, элементы и/или компоненты, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы или выполнены с помощью процессора общего назначения, процессора цифровых сигналов (DSP), специализированной интегральной схемы (ASIC), программируемой пользователем матричной БИС (FPGA) или другого программируемого логического устройства, дискретного логического элемента или транзисторной логики, дискретных компонентов аппаратных средств либо любой комбинации вышеозначенного, спроектированной так, чтобы выполнять описанные в данном документе функции. Процессором общего назначения может быть микропроцессор, но в альтернативном варианте процессором может быть любой традиционный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть реализован как сочетание вычислительных компонентов, к примеру, сочетание DSP и микропроцессора, множество микропроцессоров, один или более микропроцессоров вместе с ядром DSP либо любая другая подобная конфигурация.

Способы, описанные в связи с раскрытыми в данном документе вариантами осуществления, могут быть реализованы непосредственно в аппаратных средствах, в программном модуле, приводимом в исполнение процессором, или в их комбинации. Программный модуль может постоянно размещаться в оперативной памяти, флэш-памяти, ПЗУ, памяти типа EPROM, памяти типа EEPROM, регистрах, на жестком диске, сменном диске, компакт-диске или любой другой форме носителя хранения данных, известной в данной области техники. Носитель хранения данных может быть соединен с процессором так, чтобы процессор мог считывать информацию и записывать информацию на носитель хранения данных. В альтернативном варианте носитель хранения данных может быть встроен в процессор.

Хотя изобретение раскрыто в контексте вариантов осуществления, следует принимать во внимание, что специалистами в данной области техники может быть использовано множество реализаций, согласованных с вышеприведенным описанием и прилагаемой формулой изобретения.

Изобретение относится к способам прогнозирования ветвлений в кэше целевых адресов ветвлений. Технический результат заключается в повышении быстродействия поиска за счет сокращения поисков в кэше целевых адресов ветвлений (ВТАС). Целевой адрес ветвления извлекается из ВТАС в ответ на неудачу при поиске адреса команды в кэше команд (I-кэше). Целевой адрес ветвления ассоциирован с адресом команды. Целевой адрес ветвления, извлеченный из ВТАС, сохраняется в I-кэше. С помощью заявленного способа последующие адреса команд отыскиваются в I-кэше, непараллельным образом с ВТАС, таким образом экономя мощность за счет сокращения бесполезных поисков в ВТАС. 3 н. и 18 з.п. ф-лы, 8 ил.

1. Способ сокращения поисков в кэше целевых адресов ветвлений (ВТАС) с использованием кэша команд (I-кэша), содержащий этапы, на которых:

извлекают первый целевой адрес ветвления из ВТАС в ответ на неудачу в поиске первого адреса команды для первой команды ветвления, сохраненной в I-кэше;

сохраняют первый целевой адрес ветвления, извлеченный из ВТАС, в I-кэше, в первом местоположении, ассоциированном с первым адресом команды;

причем I-кэш выполнен с возможностью хранения множества команд, включая первую команду ветвления, при этом первый целевой адрес команды ветвления, извлеченный из ВТАС и сохраненный в I-кэше, был предоставлен в ВТАС в ответ на определение предварительного разрешения ветвления для первой команды ветвления на этапе обработки конвейера; и

в ответ на поиск адреса первой команды в I-кэше извлекают первый целевой адрес ветвления из I-кэша, если первый целевой адрес ветвления сохранен в I-кэше.

2. Способ по п.1, дополнительно содержащий этап, на котором обнаруживают ошибочное прогнозирование, ассоциированное с первой командой ветвления.

3. Способ по п.2, дополнительно содержащий выполнение, по меньшей мере, одного из этапов, на которых:

признают недействительной строку I-кэша, ассоциированную с ошибочным прогнозированием;

признают недействительным целевой адрес ветвления в этой строке I-кэша; и

обновляют целевой адрес ветвления в I-кэше.

4. Способ по п.2, в котором обнаружение ошибочного прогнозирования содержит этапы, на которых:

вычисляют фактический целевой адрес ветвления, ассоциированный с первой командой ветвления; и

определяют, что фактический целевой адрес ветвления не согласуется с первым целевым адресом ветвления, сохраненным в I-кэше.

5. Способ по п.1, дополнительно содержащий этапы, на которых:

принимают второй целевой адрес ветвления из ВТАС в ответ на вторую неудачу в поиске второго адреса команды во втором I-кэше; и сохраняют второй целевой адрес ветвления во втором I-кэше, во втором местоположении, ассоциированном со вторым адресом команды.

6. Способ по п.1, в котором поиски в ВТАС ограничены ситуациями, когда конкретная команда ветвления с косвенной адресацией не найдена в I-кэше.

7. Способ по п.1, дополнительно содержащий этап, на котором ВТАС и I-кэш обновляют разрешенным целевым адресом, принятым из конвейера.

8. Способ по п.1, дополнительно содержащий этап, на котором обновляют I-кэш, путем предоставления данных разрешенного целевого адреса в I-кэш в ответ на определение разрешения ветвления в конвейере.

9. Способ сохранения команд ветвления в кэше команд (I-кэше), содержащий этапы, на которых:

выполняют поиск адреса команды ветвления, ассоциированного с командой ветвления, в кэше команд (I-кэше);

извлекают целевой адрес ветвления из кэша целевых адресов ветвлений (ВТАС) в ответ на неудачное обращение в I-кэш, ассоциированное с командой ветвления;

сохраняют целевой адрес ветвления, извлеченный из ВТАС, в записи в I-кэше;

причем запись ассоциирована с адресом команды ветвления в I-кэше;

причем целевой адрес ветвления, извлеченный из ВТАС, был предоставлен в ВТАС в ответ на определение предварительного разрешения ветвления для команды ветвления на этапе обработки конвейера; и

в ответ на поиск адреса команды ветвления в I-кэше извлекают целевой адрес ветвления из I-кэша, если целевой адрес ветвления сохранен в I-кэше.

10. Способ по п.9, дополнительно содержащий этап, на котором прогнозируют, что следующая команда, которая должна быть выбрана, ассоциирована с целевым адресом ветвления.

11. Способ по п.10, дополнительно содержащий этап, на котором обновляют целевой адрес ветвления в I-кэше, когда прогнозирование ошибочно.

12. Способ по п.11, в котором обновление целевого адреса ветвления дополнительно содержит этапы, на которых:

принимают, из конвейера, фактический целевой адрес ветвления для команды ветвления; и

заменяют целевой адрес ветвления, сохраненный в I-кэше и в ВТАС, фактическим целевым адресом ветвления.

13. Способ по п.9, дополнительно содержащий этапы, на которых:

выполняют поиск второго адреса команды ветвления во втором I-кэше;

извлекают второй целевой адрес ветвления из ВТАС в ответ на второе неудачное обращение в I-кэш; и

сохраняют второй целевой адрес ветвления, извлеченный из ВТАС, в первой записи во втором I-кэше.

14. Способ по п.9, в котором поиски в ВТАС ограничены ситуациями, когда конкретная команда ветвления с косвенной адресацией не найдена в I-кэше.

15. Устройство для сокращения поисков в кэше целевых адресов ветвлений (ВТАС) с использованием кэша команд (I-кэша), содержащее:

кэш целевых адресов ветвлений (ВТАС) и кэш команд (I-кэш), причем I-кэш сконфигурирован для: хранения команд, включая первую команду ветвления; извлечения целевого адреса ветвления из ВТАС в ответ на неудачное обращение в I-кэш при поиске первого адреса команды ветвления в I-кэше, причем первый адрес команды ветвления ассоциирован с первой командой ветвления, которая сохранена в I-кэше;

сохранения целевого адреса ветвления, извлеченного из ВТАС; и в ответ на поиск первого адреса команды ветвления в I-кэше, предоставления целевого адреса ветвления из I-кэша, если целевой адрес ветвления сохранен в I-кэше;

причем целевой адрес ветвления, извлеченный из ВТАС, был предоставлен в ВТАС в ответ на определение предварительного разрешения ветвления для первой команды ветвления на этапе обработки конвейера.

16. Устройство по п.15, дополнительно содержащее схему прогнозирования ветвлений, сконфигурированную для прогнозирования, что вторая команда, которая должна быть выбрана, ассоциирована с целевым адресом ветвления, сохраненным в I-кэше.

17. Устройство по п.16, в котором I-кэш сконфигурирован, чтобы предоставлять целевой адрес ветвления в ответ на запрос на выбор второй команды.

18. Устройство по п.17, дополнительно содержащее логическую схему обновлений, сконфигурированную, чтобы разрешать ошибочное прогнозирование второй команды, которая должна быть выбрана.

19. Устройство по п.18, дополнительно содержащее логическую схему управления, сконфигурированную, чтобы управлять I-кэшем, по меньшей мере, посредством одного из признания недействительной строки I-кэша, которая содержит этот целевой адрес ветвления, признания недействительным целевого адреса ветвления в этой строке I-кэша; и обновления целевого адреса ветвления в I-кэше.

20. Устройство по п.15, в котором ВТАС совместно используется двумя или более процессорами.

21. Устройство по п.15, в котором поиски в ВТАС ограничены ситуациями, когда конкретная команда ветвления с косвенной адресацией не найдена в I-кэше.

| US 4722050, 26.01.1988 | |||

| US 6427192 В1, 30.07.2002 | |||

| US 5136697, 04.08.1992 | |||

| RU 2004134452 А, 10.06.2006. |

Авторы

Даты

2011-05-27—Публикация

2007-08-15—Подача