Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ АВТОНОМНЫМ РОБОТОМ | 2008 |

|

RU2424105C2 |

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1612307A2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ВЫСОКОАДАПТИВНЫМ АВТОНОМНЫМ МОБИЛЬНЫМ РОБОТОМ | 2019 |

|

RU2705049C1 |

| Устройство для параллельной обработки трехмерных сцен | 1990 |

|

SU1817109A1 |

| Устройство обработки изображений | 1989 |

|

SU1817108A1 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1689966A1 |

| Устройство для параллельной обработки трехмерных сцен | 1986 |

|

SU1456965A1 |

| Устройство для моделирования графов Петри | 1986 |

|

SU1405070A1 |

| Матричное устройство для быстрого поиска вхождений и обработки данных | 2022 |

|

RU2787742C1 |

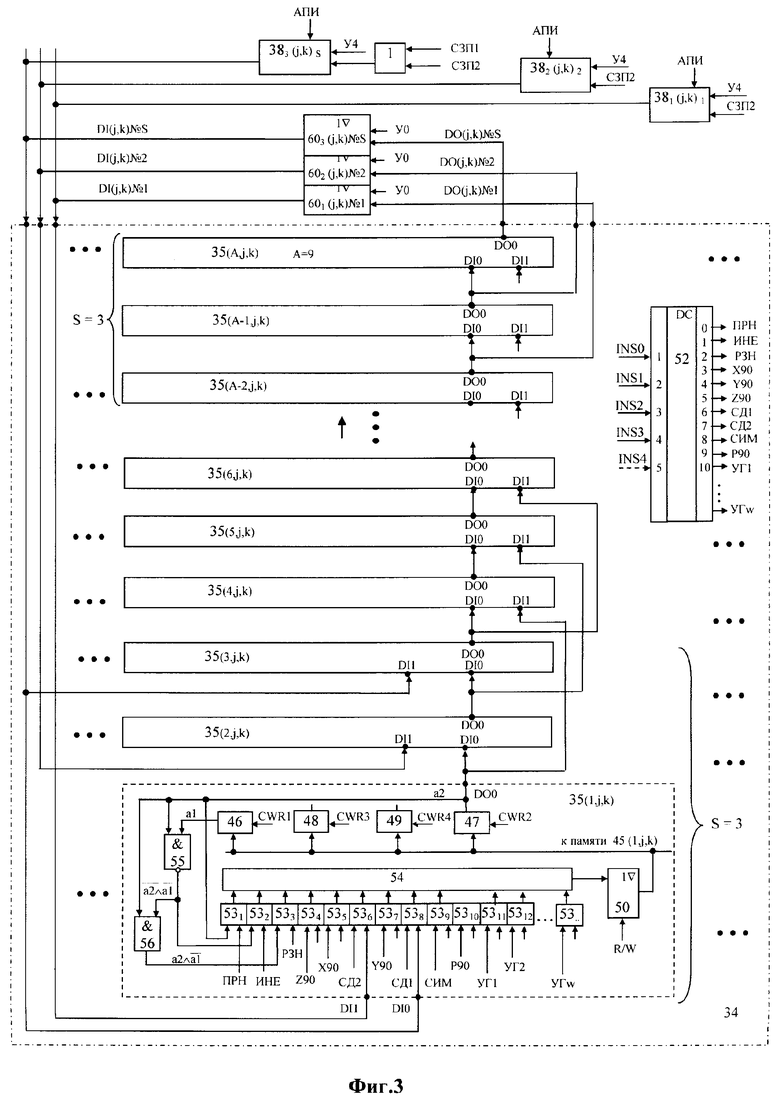

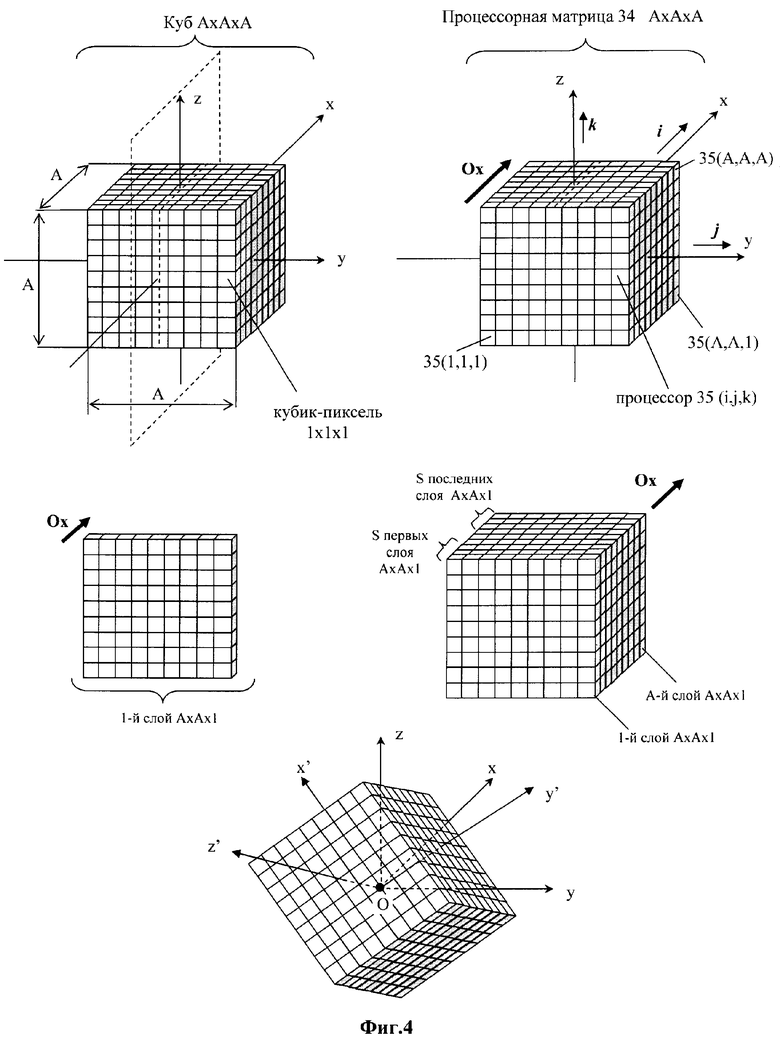

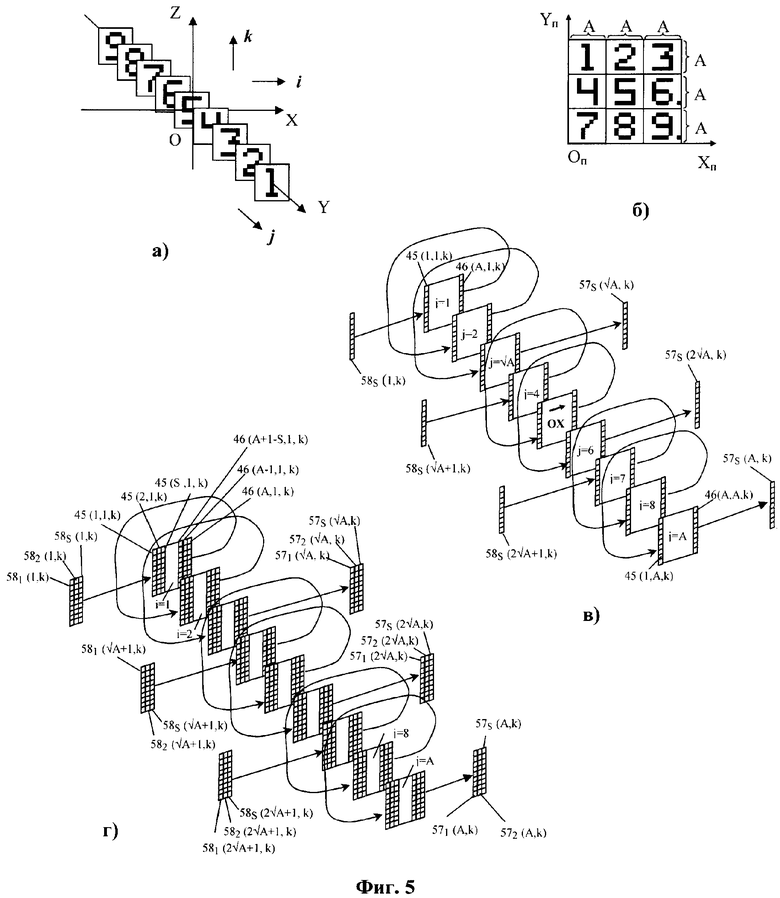

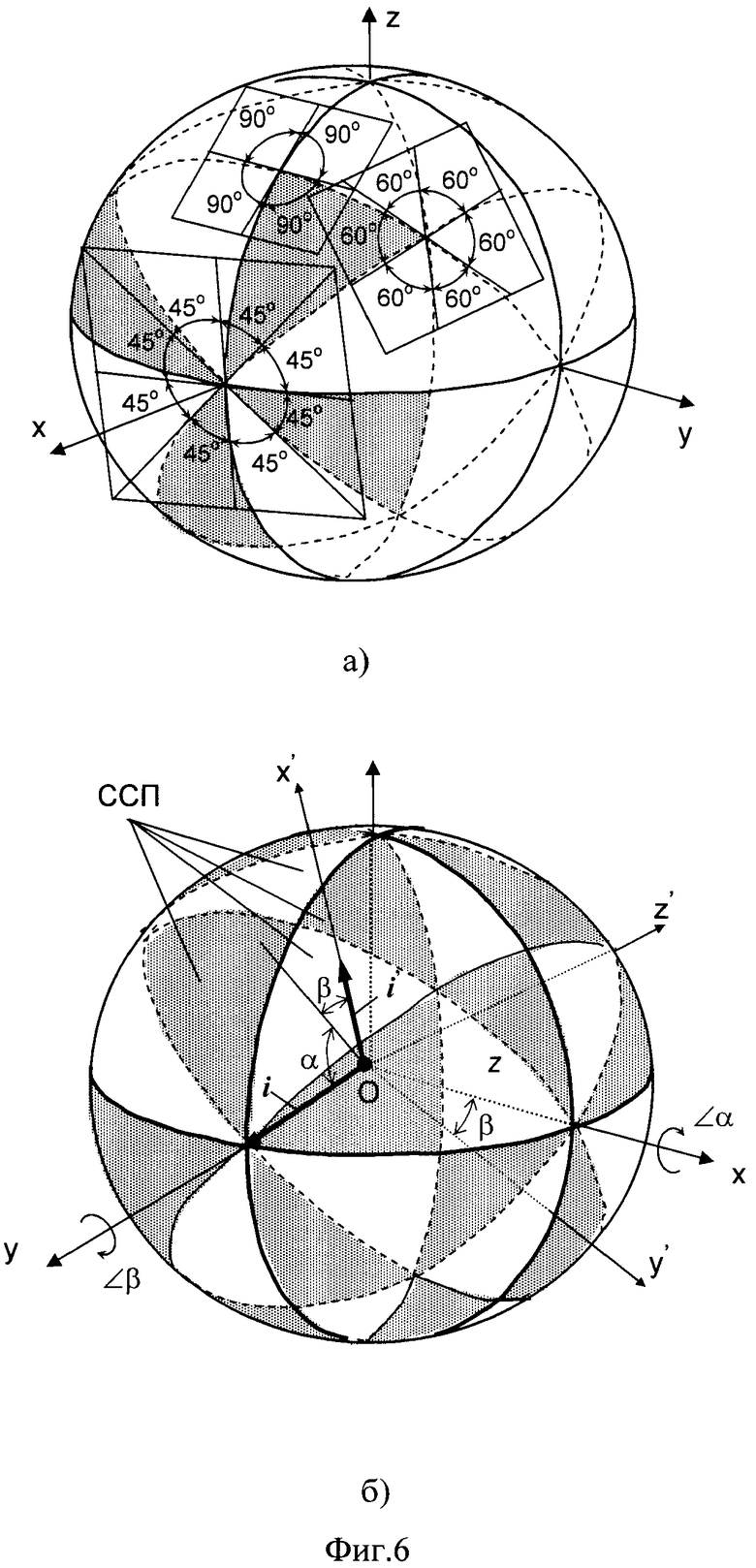

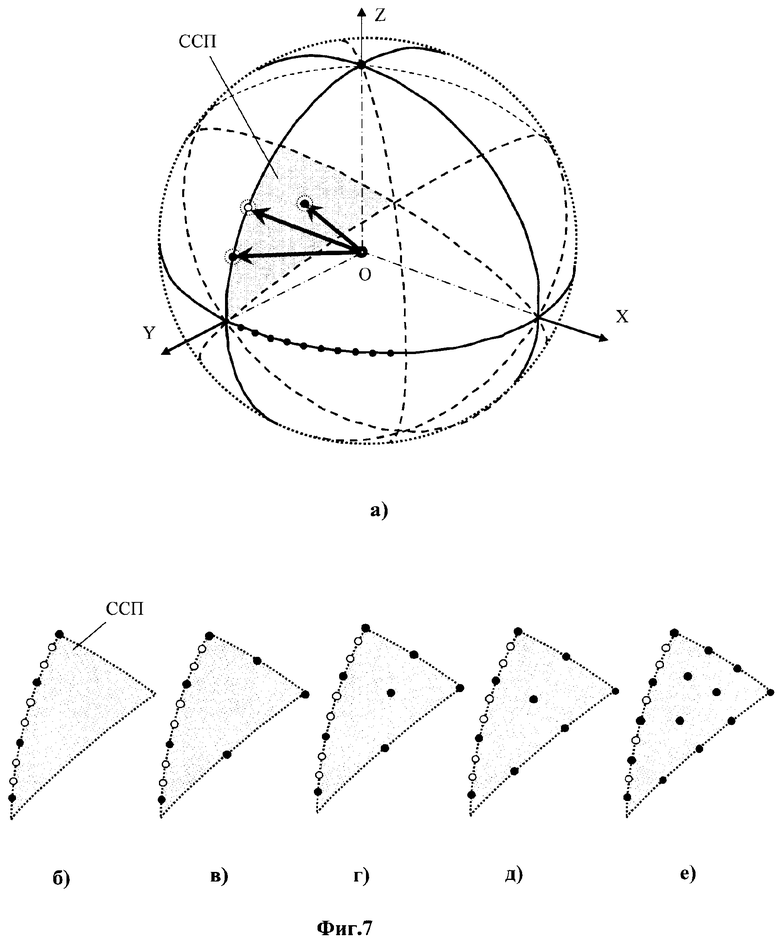

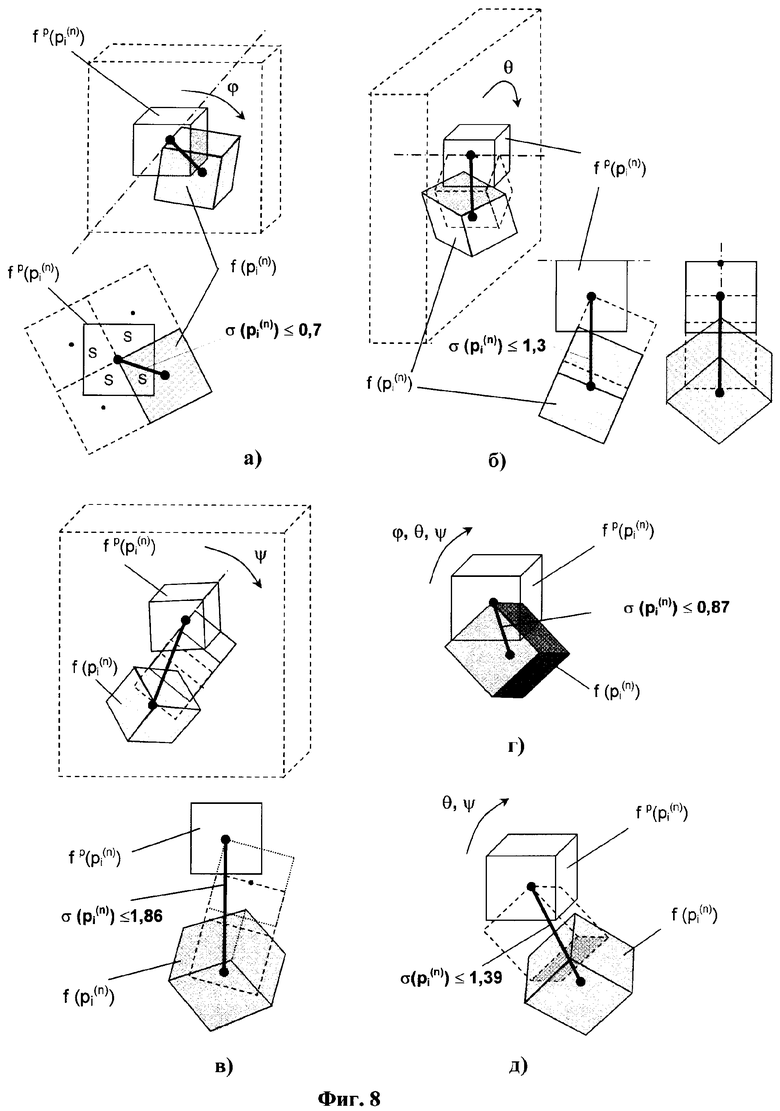

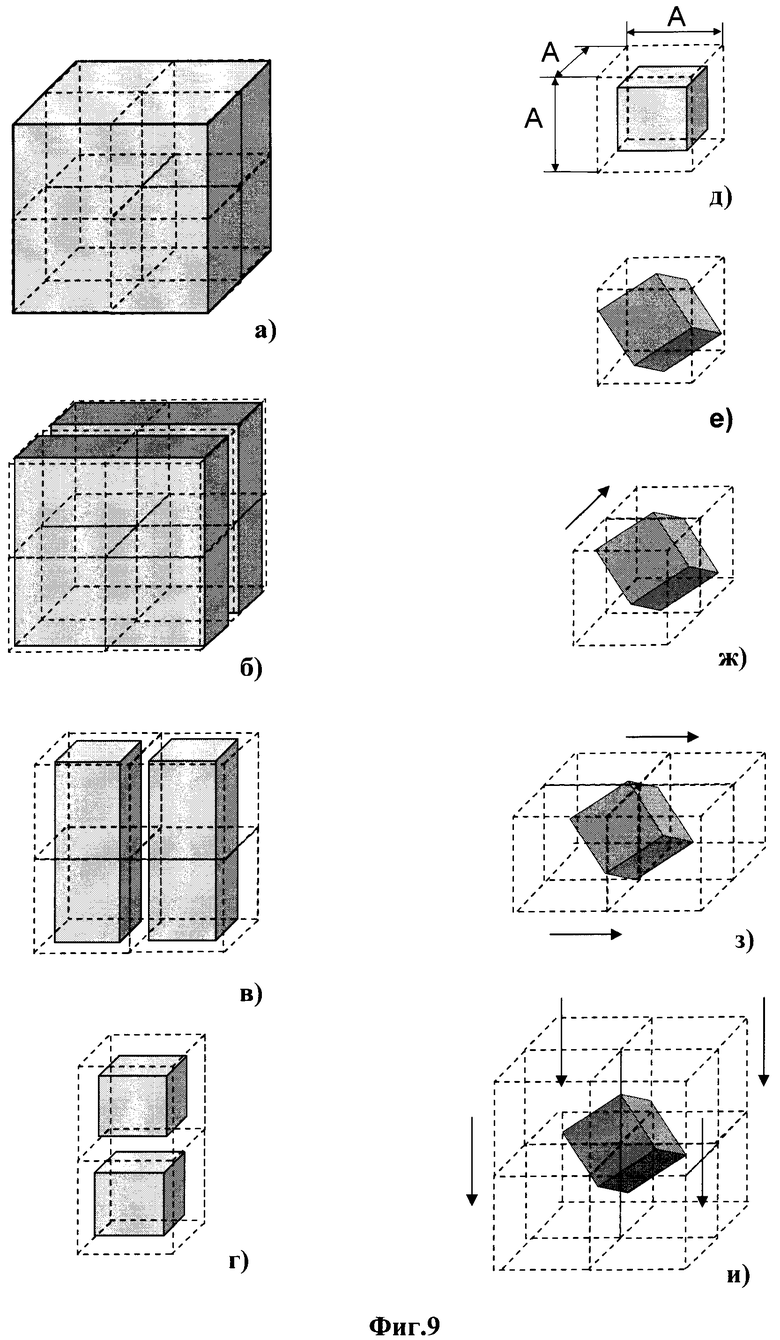

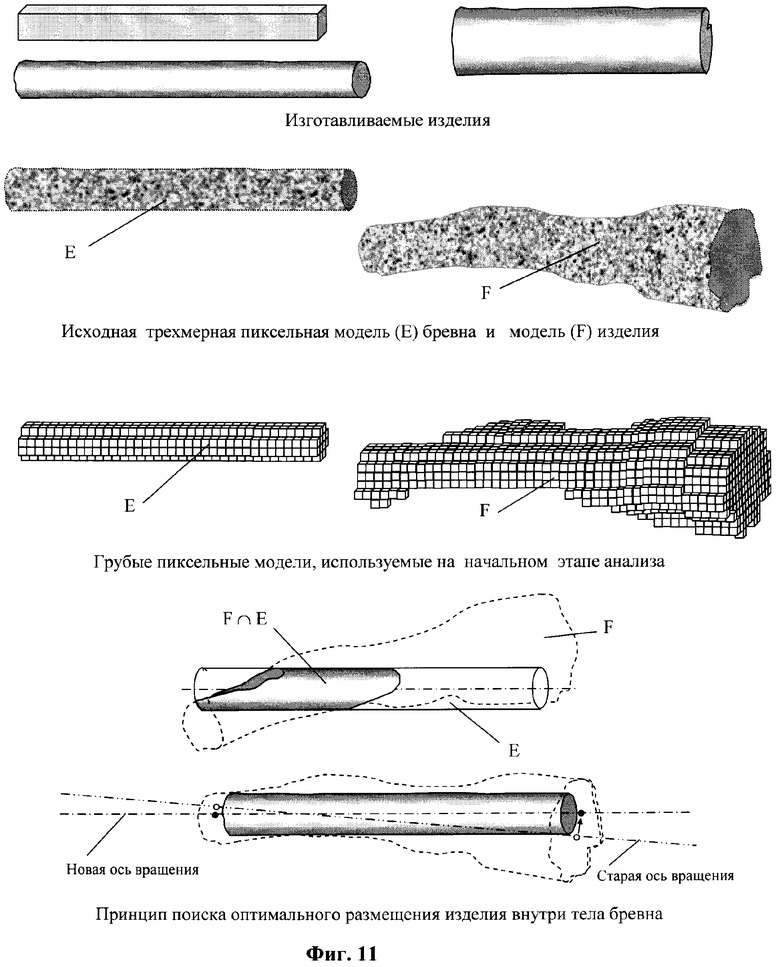

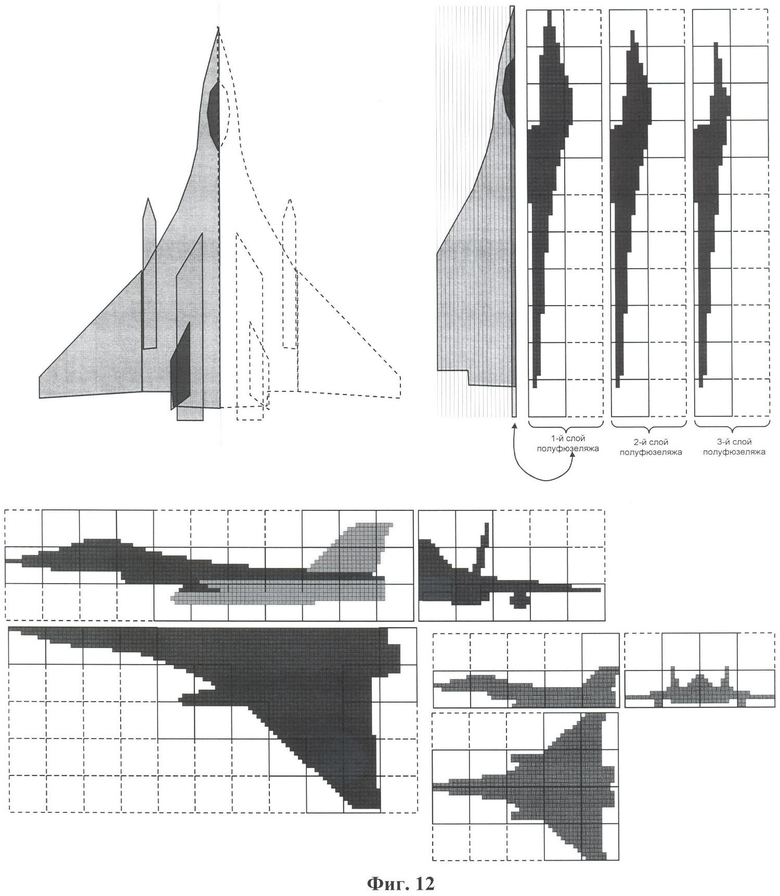

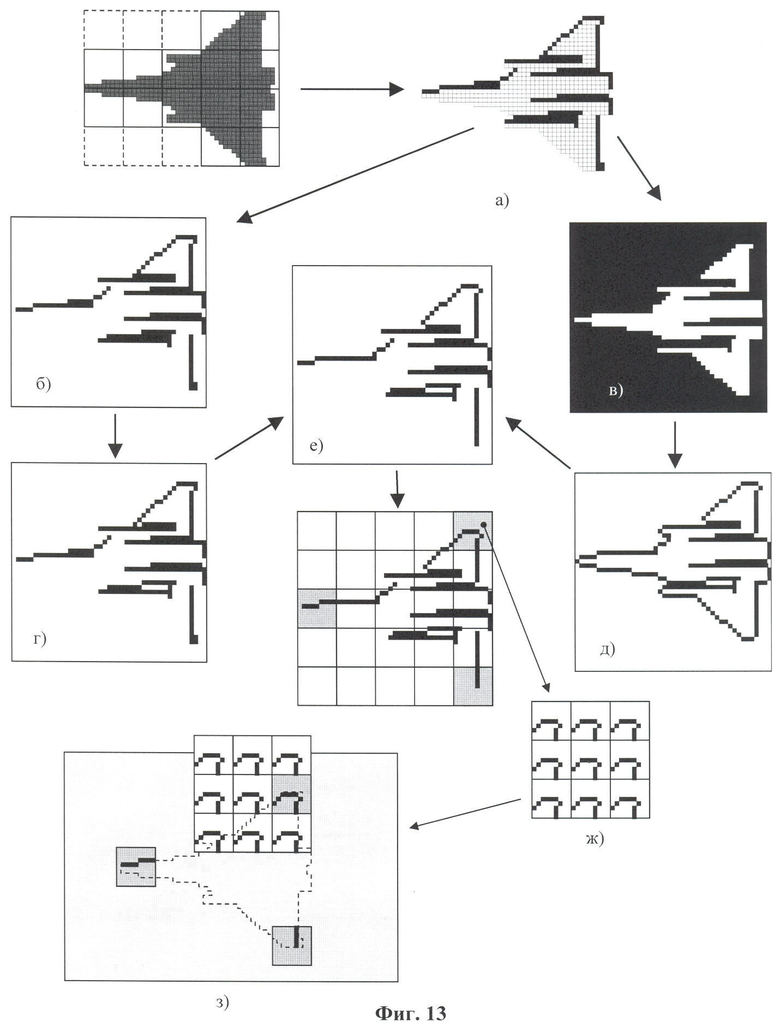

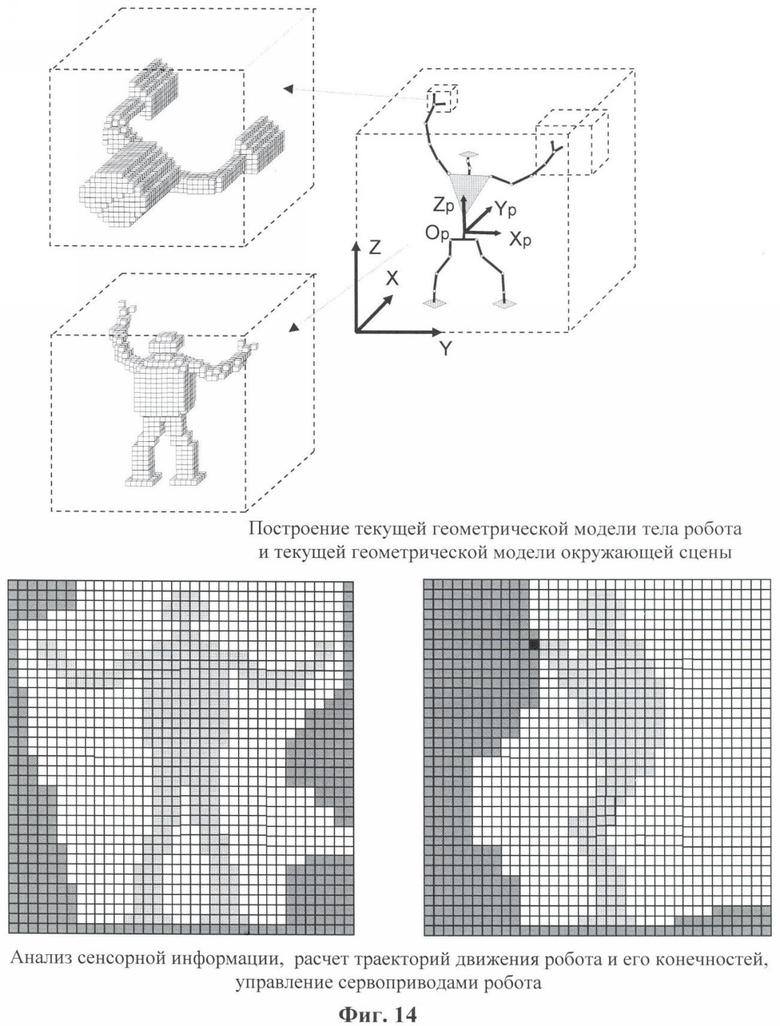

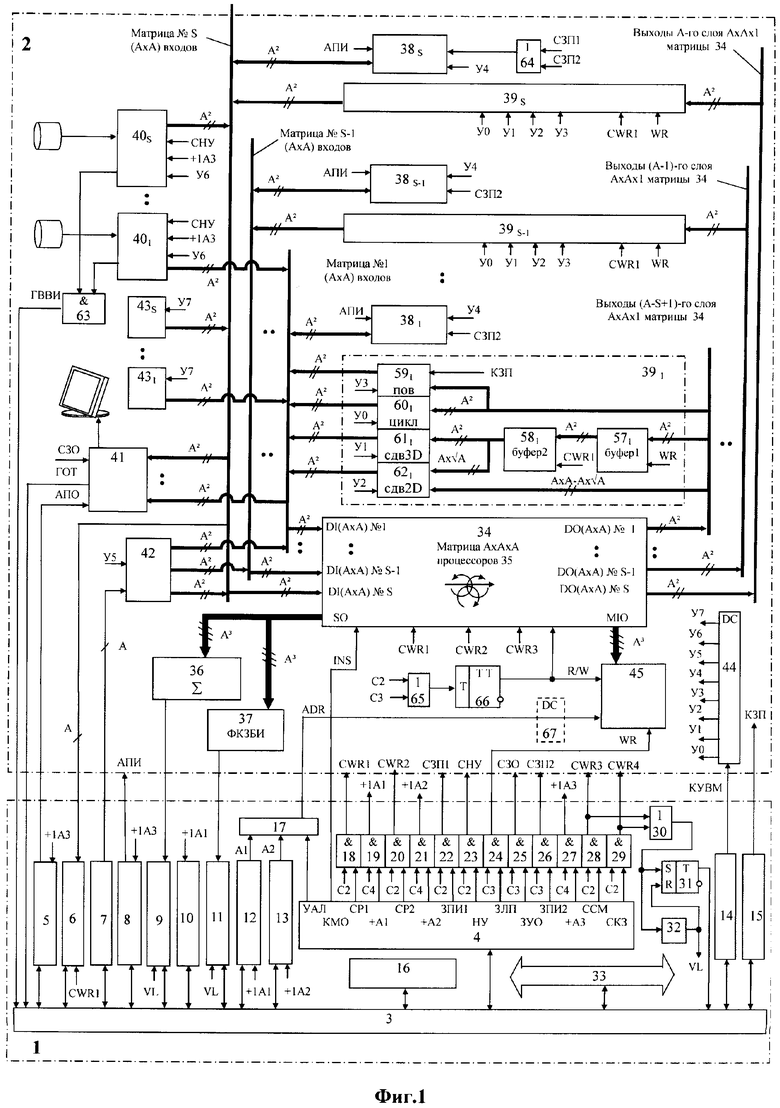

Изобретение относится к вычислительной технике и предназначено для решения задач обработки двухмерных и трехмерных изображений. Может быть применено в стационарных и бортовых системах технического зрения, в устройствах управления автономными роботами, в обрабатывающих станках с программным управлением, в системах автоматизированного проектирования. Технический результат заключается в повышении скорости и точности обработки плоских и пространственных изображений, снижении энергопотребления. Для этого в устройстве, содержащем блок управления, матрицу А×А×А одноразрядных процессоров, матрицу А×А одноразрядных узлов памяти изображений, А3-входовый узел определения объема, А3-входовый формирователь кода заполнения бинарного изображения А×А×А, матрицу А×А одноразрядных коммутаторов внутрислойного перемещения, увеличено число межпроцессорных связей внутри матрицы А×А×А, в результате при выполнении наиболее часто используемых команд поворота на угол некратный 90° вокруг центра бинарного изображения А×А×А поворачивается содержимое не одного слоя А×А×1 этого бинарного изображения, а содержимое всех его слоев A×A×1. 14 ил., 1 табл.

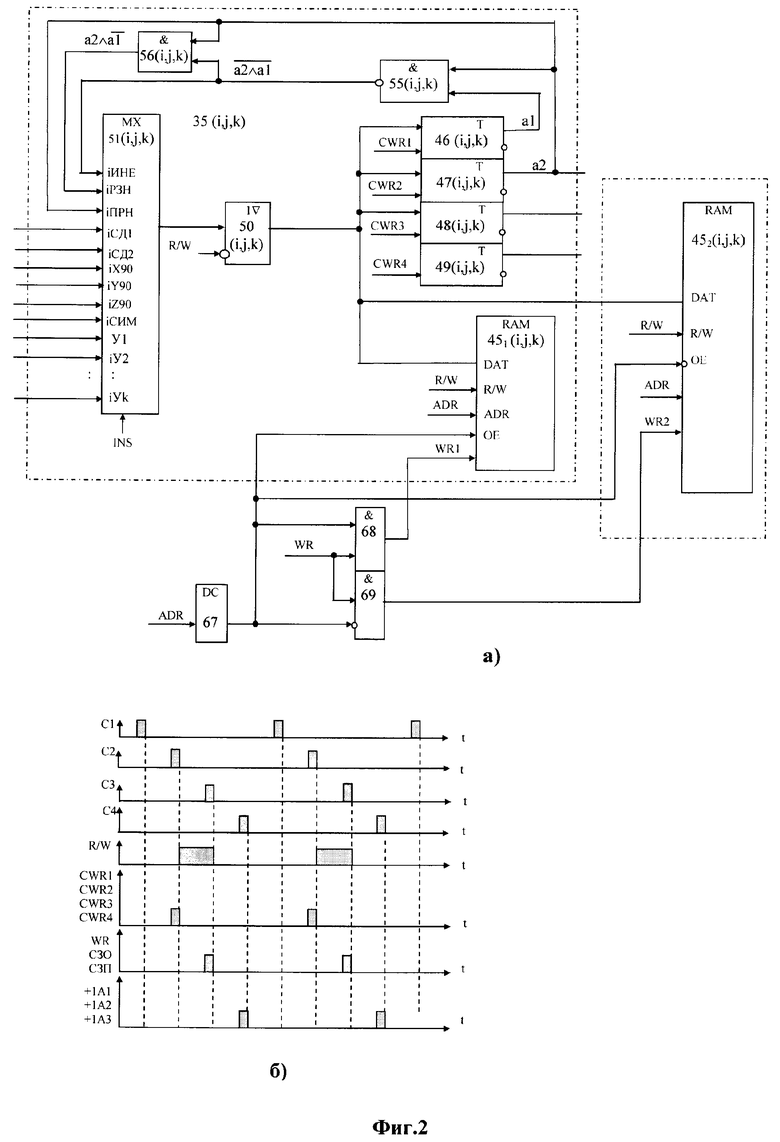

Устройство обработки двухмерных и трехмерных изображений, содержащее блок управления, матрицу А×А×А одноразрядных процессоров, имеющую матрицу А×А внешних входов и матрицу А×А внешних выходов, процессоры матрицы А×А×А взаимно однозначно соответствуют кубикам 1×1×1 куба А×А×А или квадратикам 1×1 квадрата  , а также матрицу А×А одноразрядных узлов памяти изображений, совмещенные входы-выходы которой соединены с одноименными внешними входами матрицы А×А×А процессоров, А3-входовый узел определения объема, А3-входовый формирователь кода заполнения бинарного изображения А×А×А, матрицу А×А одноразрядных коммутаторов внутрислойного перемещения, каждый из которых имеет один вход, соединенный с одноименным выходом матрицы А×А×А процессоров и четыре выхода, соединенных с соответствующими входами матрицы А×А×А процессоров, каждый (i,j,k)-й процессор матрицы А×А×А, где i=1…A, j=1…A, k=1…A, содержит (i,j,k)-й одноразрядный узел локальной памяти, (i,j,k)-й мультиплексор, выход которого соединен с информационным входом (i,j,k)-го узла локальной памяти, (i,j,k)-й первый регистр-триггер, (i,j,k)-й второй регистр-триггер, (i,j,k)-й третий регистр-триггер и (i,j,k)-й арифметико-логический узел, входы которого соединены с выходами (i,j,k)-го первого и (i,j,k)-го второго регистров-триггеров, а выходы соединены с первым и вторым входами (i,j,k)-го мультиплексора, третий вход (i,j,k)-го мультиплексора соединен с выходом (i,j,k)-го первого регистра-триггера, четвертый вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера (i-l,j,k)-го процессора, чей кубик 1×1×1 удален от кубика 1×1×1 (i,j,k)-го процессора на один шаг в направлении, противоположном оси Ох и параллельном ребру куба А×А×А и, где О - центр куба А×А×А, пятый вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера того процессора, чей кубик 1×1×1 отображается в кубик 1×1×1 (i,j,k)-го процессора при повороте на 90° вокруг оси Ох, шестой вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера того процессора, чей кубик 1×1×1 отображается в кубик 1×1×1 (i,j,k)-го процессора при повороте на 90° вокруг оси Оу, расположенной перпендикулярно оси Ох и направленной параллельно другому ребру куба А×А×А, каждый (i,j,k)-й вход узла определения объема соединен с выходом третьего (i,j,k)-го регистра-триггера, блок управления содержит центральный процессор с регистром микрослова и память программ и данных, отличающееся тем, что в каждом (i,j,k)-м процессоре матрицы А×А×А введен (i,j,k)-й двухвходовый ключ, информационный вход которого соединен с выходом (i,j,k)-го мультиплексора, управляющий вход соединен с выходом введенного двухтактного триггера, а выход соединен с входом (i,j,k)-го узла локальной памяти, вход и выход которого совмещены и выполнены в виде одного проводника, введен (i,j,k)-й четвертый регистр-триггер, выход которого соединен с (i,j,k)-м входом формирователя кода заполнения бинарного изображения А×А×А, информационный вход соединен с совмещенным входом-выходом (i,j,k)-й локальной памяти, управляющий вход соединен с выходом дополнительно введенной двухвходовой схемы И, информационный вход которой соединен с выходом дополнительно введенного разряда регистра микрослова, в каждом (i,j,k)-м многовходовом мультиплексоре введены седьмой информационный вход, соединенный с выходом (i-S,j,k)-го первого регистра-триггера, и восьмой информационный вход, соединенный с выходом первого регистра-триггера того процессора, чей квадратик 1×1 при повороте квадрата

, а также матрицу А×А одноразрядных узлов памяти изображений, совмещенные входы-выходы которой соединены с одноименными внешними входами матрицы А×А×А процессоров, А3-входовый узел определения объема, А3-входовый формирователь кода заполнения бинарного изображения А×А×А, матрицу А×А одноразрядных коммутаторов внутрислойного перемещения, каждый из которых имеет один вход, соединенный с одноименным выходом матрицы А×А×А процессоров и четыре выхода, соединенных с соответствующими входами матрицы А×А×А процессоров, каждый (i,j,k)-й процессор матрицы А×А×А, где i=1…A, j=1…A, k=1…A, содержит (i,j,k)-й одноразрядный узел локальной памяти, (i,j,k)-й мультиплексор, выход которого соединен с информационным входом (i,j,k)-го узла локальной памяти, (i,j,k)-й первый регистр-триггер, (i,j,k)-й второй регистр-триггер, (i,j,k)-й третий регистр-триггер и (i,j,k)-й арифметико-логический узел, входы которого соединены с выходами (i,j,k)-го первого и (i,j,k)-го второго регистров-триггеров, а выходы соединены с первым и вторым входами (i,j,k)-го мультиплексора, третий вход (i,j,k)-го мультиплексора соединен с выходом (i,j,k)-го первого регистра-триггера, четвертый вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера (i-l,j,k)-го процессора, чей кубик 1×1×1 удален от кубика 1×1×1 (i,j,k)-го процессора на один шаг в направлении, противоположном оси Ох и параллельном ребру куба А×А×А и, где О - центр куба А×А×А, пятый вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера того процессора, чей кубик 1×1×1 отображается в кубик 1×1×1 (i,j,k)-го процессора при повороте на 90° вокруг оси Ох, шестой вход (i,j,k)-го мультиплексора соединен с выходом первого регистра-триггера того процессора, чей кубик 1×1×1 отображается в кубик 1×1×1 (i,j,k)-го процессора при повороте на 90° вокруг оси Оу, расположенной перпендикулярно оси Ох и направленной параллельно другому ребру куба А×А×А, каждый (i,j,k)-й вход узла определения объема соединен с выходом третьего (i,j,k)-го регистра-триггера, блок управления содержит центральный процессор с регистром микрослова и память программ и данных, отличающееся тем, что в каждом (i,j,k)-м процессоре матрицы А×А×А введен (i,j,k)-й двухвходовый ключ, информационный вход которого соединен с выходом (i,j,k)-го мультиплексора, управляющий вход соединен с выходом введенного двухтактного триггера, а выход соединен с входом (i,j,k)-го узла локальной памяти, вход и выход которого совмещены и выполнены в виде одного проводника, введен (i,j,k)-й четвертый регистр-триггер, выход которого соединен с (i,j,k)-м входом формирователя кода заполнения бинарного изображения А×А×А, информационный вход соединен с совмещенным входом-выходом (i,j,k)-й локальной памяти, управляющий вход соединен с выходом дополнительно введенной двухвходовой схемы И, информационный вход которой соединен с выходом дополнительно введенного разряда регистра микрослова, в каждом (i,j,k)-м многовходовом мультиплексоре введены седьмой информационный вход, соединенный с выходом (i-S,j,k)-го первого регистра-триггера, и восьмой информационный вход, соединенный с выходом первого регистра-триггера того процессора, чей квадратик 1×1 при повороте квадрата  отображается в квадратик 1×1 (i,j,k)-го процессора, а также девятый информационный вход, соединенный с выходом двухвходовой комбинационной схемы «запрет по первому входу», дополнительно введенной в состав (i,j,k)-го арифметико-логический узла, первый вход которой соединен с выходом (i,j,k)-го первого регистра-триггера, второй вход соединен с выходом (i,j,k)-го второго регистра-триггера, дополнительно введены S-1 матриц А×А внешних входов матрицы А×А×А, каждый (j,k)-й вход v-й матрицы А×А внешних входов, где v=1, …, S, соединен с седьмым входом (v,j,k)-го многовходового мультиплексора, дополнительно введены S-1 матриц А×А одноразрядных коммутаторов внутрислойного перемещения, входы каждой v-й матрицы А×А одноразрядных коммутаторов внутрислойного перемещения соединены с одноименными выходами первых регистров-триггеров процессоров, образующих по направлению Ox (A-S+v)-й слой А×А×1 матрицы А×А×А процессоров, выходы v-й матрицы А×А одноразрядных коммутаторов внутрислойного перемещения соединены с v-й матрицей А×А внешних входов матрицы А×А×А процессоров, дополнительно введены S-1 матриц А×А одноразрядных узлов памяти изображений, совмещенные входы-выходы каждой v-й матрицы А×А одноразрядных узлов памяти изображений взаимно однозначно соединены с v-й матрицей А×А внешних входов матрицы А×А×А, в каждом (i,j,k)-м многовходовом мультиплексоре для каждого аппаратно-реализуемого дискретизирующего отображения, моделирующего преобразование f:R3 → R3 поворота, переноса или симметрии, введен дополнительный информационный вход, соединенный с выходом первого регистра-триггера того процессора матрицы А×А×А, чей соответствующий кубик 1×1×1 при моделировании указанного преобразования отображается в кубик 1×1×1, соответствующий (i,j,k)-му процессору.

отображается в квадратик 1×1 (i,j,k)-го процессора, а также девятый информационный вход, соединенный с выходом двухвходовой комбинационной схемы «запрет по первому входу», дополнительно введенной в состав (i,j,k)-го арифметико-логический узла, первый вход которой соединен с выходом (i,j,k)-го первого регистра-триггера, второй вход соединен с выходом (i,j,k)-го второго регистра-триггера, дополнительно введены S-1 матриц А×А внешних входов матрицы А×А×А, каждый (j,k)-й вход v-й матрицы А×А внешних входов, где v=1, …, S, соединен с седьмым входом (v,j,k)-го многовходового мультиплексора, дополнительно введены S-1 матриц А×А одноразрядных коммутаторов внутрислойного перемещения, входы каждой v-й матрицы А×А одноразрядных коммутаторов внутрислойного перемещения соединены с одноименными выходами первых регистров-триггеров процессоров, образующих по направлению Ox (A-S+v)-й слой А×А×1 матрицы А×А×А процессоров, выходы v-й матрицы А×А одноразрядных коммутаторов внутрислойного перемещения соединены с v-й матрицей А×А внешних входов матрицы А×А×А процессоров, дополнительно введены S-1 матриц А×А одноразрядных узлов памяти изображений, совмещенные входы-выходы каждой v-й матрицы А×А одноразрядных узлов памяти изображений взаимно однозначно соединены с v-й матрицей А×А внешних входов матрицы А×А×А, в каждом (i,j,k)-м многовходовом мультиплексоре для каждого аппаратно-реализуемого дискретизирующего отображения, моделирующего преобразование f:R3 → R3 поворота, переноса или симметрии, введен дополнительный информационный вход, соединенный с выходом первого регистра-триггера того процессора матрицы А×А×А, чей соответствующий кубик 1×1×1 при моделировании указанного преобразования отображается в кубик 1×1×1, соответствующий (i,j,k)-му процессору.

| УСТРОЙСТВО ОБРАБОТКИ ДВУХМЕРНЫХ И ТРЕХМЕРНЫХ ИЗОБРАЖЕНИЙ | 2005 |

|

RU2289161C1 |

| Устройство для параллельной обработки трехмерных сцен | 1990 |

|

SU1817109A1 |

| Устройство для параллельной обработки трехмерных сцен | 1988 |

|

SU1612307A2 |

| Устройство для параллельной обработки трехмерных сцен | 1986 |

|

SU1456965A1 |

| RU 2001121202 A, 27.06.2003 | |||

| Устройство для сохранения естественного состояния образцов горных пород | 1975 |

|

SU875031A1 |

Авторы

Даты

2009-12-20—Публикация

2008-03-28—Подача