Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известно суммирующее устройство, выполненное на основе логических элементов И, ИЛИ, НЕ, содержащее в каждом разряде три RS-триггера, девять элементов И, четыре элемента ИЛИ, один элемент НЕ и три шины управления (см. а.с. №1264165, A1 SU G 06 F 7/50).

Недостатком этого объекта является наличие трех триггерных регистров, что определяет время выполнения операции сложения, объем оборудования, потребление электроэнергии и стоимость устройства в целом.

Наиболее близким, принятым за прототип, является сумматор по а.с. 1418705 SU, он устраняет ряд недостатков, присущих объекту по а.с. 1264165 SU, т.к. содержит только два RS-триггера в каждом разряде, пять элементов И, два элемента ИЛИ, три элемента НЕ и две шины управления. Однако и прототип имеет ряд недостатков, которые мешают его широкому применению. Основным недостатком является одна выполняемая арифметическая операция (сложение) и большая временная задержка сигнала переноса, достигающая 3nτ, здесь n - число разрядов, τ задержка сигнала при прохождении через один элемент И (ИЛИ).

Задачей изобретения является расширение перечня выполняемых операций и повышение быстродействия выполнения арифметических и логических операций при минимальных затратах аппаратных средств.

Для чего предложен объект, выполненный на основе элементов И, ИЛИ, НЕ, содержащий в каждом разряде два RS-триггера, первой, второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, первый, второй и третий элементы НЕ, причем в каждом разряде первый вход первого элемента ИЛИ соединены с первым входом второго элемента И и с шиной переноса из младшего разряда; первый вход второго элемента ИЛИ подключен к выходу третьего элемента И, второй его вход соединен с выходом второго элемента И, а третий вход подключен к "единичному" выходу первого триггера, выходы упомянутых элементов ИЛИ подключены к первому и третьему входам первого элемента И, второй вход этого элемента соединен с выходом третьего элемента НЕ; выход первого элемента И является шиной переноса в старший разряд и соединен с первым входом третьего элемента И и с входом второго элемента НЕ, выход которого связан с вторым входом четвертого элемента И данного разряда; выход второго элемента И через первый элемент НЕ соединен с вторым входом третьего элемента И, третьи входы третьего и четвертого элементов И соединены с первой шиной управления, а выходы упомянутых элементов И подключены к "нулевому" и "единичному" входам первого триггера соответственно, отличающийся тем, что в его каждый разряд введены третий элемент ИЛИ, пятый элемент И, вторая, третья и четвертая шины управления, при этом первый вход пятого элемента И подключен к "единичному" выходу второго триггера, второй вход этого элемента соединен с второй шиной управления, а выход пятого элемента И соединен с первым входом третьего элемента ИЛИ, с третьим входом первого элемента ИЛИ и с вторым входом второго элемента И; второй вход третьего элемента ИЛИ соединен с первым входом первого элемента ИЛИ, третий вход третьего элемента ИЛИ подключен к третьей шине управления, а его выход соединен с первым входом четвертого элемента И, кроме того, к второму входу первого элемента ИЛИ подключена четвертая шина управления (это п.1. формулы изобретения). Кроме того, в каждый разряд объекта введены:

- шестой и седьмой элементы И, четвертый и пятый элементы ИЛИ и пятая шина управления, причем к первым входам элементов И подключена пятая шина управления, вторые входы шестого и седьмого элементов И i-того разряда соединены с выходом и входом второго элемента НЕ i+1-го разряда соответственно, выходы упомянутых элементов подключены к первым входам четвертого и пятого элементов ИЛИ, вторые входы этих элементов подключены к первой шине управления, выходы упомянутых элементов ИЛИ соединены с третьими входами третьего и четвертого элементов И соответственно; (п.2)

- четвертый элемент НЕ, причем его вход соединен с выходом третьего элемента И, а выход упомянутого элемента НЕ соединен с "нулевым" входом первого триггера; вход третьего элемента НЕ подключен к выходу четвертого элемента И, а выход этого элемента НЕ соединен с "единичным" входом первого триггера и вторым входом первого элемента И.; (п.3)

- восьмой элемент И, шестая и седьмая шины управления, причем первый вход упомянутого элемента И подключен к "единичному" выходу второго триггера, второй вход соединен с шестой шиной управления, выход восьмого элемента И подключен к третьему входу пятого элемента ИЛИ, седьмая шина управления подключена к четвертому входу второго элемента ИЛИ; (п.4)

- шестой элемент ИЛИ, при этом первый его вход подключен к шине переноса из младшего разряда, второй вход соединен с выходом второго элемента И младшего разряда, а выход упомянутого элемента ИЛИ подключен к первому входу второго элемента И рассматриваемого разряда, причем выход этого элемента И соединен с вторым входом шестого элемента ИЛИ и с четвертым входом первого элемента ИЛИ старшего разряда. (п.5)

Предлагаемый объект позволяет выполнить пять операций (сложение, сдвиг вправо, инвертирование, логическое сложение и логическое умножение) при минимальных затратах дополнительного оборудования и сократить время выполнения операции сложения (вычитания) за счет сокращении максимальной временной задержки сигнала в цепи переноса с 3nτ до 2nτ.

Укажем основные преимущества объекта, которые обеспечиваются отдельными пунктами формулы изобретения, т.е. отдельными группами отличительных признаков.

1. Выполнение операции выдачи второго слагаемого, сложения и инвертирования кода, хранящегося в первом триггере.

2. Сдвиг кода, хранящегося в первых триггерах, вправо, т.е. деление двоичного числа на 2, 4, 8 и т.д., и обеспечение выполнения операций умножения, которая состоит в последовательном выполнении операции сложения и сдвига кодов.

3. Обеспечивается повышение надежности работы устройства за счет исключения возможных (теоретически) "гонок" сигналов в цепях триггер первый и третий элемент НЕ, управляющие вторым и третьим входами первого элемента И.

4. Выполнение операций логического сложения и логического умножения.

5. Обеспечивается снижение максимальной временной задержки в цепях сквозного переноса с 3nτ (у прототипа) до 2nτ.

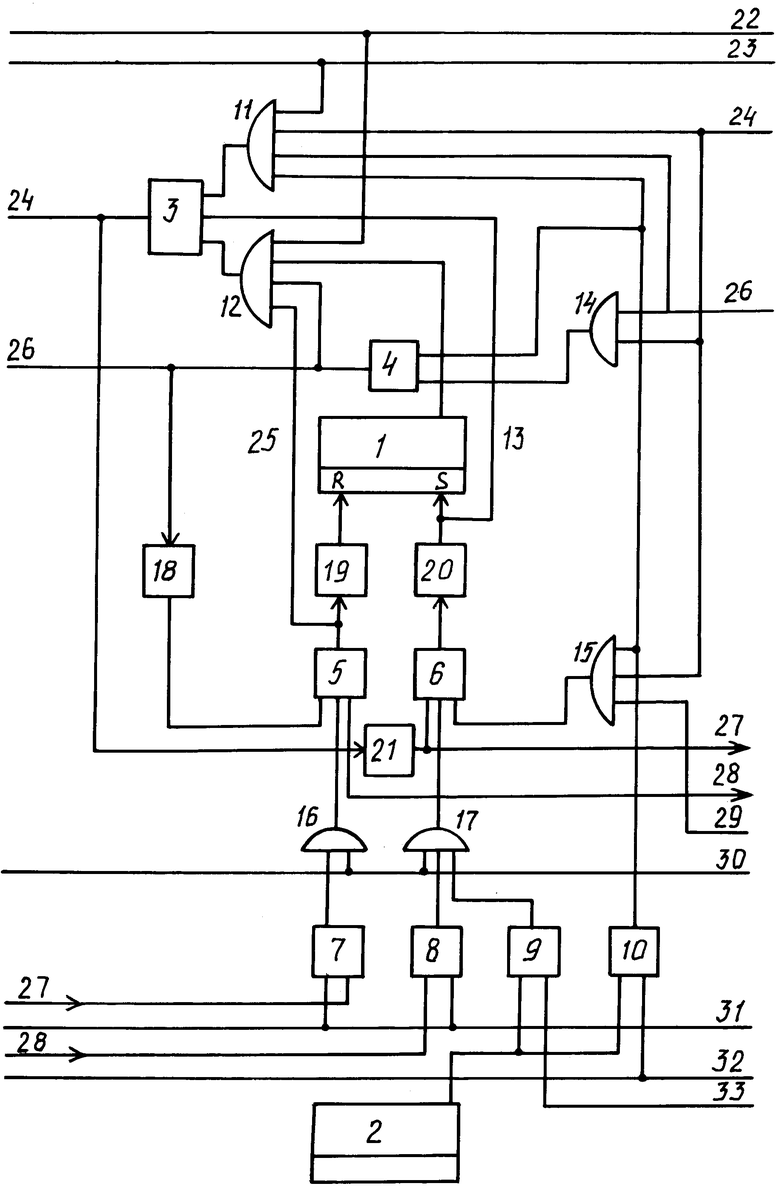

Каждый двоичный разряд объекта (чертеж) содержит RS - триггеры 1, 2, элементы И 3-10, элементы ИЛИ 11, 12, 14-17, элементы НЕ 18-21, 22 шина управления (ШУ) операцией логического умножения, 23 ШУ сдвигом кода вправо и инвертированием, 24 первый вход переноса из младшего разряда, 13 и 25 ШУ формированием сигнала переноса, 26 второй вход переноса из младшего разряда, 27 "нулевой" выход в младший разряд при сдвиге кода, 28 "единичный" выход в младший разряд при сдвиге кода вправо, 29 вторая ШУ при выполнении операций инвертирования и сдвига вправо, 30 импульсная ШУ для выполнения основных операций, 31 импульсная ШУ сдвигом вправо, 32 ШУ выдачей кода из второго триггера, 33 импульсная ШУ выполнения операции логического сложения (шины управления приемом кода во второй триггер для упрощения чертежа не приводятся).

Рассмотрим работу объекта при выполнении арифметических и логических операций. Будем считать, что до начала выполнения операции первое слагаемое хранится в триггерах 1, а второе слагаемое по первому временному такту (t1) принимается в триггеры 2.

1. Операция сложения. Одновременно с приемом второго слагаемого на ШУ 32 подается потенциал, разрешающий выдачу кода триггера 2 непосредственно на суммирующие схемы.

По второму временному такту (t2) производится формирование поразрядного и сквозного переносов во всех разрядах объекта в соответствии с следующими логическими соотношениями

Здесь Аi, Вi, Pi - значения первого и второго слагаемых и выработанного переноса i-того разряда;

Pi i-1 - сигнал переноса, выработанный в i-1-ом разряде (основной);

P" i-1 - сигнал переноса, выработанный в i-ом разряде (вспомогательный);

- сигнал установки единицы первого триггера.

- сигнал установки единицы первого триггера.

Максимальная временная задержка сигнала в цепи переноса равняется 2nτ. По истечении этого времени на ШУ 30 подается третий исполнительный импульс, который поступает на третьи входы И 5, 6 одновременно и заносит в первый триггер результат суммирования двух чисел. Другими словами, вместо первого слагаемого будет занесена сумма двух слагаемых. Переключение первого триггера будет осуществляться в соответствии со значениями слагаемых, приведенных в таблице 1.

Отметим особенности работы объекта при выполнении операции сложения. При поступлении импульса на "единичный" вход первого триггера этот же сигнал запрещает возможную выработку ложного сигнала переноса путем запрета третьего элемента И по второму его входу. Разрешение формирования переноса будет возможно только после окончания счетного импульса, поступившего по цепи ШУ 30, И 6, НЕ 20. При поступлении счетного импульса на "нулевой" вход первого триггера этот же сигнал "поддерживает" значение кода первого триггера, равного "единице", за счет прохождения импульса по цепи И 5, ИЛИ 12, И 3 до окончания этого импульса. В соответствии с таблицей 1, строка 6, 8, вырабатывается запрет изменения состояния первого триггера при наличии сигналов переноса и второго слагаемого. При этом сигналы запрета проходят по цепи И 10, И 4, НЕ 18.

2. Операция инвертирования кода. Для выполнения этой операции на ШУ 23 и 29 подаются потенциалы, являющиеся признаками этой операции. Если в первом триггере i-того разряда хранится код "единицы", то потенциал с шины 23, через ИЛИ 11, И 3 поступит на первый вход И 5. Потенциал шины 29 через ИЛИ 15 поступит на первый вход И 6. Исполнительный импульс t1 подается на шину 30 и через ИЛИ 16, И 5, НЕ 19 поступит на "нулевой" вход триггера. Если же в первом триггере хранится "нулевой" код, то исполнительный импульс по цепи шина 30, ИЛИ 17, И 6, НЕ 20 поступит на "единичный" вход первого триггера. Т.о. код регистра первого слагаемого будет проинвертирован.

3. Операция сдвига кода вправо. Для выполнения операции на шину 23 подается управляющий потенциал, который является признаком этой операции и присутствует на время всей операции. При том, если в i-том разряде хранится код "единицы", то потенциал с выхода И 3 поступит на входы НЕ 21, И 5 i-того разряда и по шинам 28, 27 поступает на входы И 8, 7 i+1-го разряда соответственно. Исполнительный импульс сдвига, поступивший на шину 31, установит первый триггер i-того разряда в нуль (если в i+1-ом хранился код нуля) и установит триггер i-1-го разряда в единицу. Последовательность импульсов, поступающих на шину 31, будет сдвигать код числа вправо. При этом значение потенциала с выхода И 3 не будет изменяться даже при переключении триггера в данном разряде, т.к. связи 13 и 25 будут "поддерживать" значение сигнала с И 3 до окончания действия импульса сдвига.

4. Операция логического сложения. Признаком выполнения этой операции является наличие высокого потенциала на ШУ 29, который через ИЛИ 15 приходит на первый вход элемента И 6. На второй вход этого элемента с выхода НЕ 21 также поступает высокий потенциал, т.к. потенциалов переносов нет ни в одном разряде объекта. По t1 исполнительный импульс по шине 33 через И 9, ИЛИ 17, И 6, НЕ 20 поступит на "единичный" вход первого триггера. Операция закончена. Результат логического сложения двух чисел будет занесен в первые триггеры, где раньше хранился код первого слагаемого.

5. Операция логического умножения. Признаком выполнения этой операции является наличие высоких потенциалов на шинах 22 и 23. Высокий потенциал с выхода И 3 поступает на первый вход И 5 и через элемент НЕ 21 на второй вход И 6. Тем самым разрешается прохождение исполнительного импульса через И 5 и запрещается - через И 6 в течение выполнения всей операции. Одновременно на ШУ 32 подается потенциал выдачи кода второго слагаемого. По t1 исполнительный импульс, поступивший на шину 30, установит все первые триггеры в "нуль", кроме тех разрядов, в которых код второго триггера хранит код "единицы". Запрет установки "нуля" первого триггера осуществляется за счет прохождения сигнала по цепи ШУ 32, И 10, И 4, НЕ 18. Операция закончена. Результат операции логического умножения будет храниться в первых триггерах.

Таким образом, предлагаемый объект позволяет повысить быстродействие выполнения операции сложения (вычитания), повысить надежность работы устройства и расширить перечень выполняемых объектом операций в 4 раза (сложение, сдвиг вправо, инвертирование, логическое сложение и логическое умножение) при незначительном увеличении аппаратных средств.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия и надежности работы устройства и расширение перечня выполняемых операций (сложение, сдвиг влево, сдвиг вправо, инвертирование, логическое сложение и логическое умножение). Устройство содержит в каждом разряде два RS-триггера, восемь логических элементов И, шесть логических элементов ИЛИ, четыре логических элемента НЕ, семь шин управления. 4 з.п. ф-лы, 1 ил., 1 табл.

| Накапливающий сумматор | 1987 |

|

SU1418705A1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| US 5691931 A, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2005-11-20—Публикация

2004-02-02—Подача