IS

1/г

Изобретение относится к цифровой вычислительной технике и предназначено для использования в составе процессоров ЭВМ и устройство цифровой авто- матики.

Цель изобретения - упрощение, сумматора.

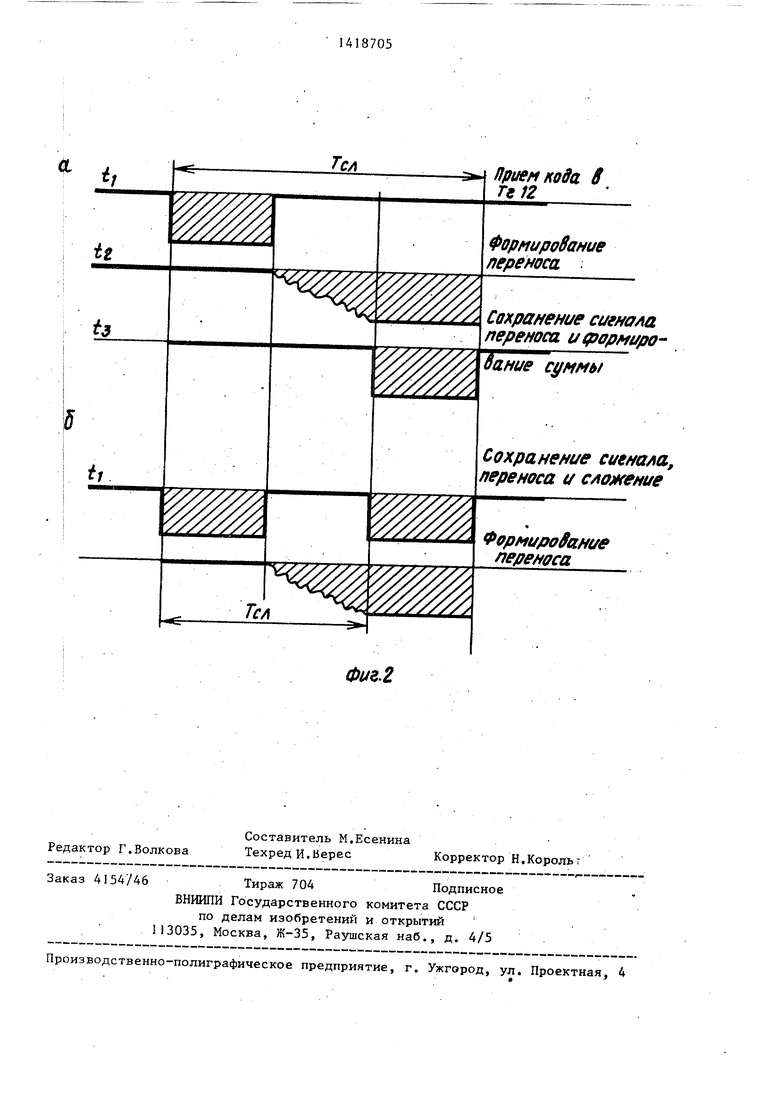

На фиг.1 представлена функциональная схема двух разрядов накапливающе- гр сумматора; на фиг.2 - временные ди- а раммы работы предлагаемого сумма- тфра.

I Каждый двоичный разряд сумматора (фиг.1) содержит элементы ИЛИ 1 и 2, элементы И 3-7, элементы НЕ 8-10, RS-триггеры 1, 12, вход 13 переноса из младшего разряда, вход J4 слогке- нйя, вход 15 разрешения записи опе- , вход 16 приема кода в данный

разряд.

I Рассмотрим работу сумматора при вы п лнении операции сложения двух чи- , представленных в двоичном коде. Будем считать, что код первого слага- хранится в триггерах 11, а код BJroporo слагаемого поступает в триггеры 12 по шинам 16. .

По первому временному такту (t) вьшолняется элементарная операций (ЭО) приема кода второго слагаемого. Для выполнения этой 30 на вход 15 подается исполнительный импульс. Если на входе 16 присутствует высокий (низкий) потенциал, соответствующий коду 1, то исполнительный импульс через элемент И 7 поступает на LS- вход триггера 12 и устанавливает его в единичнйе состояние, Если на входе 16 отсутствует высокий (низкий) потенциал, что соответствует коду О то триггер 12 сохраняет или устанавливается в нулевое состояние, .

После переключения триггера 12 в период второго временного такта начинает формироваться потенциал сквозного переноса, В каждом разряде сумматора во время такта потенциал переноса формируется в соответствии со следующим логическим выражением:

(Ч)

Р; (P;.,VA;)(.,Aj)S;..., (О

-,

-перенос,выработанный в i-OM рязряде-; .

-перенос,выработанный в младшем разряде;

0

5

0

5

0

5

0

5

Л,, В; - значение операндов i-ro разряда; R;, S; - значение сигналов на нулевом и единичном входах триггера 11,

Из соотношения (1) видно, что разрядный перенос вырабатывается в тех разрядах сумматора, в которых триггеры 11 и 12 находятся в единичном состоянии. Потенциал переноса, выработанный в младшем разряде, проходит через i-й разряд только в том случае, если в рассматриваемом разряде триггеры 11 или 12 находятся в единичном состоянии. При этом потенциал переноса может распространяться по цепи элементов ИЛИ 1, И 3 или по цепи И 4, ИЛИ 2, И 3.

По истечении второго временного такта, равного времени максимального ,. сквозного переноса, данного суммато- ра, выполняется временной такт,завер-, шающий операцию сложения.

В период третьего временного такта (t,) обеспечивается сохранение значения потенциала переноса, сформирован-; ного па в .данном разряде, и формирование значения суммы в триггере II,

Сохранение значения потенциала переноса в предложенном сумматоре до. стигается за счет наличия связей S- и R-входов триггера 11 с элементами формирования потенциала сквозного переноса. Так, например, если триггер за счет импульса сложения, поступившего на вход 14, устанавливается в 1, то этот же импульс еще до переключения триггера 11 и ИЛИ 2 поступает на вход НЕ 10 и запрещает прохождение потенциала переноса через И 3 данного разряда.

В том случае, если триггер 11 по tj устанавливается в нулевое состояние, то за счет передачи импульса, поступившего на S-вход триггера 11, через ИЛИ 2 на вход И 3, обеспечивается сохранение потенциала переноса и после переключения триггера 11 в нулевое состояние.

Значение суммы в i-ом разряде сумматоров формируется в соответствии со следующими логическими выражениями

S; tjPUAiV-P., ); Ri tjPi (А;Р,-.,),

(2) (3)

где t- - сигнал выполнения операции сложения, поступивший на вход 14.

После завершения третьего временного такта операция сложения закончена. Результат суммирования кодо двух чисел хранится в триггерах 11, В триггерах 12 хранится код второго слагаемого. При необходимости сумматор позволяет выполнить и многократное сложение один раз принятого в регистр кода второго слагаемого..

Формула изобретения

Накапливающий сумматор, содержащий в каждом , разряде первый и второй RS- триггеры, первый и второй элементы ИЛИ, первый, второй, третий, четверг тый и пятый элементы И, первый и второй элементы НЕ, причем в каждом разряде первый и второй входы первого элемента И соединены соответственно с входом разрешения записи операндов в устройство и входом соответствующего разряда, выход .этого :элемента И подключен к S-входу первого триггера, первые входы второто и третьего элементов И связаны с входом разрешения сложения, вторые входы этих элементов соединены с входом и выходом первого элемента НЕ соответственно, выход второго элемента. И подключен

к R-входу второго триггера и первому входу первого элемента ИЛИ, выход третьего элемента И соединен-с S- входом второго триггера и входом второго элемента НЕ, единичный выход второго триггера соединен с вторым входом первого элемента ИЛИ, первый вход второго элемента ИЛИ соединен с

входом переноса младшего разряда сумматора, выходы первого и В орого элементов ИЛИ соединены с первым и третьим входами пятого элемента И, второй вход которого связан с выходом

второго элемента НЕ, а выход пятого элемент-а И является выходом переноса данного разряда сумматора и .соединен с входом первого элемента НЕ, отличающийся тем, что, с

целью упрощения сумматора, в каждый его разряд введен третий элемент НЕ, при этом единичный выход первого триггера соединен с первым входом четвертого элемента И и вторым входом второго элемента ИЛИ, второй вход четвертого элемента И соединен с входом переноса из младшего разряда сумматора, а выход этого элемента И связан с третьим входом первого элемента ИЛИ

и входом третьего элемента НЕ, выход которого подключен к третьему входу второго элемента И, выход второго элемента ИЛИ соединен с третьим входом третьего элемента И.

а

Тел

Прием кода в Те 12

| название | год | авторы | номер документа |

|---|---|---|---|

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| Сумматор параллельного действия | 1974 |

|

SU531157A1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

| Двоичный накапливающий сумматор | 1983 |

|

SU1112363A1 |

| Двухтактный п-разрядный сумматор накапливающего типа | 1974 |

|

SU538365A1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

Изобретение может быть использовано в цифровой вычислительной технике и в устройствах цифровой автоматики. Цель изобретения состоит в упрощении устройства за счет сокращения числа логических элементов, на основе которых построен сумматор. Накапливающий сумматор содержит два RS- триггера, пять логических элементов И 3-7, два элемента ИЛИ 1 и 2, три элемента НЕ 8-10. Операция сложения с приемом кода второго слагаемого вьшолняется за три временньк такта (под тактом работы устройства понимается длительность исполнительных импульсов, поступающих на шины управления работой сумматора). По первому такту вьшолняется прием кода второго слагаемого. Второй временной такт отводится для формирования и распространения максимального сквозного переноса. По третьему временному такту формируется и заносится во второй RS-триггер результат сложения двух двоичных чисел. При этом результат сложения заносится в те же триггеры, в которых хранится код первого слагаемого. Для исключения неопределенности значение потенциала переноса данного разряда искусственно поддерживается за счет поступления сигнала в цепь переноса, если триггер устанавливается в О, и за счет запрета распространения сигнала переноса.в старший разряд за счет выключения элемента И цепи сквозного переноса, если триггер устанавливается в I. 2 ил. SS (Л

it

t3

Тел

Формирование переноса

Сохранение сиенола переноса t/fpopMi/poбание суммы

Сохранение си(нала, переноса и сло кение

Формирование переноса

Фие.2

| Накапливающий сумматор | 1984 |

|

SU1176323A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Накапливающий сумматор | 1985 |

|

SU1262479A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-23—Публикация

1987-02-17—Подача