Область техники, к которой относится изобретение

Настоящее изобретение относится, в основном, к усовершенствованиям, связанным со считыванием матрицы памяти полного сканирования, и, более подробно, к полезным технологиям для статического запуска общей (глобальной) разрядной линии в матрице памяти полного сканирования.

Уровень техники

Матрица памяти полного сканирования использует технологию динамического предварительного заряда и разряда при считывании битов, записанных в ячейке памяти. Эта стандартная технология обычно делится на два уровня для того, чтобы минимизировать емкость рассеяния, вносимую разрядными линиями в пределах матрицы памяти полного сканирования. Первый уровень матрицы памяти полного сканирования включает в себя запоминающие ячейки, проходные транзисторы и локальные разрядные линии. Запоминающая ячейка запоминает двоичное значение. Проходной транзистор запускается числовой шиной считывания (для считывания слов) для того, чтобы разрядить локальную разрядную линию, на основании содержимого ячейки памяти. Локальная разрядная линия обычно совместно используется многочисленными числовыми шинами считывания. Локальная разрядная линия предварительно высоко заряжена так, чтобы переход на считывание памяти мог быть распознан. Локальная разрядная линия обеспечивает вход на второй уровень.

Второй уровень матрицы памяти полного сканирования обычно включает в себя некоторое количество инверторов и согласующих транзисторных пар, причем каждая пара обеспечена входом посредством одной локальной разрядной линии. Согласующие транзисторы соединяются с динамически предварительно заряженной глобальной разрядной линией. Эту матрицу памяти называют матрицей памяти полного сканирования, потому что локальные и глобальные разрядные линии нужно протянуть для заземления, чтобы распознать значение 0, записанное в ячейке памяти. Считывая последовательные значения 0 из ячейки памяти, стандартная матрица памяти полного сканирования требует предварительного заряда и разряда локальных и глобальных разрядных линий. Предварительный заряд локальных и глобальных разрядных линий должен произойти прежде, чем будет утвержден сигнал числовой шины считывания. Этот разряд происходит, поскольку значения 0 передаются через второй уровень. Таким образом, мощность расходуется на предварительный заряд и разряд как локальных, так и глобальных разрядных линий в процессе считывания, в то время как последовательные значения 0 передаются по глобальной разрядной линии.

Кроме того, в стандартных матрицах памяти полного сканирования схема фиксации состояния (удерживающая схема) или динамико-статический преобразователь обычно добавляется к выходу глобальной разрядной линии для того, чтобы гарантировать, что выход удержит оцененное значение глобальной разрядной линии. Эта дополнительная схема занимает реальную площадь кремниевого кристалла, на котором расположена матрица памяти.

Сущность изобретения

При рассмотрении его нескольких аспектов настоящее изобретение признает проблему дополнительного расхода мощности, вызванного предварительной зарядкой и разрядом глобальной разрядной линии в стандартных матрицах полного сканирования в течение последовательных считываний ячеек памяти, которые имеют значение 0. С этой целью вариант осуществления настоящего изобретения включает в себя статически переключающиеся глобальные разрядные линии. Такая технология уменьшает потребление мощности в течение последовательных считываний значений 0 и делает это методом, который исключает потребность в удерживающей схеме или схеме динамико-статического преобразователя на выходе.

В одном варианте осуществления изобретения раскрыт способ запуска глобальной разрядной линии. Этот способ включает в себя этап, на котором соединяют множества локальных разрядных линий с глобальной разрядной линией через множество устройств с тремя состояниями. Этот способ дополнительно включает в себя этапы, на которых генерируют общий (глобальный) сигнал выбора, разрешающий работу одному из множества устройств с тремя состояниями, и выбирают соответствующую локальную разрядную линию для запуска выхода разрешенного устройства с тремя состояниями. Таким образом, глобальную разрядную линию статически запускают так, чтобы последовательные считывания битов, имеющих одно и то же значение, считанное по глобальной разрядной линии, не приводило бы к переходу состояния глобальной разрядной линии.

Более полное понимание настоящего изобретения, а также дополнительных признаков и преимуществ изобретения будет очевидно из последующего детального описания и приложенных чертежей.

Краткое описание чертежей

Фиг.1 показывает пример системы беспроводной связи, в которой могут преимущественно использоваться варианты осуществления изобретения.

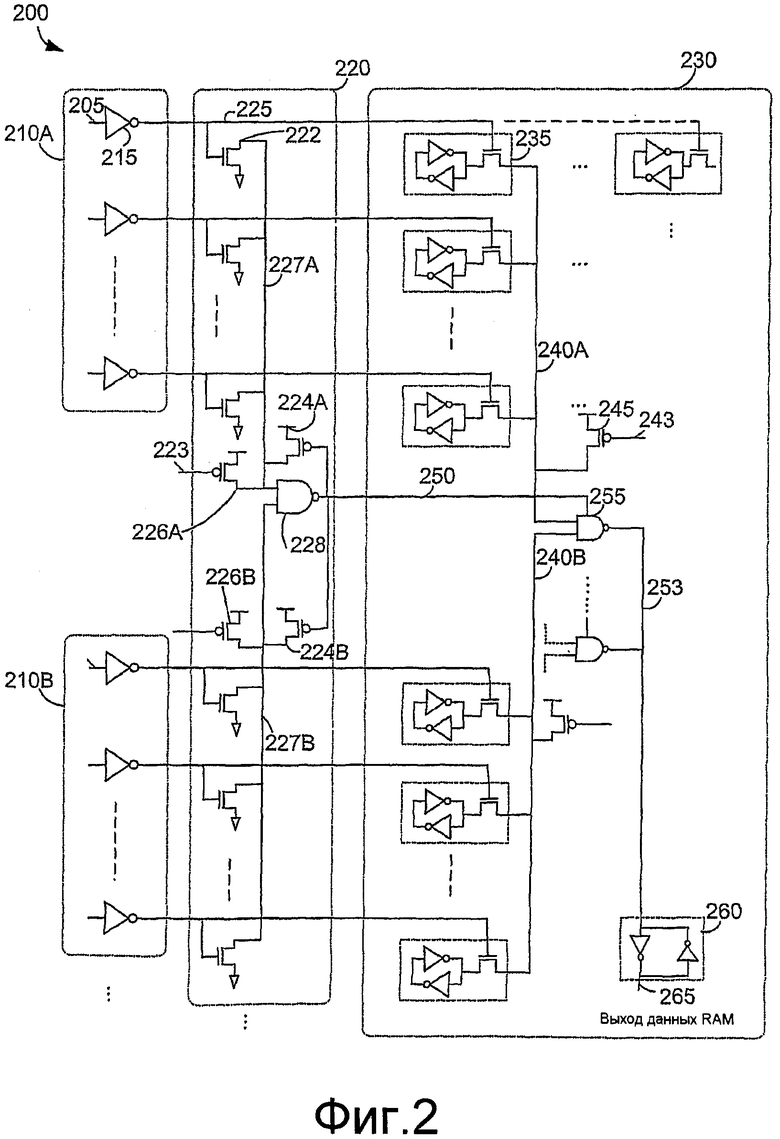

Фиг.2 - принципиальная электрическая схема считывающей части системы матрицы памяти полного сканирования в соответствии с одним из вариантов осуществления изобретения.

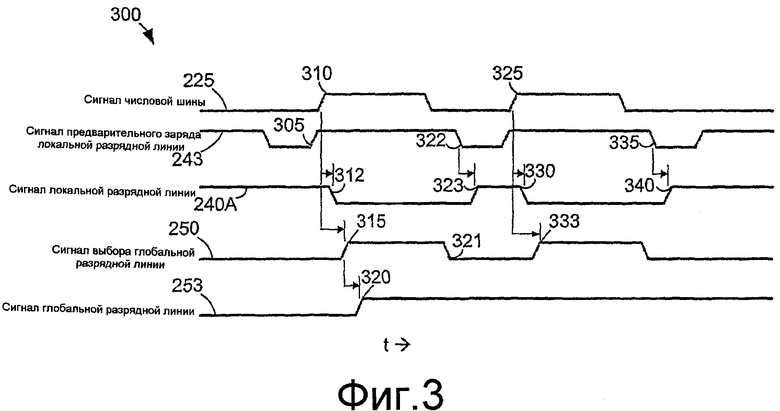

Фиг.3 - временная диаграмма, показывающая статический характер глобальной разрядной линии фиг.2 в соответствии с этим вариантом осуществления изобретения.

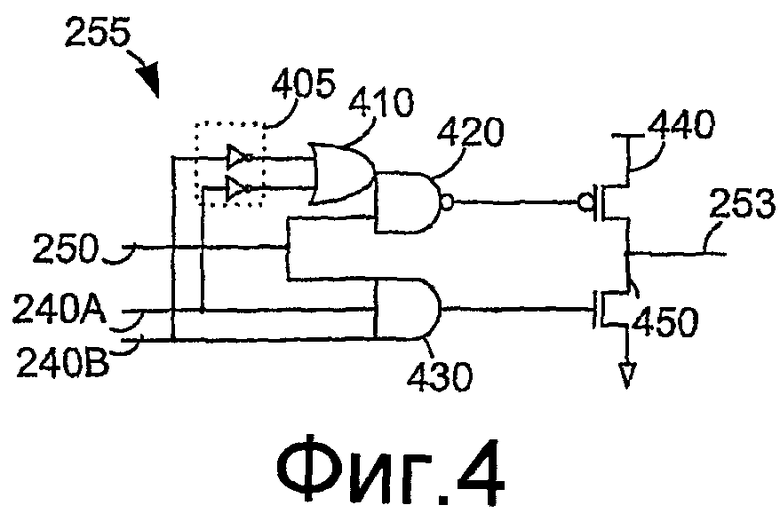

Фиг.4 показывает детали для одного подходящего устройства с тремя состояниями, представленного на фиг.2.

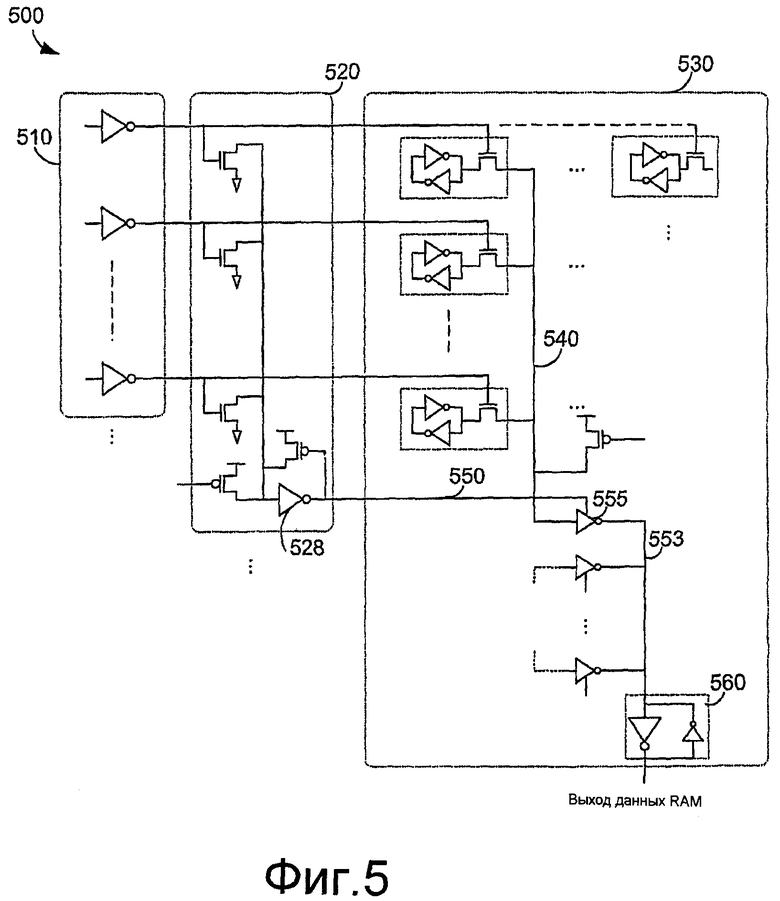

Фиг.5 - альтернативный вариант осуществления считывающей части системы матрицы памяти полного сканирования, представленной на фиг.2 в соответствии с этим вариантом осуществления изобретения.

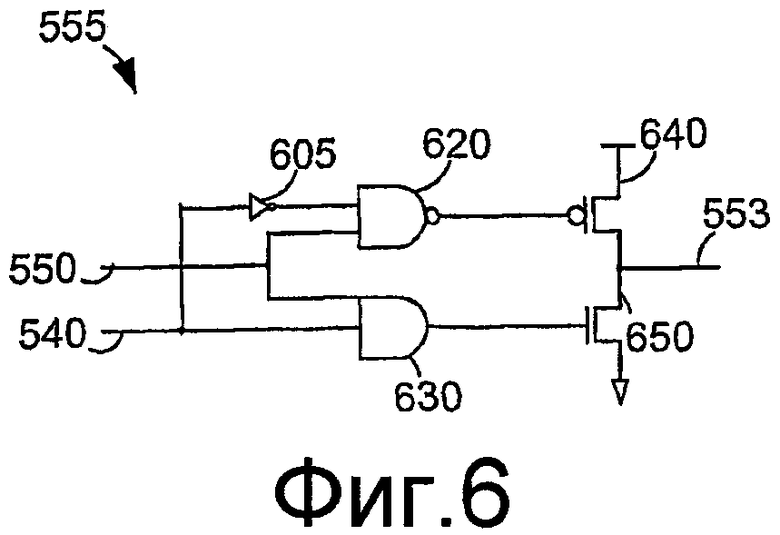

Фиг.6 показывает детали устройства с тремя состояниями, подходящего для использования на фиг.5.

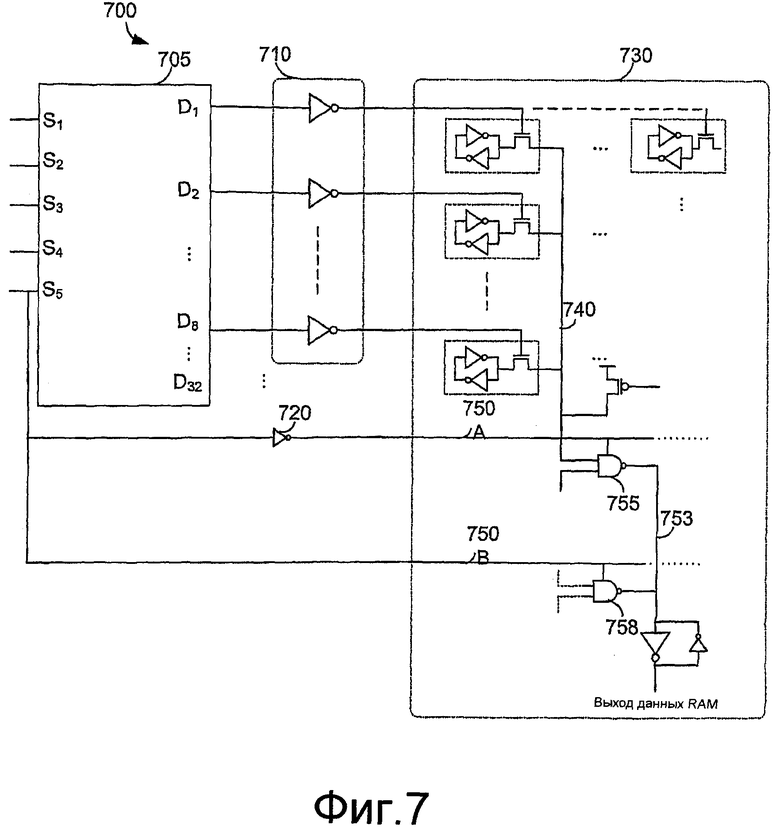

Фиг.7 показывает пример альтернативной схемы генерирования глобального сигнала выбора в соответствии с дополнительным вариантом осуществления изобретения.

Фиг.8 - блок-схема, показывающая способ статического переключения глобальной разрядной линии в соответствии с вариантом осуществления изобретения.

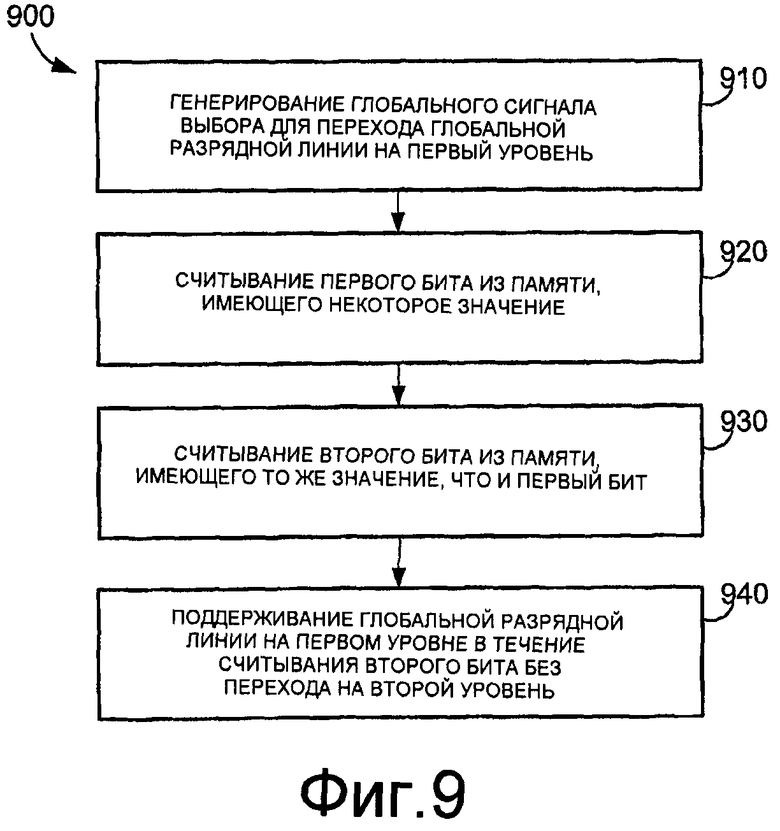

Фиг.9 - блок-схема, показывающая способ уменьшения мощности, когда последовательно считываются биты, имеющие одно и то же значение, по глобальной разрядной линии в пределах памяти в соответствии с вариантом осуществления изобретения.

Фиг.2 - принципиальная электрическая схема считывающей части системы 200 матрицы памяти полного сканирования в соответствии с вариантом осуществления изобретения. Эта считывающая часть системы 200 матрицы памяти полного сканирования включает в себя дополнительные наборы задающих устройств 210A-210B числовой шины считывания, распределенный динамический элемент ИЛИ 220 и матрицу 230 памяти полного сканирования, измененную согласно сущности изобретения. Наборы задающих устройств 210A и 210B числовой шины считывания получают активный низкий, полностью декодированный сигнал числовой шины считывания и соответственно соединяются с распределенным динамическим элементом ИЛИ 220 и матрицей 230 памяти полного сканирования. Распределенный динамический элемент ИЛИ 220 соединяется с матрицей 230 памяти полного сканирования. Наборы задающих устройств 210A-210B числовой шины считывания являются дополнительными, если сигнал числовой шины считывания высоко активен.

Для упрощения, только набор задающих устройств 210A числовой шины считывания и распределенный динамический элемент ИЛИ 220 будут здесь описаны в деталях. Набор задающих устройств 210A числовой шины считывания включает в себя до восьми инверторов, таких как инвертор 215. Инвертор 215, например, получает сигнал 205 числовой шины считывания, причем активно-низкий сигнал 205 числовой шины считывания инвертирован и передан в распределенный динамический элемент ИЛИ 220 и в матрицу 230 памяти полного сканирования. Распределенный динамический элемент ИЛИ 220 включает в себя шестнадцать согласующих транзисторов, таких как согласующий транзистор 222, причем восемь из согласующих транзисторов 222 заканчивают свои выходы в общей точке 227A разветвления, а восемь других согласующих транзисторов 222 соединяют свои выходы с общей точкой 227B разветвления и с четырьмя нагрузочными транзисторами 226А, 226В, 224А, 224В. Выходы нагрузочных транзисторов 226А, 224А заканчиваются в общей точке 227A разветвления. Выходы нагрузочных транзисторов 226В, 224В заканчиваются в общей точке 227B разветвления. Распределенный динамический элемент ИЛИ 220 также включает в себя логический элемент И-НЕ 228. Логический элемент И-НЕ 228 соединен параллельно с транзисторами 224А, 224В удержания. Общие точки 227A и 227B разветвления соединяются с логическим элементом И-НЕ 228, который создает, в качестве его выходного сигнала, глобальный сигнал выбора по глобальной линии 250 выбора.

Распределенный динамический элемент ИЛИ 220 получает в качестве входного напряжения предварительно заряженный импульс 223 низкого уровня для предварительного заряда общей точки 227A разветвления через нагрузочный транзистор 226А. Поскольку общая точка разветвления 227A предварительно заряжена, а сигнал 223 переходит на высокий уровень, транзистор 224А удержания поддерживает общую точку разветвления 227А в состоянии логической 1 так, чтобы можно было распознать переход состояния в активный логический 0.

С другой стороны, общие точки 227A и 227B разветвления могут быть разъединены путем замены логического элемента И-НЕ 228 инвертором, как представлено в альтернативном варианте осуществления, описанном на фиг.5. Однако, как будет признано при обсуждении варианта осуществления фиг.5, при соединении общих точек 227A и 227B разветвления через логический элемент И-НЕ 228 количество глобальных линий выбора будет уменьшено вдвое. Однако признано, что другие соединения между более чем двумя распределенными динамическими элементами ИЛИ для уменьшения количества глобальных линий выбора дополнительно рассмотрены в настоящем изобретении и что другие логические проекты могут быть внедрены, чтобы достигнуть тех же самых результатов, как этими идеями.

Следует отметить, что составные динамические элементы ИЛИ, такие как составной динамический элемент ИЛИ 220, могут быть изготовлены из кремния, чтобы разместить общие точки разветвления 227A и 227B, взаимодействующие друг с другом, как показано на фиг.2. Таким образом, отдельный канал разводки вытравлен по совпадающей длине пробега, который полезно уменьшает полное количество каналов разводки.

Матрица 230 памяти полного сканирования включает в себя ячейки матрицы памяти c произвольной выборкой (RAM), такие как ячейки 235 RAM. Каждый ряд ячеек RAM присоединен к той же самой числовой шине считывания. Ячейки RAM в колонке ячеек RAM соединены с другими числовыми шинами считывания. Как показано на фиг.2, подколонка из восьми ячеек RAM заканчивается в локальной разрядной линии 240A. Подобным же образом вторая подколонка из восьми ячеек RAM присоединена к другому набору числовых шин считывания и заканчивается в локальной разрядной линии 240B.

Матрица 230 памяти полного сканирования также включает в себя некоторое количество нагрузочных транзисторов, таких как нагрузочный транзистор 245, некоторое количество устройств с тремя состояниями, таких как логический элемент И-НЕ 255 с тремя состояниями, и дополнительную ячейку 260 удержания. Нагрузочный транзистор 245 получает импульс 243 низкого уровня, предварительного заряда локальной разрядной линии, для того, чтобы предварительно зарядить локальную разрядную линию 240A. Нагрузочный транзистор 245 поддерживает локальную разрядную линию 240A в логическом состоянии 1, при условии наличия предварительного заряда, до тех пор, пока логическое состояние 0 не считано из ячейки RAM. Устройства с тремя состояниями передают выходной сигнал в глобальную разрядную линию 253. Эти устройства с тремя состояниями получают входной сигнал от двух локальных разрядных линий, таких как локальные разрядные линии 240A и 240B. Эти локальные разрядные линии передают содержимое считанной ячейки RAM, когда соответствующая числовая шина считывания активизирована. Устройствам с тремя состояниями разрешают работу соответствующие глобальные сигналы выбора. Например, логическому элементу И-НЕ 255 с тремя состояниями соответственно разрешает работу глобальный сигнал 250 выбора.

Количество устройств с тремя состояниями, используемых в матрице памяти полного сканирования, согласно сущности изобретения изменяется в соответствии с размером памяти полного сканирования и количеством ячеек RAM, заканчивающихся в устройстве с тремя состояниями. В целом, полное количество устройств с тремя состояниями, nt, может быть выражено следующим образом:

n

t

=(R·C)/b

r,

(1)

(1)

где R - количество рядов матрицы памяти полного сканирования, C - количество колонок матрицы памяти полного сканирования и br - количество ячеек RAM, заканчивающихся в устройстве с тремя состояниями. Например, в любом варианте осуществления логического элемента И-НЕ с тремя состояниями 32×32 системы матрицы памяти полного сканирования nt равнялось бы 32 разрядам 32 рядов колонок, разделенных 16 ячейками RAM на логический элемент И-НЕ с тремя состояниями, и в сумме составляет 64 устройства И-НЕ с тремя состояниями. Для конфигурации матрицы памяти полного сканирования 64×32 следовало бы использовать 128 устройств И-НЕ с тремя состояниями. Количество устройств И-НЕ с тремя состояниями, используемых в особой колонке, nc, выражено следующим образом:

nc=R/br. (2)

(2)

Между прочим, nc также равняется количеству глобальных линий выбора, используемых в этой системе.

Предполагая, что фиг.2 показывает 64×32 конфигурацию, матрица 230 памяти полного сканирования содержала бы 64 шины считывания, где каждый набор задающих устройств числовой шины считывания имеет восемь инверторов, чтобы соединиться с восемью числовыми шинами считывания, таким образом, в общей сумме восемь наборов из восьми задающих устройств числовой шины. Два набора задающих устройств числовой шины соединились бы с соответствующим динамическим элементом ИЛИ, имеющим шестнадцать согласующих транзисторов, и с шестнадцатью рядами 32 ячеек RAM. Локальная разрядная линия соединила бы восемь ячеек RAM. Каждая колонка матрицы 230 памяти полного сканирования содержала бы восемь локальных разрядных линий, таким образом, в общей сумме 256 локальных разрядных линий. Каждая колонка матрицы 230 памяти полного сканирования также содержала бы одну глобальную разрядную линию для, в общей сумме, 32 глобальных разрядных линий, где каждая глобальная разрядная линия соединялась бы с восемью локальными разрядными линиями через четыре логических элемента И-НЕ с тремя состояниями. Следует отметить, что другие конфигурации размера системы матрицы памяти полного сканирования поддерживаются без ограничения вариантов осуществления изобретения.

При считывании ряда памяти один сигнал числовой шины считывания утвержден таким, как сигнал 205 числовой шины считывания. Например, инвертор 215 инвертирует сигнал 205 числовой шины считывания и передает этот инвертированный сигнал 225, который является активным сигналом высокого уровня по отношению к согласующему транзистору 222, для того, чтобы считать соответствующий ряд ячеек RAM, включая ячейку 235 RAM. Предполагая, например, что общая точка 227A разветвления была первоначально предварительно заряжена через нагрузочный транзистор 226А, согласующий транзистор 222 активизирован, что снижает общую точку разветвления 227А до заземления ее или логического 0. Предполагая, что, самое большее, только одна числовая шина считывания активна в любой момент и, таким образом, общая точка 227B разветвления фиксирует логическую 1, логический элемент 228 И-НЕ передает логический 0 из общей точки 227А разветвления к логической 1, чтобы разблокировать логический элемент 255 И-НЕ с тремя состояниями.

Одновременно содержимое ячейки 235 RAM передается в локальную разрядную линию 240A. Предполагая, что нагрузочный транзистор 245 предварительно заряжен локальной разрядной линией 240A посредством сигнала 243 предварительного заряда и что если содержимое ячейки 235 RAM имеет логический 0, то локальная разрядная линия разряжена до логического 0. Разблокированный логический элемент 255 И-НЕ с тремя состояниями тогда передает логический 0 от локальной разрядной линии 240A к логической 1 на глобальной разрядной линии 253. Инвертор в ячейке 260 удержания инвертирует логическую 1 в логический 0 и передает логический 0 на выход 265. Если получен следующий сигнал считывания, который использует глобальную разрядную линию 253, в результате чего считывается ячейка RAM, содержащая логический 0, то глобальная разрядная линия 253 остается в состоянии логической 1, без необходимости к переходу, таким образом экономится расход мощности. Режим работы считывающей части системы матрицы 200 памяти полного сканирования будет описан в дополнительных деталях при обсуждении фиг.3.

Фиг.3 - временная диаграмма 300, показывающая статический характер глобальной разрядной линии, такой как глобальная разрядная линия 253 на фиг.2 в соответствии с вариантом осуществления изобретения. Временная диаграмма 300 показывает пять сигналов, включая сигнал 225 числовой шины считывания, сигнал 243 предварительного заряда локальной разрядной линии (LBL), сигнал 240A локальной разрядной линии (LBL), глобальный сигнал выбора глобальной линии 250 выбора и сигнал 253 глобальной разрядной линии (GBL).

Так, например, фиг.3 будет описана вместе с фиг.2 для ситуации, где два логических 0 последовательно считаны из матрицы 230 памяти полного сканирования. Сначала нагрузочный транзистор 245 предварительно полностью заряжает локальную разрядную линию 240 в состояние логической 1 во время 305. Точно так же нагрузочные транзисторы 226А, 226В предварительно полностью заряжают общие точки 227A и 227B разветвления в состояние логической 1. Числовая шина 225 считывания теперь утверждена во время 310, что приводит к двум совпадающим случаям. Первый: общая точка 227A разветвления приведена к логическому 0 путем разряда через согласующий транзистор 222. Второй: содержимое ячейки 235 RAM, которое, как предполагают, является логическим 0, считывается, разряжая LBL 240A до логического 0.

Возвращаясь к первому случаю, логический элемент 228 И-НЕ получает как входное устройство значение логического 0 от общей точки разветвления 227A, и так как общая точка разветвления 227B не была разряжена, то она остается в состоянии логической 1. Таким образом, во время 315 сигнал глобального выбора 250 является активным, чтобы разблокировать логический элемент 255 И-НЕ с тремя состояниями, после того как LBL 240A был оценен во время 312.

Теперь, когда логический элемент 255 И-НЕ с тремя состояниями разблокирован и он получает как входное устройство логический 0 по локальной разрядной линии 240A, и так как никакие числовые шины считывания, соответствующие набору задающих устройств 210B числовой шины, не были активизированы, локальная разрядная линия 240B остается в состоянии логической 1. Следовательно, во время 320 глобальная разрядная линия 253 переходит в состояние логической 1 и выход 265 данных RAM переходит в состояние логического 0, чтобы соответствовать содержимому ячейки 235 RAM.

Во время 321 сигнал 250 выбора глобальной разрядной линии невозможен до того, как предварительно заряженная сигналом 243 локальная разрядная линия будет разблокирована во время 322. Во время 323 локальная разрядная линия 240A закончила предварительную зарядку через нагрузочный транзистор 245, таким образом, она устанавливается предварительно в состояние логической 1 для следующего активного сигнала числовой шины считывания. Во время 325 активизирован последующий сигнал числовой шины считывания, который снова приводит к двум совпадающим случаям. Первый: общая точка разветвления 227A приведена в состояние логического 0. Второй: содержимое ячейки 235 RAM, которая продолжает быть в состоянии логического 0, считывается, разряжая нагрузочный транзистор 245 и переводя LBL 240A в состояние логического 0 во время 330.

Возвращаясь к первому случаю, логический элемент 228 И-НЕ получает, как входное устройство логический 0 от общей точки разветвления 227A и, так как нагрузочный транзистор 226В не был разряжен, получает логическую 1 от общей точки разветвления 227B. Таким образом, во время 333 идет активный сигнал глобального выбора 250, чтобы разблокировать логический элемент 255 И-НЕ с тремя состояниями. Выходное устройство логического элемента 255 И-НЕ остается в состоянии логической 1. Таким образом, глобальная разрядная линия 253 остается в состоянии логической 1, без перехода, как она это сделала во время 320, что приводит к экономии мощности между последующими считываниями по той же самой глобальной разрядной линии, где значение считывания есть 0. Этот режим работы глобальной разрядной линии 253 относится к статическому режиму работы. Напротив, локальная разрядная линия 240A, так же как стандартные глобальные разрядные линии, динамически переходит при каждом считывании благодаря предварительной зарядке и разрядке емкости локальной разрядной линии независимо от предыдущих считанных данных.

Следует отметить, что хотя вышеупомянутый пример был описан в контексте двух последовательных считываний из той же самой ячейки RAM, глобальная разрядная линия 253 останется высокой для последовательных считываний любой ячейки RAM с теми же самыми данными, которые заканчиваются в любом логическом элементе И-НЕ с тремя состояниями, соединенном с той же самой глобальной разрядной линией.

Фиг.4 показывает детали для одного подходящего варианта осуществления логического элемента 255 И-НЕ с тремя состояниями, представленного на фиг.2. Логический элемент 255 И-НЕ с тремя состояниями включает инверторы 405, логический элемент 410 ИЛИ, логический элемент 420 И-НЕ, логический элемент И 430 и выходной транзисторный комплект, включающий нагрузочный транзистор 440 и согласующий транзистор 450. Как описано выше, логический элемент 255 И-НЕ получает, в качестве входных сигналов, сигнал глобального выбора 250 и локальные разрядные линии 240A и 240B и создает свой выходной сигнал в глобальной разрядной линии 253. Глобальная разрядная линия 253 соединяется с нагрузочным транзистором 440 и согласующим транзистором 450.

Нагрузочный транзистор 440 соединяется с выходным устройством логического элемента 420 И-НЕ. Логический элемент 420 И-НЕ соединяется с выходом логического элемента 410 ИЛИ и глобальным сигналом 250 выбора. Логический элемент 410 ИЛИ соединяется с инверторами 405. Инверторы 405 соединяются с локальными разрядными линиями 240A и 240B.

Согласующий транзистор 450 соединяется с выходом логического элемента 430 И. Логический элемент 430 И соединяется с сигналом глобального выбора 250 и с локальными разрядными линиями 240A и 240B. Глобальная разрядная линия 253 имеет состояние логической 1, когда или локальная разрядная линия 240A, или 240B имеют состояние логического 0, и сигнал глобального выбора 250 имеет состояние логической 1. Глобальная разрядная линия 253 имеет состояние логического 0, когда локальные разрядные линии 240A и 240B и сигнал глобального выбора 250 имеют состояние логической 1. В любой другой комбинации значений, введенных в логический элемент 255 И-НЕ, значение глобальной разрядной линии 253 будет определено разблокированным логическим элементом И-НЕ, который также соединен с ней. Если ни один из логических элементов И-НЕ, соединенных с глобальной разрядной линией 253, не разблокирован, то глобальная разрядная линия 253 поддержит последнее значение, считанное с нее ячейкой 260 удержания.

При использовании выходного комплекта, включающего в себя два транзистора, физические размеры этих транзисторов меньше для данной нагрузки глобальной разрядной линии, чем стандартные выходные комплекты, имеющие больше двух выходных транзисторов. Такое преимущество уменьшает размер печатной платы и собственную емкость на глобальной разрядной линии благодаря выходным транзисторам устройства с тремя состояниями.

Фиг.5 - вариант альтернативного осуществления считывающей части системы 200 матрицы памяти полного сканирования в соответствии с другим вариантом осуществления изобретения. Считывающая часть системы 500 матрицы памяти полного сканирования включает в себя задающие устройства 510 числовой шины считывания, динамические элементы 520 ИЛИ и матрицу 530 памяти полного сканирования, модифицированные согласно сущности изобретения. Задающие устройства 510 числовой шины считывания соединяются как с динамическим элементом ИЛИ 520, так и с матрицей 530 памяти полного сканирования. Динамический элемент ИЛИ 520 соединяется с матрицей 530 памяти полного сканирования через глобальную линию 550 выбора.

Система матрицы 500 памяти полного сканирования отличается от системы матрицы 200 памяти полного сканирования одним набором задающих устройств 510 числовой шины, обеспечивающих входные сигналы в динамический элемент 520 ИЛИ. Одна локальная разрядная линия 540 соединяется с глобальной разрядной линией 553 через инвертор 555 с тремя состояниями и отдельную глобальную линию выбора, такую как глобальная линия 550 выбора, используемую для каждой локальной разрядной линии. Режим работы системы матрицы 500 памяти полного сканирования подобен системе матрицы 200 памяти полного сканирования. Если номера ссылок заменяются для соответствия элементам в фиг.5, то обсуждение временной диаграммы на фиг.3 применимо также к фиг.5.

Фиг.6 показывает детали устройства с тремя состояниями, подходящего для использования, как инвертор 555 с тремя состояниями, представленный на фиг.5. Инвертор 555 с тремя состояниями включает в себя инвертор 605, логический элемент 620 И-НЕ и логический элемент 630 И, нагрузочный транзистор 640 и согласующий транзистор 650. Инвертор 555 с тремя состояниями получает, в качестве входных сигналов, глобальный сигнал 550 выбора и локальную разрядную линию 540 и создает свой выходной сигнал в глобальной разрядной линии 553. Глобальная разрядная линия 553 соединяется с нагрузочным транзистором 640 и согласующим транзистором 650.

Нагрузочный транзистор 640 соединяется с выходом логического элемента 620 И-НЕ. Логический элемент 620 И-НЕ соединяется с выходом инвертора 605 и сигналом 550 глобального выбора. Инвертор 605 соединяется с локальной разрядной линией 540. Согласующий транзистор 650 соединяется с выходом логического элемента 630 И. Логический элемент 630 И соединяется с глобальным сигналом 550 выбора и локальной разрядной линией 540.

Глобальная разрядная линия 553 имеет состояние логической 1, когда локальная разрядная линия 540 имеет состояние логического 0, и сигнал глобального выбора 550 имеет состояние логической 1. Глобальная разрядная линия 553 имеет состояние логического 0, когда локальная разрядная линия 540 и сигнал глобального выбора 550 имеют состояние логической 1. В любой другой комбинации значений, введенных на инвертор 555 с тремя состояниями, значение глобальной разрядной линии 553 будет определено разблокированным инвертором с тремя состояниями, таким как инвертор 555 с тремя состояниями, например, который также соединен с глобальной разрядной линией 553. Если ни один из инверторов с тремя состояниями, соединенных с глобальной разрядной линией 553, не будет разблокирован, то глобальная разрядная линия 553 поддержит последнее значение, считанное с нее благодаря ячейке 560 удержания.

Фиг.7 показывает пример альтернативной компоновки для генерирования сигнала глобального выбора в соответствии с вариантом осуществления изобретения. Альтернативный вариант осуществления может использоваться, чтобы генерировать глобальный сигнал выбора при использовании закодированного адреса памяти, а не декодированного адреса и динамических элементов ИЛИ на фиг.2 и 5. Пример варианта осуществления, представленный на фиг.7, показывает считывающую часть 32×32 системы 700 матрицы памяти полного сканирования. Система 700 включает в себя 5×32 декодер 705, набор задающих устройств числовой шины считывания, такой как задающее устройство 710 числовой шины, и 32×32 матрицу 730 памяти полного сканирования, модифицированную согласно сущности изобретения.

Декодер 5×32 соединяется с наборами задающих устройств числовой шины считывания. Для упрощения показа только один набор задающих устройств 710 числовой шины представлен на фиг.7. Наборы задающих устройств числовой шины считывания соединяются с матрицей 730 памяти полного сканирования. 5×32 декодер получает закодированный адрес памяти, S5-S1 бит. Самый значащий бит, например, S5, соединен с логическим элементом 755 И-НЕ с тремя состояниями через инвертор 720, чтобы генерировать сигнал глобального выбора на глобальной линии 750А выбора. Хотя и не представленная, глобальная (общая) линия 750А выбора также соединена с логическим элементом И-НЕ с тремя состояниями, соответствующим другим 31 биту в ряду из 32 битов, для того, чтобы передать все слово из 32 битов, когда единственная числовая шина считывания активизирована. Логический элемент 755 И-НЕ с тремя состояниями соединяется с двумя локальными разрядными линиями, причем каждая локальная разрядная линия поддерживает восемь ячеек RAM. Также глобальная линия 750А выбора разрешает работу логическим элементам И-НЕ с тремя состояниями, которые поддерживают младший порядок, S5=0,16 рядов памяти.

Самый значащий бит, S5, также непосредственно соединен с логическим элементом 758 И-НЕ с тремя состояниями, который также соединен с глобальной линией выбора 750В. Следует отметить, что глобальная линия выбора 750В также соединяется с логическими элементами И-НЕ с тремя состояниями, не представленными, которые соответствуют другому 31 биту в ряду из 32 битов. Также, глобальная линия выбора 750В разблокирует логические элементы И-НЕ с тремя состояниями, которые поддерживают высший порядок, S5=1,16 рядов памяти.

Следует отметить, что другие логические комбинации закодированных адресных битов для генерирования глобальных сигналов выбора предполагаются настоящим изобретением и могут отличаться согласно другим конфигурациям матрицы памяти полного сканирования. Например, 64×32 матрица памяти полного сканирования использовала бы 6×64 декодер. Используя вариант осуществления логического элемента И-НЕ с тремя состояниями, такого как на фиг.2, два самых значащих бита шести закодированных адресных битов 6×64 декодера использовались бы, чтобы запустить все логические элементы И-НЕ с тремя состояниями. В общем, количество самых значащих адресных битов, нужных для контролирования логических элементов И-НЕ с тремя состояниями, n, определяется выражением:

n=log2(R/br), (3)

(3)

где R - количество рядов матрицы памяти полного сканирования и br - количество RAM ячеек, обслуживаемых устройством с тремя состояниями. Например, в варианте осуществления логического элемента И-НЕ с тремя состояниями 64×32 системы матрицы памяти полного сканирования n равнялось бы log2(64 ряда/16 RAM ячеек на логический элемент И-НЕ с тремя состояниями), который является 2 битами. Посредством варианта осуществления инвертора с тремя состояниями 64×32 системы матрицы памяти полного сканирования n равнялось бы log2(64 ряда/8 ячеек RAM на логический элемент инвертора с тремя состояниями), который является 3 битами.

Фиг.8 - алгоритм, показывающий способ 800 статического переключения глобальной разрядной линии в соответствии с вариантом осуществления изобретения. На этапе 810 множество локальных разрядных линий соединено с глобальной разрядной линией через множество устройств с тремя состояниями. На фиг.2, например, две локальные разрядные линии соединяются через логический элемент И-НЕ с тремя состояниями с глобальной разрядной линией. На фиг.5, например, одна локальная разрядная линия соединяется через инвертор с тремя состояниями с глобальной разрядной линией. На этапе 820 сигнал глобального выбора генерируется, чтобы разрешить работу одному из множества устройств с тремя состояниями. На фиг.2, например, сигнал глобального выбора для логического элемента И-НЕ с тремя состояниями генерируется, когда одна числовая шина считывания из двух наборов задающих устройств числовой шины активизирована. На фиг.5, например, сигнал глобального выбора для инвертора с тремя состояниями генерируется, когда одна из соответствующего набора числовых шин считывания активизирована.

На этапе 830 соответствующая локальная разрядная линия выбрана для запуска выходного устройства разрешенного устройства с тремя состояниями. В варианте осуществления фиг.2 И-НЕ с тремя состояниями распространяет активную локальную разрядную линию как описано. В варианте осуществления фиг.5 инвертор с тремя состояниями распространяет соответствующую локальную разрядную линию, как описано.

Фиг.9 - алгоритм, показывающий способ уменьшения мощности, при последовательном считывании битов, имеющих то же самое значение по глобальной разрядной линии в пределах памяти в соответствии с вариантом осуществления изобретения. На этапе 910 сигнал глобального выбора генерируется, чтобы перевести глобальную разрядную линию к первому уровню. Что касается времени 315 на фиг.3, например, сигнал глобального выбора 250 переходит на активный высокий уровень, чтобы разрешить работу логическому элементу И-НЕ с тремя состояниями 255, после того, как локальная разрядная линия 240A была оценена во время 312. На этапе 920 первый бит считан из памяти. Что касается времени 320 на фиг.3, например, то глобальная разрядная линия 253 переходит к высокому значению после того как логический элемент И-НЕ 255 был оценен. На этапе 930 второй бит считан из памяти. Значение второго бита есть то же самое значение, как и у первого считывания бита. Что касается времени 333 на фиг.3, например, сигнал глобального выбора 250 переходит к активному высокому уровню, чтобы снова разрешить работу логическому элементу И-НЕ с тремя состояниями 255. На этапе 940 глобальная разрядная линия поддерживается на первом уровне в течение считывания второго бита без перехода. Что касается времени 333 на фиг.3, например, то глобальная разрядная линия 253 остается на том же самом уровне, как это было во время 320.

В то время как изобретение раскрыто в контексте множества вариантов осуществления, будет признано, что широкое разнообразие внедрений может использоваться рядовыми специалистами в данной области техники, связанных с указанным выше обсуждением и с формулой изобретения, которая следует ниже.

Изобретение относится к способам и устройству считывания матрицы памяти полного сканирования. Техническим результатом является уменьшение мощности при считывании указанной матрицы. Матрица памяти полного сканирования включает в себя множество локальных разрядных линий и глобальную разрядную линию. Способ запуска глобальной разрядной линии включает в себя этап соединения множества локальных разрядных линий с глобальной разрядной линией через множество устройств с тремя состояниями, генерирования глобального сигнала выбора для разрешения работы одному из множества устройств с тремя состояниями и выбора соответствующей локальной разрядной линии для запуска выхода разрешенного устройства с тремя состояниями. Таким образом, глобальную разрядную линию статически запускают так, чтобы последовательные считывания битов, имеющих одно и то же значение, считанное по глобальной разрядной линии, не приводило бы к переходу состояния глобальной разрядной линии. 2 н. и 11 з.п. ф-лы, 9 ил.

1. Способ запуска общей разрядной линии матрицы памяти полного сканирования, содержащий этапы, на которых

соединяют множество локальных разрядных линий с общей разрядной линией через множество устройств с тремя состояниями;

генерируют общий сигнал выбора для разрешения работы одному из множества устройств с тремя состояниями и

выбирают соответствующую локальную разрядную линию для запуска выхода разрешенного устройства с тремя состояниями, посредством чего последовательные считывания битов, имеющих одно и то же значение, считанное по общей разрядной линии, не приводят к переходу состояния общей разрядной линии.

2. Способ по п.1, в котором выход общей разрядной линии соединяется с ячейкой удержания.

3. Способ по п.1, в котором этап генерирования дополнительно содержит этапы, на которых

компонуют множество транзисторов, заканчивающихся в общей точке разветвления;

получают сигнал считывания в одном из множества транзисторов и

осуществляют переход общей точки разветвления для разрешения работы одному из множества устройств с тремя состояниями в ответ на получение сигнала считывания.

4. Способ по п.1, в котором этап генерирования дополнительно содержит этап, на котором

используют бит из закодированного адреса памяти для генерирования общего сигнала выбора.

5. Способ по п.1, в котором выбранным устройством с тремя состояниями является логический элемент И-НЕ с тремя состояниями.

6. Способ по п.1, в котором выбранным устройством с тремя состояниями является инвертор с тремя состояниями.

7. Способ по п.1, в котором устройство с тремя состояниями из множества устройств с тремя состояниями включает в себя выходной транзисторный комплект из двух транзисторов.

8. Способ уменьшения мощности считывания при считывании последовательных битов, имеющих одно и то же значение, по общей разрядной линии в пределах памяти, содержащий этапы, на которых

генерируют общий сигнал выбора для перехода общей разрядной линии на первый уровень, причем общий сигнал выбора разрешает работу устройству с тремя состояниями;

считывают первый бит из памяти, имеющий некоторое значение;

считывают второй бит из памяти, имеющий то же самое значение как и первый бит; и

поддерживают общую разрядную линию на первом уровне в течение считывания второго бита без перехода на второй уровень.

9. Способ по п.8, в котором этап генерирования дополнительно содержит этапы, на которых

компонуют множество транзисторов, заканчивающихся в общей точке разветвления;

получают сигнал считывания в одном из множества транзисторов и

осуществляют переход общей точки разветвления для активирования общего сигнала выбора.

10. Способ по п.8, в котором этап генерирования дополнительно содержит этап, на котором

используют бит из закодированного адреса памяти для генерирования общего сигнала выбора.

11. Способ по п.8, в котором выбранным устройством с тремя состояниями является логический элемент И-НЕ с тремя состояниями.

12. Способ по п.8, в котором выбранным устройством с тремя состояниями является инвертор с тремя состояниями.

13. Способ по п.8, в котором логический элемент И-НЕ с тремя состояниями включает в себя выходной транзисторный комплект из двух транзисторов.

| US 5357477 А, 18.10.1994 | |||

| СХЕМНОЕ УСТРОЙСТВО С ИСПЫТАТЕЛЬНОЙ СХЕМОЙ | 1997 |

|

RU2183361C2 |

| US 6584034 B1, 24.06.2003 | |||

| РЕЖИМ СТИРАНИЯ СТРАНИЦЫ В МАТРИЦЕ ФЛЭШ-ПАМЯТИ | 1999 |

|

RU2222058C2 |

Авторы

Даты

2010-05-27—Публикация

2006-06-05—Подача