5

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для обучения | 1988 |

|

SU1663618A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Микропрограммное устройство управления | 1985 |

|

SU1315974A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1987 |

|

SU1472913A1 |

| Устройство для сопряжения двух вычислительных машин | 1987 |

|

SU1474665A1 |

| Устройство для синхронизации распределенной вычислительной системы | 1988 |

|

SU1508201A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

Изобретение относится к области вычислительной техники и может быть использовано для отладки программ микропроцессорных вычислительных комплексов. Цель изобретения - повышение быстродействия при отладке. В состав системы входят блок 1 обработки, блок 3 отображения, коммутатор 5, дешифратор 8, генератор 7, блок 9 задания перехода, блок 10 синхронизации, счетчик 11 времени и блок 12 памяти. Новые конструктивные признаки системы позволяют реализовать непосредственный переход из заданной точки основной памяти в заданную точку теневой памяти так, как если бы точка перехода находилась в программе того же блока памяти, что и команда перехода. 1 з.п.ф-лы, 15 ил.

4 00

J 1

Ј

Изобретение относится к вычислительной технике и может быть использовано для отладки программ микропроцессорных вычислительных комплексов.

Цель изобретения - повышение быстродействия при отладке.

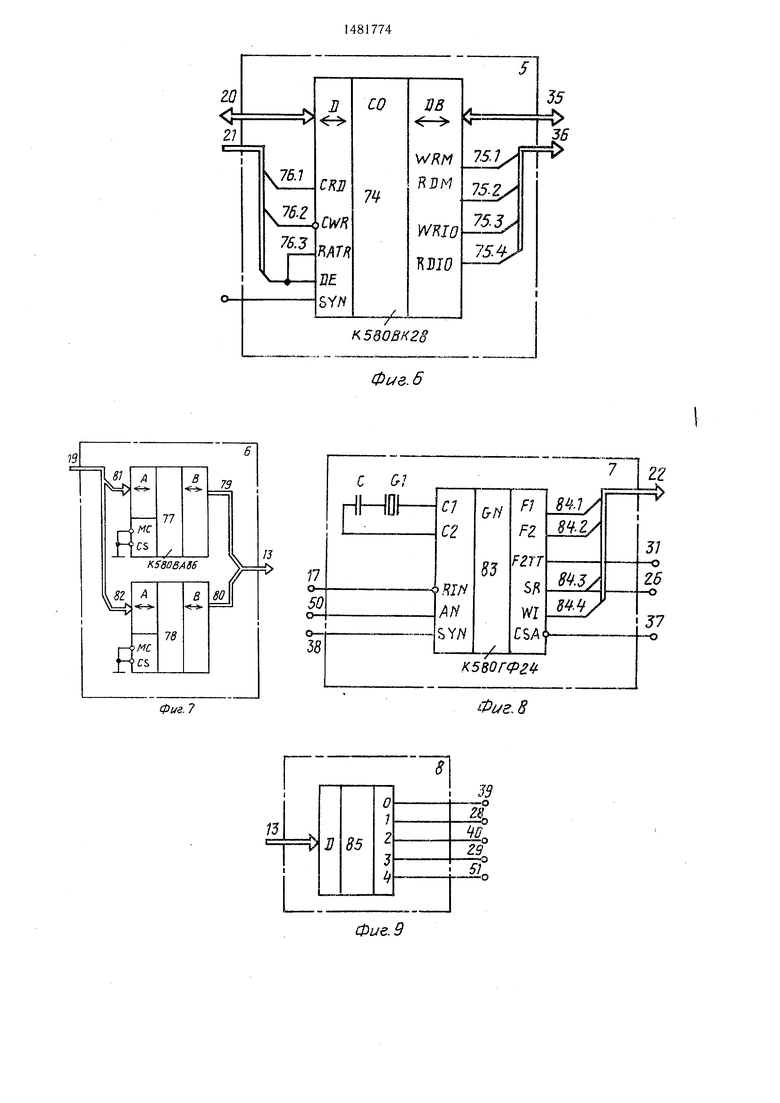

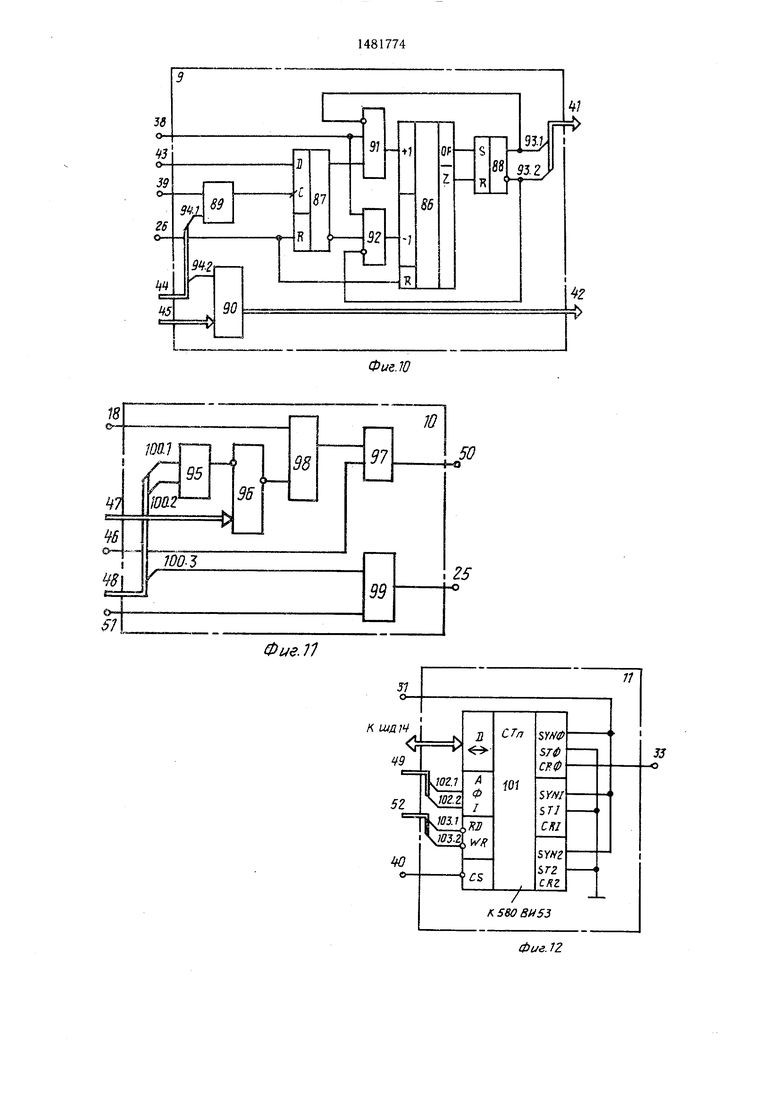

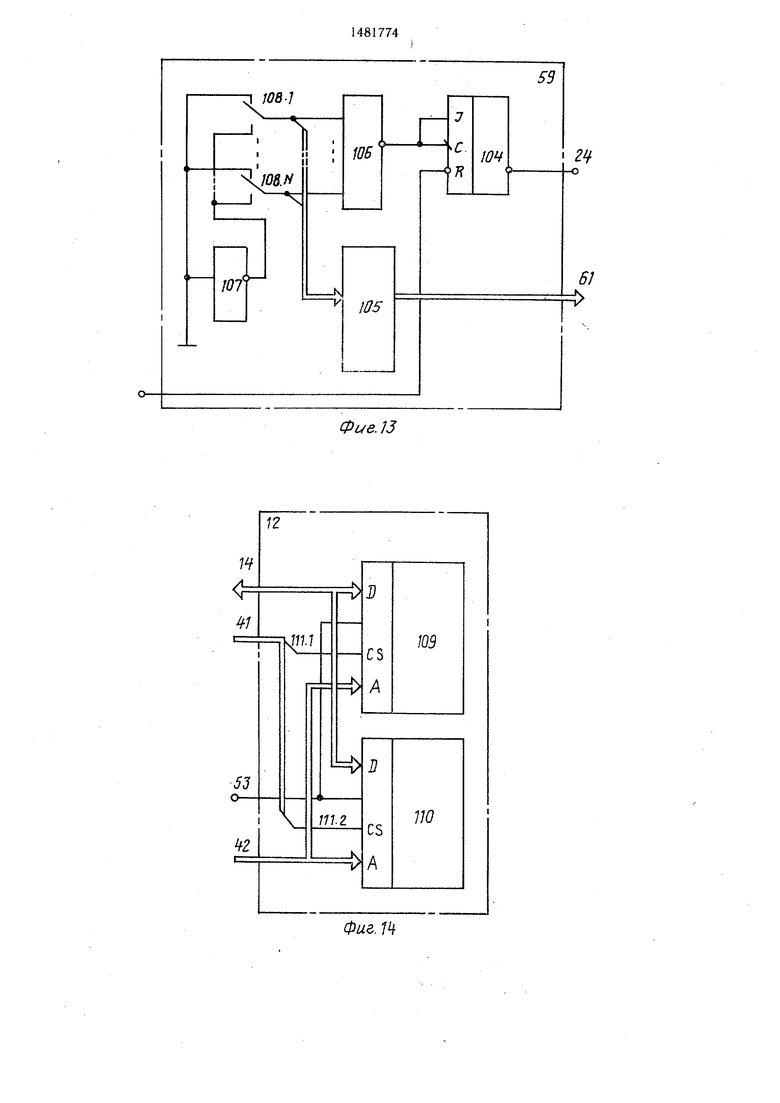

На фиг. 1 изображена структурная схема системы; на фиг. 2 - схема блока обработки; на фиг. 3 - схема блока ввода; на фиг. 4 - схема блока отображения; на фиг. 5 - схема блока асинхронной связи; на фиг. 6 - коммутатор сигналов обращения; на фиг. 7 - схема шинного формирователя адреса; на фиг. 8 - схема генератора; на фиг. 9 - схема дешифратора; на фиг. 10 - схема блока задания перехода; на фиг. 11 - схема блока синхронизации; на фиг. 12 - счетчик времени; на фиг. 13 - клавиатура;, на фиг. 14 -- блок памяти; на фиг. 15 - временные диаграммы работы системы.

Система для отладки программ (фиг. 1) содержит блок 1 обработки, блок 2 ввода, блок 3 отображения, блок 4 асинхронной связи, коммутатор 5 сигналов обращения, шинный формирователь 6 адреса, тактовый генератор 7, дешифратор 8, блок 9 задания перехода, блок 10 синхронизации,счетчик 11 времени, блок 12 памяти, шины адреса 13, данных 14 и управления 15. Символами 16-53 обозначены входы и выходы блоков и узлов системы. Выход 16 - выход блока 4, вход 17 установки в исходное состояние системы, вход 18 ответ блока 10, группа адресных выходов 19 микропроцессора 1, входы-выходы 20 блока 1, выходы 21 управления микропроцессора 1, тактовый вход 22 блока 1, выход 23 блока 2 ввода, вход 24 запроса прерывания блока 1, выход 25 подтверждения прерывания системы, вход 26 начальной установки блока 3 отображения и блока 9 задания перехода, вход 27 управления записи и чтения блока 3, вход 28 выбора устрой- ства, выход 29 дешифратора 8, адресный выход 30 системы, выход 31 генератора 7, груи-па управляющих выходов 32 системы, выход 33 переполнения счетчика, выход 34 шины данных 14, входы-выходы 35 коммутатора 5, группа 36 управляющих выходов коммутатора 5, тактовый вход 37 коммутатора 5, выход 38 блока 1, выходы 39 и 40 дешифратора 8, выход 41 признака перехода блока 9 задания перехода, адресный выход 42 блока 9, входы 43-45 блока 9, входы 46- 48 блока 10, вход 49 счетчика 11 времени, выход 50 блока 10, выход 51 дешифратора 8, вход 52 счетчика 11 времени, вход 53 блока 12 памяти.

Блок 1 (фиг. 2) предназначен для выполнения программ отладки или других заданных программ.

Он может быть реализован на известном БИС процессоре, например, типа К580ИК80 или другом аналогичном.

Q 5

5 0 5 о 5 0

5

Блок I содержит микропроцессор 54, группа адресных выходов 55 которой образует группу 19 адресных выходов блока 1. Группа 56 входов-выходов данных блока 54 образует одноименную группу 20 входов- выходов блока 1.

Выходы RD, WR, WI, RATR и SYN микропроцессора 54 образуют соответственно выходы чтения (приема) 57.1, записи 57.2, ожидания 57.3, запроса захвата 57.4 и синхронизации 57.5 группы 21 управляющих выходов блока .

Вход 24 запроса прерывания блока 1 является одноименным входом (RA) микропроцессора 54.

Входы первого 58.1 - четвертого 58.2 разрядов группы 22 входов блока 1 соединены соответственно с первым F1, вторым F2 входами тактовых сигналов, входом начальной установки (R) и входом запроса захвата (RA) блока 54.

Алгоритмы функционирования блока 1 полностью идентичны соответствующим алгоритмам известного микропроцессора К580ИК80.

Блок 2 ввода (фиг. 3) содержит клавиатуру 59 и шинный формирователь 60, группа выходов которого образует группу 23 выходов блока 2. Вход 25 блока 2 соединен с управляющим (CS) входом формирователя 60 и входом клавиатуры 59, группа 61 выходов и управляющий выход которой соединены соответственно с группой входов формирователя 60 и выходом 24 блока 2.

Блок 2 предназначен для ввода данных с клавиатуры 59 па шину 14 данных системы. При нажатии хотя бы одной из клавиш клавиатуры 59 вырабатывается сигнал запроса прерывания на выходе 24 блока 2, который поступает на вход РО микропроцессора 54 (фиг. 2).

После формирования блоком 10 синхронизации сигнала подтверждения прерывания на выходе 25 (фиг. 1) включается на передачу формирователь 60 блока 2 (фиг. 3), а с выходов 61 клавиатуры 59 осуществляется выдача кода данных.

Этот код данных через формирователь 60 и выходы 23 блока 2 передается на шину данных 14 системы (фиг. 1) для приема в блок 1 известным образом.

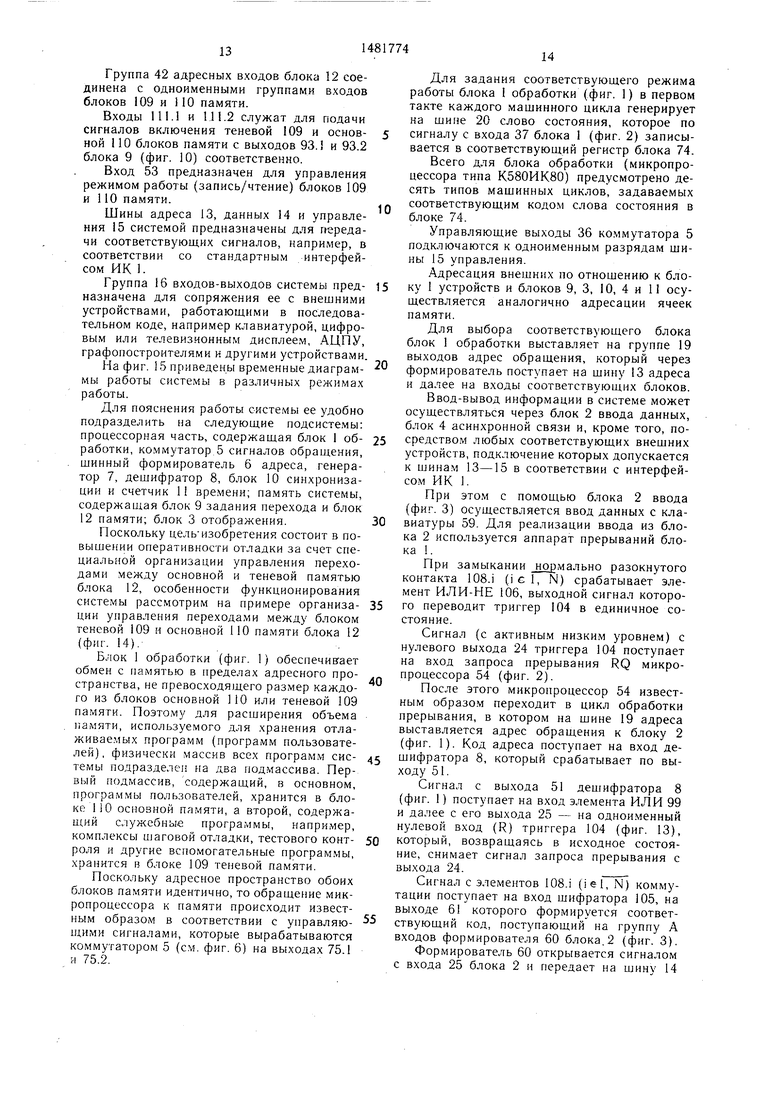

Блок 3 отображения (фиг. 4) содержит блок 62 ввода-вывода параллельной информации различного формата, дисплей 63 и клавиатуру 64.

Группа выходов 65 данных каналов ВО блока 62 соединена с группой информационных входов дисплея 63.

Разряды 66.1 и 66.2 группы выходов 66 данных канала В1 блока 62 соединены соответственно с группами управляющих входов дисплея 63 и клавиатуры 64.

Группа 67 информационных выходов клавиатуры 64 соединена с группой входов канала В2 блока 62.

Группа 14 входов-выходов данных блока 3 соединена с одноименной группой входов- выходов блока 62.

Группа 13 адресных входов, входы 28 и 26 блока 3 соединены соответственно с ад- ресными входами (А) выбора каналов, входом выбора устройства (CS) и входом (R) начальной установки блока 62.

Входы разрядов управления чтением 68.1 и записью 68.2 группы 27 входов блока 3 сое- динены соответственно с входами чтения (RD) и записи (WR) данных блока 62,

Блок 3 предназначен для отображения информации при отладке. Он может быть выполнен по известной схеме с использованием программируемого устройства ввода- вывода параллельной информации различного формата, а также знакосинтезирующего дисплея и матричной клавиатуры. При этом канал В1 применяется известным образом для сканирования дисплея и клавиатуры, канал В 0 - для записи кода очередного отображаемого разряда дисплея, а канал В2 - для чтения кода нажатой клавиши с матрицы клавиатуры. Дешифрирование и сканирование клавиатуры может осуществляться программно.

В частности, в блоке 3 к блоку 62 может быть подключено репрограммируемое ПЗУ для хранения информации при отладке.

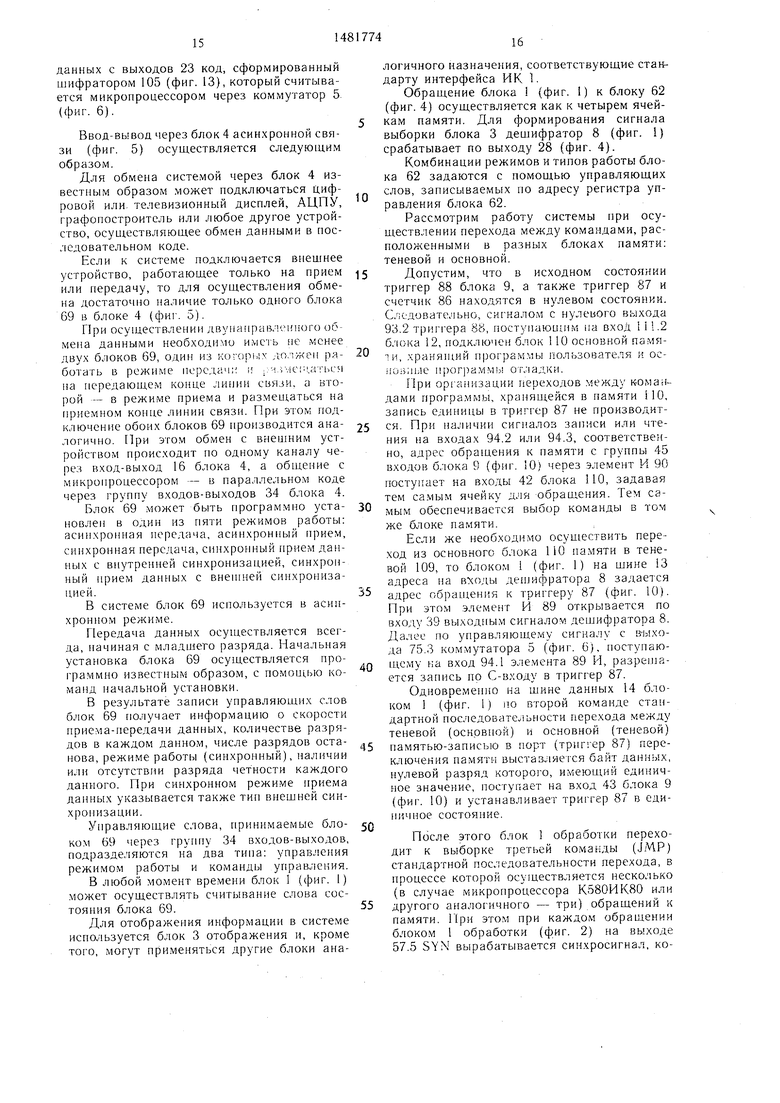

Блок 4 асинхронной связи (фиг. 5) содержит синхронно-асинхронный приемопередатчик 69, группа входов-выходов (D) дан- ных которого соединена с группой 34 входов-выходов данных блока 4.

Входы 31, 30, 29 блока 4 соединены соответственно с входами синхросигнала (SIN), управление/данные (AD) и выбора устройства (CS) приемопередатчика 69.

Вход приемника и выход 70 передатчика приемопередатчика 69 образуют группу 16 входов-выходов блока 4.

Вход 33 блока 4 соединен с входами синхронизации передатчика CD и приемника CD приемопередатчика 69.

Выход 71 запроса приемника терминала (RTS) приемопередатчика 69 соединен с входом готовности приемника терминала ($TS) приемопередатчика 69.

Выход 72 запроса передатчика термина- ла (DTR) соединен с входом готовности передатчика терминала (DSR) приемопередатчика 69.

Входы разрядов управления чтением 73.1 и записью 73.2 группы 32 управляющих вхо- дов коммутатора 5 соединены соответственно с одноименным входами RD и WR приемопередатчика 69.

Блок 4 предназначен для организации двунаправленного обмена данными между системой и внешними устройствами в последовательном коде. Причем в качестве внешних устройств могут использоваться известным образом клавиатура, цифровой или

0

Q

5 5

0

5

5

0

телевизионный дисплей, АЦПУ, графопостроители и др. устройства.

Обмен информацией с такими устройствами может осуществляться по одному каналу, на входе и выходе которого подключаются аналогично показанному на фиг. I, 5 блоки 4, работающие в режимах приема и передачи.

Блок 4 может быть выполнен на известной микросхеме типа К580ВВ51А (на фиг. 5 показаны только те входы и выходы приемопередатчика 69, которые необходимы для пояснения его работы).

При передаче данных приемопередатчик 69 преобразует данные в параллельном коде в последовательность символов со служебной информацией и выдает ее в канал с различной (задаваемой программой) скоростью.

Причем данные могут передаваться по каналам связи в синхронном или асинхронном режиме. В системе блок 4 работает в режиме внешней синхронизации.

Группа входов-выходов 34 данных предназначена для приема н передачи данных в параллельном коде.

Вход 31 предназначен для подачи синхросигналов от генератора 7.

Вход 30 (управление/данные) служит для подачи сигнала записи-чтения данных или управляющих сигналов. Нулевой уровень сигнала на этом выходе указывает на возможность записи-чтения данных, а единичный разрешает запись в приемопередатчик 69 управляющего слова или считывание информации о состоянии схемы.

Вход 73.1 чтения предназначен для подачи входного сигнала, разрешающего передачу данных и информации состояния приемопередатчика 69 на шину данных системы.

Вход 73.2 записи предназначен для подачи входного сигнала, разрешающего передачу данных и управляющего слова с шины данных системы в приемопередатчик 69.

Вход 29 предназначен для выбора кристалла (CS) приемопередатчика 69.

Входы 33 синхронизации (CD) приема и передачи предназначены для приема тактовых сигналов от внешнего устройства синхронизации.

Вход STS готовности приемника терминала предназначен для информирования приемопередатчика 69 о готовности приемника терминала принять в ответ на сигнал запроса по выходу RTS запроса приемника терминала.

Выход 70.1 и вход 70.2 являются выходом передатчика и входом приемника приемопередатчика 69 соответственно.

Вход DSR готовности передатчика терминала предназначен для подачи входного сигнала, информирующего приемопередатчик 69 о готовности внешнего передатчика к посылке информации по каналу связи. Состояние сигнала на этом входе может быть определено no разряду D 7 слова состояния приемопередатчика 69 при его чтении.

Выход DTR предназначен для подачи сигнала, информирующего внешний передатчик о готовности канала приемника приеме- передатчика 69 к приему информации и проверке готовности передатчика к работе.

Выход RTS запроса приемника терминала приемопередатчика 69 предназначен для подачи выходного сигнала запроса о готов- ностн приемника терминала к приему данных.

Для работы с блоком в него записываются команды начальной установки. Посредством записи управляющих слов приемопередатчика 69 задается скорость приема- передачи данных, количество разрядов в каждом данном, число разрядов останова, режим работы, наличие или отсутствие разряда четности каждого данного и др. информация.

При этом управляющие c. ioi.j подразделяются на два типа гк ч р кни режима и инструкции коман i

При обмене дачными npnevi, передатчик 69 преобразует информацию ич паралчель- ного кода в последовательный и наоборот. Причем со стороны системы осуществляется обмен в параллельном коде, а со стороны внешних устройств - в последовательном.

Дешифратор сигналов обращения (фиг.6) содержит блок 74 формирования магистралей управления.

Группа 20 входов-выходов данных ком- м тагора 5 соединена с одноименной первой группой входов-выходов (D) блока 74.

Вход 37 и группа 35 входов-выходов коммутатора 5 соединены соответственно с входом управления системной шпион (SVN) и второй группой входов-выходов данных (DB-) блока 74.

Выходы управления записью (WRM), чтением (RDM), приемом (WRJO) и выдачей (RDJO) блока 74 образуют соответственно выходы одноименных разрядов 75.1, 75.2, 75.3 и 75.4 группы 36 выходов коммута- юра 5.

Входы разрядов 76.1, 76.2 и 76.3 гр ппы 21 входов коммутатора 5 соединены соогвег ственпо с входами чтения (CRDj, записи (CWR), разрешения доступа к магистрали (RATR) блока 74.

Вход управления системной шиной (DE) соединен с входом разряда 76.3 группы 21 входов коммутатора 5.

Коммутатор 5 предназначен для организации управ,тения доступом микропроцессо- ра к шине данных, а также для формирования на группе 36 выходов сигналов на шину управления системы на основании выходных управляющих сигналов блока I обработки, поступающих на группу 21 входов коммутатора 5.

Алгоритм функционирования коммутатора 5 идентичен известному для микросхемы К580ВК28.

Шинный формирователь 6 адреса (фиг. 7) содержит шинные формирователи 77 и 78, выходы 79 и 80 - группу 13 выходов формирователя 6, информационные входы 81 и 82 которых образуют группу 19 входов формирователя 6. Управляющие входы (МС и CS) формирователей 77 и 78 соединены с шиной нулевого потенциала.

Формирователи 77 и 78 могут быть реализованы на известных микросхемах, например, типа К580ВА86.

Формирователь 6 предназначен для соединения группы 19 адресных выходов блока 1 обработки с шиной 13 адреса системы.

Генератор 7 (фиг. 8) содержит генератор 83 тактовых импульсов, который может быть выполнен на известной микросхеме типа К580ГФ24. или другой аналогичной.

Выходы 84.1, (F 1).84.2 (F2),31 (F21T), 84,3 (SR), 84.4 (WI) и 37 (CSA) предназначены соответственно для выдачи сигналов синхроимпульсов, сигнала фазы (уровнем l 1 j, сигнала «Сброс, сигнала готовности и строба фиксации состояния.

Выходы разрядов 84.1, 84.2, 84.3, 84.4 группы 22 выходов генератора 7 (фиг. 8) соединены соответственно с входами 58.1 (F 1), 58.2 (F 2), 58.3 (R) и 58.4 (RA) микропроцессора 54 (фиг. 2).

Влоды С1 и С2 генератора 83 (фиг. 8) предназначены для подключения колебательного контура, собранного из последовательно включенных емкости С и кварцевого резонатора G 1.

Входы 7 (RIN), 50 (AN), 38 (SYN) генератора 83 предназначены для подачи сигналов сброса, готовности и синхронизации соответственно.

Генератор 7 предназначен для формирования периодической последовательности импульсов положительной полярности с несовпадающими фазами опорной частоты F 1 и F 2 на выходах 84.1 и 84.2.

Кроме того, на выходе 31 (F2TT) формируется тактовый импульс F2TT положительной полярности со стандартными уровнями TTL логики, на выходе 37 - импульс стробирования состояния системы коммутатора 5 (фиг. I).

На выходе SR (фиг. 8) формируется сигнал сброса микропроцессора, а на выходе WI - сигнал, информирующий процессор о готовности системы.

Дешифратор 8 (фиг. 9) содержит дешифратор 85, группа 13 входов которого является группой входов дешифратора 8, а нулевой --- четвертый выходы образуют соответственно выходы 39, 28, 40, 29 и 51 дешифратора 8.

Дешифратор 8 предназначен для задания собственного адреса устройства и блоков,, к которым подключены его выходы.

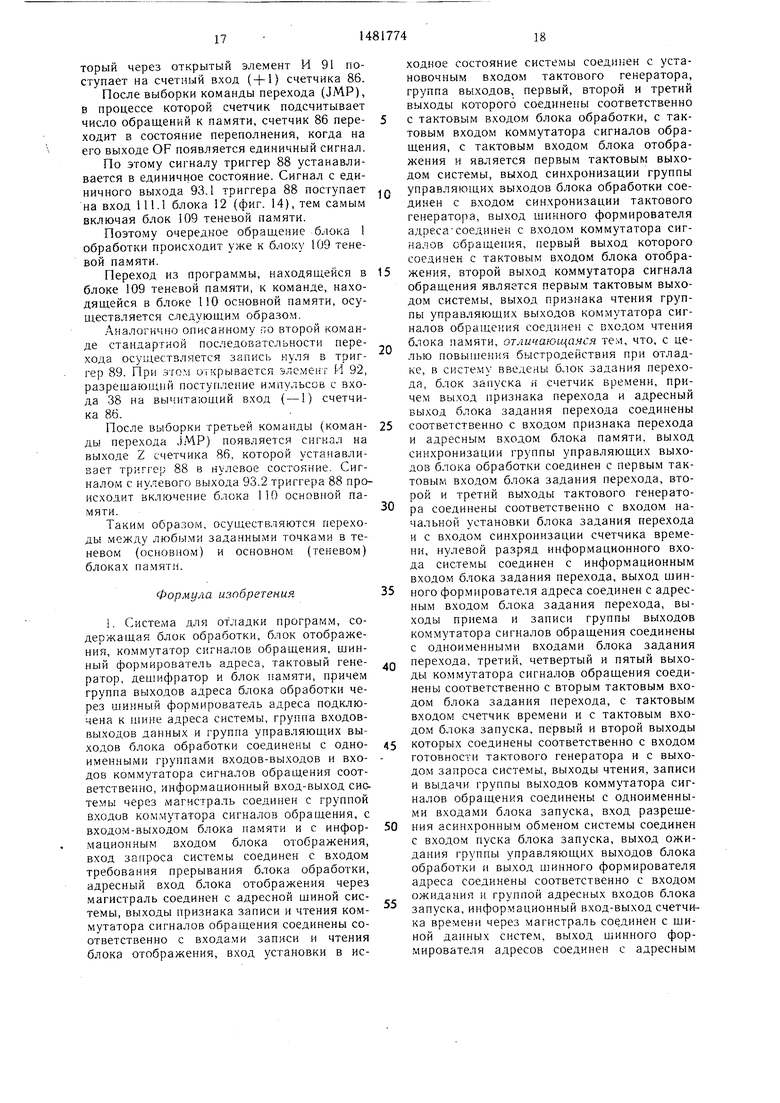

Блок 9 задания перехода (фиг. 10) содержит счегчик 86, первый триггер 87, второй

триггер 88, первый 89, второй 90, третий 91 и четвертый 92 элементы И.

Прямой 93.1 и инверсный 93.2 выходы триггера 88 образуют группу 41 выходов блока 9.

Входы разряда приема 94. и записи 94.2 группы 44 управляющих входов блока 9 соединены соответственно с первым входом элемента И 89 и первым входом элемента И 90, группы информационных входов 45 блока 9 соединены с группой входов элемен- та И 90, группа выходов которого соединена с группок выходов 42 блока 9. Выходы переполнения (OF) и нулевого состояния (Z) счетчика 86 соединены соответственно с единичным и нулевым входами тригге- ра 88, единичный выход которого соединен с первым входом элемента И 9.

Выходы элементов И 91 и И 92 соединены соответственно с суммирующим (-f-1) и вычитающим (- I) входами счетчика 86 соответственно.

Вход 26 блока 9 соединен с нулевым входом (R) триггера 87 и установочным входом счетчика 86.

Единичный и нулевой выходы триг- гера 87 соединены с вторыми входами элементов И 9 и И 92 соответственно.

Вход 39 блока 9 соединен с вторым входом элемента И 89, выход которого соединен с синхровходом триггера 87.

Вход 38 блока 9 соединен с третьим входом элемента И 91 и вторым входом элемента И 92.

Вход 43 блока 9 соединен с информационным (D) входом триггера 87.

Блок 9 предназначен для переключения блоков теневой и основной памяти по коман- де вывода в порт (триггер 87) переключения памяти с задержкой на время выборки блоком 1 команды перехода (JMP) из той же области памяти, из которой осуществлял-ась выборка команды вывода в порт переключения.

Счетчик 86 предназначен для отсчета времени задержки на время выборки команды перехода (JMP). Время задержки отсчитывается путем подсчета сигналов синхронизации (SYX1), поступающих на вход 38 блока 9 с выхода синхронизации 57.5 (фиг. 2) блока обработки 1 в начале каждого машинного цикла.

Сигнал на .выходе переполнения OF (нулевого состояния Z) выдается при отра- ботке такого количества машинных циклов, которое необходимо для выборки команды перехода (JMP) при отсчете от нулевого состояния счетчика (состояния переполнения) .

Если счетчик 86 находится в нулевом сое- тоянии, то при поступлении импульсов на вычитающий вход (- 1) его состояние не изменяется.

5

° 5

0

5

0

5 0

5

Q

5

Триггер 87 выполняет роль порта начала переключения типа памяти, а триггер 88 - окончания переключения.

Элемент И 89 предназначен для формирования сигнала записи в триггер 87 переключения блоков памяти (теневой и основной).

Элемент И 90 предназначен для управления передачей кода адреса в блок 12 памяти при наличии управляющего сигнала записи с входа 94.2 блока 9.

Элемент И 91 предназначен для управления подачей на счетный вход ( + 1) счетчика 86 импульсов синхронизации с входа 38 блока 9 для задержки переключения с основной памяти на теневую.

Триггер 88 предназначен для выдачи на выходы 93.1 и 93.2 сигнала включения основной и теневой памяти в блоке 12 памяти.

Единичное (нулевое) состояние триггера 88 соответствует включению теневой (основной) памяти в блоке 12.

Единичное (нулевое) состояние триггера 87 соответствует переходу к теневой (основной) памяти.

Блок 10 синхронизации (фиг. II) содержит первый 95, второй 96, третий 97 элементы И, первый 98 и второй 99 элементы ИЛИ.

Входы 18, 100.1, 100.2, 100.3, 46, 51 и группа 47 входов блока 10 соединены соответственно с первым входом элемента ИЛИ 98, первым, вторым входами элемента И 95, первым входом элемента ИЛИ 99, первым входом элемента И 97, вторым входом элемента ИЛИ 99 и группой входов элемента И 96.

Выход элемента И 95 соединен с входом элемента И 96, выход которого соединен с вторым входом элемента ИЛИ 98.

Выход элемент ИЛИ 98 соединен с вторым входом элемента И 97, выход которого является выходом 50 блока 10.

Выход элемента ИЛИ 99 соединен с выходом 25 блока 10.

Блок 10 предназначен для формирования сигналов синхронизации обмена с внешними устройствами на выходе 50 и подтверждения прерывания на выходе 25.

Вход 18 предназначен для подачи сигнала «Ответ с соответствующего разряда шины 15 управления системы (фиг. 1). Этот сигнал формируется при асинхронном обмене с внешними устройствами, которые могут подключаться к шинам 13, 14 и 15 системы в соответствии с известным интерфейсом ИК 1.

Входы разрядов 100.1, 100.2 и 100.3 группы 48 входов блока 10 предназначены для подачи сигналов чтения, записи и выдачи с соответствующих разрядов шины 15 управления системы (фиг. 1).

Группа 47 входов предназначена для подачи сигналов выбора собственного адреса блока 10 с шины 13 адреса системы (фиг. 1).

Вход 48 предназначен (фиг. 11) для подачи сигнала - признака нахождения блока 1 (фиг. 2) в состоянии ожидания. Этот сигнал поступает с выхода 57.3 микропроцессора 54.

Вход 51 предназначен для подачи сигнала, разрешающего формирование сигнала подтверждения на выходе 25 с выхода 51 дешифратора 8.

Выход 50 предназначен для формирова- ния сигнала готовности на вход AN генератора 7 (фиг. 8).

Счетчик 11 (фиг. 12) времени предназначен для организации временных интервалов при отладке, а также для синхронизации работы блока 4 (фиг. 1) асинхронной связи.

Счетчик 11 (фиг. 12) может быть выполнен на известной микросхеме типа К580ВИ53.

Группа 14 входов-выходов счетчика 11 соединена с группой одноименных входов

иыходов блока 101 счета.

Входы первого 102.1 и второго 102.2 разрядов группы 49 входов счетчика 11 соединены соответственно с входами А0 и А1 блока 101.

Входы разрядов управления чтением 103.1 и записью 103.2 группы 52 входов счетчика 1 1 соединены соответственно с входами чтения (RD) и записи (WR) блока 101.

Вход 40 счетчика 11 соединен с входом CS выбора устройства блока 101.

Вход 31 счетчика 11 соединен с входами такювой частоты первого (SYN 0), второго (SYN1) и третьего (SYN2) каналов.

Выход (CR0) первого канала блока 101 соединен с выходом 33 блока 11.

Входы разрешения работы первого (ST0) второго (ST1) и третьего (ST2) каналов блока 101 соединены с шиной нулевого потенциала источника питания.

Выходы второго (CR1) и третьего (CR2) каналов блока 101 не используются.

Входы-выходы данных (D) блока 101 предназначены для передачи данных и управ- ляющих слов между блоками 1 (фиг. 1, 2) и выбранными каналами блока 101.

Входы 102.1 и 102.2 блока 101 предназначены для задания блоку 101 выбора одного из каналов или регистра управления.

Входы управления чтением (RD) и запись (WR) блока 101 предназначены для подачи сигналов на выдачу данных из внутренних регистров блока 101 на входы-выходы 14 данных блока 101 и на запись данных с входов-выходов 14 в блок 101.

Всход CS блока 101 предназначен для подачи сигнала выбора микросхемы.

Входы SYN, ST и выход CR каждого из трех каналов блока 101 предназначены для подачи импульсов входной частоты сигнала разрешения работы и выдачи выходных сиг- налов.

В системе блок 101 используется в режиме генератора тактовых импульсов.

Режим работы блока 101 задается известным образом при начальной установке с прмощью команд вывода данных из блока 1 путем записи управляющего слова в регистр режима канала.

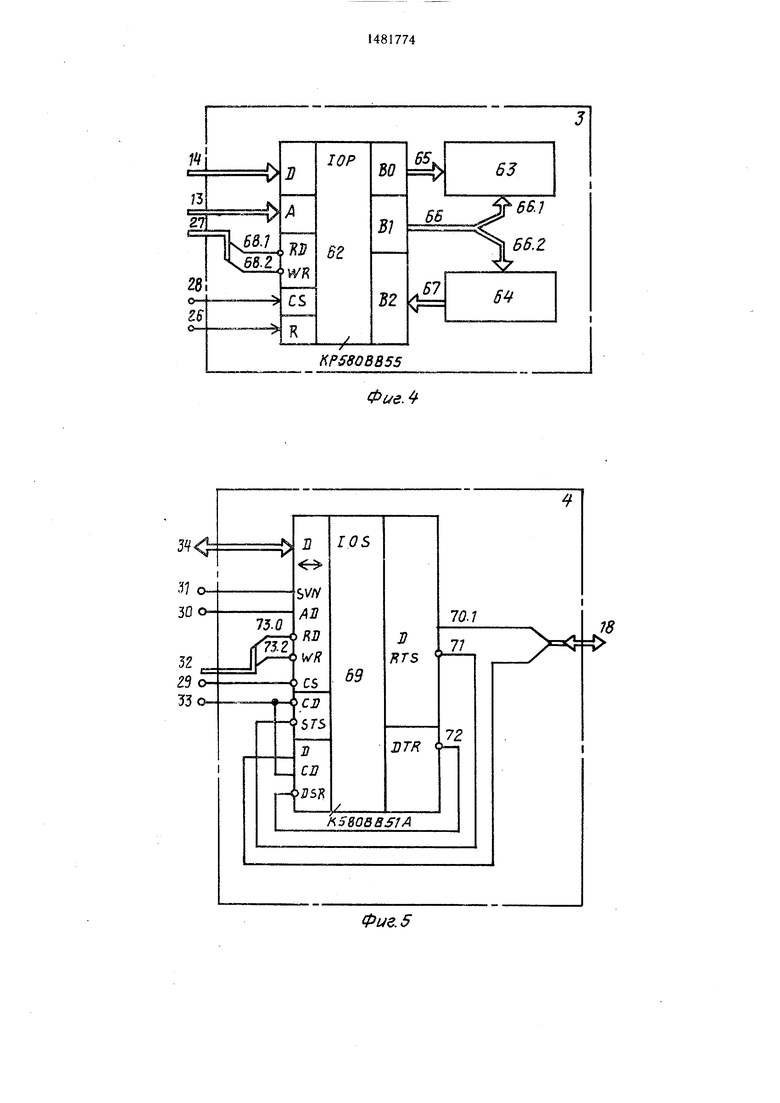

Клавиатурами (фиг. 13) содержит триггер 104, шифратор 105, элемент ИЛИ-НЕ 106, элемент НЕ 107, группу 108 элементов коммутации.

Нулевой выход триггера 104 является выходом 24, а группа выходов шифратора 105 образует группу 61 выходов клавиатуры 59.

Нормально замкнутые контакты элементов 108.1 -108.N коммутации и вход элемента НЕ 107 соединены с шиной нулевого потенциала источника питания. Выход элемента НЕ 107 соединен с нормально разомкнутыми контактами элементов 108.1 -108.X коммутации, выходы которых соединены с входами шифратора 105 и входами элемента ИЛИ-НЕ 106.

Выход элемента ИЛИ-НЕ соединен с J- и С-входами триггера 104, нулевой вход (R) которого подключен к входу 25 клавиатуры 59.

Клавиатура 59 предназначена для осуществления внешнего ввода данных в систему для отладки.

Триггер 104 предназначен для формирования сигнала запроса в микропроцессор 1 на выходе 24 клавиатуры 59.

Шифратор 105 предназначен для формирования кода, соответствующего сигналу, который поступает с одного из элементов 108.1 -108.N коммутации.

Элемент ИЛИ-НЕ 106 предназначен для формирования сигнала запроса в триггер 104 при замыкании одного из элементов 108.1 - 108.N коммутации.

При замыкании одного из элементов 108.1 -108.N коммутации на выходе С1 шифратора устанавливается соответствующий код для передачи на шину 14 данных систем ( фиг. 1). Кроме того, выходным сигналом элемента ИЛИ-НЕ 106 триггер 104 устанавливается в единичное состояние, вырабатывая инверсный сигнал запроса на выходе 24. По этому сигналу блок 1 переходит в режим прерывания и подает на вход 25 клавиатуры 59 сигнал подтверждения прерывания, по которому осуществляется возврат триггера 104 в исходное состояние и снятие сигнала запроса.

Блок 12 памяти (фиг. 14) содержит блоки теневой 109 и основной 110 памяти, входы- выходы данных (D) которых соединены с вхо- дом 14 данных блока 12. Входы управления включением блоков теневой 109 и основной НО памяти группы 41 управляющих входов блока 12 соединены соответственно с входами выбора (CS) блоков 109 и 110.

Управляющий вход 53 блока 12 соединен с управляющими входами блоков 109 и 110.

Группа 42 адресных входов блока 12 соединена с одноименными группами входов блоков 109 и НО памяти.

Входы 111.1 и 111.2 служат для подачи сигналов включения теневой 109 и основ- ной 110 блоков памяти с выходов 93. и 93.2 блока 9 (фиг. 10) соответственно.

Вход 53 предназначен для управления режимом работы (запись/чтение) блоков 109 и 110 памяти.

Шины адреса 13, данных 14 и управления 15 системой предназначены для передачи соответствующих сигналов, например, в соответствии со стандартным интерфейсом ИК 1.

Группа 16 входов-выходов системы пред- назначена для сопряжения ее с внешними устройствами, работающими в последовательном коде, например клавиатурой, цифровым или телевизионным дисплеем, АЦПУ, графопостроителями и другими устройствами

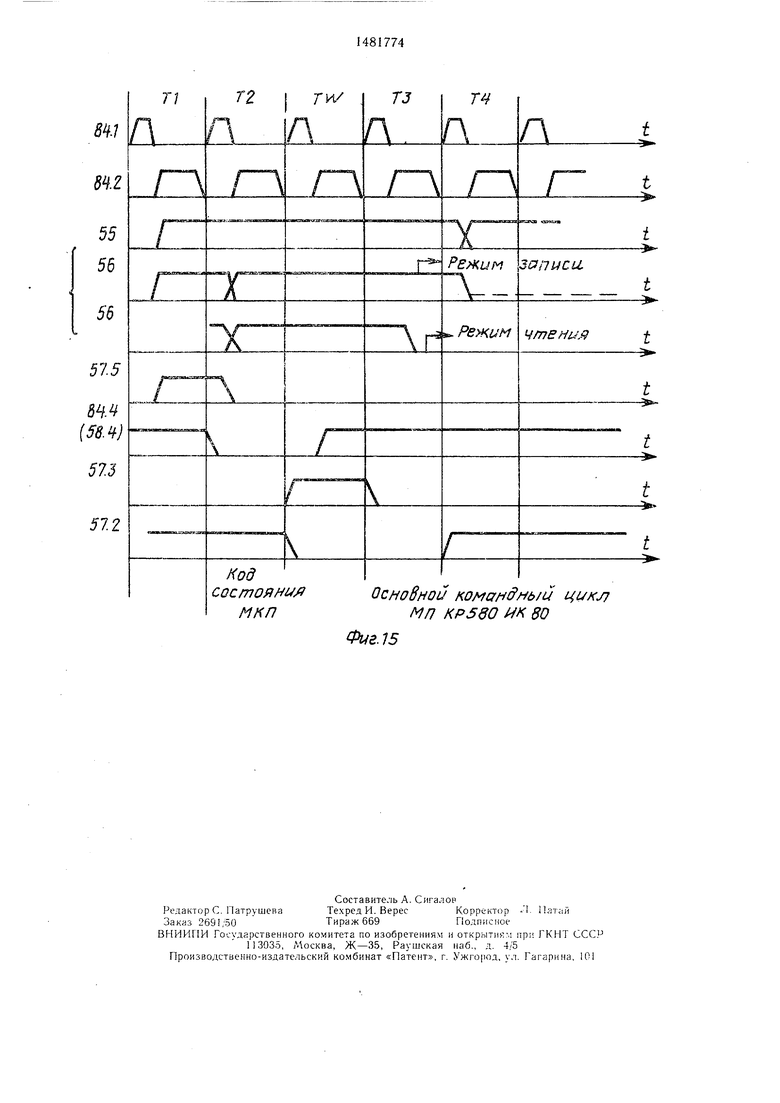

На фиг. 15 приведены временные диаграм- мы работы системы в различных режимах работы.

Для пояснения работы системы ее удобно подразделить на следующие подсистемы: процессорная часть, содержащая блок 1 об- работки, коммутатор 5 сигналов обращения, шинный формирователь 6 адреса, генератор 7, дешифратор 8, блок 10 синхронизации и счетчик 11 времени; память системы, содержащая блок 9 задания перехода и блок 12 памяти; блок 3 отображения.

Поскольку цель изобретения состоит в повышении оперативности отладки за счет специальной организации управления переходами между основной и теневой памятью блока 12, особенности функционирования системы рассмотрим на примере организа- ции управления переходами между блоком теневой 109 и основной 110 памяти блока 12 (фиг. 14)

Блок 1 обработки (фиг. 1) обеспечивгает обмен с памятью в пределах адресного пространства, не превосходящего размер каждого из блоков основной 110 или теневой 109 памяти. Поэтому для расширения объема памяти, используемого для хранения отлаживаемых программ (программ пользователей), физически массив всех программ сие- темы подразделен на два подмассива. Первый нодмассив, содержащий, в основном, программы пользователей, хранится в блоке 110 основной памяти, а второй, содержащий служебные программы, например, комплексы шаговой отладки, тестового конт- роля и другие вспомогательные программы, хранится в блоке 109 теневой памяти.

Поскольку адресное пространство обоих блоков памяти идентично, то обращение микропроцессора к памяти происходит известным образом в соответствии с управляю- щи ми сигналами, которые вырабатываются коммутатором 5 (см. фиг. 6) на выходах 75.1 и 75.2.

0

Для задания соответствующего режима работы блока 1 обработки (фиг. 1) в первом такте каждого машинного цикла генерирует на шине 20 слово состояния, которое по сигналу с входа 37 блока 1 (фиг. 2) записывается в соответствующий регистр блока 74.

Всего для блока обработки (микропроцессора типа К580ИК80) предусмотрено десять типов машинных циклов, задаваемых соответствующим кодом слова состояния в блоке 74.

Управляющие выходы 36 коммутатора 5 подключаются к одноименным разрядам шины 15 управления.

Адресация внешних по отношению к блоку 1 устройств и блоков 9, 3, 10, 4 и 11 осуществляется аналогично адресации ячеек памяти.

Для выбора соответствующего блока блок 1 обработки выставляет на группе 19 выходов адрес обращения, который через формирователь поступает на шину 13 адреса и далее на входы соответствующих блоков.

Ввод-вывод информации в системе может осуществляться через блок 2 ввода данных, блок 4 асинхронной связи и, кроме того, посредством любых соответствующих внешних устройств, подключение которых допускается к шинам 13-15 в соответствии с интерфейсом ИК 1.

При этом с помощью блока 2 ввода (фиг. 3) осуществляется ввод данных с клавиатуры 59. Для реализации ввода из блока 2 используется аппарат прерываний блока 1.

При замыкании нор мально разокнутого контакта 108.i (icl, N) срабатывает элемент ИЛИ-НЕ 106, выходной сигнал которого переводит триггер 104 в единичное состояние.

Сигнал (с активным низким уровнем) с нулевого выхода 24 триггера 104 поступает на вход запроса прерывания RQ микропроцессора 54 (фиг. 2).

После этого микропроцессор 54 известным образом переходит в цикл обработки прерывания, в котором на шине 19 адреса выставляется адрес обращения к блоку 2 (фиг. 1). Код адреса поступает на вход дешифратора 8, который срабатывает по выходу 51.

Сигнал с выхода 51 дешифратора 8 (фиг. 1) поступает на вход элемента ИЛИ 99 и далее с его выхода 25 - на одноименный нулевой вход (R) триггера 104 (фиг. 13), который, возвращаясь в исходное состояние, снимает сигнал запроса прерывания с выхода 24.

Сигнал с элементов 108.i (iel, N) коммутации поступает на вход шифратора 105, на выходе 61 которого формируется соответствующий код, поступающий на группу А входов формирователя 60 блока.2 (фиг. 3).

Формирователь 60 открывается сигналом с входа 25 блока 2 и передает на шину 14

данных с выходов 23 код, сформированный шифратором 105 (фиг. 13), который считывается микропроцессором через коммутатор 5 (фиг. 6).

Ввод-вывод через блок 4 асинхронной связи (фиг. 5) осуществляется следующим образом.

Для обмена системой через блок 4 известным образом может подключаться цифровой или телевизионный дисплей, АЦПУ, графопостроитель или любое другое устройство, осуществляющее обмен данными в последовательном коде.

Если к системе подключается внешнее устройство, работающее только на прием или передачу, то для осуществления обмена достаточно наличие только одного блока 69 в блоке 4 (фиг. 5).

При осуществлении двунаправленного об мена данными необходимо иметь не менее двух блоков 69, один из до жен ря- ботагь в режиме передач;; i: t - .мещапи-ч на передающем конце линии связи, а второй - в режиме приема и размещаться на приемном копне линии связи. При этом подключение обоих блоков 69 производится аналогично. При этом обмен с внешним устройством происходит по одному каналу через вход-выход 16 блока 4, а общение с микропроцессором - в параллельном коде через группу входов-выходов 34 блока 4.

Блок 69 может быть программно установлен в один из пяти режимов работы: асинхронная передача, асинхронный прием, синхронная передача, синхронный прием данных с внутренней синхронизацией, синхронный прием данных с внешней синхронизацией.

В системе блок 69 используется в асинхронном режиме.

Передача данных осуществляется всегда, начиная с младшего разряда. Начальная установка блока 69 осуществляется программно известным образом, с помощью команд начальной установки.

В результате записи управляющих слов блок 69 получает информацию о скорости приема-передачи данных, количестве разрядов в каждом данном, числе разрядов останова, режиме работы (синхронный), наличии или отсутствии разряда четности каждого данного. При синхронном режиме приема данных указывается также тип внешней синхронизации.

Управляющие слова, принимаемые блоком 69 через группу 34 входов-выходов, подразделяются на два типа: управления режимом работы и команды управления.

В любой момент времени блок 1 (фиг. I) может осуществлять считывание слова состояния блока 69.

Для отображения информация в системе используется блок 3 отображения и, кроме того, могут применяться другие блоки ана0

5

0

5

0

5

0

5

0

5

логичного назначения, соответствующие стандарту интерфейса ИК 1.

Обращение блока 1 {фиг. 1) к блоку 62 (фиг. 4) осуществляется как к четырем ячейкам памяти. Для формирования сигнала выборки блока 3 дешифратор 8 (фиг. 1) срабатывает по выходу 28 (фиг. 4).

Комбинации режимов и типов работы блока 62 задаются с помощью управляющих слов, записываемых по адресу регистра управления блока 62.

Рассмотрим работу системы при осуществлении перехода между командами, расположенными в разных блоках памяти: теневой и основной.

Допустим, что в исходном состоянии триггер 88 блока 9, а также триггер 87 и счетчик 86 находятся в нулевом состоянии. Следовательно, сигналом с нулевого выхода 93.2 триггера 88, поступающим па вход i i 1.2 блока 12, подключен блок 110 основной памя- IH, хранящий программы пользователя к ос- .KjiS.iuc программы отладки.

При орк-шизации переходов между командами программы, хранящейся в памяти НО, запись единицы в триггер 87 не производится. При наличии сигналов записи или чтения на входах 94.2 или 94.3, соответственно, адрес обращения к памяти с группы 45 входов блока 9 (фиг. 10) через элемент И 90 поступает на входы 42 блока 110, задавая тем самым ячейку для обращения. Тем самым обеспечивается выбор команды в том же блоке памяти.

Если же необходимо осушесгвить переход из основного блока 110 памяти в теневой 109, то блоком 1 (фиг. 1) на шине 13 адреса на входы дешифратора 8 задается адрес обращения к триггеру 87 (фиг. 10). При этом элемент И 89 открывается по входу 39 выходным сигналом дешифратора 8. Далее по управляющему сигналу с въ хода 753 коммутатора 5 (фиг. 6), поступающему на вход 94.1 элемента 89 И, разрешается запись по С-входу в триггер 87.

Одновременно на шине данных 14 блоком 1 (фиг. 1) по второй команде стандартной последовательности перехода между теневой (основной) и основной (теневой) памятью-записью в порт (триггер 87) переключения памяти выстазляе ся байт данных, нулевой разряд которого, имеющий единичное значение, поступает на вход 43 блока 9 (фиг. 10) и устанавливает триггер 87 в единичное состояние.

После этого блок 1 обработки переходит к выборке третьей команды (JMP) стандартной последовательности перехода, в процессе которой осуществляется несколько (в случае микропроцессора К580ИК.80 или другого аналогичного - три) обращений к памяти. При этом при каждом обращении блоком 1 обработки (фиг. 2) на выходе 57.5 SYN вырабатывается синхросигнал, который через открытый элемент И 91 поступает на счетный вход (+1) счетчика 86.

После выборки команды перехода (JMP), в процессе которой счетчик подсчитывает число обращений к памяти, счетчик 86 пере- ходит в состояние переполнения, когда на его выходе OF появляется единичный сигнал.

По этому сигналу триггер 88 устанавливается в единичное состояние. Сигнал с единичного выхода 93.1 триггера 88 поступает на вход 111.1 блока 12 (фиг. 14), тем самым включая блок 109 теневой памяти.

Поэтому очередное обращение блока 1 обработки происходит уже к блоку 109 теневой памяти.

Переход из программы, находящейся в блоке 109 теневой памяти, к команде, находящейся в блоке 110 основной памяти, осуществляется следующим образом.

Аналогично описанному го второй команде стандартной последовательности перехода осуществляется запись нуля в триггер 89. При чтем обрывается элемент И 92, разрешающий поступление импульсов с входа 38 на вычитающий вход (- 1) счетчика 86.

После выборки третьей команды (к.оман- ды перехода JMP) появляется сигнал на выходе Z счетчика 86, которой устанавливает триггер 88 в нулевое состояние Сигналом с нулевого выхода 93.2 триггера 88 происходит включение блока 110 основной памяти.

Таким образом, осуществляются переходы между любыми заданными точками в теневом (основном) и основном (теневом) блоках памяти.

Формула изобретения

5

5

5 0

0

5

Q 5 0

5

ходное состояние системы соединен с установочным входом тактового генератора, группа выходов, первый, второй и третий выходы которого соединены соответственно с тактовым входом блока обработки, с тактовым входом коммутатора сигналов обращения, с тактовым входом блока отображения и является первым тактовым выходом системы, выход синхронизации группы управляющих выходов блока обработки соединен с входом синхронизации тактового генератора, выход, шинного формирователя адреса соединен с входом коммутатора сигналов обращения, первый выход которого соединен с тактовым входом блока отображения, второй выход коммутатора сигнала обращения является первым тактовым выходом системы, выход признака чтения группы управляющих выходов коммутатора сигналов обращения соединен с входом чтения блока памяти, отличающаяся тем, что, с целью повышения быстродействия при отладке, в систему введены блок задания перехода, блок запуска и счетчик времени, причем выход признака перехода и адресный выход блока задания перехода соединены соответственно с входом признака перехода и адресным входом блока памяти, выход синхронизации группы управляющих выходов блока обработки соединен с первым тактовым входом блока задания перехода, второй и третий выходы тактового генератора соединены соответственно с входом начальной установки блока задания перехода и с входом синхронизации счетчика времени, нулевой разряд информационного входа системы соединен с информационным входом блока задания перехода, выход шинного формирователя адреса соединен с адресным входом блока задания перехода, выходы приема и записи группы выходов коммутатора сигналов обращения соединены с одноименными входами блока задания перехода, третий, четвертый и пятый выходы коммутатора сигналов обращения соединены соответственно с вторым тактовым входом блока задания перехода, с тактовым входом счетчик времени и с тактовым входом блока запуска, первый и второй выходы которых соединены соответственно с входом готовности тактового генератора и с выходом запроса системы, выходы чтения, записи и выдачи группы выходов коммутатора сигналов обращения соединены с одноименными входами блока запуска, вход разрешения асинхронным обменом системы соединен с входом пуска блока запуска, выход ожидания группы управляющих выходов блока обработки и выход шинного формирователя адреса соединены соответственно с входом ожидания и группой адресных входов блока запуска, информационный вход-выход счетчика времени через магистраль соединен с шиной данных систем, выход шинного формирователя адресов соединен с адресным

входом счетчика времени, выходы приема и выдачи группы выходов коммутатора сигналов обращения соединены с одноименными входами счетчика времени, выход переполнения которого является выходом разрешения системы.

0

ственно с единичным и нулевым входами второго триггера, прямой и инверсный выходы которого являются прямым и инверсным выходами признака перехода блока, второй тактовый вход блока соединен с первыми входами второго и третьего элементов И, информационный и адресный входы блока соединены соответственно с информационным входом первого триггера и вторым входом второго элемента И, выход которого является адресным выходом блока, прямой и инверсный выходы первого триггера соединены с вторыми входами третьего и четвертого элементов и соответственно, выходы которых соединены соответственно с ин- крементным и декрементным входами счетчика, прямой и инверсный выходы второго триггера соединены с инверсными входами третьего и четвертого элементов И соответственно

Фиг.З

Фиг А

Фие.5

Фиг. 7

L

Фие.б

Фиг. 8

Фие.9

Фие.11

Фие.Ю

Фиг. 72

Фие. 13

Фие П

вы ш

55 56

56

W.4 ()

Фиг.15

| Устройство для отладки программ | 1984 |

|

SU1213482A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Макглин Д | |||

| Р | |||

| Микропроцессоры | |||

| Технология, архитектура и применение | |||

| М.: Энергия, 1979, с | |||

| Вага для выталкивания костылей из шпал | 1920 |

|

SU161A1 |

Авторы

Даты

1989-05-23—Публикация

1987-04-09—Подача