УРОВЕНЬ ТЕХНИКИ

Настоящее изобретение относится, в общем, к области техники процессоров, а в частности к увеличению фактического размера блока стековых регистров с помощью теневых регистров.

RISC-процессоры характеризуются относительно небольшим набором команд, причем каждая команда выполняет одну команду, такую как арифметическая, логическая операция или операция загрузки/сохранения. Арифметические и логические команды получают свои операнды из и записывают результаты в один или более регистров общего назначения (GPR). GPR - это архитектурные регистры. Т.е. они содержат дискретные ячейки памяти, явно указанные в архитектуре набора команд, и напрямую адресуются посредством команд.

GPR зачастую реализуются в аппаратных средствах как массив высокоскоростных многопортовых регистров, каждый из которых имеет ширину слова, заданную посредством набора команд (к примеру, 32 или 64 бита). Этот массив физических регистров упоминается как блок физических регистров. В реализации регистров с прямым отображением число регистров в блоке физических регистров точно совпадает с числом архитектурных GPR, и каждый логический идентификатор GPR назначается конкретному аппаратному регистру. Для более высокой производительности, а также для того, чтобы поддерживать суперскалярные конвейеры, многие современные процессоры разделяют логические идентификаторы GPR из физических регистров в блоке физических регистров. Переименование регистров, буферы восстановления последовательности и т.п. - это методики, известные в данной области техники, для отделения логических идентификаторов GPR от физических регистров. Будь то напрямую назначенные или переименованные, управление блоком физических регистров во множестве программных процедур является сложной задачей разработки и зачастую "узким местом" по производительности.

Большая часть современного программного обеспечения является модульной по природе. Т.е. одна процедура может "вызывать" или передавать управление в другую процедуру (по-другому упоминаемую как функция, подпрограмма, подмодуль и т.п.). Вызываемая процедура может, в свою очередь, вызывать другую процедуру и т.д., что приводит к вложенности процедур, часто до значительной глубины. В ходе приведения в исполнение посредством процессора, каждой процедуре (также упоминаемой в ходе приведения в исполнение как контекст) выделяются определенные ресурсы процессора, в том числе определенное число GPR. Число GPR, выделяемых процедуре, может быть предварительно определено посредством анализа компилятором команд в процедуре и может варьироваться от нескольких GPR до полного архитектурного набора GPR. Когда первая процедура вызывает вторую процедуру (также называемую контекстным переключателем), первая, или вызывающая, процедура становится неактивной, тогда как второй, или вызываемой процедуре, выделяются отдельные ресурсы, в том числе собственный набор GPR, и начинается ее приведение в исполнение. Когда вторая процедура завершает приведение в исполнение, ее ресурсы освобождаются, ресурсы повторно выделяются вызывающей процедуре (при необходимости), и вызывающая процедура возобновляет приведение в исполнение. Часть ресурсов, выделенных вызывающей процедуре, необязательно может оставаться доступной для вызываемой процедуры, например, регистры, используемые для того, чтобы передавать параметры вызова и возвращаемые значения между процедурами.

В некоторых процессорах предшествующего уровня техники, например, Intel i-960, контекстный переключатель, или новая процедура, предлагает процессору сохранить все содержимое блока физических регистров в памяти, делая весь блок физических регистров доступным для новой процедуры. Когда вызываемая процедура завершает приведение в исполнение и возвращает управление своей вызывающей процедуре, ранее сохраненные значения регистров повторно сохраняются в блоке физических регистров, и приведение в исполнение вызывающей процедуры продолжается. Содержимое блока физических регистров сохраняется в "поддерживающем запоминающем устройстве", таком как системное запоминающее устройство (RAM). Чтобы уменьшить влияние на производительность нескольких обращений к памяти вне микросхемы для каждого контекстного переключателя, когда поддерживающее устройство содержит RAM вне микросхемы, процессор может предоставлять один или более блоков кэш-регистров, которые могут содержать фактические регистры или альтернативно могут содержать внутреннюю кэш-память, для сохранения содержимого блока физических регистров. Тем не менее, весь блок физических регистров должен быть сохранен/извлечен за один раз, нанося удар по производительности, даже в случае хранилища кэшированных регистров.

Методика, используемая многими современными процессорами, такими как Intel Itanium, которая устраняет необходимость сохранять и извлекать блок физических регистров сразу, известна как архитектура блока стековых регистров. В архитектуре блока стековых регистров высокоуровневый контроллер процесса рассматривает блок физических регистров как логический стек бесконечной глубины. Этот логически бесконечный стек реализован в блоке физических регистров посредством пошагового выделения регистров процедурам по мере того, как они вызываются, и сохранения содержимого ранее выделенных регистров при необходимости.

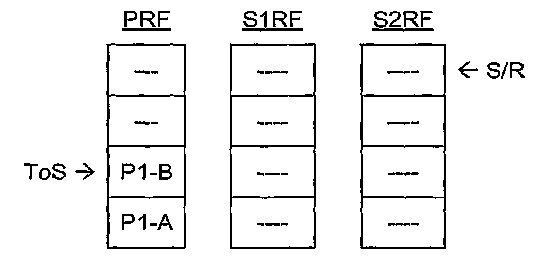

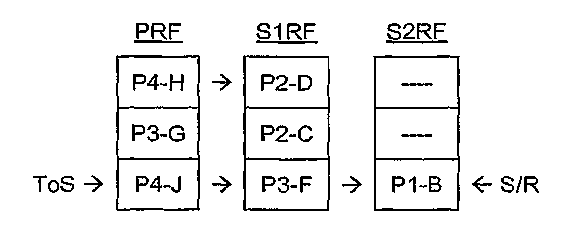

Фиг.1 иллюстрирует функциональную блок-схему характерной реализации архитектуры блока стековых регистров. Блок 1 физических регистров содержит массив высокоскоростных многопортовых физических регистров, при этом массив включает в себя, по меньшей мере, столько регистров, сколько GPR в архитектуре набора команд. Например, блок 1 физических регистров может содержать 128 регистров, начиная от физического регистра 0 (PR0) внизу до физического регистра 127 (PR127) наверху. Логические указатели реализуют управление стеком: указатель вершины стека и указатель сохранения/восстановления.

Первоначально оба указателя задаются равными PR0. По мере того как процедуры вызываются и регистры выделяются им, указатель вершины стека перемещается вверх. Когда все или практически все доступные физические регистры выделены, и новая вызываемая процедура требует больше регистров, чем число невыделенных регистров, оставшихся в блоке 1 физических регистров, указатель вершины стека "оборачивается" и начинает выделение регистров снизу блока 1 физических регистров, начиная с PR0. Тем не менее, прежде чем это осуществляется, доступное число регистров снизу блока 1 физических регистров должно иметь свое содержимое сохраненным в поддерживающем запоминающем устройстве 3, например системной памяти (RAM).

Механизм 2 сохранения регистров прерывает процессор и приводит в исполнение команды, требуемые для того, чтобы выполнять операции считывания регистров и сохранения в памяти, чтобы сохранять содержимое самых последних выделенных регистров внизу блока 1 физических регистров в поддерживающее запоминающее устройство 3. Механизм 2 сохранения регистров увеличивает указатель сохранения/восстановления, указывающий то, что регистры ниже указателя доступны для выделения новым вызываемым процедурам. Когда механизм 2 сохранения регистров завершает операцию сохранения регистров и отказывается от управления процессором, контроллер процессора выделяет регистры следующей процедуре и увеличивает указатель вершины стека, заворачивая его и увеличивая его мимо регистров, содержимое которых сохранено в поддерживающее запоминающее устройство 3, поскольку эти регистры повторно выделяются и используются посредством вызываемой процедуры.

Аналогично, по мере того как вызываемая процедура завершает приведение в исполнение и возвращает управления вызывающей процедуре, стек выталкивается, и регистры, выделенные вызываемой процедуре, освобождаются или делаются доступными для выделения другим процедурам. Если все данные, ассоциативно связанные с вызывающей процедурой, еще не находятся в блоке 1 физических регистров, т.е. если один или более регистров вызывающей процедуры повторно выделен, механизм 2 сохранения регистров повторно прерывает процессор, извлекает содержимое самых последних сохраненных регистров из поддерживающего запоминающего устройства 3, восстанавливает данные в блок 1 физических регистров, выделяет регистры вызывающей процедуре и увеличивает индикатор сохранения/восстановления, чтобы указать то, что регистры выделены и содержат допустимые данные.

Система блоков стековых регистров предоставляет оптимальную производительность при объемном блоке 1 физических регистров, при относительно небольшой глубине вложенности процедур и/или при относительно небольшом числе регистров, выделенных каждой процедуре. При этих условиях указатель вершины стека просто перемещается вверх и вниз посредством блока 1 физических регистров, выделяя и освобождая регистры для процедур при необходимости, без задержки. Тем не менее, по мере того как глубина вложенности процедур возрастает и/или одна или более процедур требуют большого числа регистров, процессор испытывает многочисленные прерывания от механизма 2 сохранения регистров для того, чтобы сохранять данные и восстанавливать их в регистры в блоке 1 физических регистров, поскольку физические регистры освобождаются и повторно выделяются вызывающим процедурам.

Один способ того, чтобы повысить производительность системы блоков стековых регистров, состоит в том, чтобы просто увеличить размер блока 1 физических регистров. Хотя это предоставляет более высокую производительность, регистры в блоке 1 физических регистров обычно являются высокоскоростными многопортовыми регистрами с произвольным доступом. Каждый регистр может включать в себя, к примеру, три-пять портов чтения и записи. Более того, для гибкости в распределении операций и выделении регистров, порт считывания каждого физического регистра должен направляться в каждую ступень канала приведения в исполнение из каждого конвейера, и ступень канала обратной записи должна быть соединена с портом записи каждого регистра в блоке физических регистров. Таким образом, увеличение размера блока 1 физических регистров является затратным в отношении счетчика вентилей и сложности сети соединений, при сопутствующем возрастании сложности тестирования и проверки и потребления энергии. В любое данное время только одна процедура приводится в исполнение, обычно осуществляя доступ только к небольшому поднабору регистров в блоке 1 физических регистров. Таким образом, увеличение размера блока 1 физических регистров приводит к существенным затратам при низкой эффективности использования дорогого оборудования.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В одном или более вариантов осуществления один или более блоков теневых регистров помещаются между блоком физических регистров, содержащим множество многопортовых регистров и поддерживающим запоминающим устройством в архитектуре блоков стековых регистров. Блоки теневых регистров содержат двухпортовые регистры и соединены последовательно, формируя цепочку, идущую от каждого многопортового регистра в блоке физических регистров. Данные в многопортовых регистрах, выделенных неактивным процедурам, сохраняются в соответствующих двухпортовых регистрах в первом блоке теневых регистров. Данные затем могут быть сдвинуты во второй двухпортовый регистр во втором блоке теневых регистров, поскольку более новые данные, ассоциативно связанные с другой неактивной процедурой, сохраняются из многопортового регистра в двухпортовый регистр в первом блоке теневых регистров. Цепочка блоков теневых регистров может иметь произвольную глубину. Механизм сохранения регистров при необходимости сохраняет и восстанавливает данные из поддерживающего запоминающего устройства (такого как RAM вне микросхемы) для последнего блока теневых регистров в цепочке. По мере того, как процедуры повторно активируются, данные сдвигаются посредством цепочки блоков теневых регистров в направлении многопортовых регистров блока физических регистров.

Один вариант осуществления относится к способу управления системой блоков теневых регистров, имеющей один или более блоков теневых регистров. Один или более многопортовых регистров из блока многопортовых регистров выделяются первой процедуре, и данные, ассоциативно связанные с первой процедурой, сохраняются в выделенных многопортовых регистрах. Данные, ассоциативно связанные с первой процедурой, выборочно сохраняются из одного или более многопортовых регистров в один или более первых двухпортовых регистров, и соответствующие выделенные многопортовые регистры освобождаются для выделения второй процедуре. До продолжения приведения в исполнение первой процедуры данные, ассоциативно связанные с первой процедурой, восстанавливаются из двухпортовых регистров в многопортовые регистры, и регистры повторно выделяются первой процедуре.

Другой вариант осуществления относится к процессору, реализующему архитектуру набора команд, задающую множество регистров общего назначения. Процессор включает в себя блок физических регистров, содержащий, по меньшей мере, столько многопортовых регистров, сколько регистров общего назначения, заданных в архитектуре набора команд процессора, при этом регистры динамически выделяются программным процедурам. Процессор также включает в себя механизм сохранения регистров, выполненный с возможностью выборочно сохранять данные из многопортовых регистров, выделяемых неактивным процедурам, и восстанавливать данные в многопортовые регистры до того, как процедуры становятся активными. Процессор дополнительно включает в себя первый блок теневых регистров, содержащий такое же число двухпортовых регистров, что и число многопортовых регистров в блоке физических регистров. Первый порт каждого двухпортового регистра непосредственно соединен с соответствующим многопортовым регистром и выполнен с возможностью хранить данные, сохраненные из многопортовых регистров, выделенных неактивным процедурам, под управлением механизма сохранения регистров.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - это блок-схема блока стековых регистров предшествующего уровня техники.

Фиг.2 - это функциональная блок-схема процессора.

Фиг.3 - это функциональная блок-схема блока стековых регистров, включающего в себя множество блоков теневых регистров.

Фиг.4 - это блок-схема последовательности операций способа управления архитектурой блока стековых регистров.

Фиг.5 - блок-схема последовательности операций варианта осуществления изобретения.

ПОДРОБНОЕ ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг.2 иллюстрирует функциональную блок-схему процессора 10. Процессор 10 приводит в исполнение команды в конвейере 12 приведения в исполнение команд согласно управляющей логике 14. Конвейер 12 может иметь суперскалярную архитектуру с несколькими параллельными конвейерами, такими как 12a и 12b. Каждый конвейер 12a, 12b включает в себя различные регистры или защелки 16, организованные в ступенях канала, и один или более арифметико-логических устройств (ALU) 18. Конвейеры 12a, 12b извлекают команды из кэша команд (I-кэша или I$) 20, причем адресация памяти и разрешения управляются посредством командного буфера быстрого преобразования адреса (ITLB) 22.

Доступ к данным осуществляется из кэша данных (D-кэша или D$) 24, причем адресация памяти и разрешения управляются посредством буфера быстрого преобразования адреса (TLB) 26. В различных вариантах осуществления ITLB 22 может содержать копию части TLB 26. Альтернативно, ITLB 22 и TLB 26 могут быть интегрированы. Аналогично, в различных вариантах осуществления процессора 10 I-кэш 20 и D-кэш 24 могут быть интегрированы или объединены. Промахи в I-кэше 20 и/или D-кэше 24 вызывают доступ в основную (вне микросхемы) память 36 под управлением интерфейса 34 памяти.

Регистры или защелки 16 ступеней канала и ALU 18 могут считывать операнды и/или записывать результаты в регистры в блоке 28 физических регистров. Блок 28 физических регистров управляется посредством механизма 30 сохранения регистров, который также управляет одним или более блоков 32 теневых регистров. Данные передаются между одним блоком 32 теневых регистров и основной памятью 36 посредством интерфейса 34 памяти. Работа блока 28 физических регистров, механизма 30 сохранения регистров и блоков 32 теневых регистров подробнее описана ниже.

Процессор 10 может включать в себя интерфейс 38 ввода/вывода (I/O), управляющий доступом к различным периферийным устройствам 40, 42. Специалисты в данной области техники должны признавать, что возможно множество вариантов процессора 10. Например, процессор 10 может включать в себя кэш второго уровня (L2) для I- и D-кэшей. Помимо этого, один или более функциональных блоков, проиллюстрированных в процессоре 10, могут быть опущены из конкретного варианта осуществления.

Фиг.3 иллюстрирует функциональную блок-схему архитектуры блоков стековых регистров процессора 10. Логически бесконечный стек регистров реализован в блоке 28 физических регистров, который включает в себя, по меньшей мере, столько многопортовых физических регистров, сколько GPR задает архитектура набора команд процессора; один или более блоков 32 теневых регистров, каждый из которых содержит такое же число двухпортовых регистров, сколько блок 28 физических регистров содержит многопортовых регистров; и поддерживающее запоминающее устройство 36 очень большого размера. При использовании в данном документе многопортовый регистр - это ячейка хранения, имеющая три или более независимых порта чтения/записи данных. Двухпортовый регистр - это ячейка хранения, имеющая два независимых порта чтения/записи данных. Регистры в блоке 28 физических регистров являются многопортовыми, поскольку данные записываются и считываются из регистров посредством нескольких ступеней конвейера, ALU и т.п. Фактически, именно сложность, кремниевая зона и сложность сети соединений большого числа многопортовых регистров с произвольным доступом делает простое расширение блока 28 физических регистров затратным подходом к снижению задержек, связанных с сохранением их содержимого в поддерживающее запоминающее устройство 36.

Каждый многопортовый регистр в блоке 28 физических регистров напрямую соединен с первым портом соответствующего двухпортового регистра в блоке 32-1 теневых 1 регистров. Как показано на фиг.3, второй порт каждого двухпортового регистра в блоке 32-1 теневых 1 регистров напрямую соединен с первым портом соответствующего двухпортового регистра в блоке 32-2 теневых 2 регистров. Ко второму порту двухпортовых регистров в блоке 32-2 теневых 2 регистров осуществляется доступ посредством механизма 30 сохранения регистров. Хотя фиг.3 иллюстрирует блоки 32-1, 32-2 теневых регистров, специалисты в данной области техники должны легко признавать, что число последовательно соединенных блоков 32-1, 32-2 теневых регистров может варьироваться от одного до любого требуемого числа. Набор регистров, включающий в себя блок 28 физических регистров и все последовательно соединенные блоки 32 теневых регистров, упоминается в данном документе как система блоков теневых регистров.

Указатель вершины стека и указатель сохранения/восстановления управляют доступностью многопортовых регистров в блоке 28 физических регистров, а также, в некоторых вариантах осуществления, сохранением данных и восстановлением данных из последнего блока 32-2 теневых регистров. Оба указателя поддерживаются посредством механизма 30 сохранения регистров. В одном варианте осуществления оба указателя инициализируются на вершине блоков регистров. Поскольку многопортовые регистры в блоке 28 физических регистров выделяются новым вызываемым процедурам, указатель вершины стека увеличивается на число выделенных многопортовых регистров. Регистры в или ниже указателя вершины стека (и выше позиции указателя сохранения/восстановления) выделяются процедурам и могут содержать программные данные, а регистры выше указателя вершины стека (и в или ниже позиции указателя сохранения/восстановления) свободны для выделения новым процедурам. Эта взаимосвязь сохраняется даже после того, как указатели "оборачиваются" вокруг блоков регистров. Когда регистры вершины стека и сохранения/восстановления указывают на одну позицию с блоками регистров, блок 28 физических регистров полон.

По мере того, как процедура завершает, приведение в исполнение и возвращает управление в вызывающую процедуру, указатель вершины стека уменьшается на число регистров, которые выделены выполненной процедуре. Регистры ниже указателя вершины стека (и над позицией указателя сохранения/восстановления) содержат данные, ассоциативно связанные с текущей активной процедурой, и, возможно, данные, ассоциативно связанные с одной или более процедур, которые являются неактивными, вызывающих другие процедуры, но повторно активируются, когда вызываемая процедура завершает приведение в исполнение.

Когда процедура вызвана и запрашивает выделение большего числа многопортовых регистров, чем число невыделенных многопортовых регистров, оставшихся в блоке 28 физических регистров, механизм 30 сохранения регистров сохраняет данные, ассоциативно связанные с неактивными процедурами, т.е. данные, сохраненные в многопортовых регистрах, которые выделены неактивным процедурам (возможно, включающим в себя вызывающую процедуру), и блока 28 физических регистров в соответствующие двухпортовые регистры в блоке 32-1 теневых 1 регистров. Эта операция упоминается в данном документе как "вытеснение" данных. Поскольку каждый многопортовый регистр в блоке 28 физических регистров непосредственно соединен с соответствующим двухпортовым регистром в блоке 32-1 теневых 1 регистров, данные, ассоциативно связанные со всеми неактивными процедурами, могут быть сохранены из блока 28 физических регистров в блок 32-1 теневых 1 регистров за один цикл согласно одному варианту осуществления.

Тем не менее, считывание большого числа многопортовых регистров и запись того же большого числа двухпортовых регистров в одном цикле может приводить к нежелательному "выбросу" мощности. Как следствие, в другом варианте осуществления может быть использован более поэтапный подход к сохранению многопортовых регистров. Например, каждый раз, когда предварительно определенное число многопортовых регистров, сохраняющих данные, становится неактивным (т.е. их ассоциативно связанная процедура(ы) становится неактивной посредством вызывания другой процедуры), данные могут передаваться в двухпортовые регистры. Предварительно определенное число регистров, которые должны быть сохранены одновременно, т.е. "уровень модульности" операций сохранения данных многопортовых регистров, может быть приспособлено так, как требуется для конкретных реализаций, и/или может быть переменным, например, посредством записи значения в конфигурационный регистр.

По мере того, как вызываемые процедуры завершают приведение в исполнение и их вызывающая процедура повторно активируется, указатель вершины стека перемещается вниз, освобождая многопортовые регистры, ассоциативно связанные с завершенной вызываемой процедурой. По мере того, как указатель вершины стека достигает позиции указателя сохранения/восстановления, данные восстанавливаются до ранее освобожденных многопортовых регистров в блоке 28 физических регистров из блока 32-1 теневых 1 регистров. Эта операция упоминается в данном документе как "наполнение" данных. Кроме того, прямое соединение между каждым многопортовым или двухпортовыми регистрами дает возможность восстановления множества многопортовых регистров в одном цикле. Число регистров, восстанавливаемых за один раз, может быть предварительно определенным значением, а в некоторых вариантах осуществления может быть переменным. Когда данные восстановлены, указатель сохранения/восстановления перемещается вниз соответствующим образом.

Как показано на фиг.3, система блоков теневых регистров может включать в себя более одного блока 32-1, 32-2 теневых регистров. Поскольку данные вытесняются из блока 28 физических регистров в блок 32-1 теневых 1 регистров, соответствующие регистры в блоке 32-1 теневых 1 регистров могут содержать сохраненные данные. В этом случае каждый раз, когда данные вытесняются из многопортового регистра в блоке 28 физических регистров в двухпортовый регистр блока 32-1 теневых 1 регистров, сохраненные данные в двухпортовом регистре сдвигаются в соответствующий двухпортовый регистр блока 32-2 теневых 2 регистров. Поскольку многопортовые регистры, теневые 1 двухпортовые регистры и теневые 2 двухпортовые регистры непосредственно соединены с выделенными портами чтения/записи, множество операций вытеснения регистров может выполняться в одном цикле.

Когда данные наполняются или восстанавливаются в один или более многопортовых регистров блока 28 физических регистров из соответствующих двухпортовых регистров блока 32-1 теневых 1 регистров, если сохраненные данные размещаются в соответствующих двухпортовых регистрах блока 32-2 теневых 2 регистров, они восстанавливаются в теневые 1 двухпортовые регистры как часть операции наполнения. Специалисты в данной области техники должны легко признавать, что блоки 32 теневых регистров могут быть вложены до любой требуемой или желательной глубины в данной реализации, к примеру, от 1 до n, где n - это любое положительное целое число.

Механизм 30 сохранения регистров вытесняет или сохраняет данные из n-го существующего блока теневых регистров (к примеру, блока 32-2 теневых 2 регистров в системе блоков теневых регистров, показанной на фиг.3) в поддерживающее запоминающее устройство 36, такое как RAM вне микросхемы. В отличие от промежуточных блоков теневых регистров, порты чтения/записи в расчете на регистр которых непосредственно соединены с другими регистрами, механизм 30 сохранения регистров имеет произвольный доступ на чтение/запись ко второму порту регистров в n-ном блоке теневых регистров. В одном варианте осуществления механизм 30 сохранения регистров сохраняет данные из регистров в n-м блоке 32-n теневых регистров по мере того, как они вытесняются из системы блоков теневых регистров, т.е. данные "выталкиваются" из регистра посредством данных в (n-1)-м блоке теневых регистров по мере того, как данные вытесняются из одного или более многопортовых регистров в блоке 28 физических регистров.

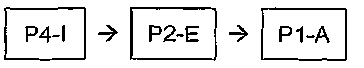

Базовая операция системы блоков теневых регистров показана в примере ниже. Рассмотрим систему блоков теневых регистров по фиг.3, но для краткости каждый блок регистров содержит только четыре регистра. Первоначально первая процедура (P1) запрашивает и ей выделяется два многопортовых регистра в блоке физических регистров (PRF) 28. Указатель вершины стека (инициализированный наверху PRF 28) увеличивается дважды и помещается наверху зоны "допустимых данных" PRF 28, которая является зоной PRF 28 в или ниже указателя вершины стека и выше указателя сохранения/восстановления. Поскольку данные не вытеснены из PRF 28, указатель сохранения/восстановления не изменяет свою первоначальную позицию наверху блоков регистров. P1 записывает данные A и B в два выделенных многопортовых регистра.

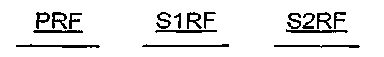

Процедура P1 вызывает вторую процедуру (P2), которая запрашивает три многопортовых физических регистра. Прежде чем три многопортовых регистра могут быть выделены P2, по меньшей мере, часть данных, ассоциативно связанных с неактивной в данный момент процедурой P1, должна быть вытолкнута из двухпортовых регистров блока теневых 1 регистров (S1RF) 32-1. Указатель сохранения/восстановления увеличивается, чтобы указать операцию сохранения (вытеснения) из PRF 28. P2 далее сохраняет данные C-E, и указатель вершины стека оборачивается. Поскольку нет регистров выше указателя вершины стека, но ниже указателя сохранения/восстановления, нет свободного пространства в PRF.

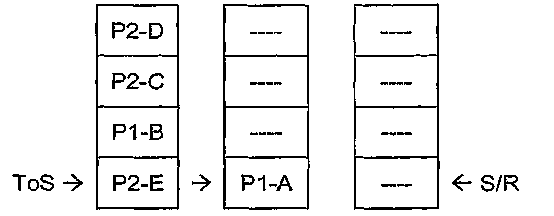

Процедура P2 вызывает третью процедуру (P3), которая запрашивает два физических регистра. Данные вытесняются из двух многопортовых регистров PRF 28 в S1RF 32-1, и регистр сохранения/восстановления увеличивается дважды. P3 выделяется два многопортовых регистра, указатель вершины стека увеличивается дважды, и P3 сохраняет данные F и G.

Процедура P3 вызывает четвертую процедуру (P4), которая запрашивает три физических регистра. Данные вытесняются из двух многопортовых регистров PRF 28 в три соответствующих двухпортовых регистра S1RF 32-1. Это инструктирует данным из одного двухпортового регистра S1RF 32-1 вытесняться в соответствующий двухпортовый регистр блока теневых 2 регистров (S2RF) 32-2. Указатель сохранения/восстановления увеличивается три раза (и оборачивается).

P4 сохраняет данные H-J, и указатель вершины стека увеличивается в три раза (и оборачивается).

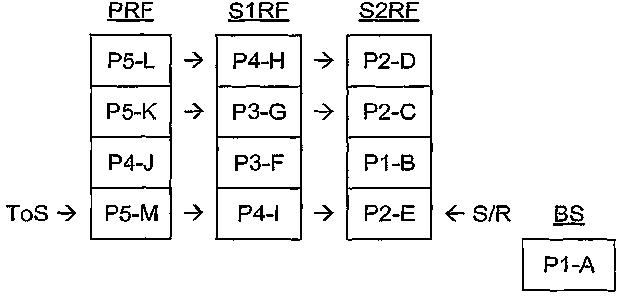

Процедура P4 вызывает пятую процедуру (P5), которая запрашивает три физических регистра. Поскольку запрошено больше многопортовых регистров, чем свободных регистров в S2RF 32-2, механизм 30 сохранения регистров должен вытеснить данные, по меньшей мере, что из одного двухпортового регистра S2RF 32-2 в поддерживающее запоминающее устройство 36. После этой операции сохранения данные вытесняются из трех регистров PRF 28 со следующими результатами.

Шестая процедура (P6) запрашивает два регистра, вызывая больше вытеснений из блока стековых регистров в поддерживающее запоминающее устройство 36.

В показанном варианте осуществления данные, вытесненные из S2RF 32-2 в BS 36, сохраняются в логическом стеке или структуре данных LIFO. Тем не менее, настоящее изобретение не ограничено такой структурой. В общем, механизм 30 сохранения регистров может сохранять вытесненные данные в BS 36 в любой форме или структуре, до тех пор, пока он отслеживает данные, и может наполнять систему блоков теневых регистров сохраненными данными в обратном порядке тому, в котором они вытеснены.

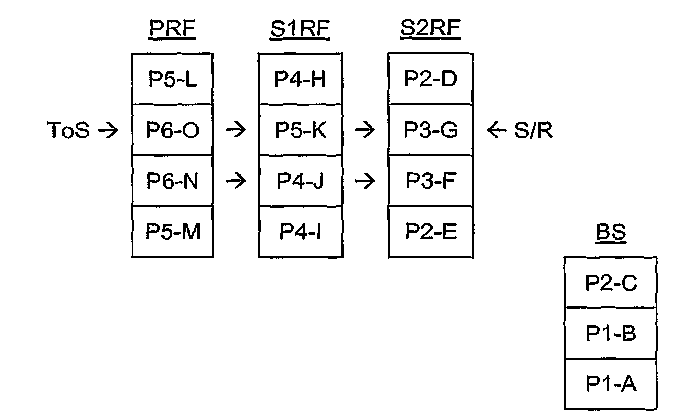

После этого процедура P6 завершает приведение в исполнение и возвращает управление вызывающей процедуре P5. Многопортовые регистры PRF 28, содержащие данные O и N, ассоциативно связанные с P6, освобождаются посредством уменьшения указателя вершины стека два раза. Это инструктирует данным, сохраненным в соответствующих позициях S1RF 32-1 и S2RF 32-2, наполняться. Это, в свою очередь, инструктирует механизму 30 сохранения регистров заполнять соответствующие позиции S2RF 32-2 данными от BS 36, начиная с позиции указателя сохранения/восстановления и уменьшая для каждого наполненного регистра. После данной операции наполнения регистров указатель вершины стека и указатель сохранения/восстановления снова адресует один объект в системе блоков теневых регистров, указывая то, что PRF 28 заполнен.

По мере того, как процедуры завершаются и возвращают управление в вызывающие процедуры, многопортовые регистры в PRF 28 освобождаются, и данные наполняются из S1RF 32-1 в PRF 28, из S2RF 32-2 в S1RF 32-1 и из BS 36 в S2RF 32-2. После возврата каждой вызываемой процедуры состояние системы блоков теневых регистров будет в обратном порядке тому, что показан выше (к примеру, таблицы 4, 3, 2 и 1).

Для эффективной работы механизм 30 сохранения регистров отслеживает содержимое системы блоков теневых регистров. Например, в операциях вытеснения, показанных в таблицах 2, 3 и 4, механизм 30 сохранения регистров не должен вытеснять данные из n-го блока 32 теневых регистров в поддерживающее запоминающее устройство 36. Тем не менее, в операциях вытеснения, показанных в таблицах 5 и 6, он должен. В одном варианте осуществления механизм 30 сохранения регистров поддерживает глобальный указатель дна стека посредством подсчета числа вытеснений данных из блока 28 физических регистров и уменьшения на наполнения данных. Посредством деления этого показателя по модулю на размер блока регистров механизм 30 сохранения регистров может легко обнаружить "конец" цепочки данных, вытесняемой из блока 28 физических регистров.

В другом варианте осуществления механизм 30 сохранения регистров может определять требуемые операции из числа выделяемых регистров, позиции указателя сохранения/восстановления, а также того, заполнен или нет предшествующий блок регистров в цепочке. В этом варианте осуществления бит состояния FULL ассоциативно связывается с каждым блоком регистров (к примеру, PRF 28, S1RF 32-1, S2RF 32-2, ..., SnRF 32-n). Бит задается каждый раз, когда соответствующий блок регистров полный, и сбрасывается, когда блок регистров имеет свободные регистры, доступные для того, чтобы сохранять новые данные. Например, в таблице 2 блок 32-1 теневых 1 регистров неполный. Таким образом, механизм 30 сохранения регистров знает, что вытеснение в поддерживающее запоминающее устройство 36 не требуется для следующего выделения регистров, поскольку процедуре не может быть выделено больше, чем количество регистров в блоке 28 физических регистров.

В варианте осуществления вышеприведенного примера данные вытесняются из блока 28 физических регистров только при необходимости. Т.е., когда вызываемая процедура запрашивает три регистра и блок 28 физических регистров полный, только три регистра вытесняются в блок 32-1 теневых 1 регистров (и дополнительно посредством системы блоков теневых регистров при необходимости). Когда система блоков теневых регистров полная (т.е. блок 28 физических регистров и блоки 32 теневых регистров полные), выталкивание в поддерживающее запоминающее устройство 36 требуется для каждого нового выделения регистров. Это накладывает задержку, ассоциативно связанную с доступом к RAM вне микросхемы для каждого вызова и возврата процедуры, когда внутренняя система блоков стековых регистров полная. Хотя этот способ системы управления системой блоков теневых регистров является полнофункциональным и предоставляет корректные результаты, он может быть субоптимальным.

В другом варианте осуществления каждый раз, когда недостаточное количество невыделенных многопортовых регистров имеется в блоке 28 физических регистров, чтобы удовлетворять процедуре выделения регистров вызываемой процедуры, все данные, ассоциативно связанные с неактивными процедурами, могут быть вытеснены совместно в блок 32-1 теневых 1 регистров (и далее, как требуется, вниз по цепочке блоков 32 теневых регистров). Если n-ный блок теневых регистров содержит допустимые данные, механизм 30 сохранения регистров, возможно, должен вытеснить данные в поддерживающее запоминающее устройство 36, накладывая задержку на обращение к памяти по вызову процедуры. Тем не менее, значительное пустое пространство должно оставаться в блоке 28 физических регистров, и впоследствии вызываемым процедурам сразу могут выделяться многопортовые регистры.

В другом варианте осуществления, в котором совместное вытеснение может приводить к нежелательному выбросу мощности, данные могут вытесняться из блока 28 физических регистров каждый раз, когда предварительно определенное число многопортовых регистров в блоке 28 физических регистров содержит данные, ассоциативно связанные с неактивными процедурами. Это предварительно определенное число может быть фиксированным или может задаваться пользователем, к примеру, посредством записи значения в конфигурационный регистр. В этом варианте осуществления, хотя выделение многопортовых регистров в блоке 28 физических регистров новой вызываемой процедуре и сопутствующая деактивация вызывающей процедуры является триггером, который инициирует операцию вытеснения (посредством инструктирования предварительно определенному числу регистров, ассоциативно связанных с неактивными процедурами, быть удовлетворенными или превышенными), вытеснение не должно быть выполнено, чтобы продолжить выделение многопортовых регистров новой вызываемой процедуре. Т.е. операция вытеснения (увеличения указателя сохранения/восстановления) отделяется от выделения многопортовых регистров (увеличения счетчика вершины стека). Это дает возможность операции вытеснения продолжаться как "фоновой" задачей, к примеру, посредством запроса с низким приоритетом в интерфейс 34 памяти, который обслуживается, только когда достаточная полоса пропускания на обращение к памяти доступна. В этом случае пространство в системе блоков теневых регистров становится доступным для выделения многопортовых физических регистров новым выделяемым процедурам, при этом накладывая минимальное влияние на производительность системы.

Согласно другому варианту осуществления, чтобы дополнительно минимизировать влияние обращений на поддерживающее запоминающее устройство 36, механизм 30 сохранения регистров может вытеснять и заполнять n-ный блок 32 теневых регистров безотносительно содержимого блока 28 физических регистров. Если механизм 30 сохранения регистров предполагает значительное число вызовов процедур или вызовы в процедуры, которые требуют большого числа физических регистров, он может активно вытеснять n-ный блок 32 теневых регистров, чтобы обеспечить значительное пространство во внутренней системе блоков теневых регистров, так что процедуры не накладывают задержку обращения к памяти, ассоциативно связанную с операциями вытеснения в поддерживающее запоминающее устройство 36. Альтернативно, если механизм 30 сохранения регистров допускает большое число возвратов процедур или возвратов в вызывающие процедуры, которым выделено большое число физических регистров, он может активно наполнять n-ный блок 32 теневых регистров, чтобы обеспечить много данных в системе блоков теневых регистров, так что процедуры не накладывают задержку обращения к памяти, ассоциативно связанную с операциями наполнения из поддерживающего запоминающего устройства 36.

В этом варианте осуществления механизм 30 сохранения регистров может отдельно отслеживать точку вытеснения/заполнения n-го блока 32 теневых регистров с помощью глобального указателя дна стека, описанного выше. Альтернативно, указатель дна стека может отслеживать только точку вытеснения/заполнения в n-м блоке 32 теневых регистров и базироваться на индикаторе FULL, ассоциативно связанном с (n-1)-м блоком 32 теневых регистров, чтобы идентифицировать вытеснения данных в n-ный блок 32 теневых регистров. В любом случае вследствие произвольного доступа второго порта двухпортовых регистров n-го блока 32 теневых регистров, механизм 30 сохранения регистров может вытеснять и заполнять данные между n-м блоком 32 теневых регистров и поддерживающим запоминающим устройством 36 независимо от выделения многопортовых регистров в блоке 28 физических регистров.

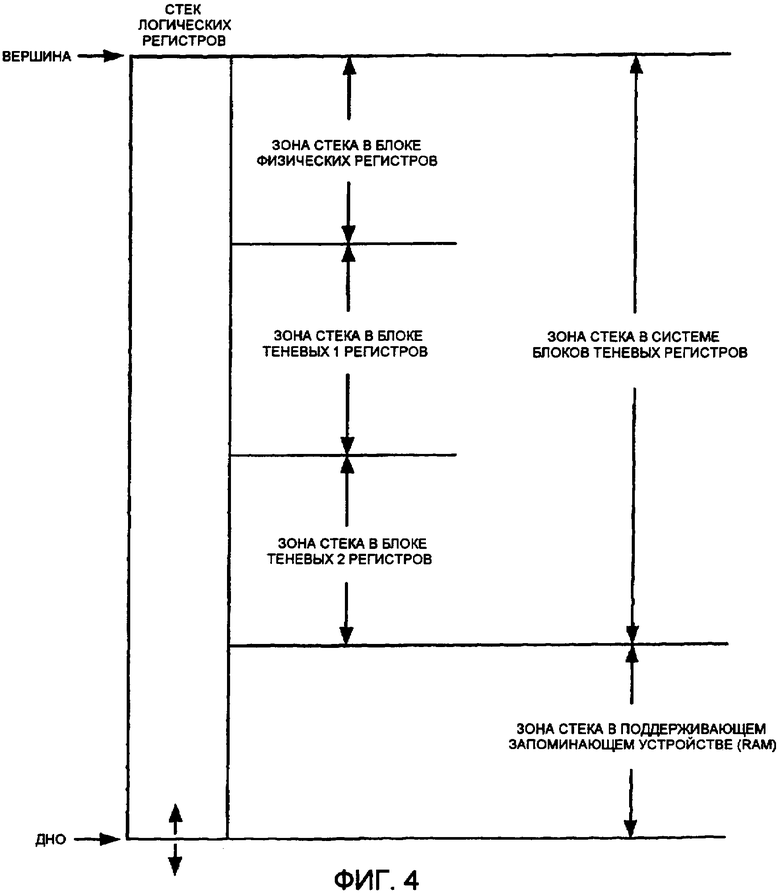

Фиг.4 иллюстрирует логическое представление системы блоков стековых регистров и ее физической реализации (в варианте осуществления, показанном на фиг.3). Система блоков стековых регистров работает как логический стек многопортовых регистров бесконечной глубины. Поскольку каждая процедура может осуществлять доступ только к стольким регистрам, сколько GPR, заданных в архитектуре набора команд, и блок 28 физических регистров имеет, по меньшей мере, этот размер, регистры, доступ к которым осуществляется напрямую посредством процедур, являются многопортовыми регистрами. Ниже блока физических регистров в логическом стеке регистров находятся двухпортовые регистры в блоках 32 теневых регистров. Система блоков теневых регистров содержит блок 28 физических регистров и все блоки 32 теневых регистров. Это внутренние регистры, из которых доступ к данным может осуществляться с минимальной задержкой. На дне логического стека регистров находятся данные, сохраненные в поддерживающее запоминающее устройство, например RAM вне микросхемы.

Отметим, что глубина логического стека регистров, реализованного во внутренних регистрах, является кратным целым размера блока 28 физических регистров (3× в показанном варианте осуществления). По меньшей мере, половина из этих регистров (2/3 из них в показанном варианте осуществления) являются простыми двухпортовыми регистрами с прямым соединением. Тем не менее, система блоков теневых регистров предоставляет производительность, очень близкую к производительности, достигаемой посредством более затратного варианта увеличения размера блока 28 физических регистров с помощью многопортовых регистров.

Соответствие один к одному и прямое связывание каждого многопортового регистра в блоке 28 физических регистров с одним или более двухпортовыми регистрами в блоках 32 теневых регистров позволяет системе блоков теневых регистров быть разделенной на банки, при этом каждый банк блока 28 физических регистров имеет увеличенную фактическую глубину посредством операций вытеснения и заполнения, как описано выше. Например, в определенных вариантах применения, таких как портативные электронные устройства с питанием от аккумуляторов, где энергопотребление является критичным, распространено снижать энергопотребление одного или более банков блока 28 физических регистров. Система блоков теневых регистров, использующая блоки 32 теневых регистров, полностью поддерживает эту стратегию экономии питания. Каждый блок 32 теневых регистров может быть разделен на банки, соответствующие банкам блока 28 физических регистров, и энергопотребление одного или более банков может быть снижено наряду с соответствующими банками блока 28 физических регистров. В функционирующих банках указатели вершины стека, сохранения/восстановления и (если имеется) дна стека работают так, как описано выше, в рамках границ банка. Данные сохраняются из одного или более многопортовых регистров в соответствующие двухпортовые регистры, чтобы повысить фактическую глубину функционирующего банка блока 28 физических регистров без реализации дополнительных затратных многопортовых регистров.

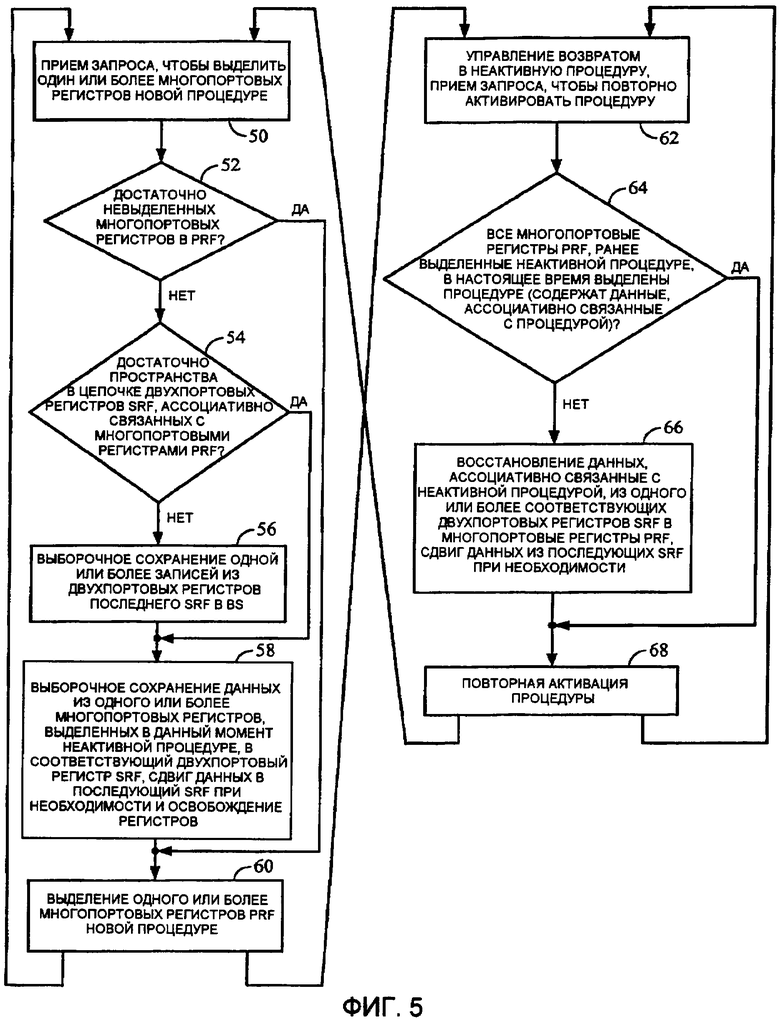

Способ работы системы блоков стековых регистров согласно одному варианту осуществления показан на блок-схеме последовательности операций по фиг.5. Механизм 30 сохранения регистров принимает запрос, чтобы выделить один или более многопортовых регистров в блоке 28 физических регистров для эксклюзивного использования посредством новой вызываемой процедуры, чтобы записать и считать данные, такие как операнды или результаты арифметических либо логических команд (этап 50). Механизм 30 сохранения регистров определяет то, достаточно ли невыделенных регистров остается в блоке 28 физических регистров (этап 52). Первоначально их достаточно, и запрошенное число многопортовых регистров блока 28 физических регистров выделяется новой процедуре (этап 60). Данный процесс может повторяться несколько раз, поскольку каждая процедура вызывает последующую процедуру (этап 50).

В некоторой точке процедура вызывается, и выделение многопортовых регистров запрашивается (этап 50), но недостаточно невыделенных многопортовых регистров остается в блоке 28 физических регистров, чтобы удовлетворить запрос (этап 52). Механизм 30 сохранения регистров в таком случае определяет, какие регистры в блоке 28 физических регистров должны быть освобождены, чтобы удовлетворить запрос, и являются ли соответствующие двухпортовые регистры в конце цепочки блоков 32 теневых регистров свободными (этап 54). Если да, по меньшей мере, достаточное число многопортовых регистров, которые выделены одной или более неактивных в данный момент процедур, освобождаются посредством сохранения их содержимого в соответствующие двухпортовые регистры с прямым соединением в блоке 32 теневых регистров (этап 58). Все данные в двухпортовых регистрах вытесняются в многопортовые регистры в последующем блоке 32 теневых регистров и так далее вниз по цепочке. Механизм 30 сохранения регистров затем выделяет эти освобожденные регистры, наряду с имеющимися освобожденными регистрами в блоке 28 физических регистров, в запрашивающую новую процедуру (этап 60), которая может продолжить приведение в исполнение и сохранить данные в ассоциативно связанных многопортовых регистрах блока 28 физических регистров.

Если достаточно новых процедур вызвано и/или если новые процедуры требуют большого числа выделений регистров, данные должны быть вытеснены в последний, или n-ный, блок 32 теневых регистров. В этом случае при запросе посредством новой процедуры (этап 50), если двухпортовые регистры в n-ном блоке 32 теневых регистров, которые соответствуют многопортовым регистрам в блоке 28 физических регистров, которые должны быть выделены, содержат допустимые данные (этап 54), механизм 30 сохранения регистров вытесняет данные в поддерживающее запоминающее устройство 36, такое как RAM вне микросхемы (этап 56). Данные затем могут быть сохранены из многопортовых регистров в блоке 28 физических регистров в соответствующие двухпортовые регистры в блоке 32 теневых регистров (этап 58) и освобожденные многопортовые регистры блока 28 физических регистров, выделенные новой процедуре (этап 60). Этот процесс может повторяться по мере того, как вызываются новые процедуры (этап 50).

В некоторой точке вместо вызова новой процедуры (этап 50) активная процедура может завершаться и возвращать управление в вызывающую процедуру, которая запрашивает повторную активацию (этап 62). Механизм 30 сохранения регистров выполняет проверку, чтобы определить то, остаются ли все регистры, первоначально выделенные неактивной процедуре, выделенными ей в блоке 28 физических регистров (этап 64). Если да, то все данные, записанные посредством процедуры, прежде чем она вызвала другую процедуру и стала неактивной, остаются в блоке 64 физических регистров, и процедура может повторно активироваться и возобновить приведение в исполнение (этап 68).

Если механизм 30 сохранения регистров вытеснил данные из одного или более многопортовых регистров, первоначально выделенных неактивной процедуре, в соответствующие двухпортовые регистры и выделил многопортовые регистры другой процедуре, механизм 30 сохранения регистров наполняет блок 28 физических регистров посредством сдвига данных, сохраненных в соответствующих двухпортовых регистрах блока 32 теневых регистров (этап 64). Неактивная процедура затем повторно активируется (этап 68). Данные могут быть наполнены в n-ный блок 32 теневых регистров из поддерживающего запоминающего устройства 36.

Система блоков теневых регистров, использующая блоки 32 теневых регистров, повышает производительность процессора посредством уменьшения количества раз, когда процессор должен быть прерван на операции сохранения/восстановления в поддерживающее запоминающее устройство 36 для блока 28 физических регистров. Это приводит к более быстрому выделению/освобождению регистров по вызовам/возвратам программных процедур, а также к снижению требуемого числа относительно медленных обращений к памяти вне микросхемы.

Система блоков теневых регистров, использующая блоки 32 теневых регистров, также экономит питание за счет уменьшения обращений к памяти вне микросхемы и за счет управления более короткими сетями посредством использования простых двухпортовых регистров, в сравнении с многопортовыми регистрами блока 28 физических регистров.

В одном варианте осуществления, чтобы максимизировать скорость операций вытеснения/наполнения регистров и минимизировать энергопотребление, двухпортовые регистры в блоке 32-1 теневых 1 регистров физически размещаются непосредственно рядом с соответствующими многопортовыми регистрами в блоке 28 физических регистров и соединяются напрямую. Аналогично, двухпортовые регистры в блоке 32-2 теневых 2 регистров физически размещаются непосредственно рядом с соответствующими двухпортовыми регистрами в блоке 32-1 теневых 1 регистров и соединяются напрямую. Фактически, в одном варианте осуществления каждая "строка" соответствующих многопортовых и двухпортовых регистров разрабатывается как модуль, который должен быть размещен и направляем на микросхеме. Это обеспечивает прямое соединение при минимальной длине сети между каждым соответствующим регистром (в отличие от разработки блока 28 физических регистров и блоков 32 теневых регистров как отдельных модулей, и при этом соединения между ними могут направляться с использованием большей длины сети по большей кремниевой зоне).

Хотя настоящее изобретение описано в отношении конкретных признаков, аспектов и вариантов осуществления, должно быть очевидным, что множество вариаций, модификаций и других вариантов осуществления возможно в рамках широкой области применения настоящего изобретения, и, соответственно, все вариации, модификации и варианты осуществления должны рассматриваться как находящиеся в рамках области применения изобретения. Следовательно, настоящие варианты осуществления должны рассматриваться во всех аспектах как иллюстративные, а не ограничивающие, и все изменения, попадающие в рамки смысла и эквивалентности прилагаемой формулы изобретения, должны охватываться ею.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСПОЛЬЗОВАНИЕ СИСТЕМЫ ПЕРЕИМЕНОВАНИЯ РЕГИСТРА ДЛЯ ПЕРЕДАЧИ ПРОМЕЖУТОЧНЫХ РЕЗУЛЬТАТОВ МЕЖДУ СОСТАВНЫМИ КОМАНДАМИ И РАСШИРЕННОЙ КОМАНДОЙ | 2008 |

|

RU2431887C2 |

| ЗАПОМИНАНИЕ ОПЕРАНДОВ СТЕКА В РЕГИСТРЕ | 2001 |

|

RU2271565C2 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| СИСТЕМЫ И СПОСОБЫ ПРОВЕРКИ АДРЕСА ВОЗВРАТА ПРОЦЕДУРЫ | 2014 |

|

RU2628163C2 |

| МАТРИЧНО-ВЕКТОРНЫЙ УМНОЖИТЕЛЬ С НАБОРОМ РЕГИСТРОВ ДЛЯ ХРАНЕНИЯ ВЕКТОРОВ, СОДЕРЖАЩИМ МНОГОПОРТОВУЮ ПАМЯТЬ | 2019 |

|

RU2795887C2 |

| ЭНЕРГОЭКОНОМНЫЕ СПОСОБЫ И УСТРОЙСТВО ИЗБИРАТЕЛЬНОГО РАЗРЕШЕНИЯ КОМПАРАТОРОВ В РЕГИСТРОВОМ ФАЙЛЕ С ПЕРЕИМЕНОВАНИЕМ НА ОСНОВЕ САМ НА ОСНОВАНИИ ИЗВЕСТНОГО СОСТОЯНИЯ ПРОЦЕССОРА | 2006 |

|

RU2389059C2 |

| СПОСОБ ОРГАНИЗАЦИИ ПЕРСИСТЕНТНОЙ КЭШ ПАМЯТИ ДЛЯ МНОГОЗАДАЧНЫХ, В ТОМ ЧИСЛЕ СИММЕТРИЧНЫХ МНОГОПРОЦЕССОРНЫХ КОМПЬЮТЕРНЫХ СИСТЕМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2002 |

|

RU2238584C2 |

| СИСТЕМЫ И СПОСОБЫ ОТСЛЕЖИВАНИЯ ФЛАГА В ОПЕРАЦИЯХ УСТРАНЕНИЯ ПЕРЕМЕЩЕНИЯ | 2014 |

|

RU2628156C2 |

| Устройство для синтаксического анализа программ | 1980 |

|

SU918950A1 |

Изобретения относятся к процессорам. Техническим результатом является повышение производительности. Способ управления системой блоков теневых регистров содержит этапы: выделяют первой процедуре один или более многопортовых регистров из блока физических регистров, которому соответствует часть логического стека регистров, сохраняют данные, ассоциативно связанные с первой процедурой, в выделенных многопортовых регистрах; выборочно сохраняют данные, ассоциативно связанные с первой процедурой, из одного или более многопортовых регистров в один или более регистров первого блока теневых регистров системы блоков теневых регистров, причем один или более регистров имеет независимые порты чтения/записи данных, и освобождают соответствующие выделенные многопортовые регистры для выделения второй процедуре; сохраняют данные, ассоциативно связанные с первой процедурой из первого блока теневых регистров во второй блок теневых регистров; сохраняют по меньшей мере часть данных, ассоциативно связанных с первой процедурой, из конкретного регистра второго блока теневых регистров в поддерживающее запоминающее устройство, и впоследствии извлекают упомянутую часть данных, ассоциативно связанных с первой процедурой, из поддерживающего запоминающего устройства в конкретный регистр второго блока теневых регистров; извлекают данные из второго блока теневых регистров в один или более регистров первого блока теневых регистров; и до продолжения приведения в исполнение первой процедуры, восстанавливают данные, ассоциативно связанные с первой процедурой, из одного или более регистров в один или более многопортовых регистров, и повторно выделяют один или более многопортовых регистров первой процедуре. 2 н. и 13 з.п. ф-лы, 5 ил.

1. Способ управления системой блоков теневых регистров, имеющей один или более блоков теневых регистров, содержащий этапы, на которых:

выделяют первой процедуре один или более многопортовых регистров из блока физических регистров, которому соответствует часть логического стека регистров, которая используется первой процедурой, и сохраняют данные, ассоциативно связанные с первой процедурой, в выделенных многопортовых регистрах;

выборочно сохраняют данные, ассоциативно связанные с первой процедурой, из одного или более многопортовых регистров в один или более регистров первого блока теневых регистров системы блоков теневых регистров, причем один или более регистров имеет независимые порты чтения/записи данных, и освобождают соответствующие выделенные многопортовые регистры для выделения второй процедуре;

сохраняют данные, ассоциативно связанные с первой процедурой из первого блока теневых регистров во второй блок теневых регистров системы блоков теневых регистров;

сохраняют по меньшей мере часть данных, ассоциативно связанных с первой процедурой, из конкретного регистра второго блока теневых регистров в поддерживающее запоминающее устройство, и впоследствии извлекают упомянутую часть данных, ассоциативно связанных с первой процедурой, из поддерживающего запоминающего устройства в конкретный регистр второго блока теневых регистров;

извлекают данные из второго блока теневых регистров в один или более регистров первого блока теневых регистров; и

до продолжения приведения в исполнение первой процедуры восстанавливают данные, ассоциативно связанные с первой процедурой, из одного или более регистров в один или более многопортовых регистров, и повторно выделяют один или более многопортовых регистров первой процедуре.

2. Способ по п.1, в котором каждый многопортовый регистр напрямую соединен с первым портом соответствующего двухпортового регистра системы блоков теневых регистров.

3. Способ по п.1, в котором часть данных сохраняется в конкретный регистр через первый порт упомянутого конкретного регистра, и в котором сохранение части данных, ассоциативно связанных с первой процедурой, из конкретного регистра в поддерживающее запоминающее устройство содержит считывание из второго порта упомянутого конкретного регистра.

4. Способ по п.1, в котором извлечение данных, ассоциативно связанных с первой процедурой, из поддерживающего запоминающего устройства в конкретный регистр выполняется механизмом сохранения регистров, имеющим произвольный доступ на чтение/запись к одному или более регистров отдельно взятого блока теневых регистров.

5. Способ по п.1, в котором второй порт каждого из одного или более регистров напрямую соединен с первым портом соответствующего регистра второго блока теневых регистров.

6. Способ по п.1, в котором сохранение данных и извлечение данных в регистры второго блока теневых регистров выполняется независимо от выделения многопортовых регистров.

7. Способ по п.1, в котором сохранение данных, ассоциативно связанных с первой процедурой, из регистров второго блока теневых регистров в поддерживающее запоминающее устройство содержит этап, на котором считывают данные, ассоциативно связанные с первой процедурой, из второго порта каждого регистра второго блока теневых регистров, и записывают данные в поддерживающее запоминающее устройство.

8. Способ по п.1, в котором извлечение данных, ассоциативно связанных с первой процедурой, из поддерживающего запоминающего устройства в регистры второго блока теневых регистров содержит этап, на котором считывают данные, ассоциативно связанные с первой процедурой, из поддерживающего запоминающего устройства и записывают данные во второй порт того же регистра второго блока теневых регистров, из которого они были считаны.

9. Способ по п.1, в котором выборочное сохранение данных, ассоциативно связанных с первой процедурой, из одного или более многопортовых регистров в один или более регистров содержит этап, на котором сохраняют данные, ассоциативно связанные с первой процедурой, в один или более регистров, только когда из числа многопортовых регистров остается недостаточно невыделенных регистров для выделения для второй процедуры.

10. Способ по п.1, в котором выборочное сохранение данных, ассоциативно связанных с первой процедурой, из одного или более многопортовых регистров в один или более регистров содержит этап, на котором сохраняют только данные, ассоциативно связанные с первой процедурой, в один или более регистров.

11. Способ по п.1, в котором выборочное сохранение данных, ассоциативно связанных с первой процедурой, из одного или более многопортовых регистров в один или более регистров содержит этап, на котором сохраняют: данные, ассоциативно связанные с первой процедурой, и дополнительно данные, ассоциативно связанные с одной или более процедур, приведенных в исполнение до первой процедуры, в один или более регистров.

12. Способ по п.11, в котором выборочное сохранение данных, ассоциативно связанных с первой процедурой и одной или более предыдущих процедур содержит этап, на котором сохраняют данные, когда предварительно определенное число многопортовых регистров содержит данные, ассоциативно связанные с неактивными процедурами.

13. Способ по п.11, в котором выборочное сохранение данных, ассоциативно связанных с первой процедурой и одной или более предыдущих процедур содержит этап, на котором сохраняют все данные в многопортовых регистрах, ассоциативно связанных с неактивными процедурами.

14. Способ по п.1, дополнительно содержащий этапы, на которых:

разделяют блок физических регистров и соответствующие двухпортовые регистры на два или более банка;

понижают энергопотребление, по меньшей мере, одного банка; и

выделяют функционирующие многопортовые регистры, сохраняют данные в функционирующих многопортовых регистрах, выборочно сохраняют данные в функционирующих двухпортовых регистрах, освобождают функционирующие многопортовые регистры для выделения, восстанавливают данные из функционирующих двухпортовых регистров в многопортовые регистры, и повторно выделяют функционирующие многопортовые регистры в одном или более функционирующих банках.

15. Устройство для управления системой блоков теневых регистров, имеющей один или более блоков теневых регистров, содержащее:

средство для выделения первой процедуре одного или более многопортовых регистров из блока физических регистров, которому соответствует часть логического стека регистров, которая используется первой процедурой, и для сохранения данных, ассоциативно связанных с первой процедурой, в выделенных многопортовых регистрах;

средство для выборочного сохранения данных, ассоциативно связанных с первой процедурой, из одного или более многопортовых регистров в один или более двухпортовых регистров первого блока теневых регистров, имеющих независимые порты чтения/записи данных, когда предварительно заданное количество многопортовых регистров становится неактивным, и для освобождения соответствующих выделенных многопортовых регистров для выделения второй процедуре, причем предварительно заданное количество задается записываемым значением в конфигурационном регистре;

средство для сохранения данных из одного или более двухпортовых регистров первого блока теневых регистров в соответствующие регистры второго блока теневых регистров;

средство для выборочного сохранения данных из соответствующих регистров второго блока теневых регистров в поддерживающее запоминающее устройство, и для извлечения данных из поддерживающего запоминающего устройства во второй блок теневых регистров; и

средство для, до продолжения приведения в исполнение первой процедуры, восстановления данных, ассоциативно связанных с первой процедурой, из соответствующих регистров второго блока теневых регистров в один или более двухпортовых регистров первого блока теневых регистров, и для восстановления данных из одного или более двухпортовых регистров в многопортовые регистры, и для повторного выделения многопортовых регистров первой процедуре.

| Фильтр для очистки воды от масла | 1980 |

|

SU955583A1 |

| Фундамент под колонну | 1978 |

|

SU676691A1 |

| US 2002116662 A1, 22.08.2002 | |||

| АДРЕСАЦИЯ РЕГИСТРОВ В УСТРОЙСТВЕ ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2193228C2 |

Авторы

Даты

2010-11-27—Публикация

2006-11-13—Подача