ОБЛАСТЬ ТЕХНИКИ, К КОТОРОЙ ОТНОСИТСЯ ИЗОБРЕТЕНИЕ

Настоящее изобретение в целом относится к способам снижения мощности (энергопотребления) в процессоре и, более конкретно, к эффективным способам избирательного разрешения на основании известного состояния процессора компараторов в регистровом файле с возможностью переименования на основе ассоциативного запоминающего устройства (АЗУ, CAM).

УРОВЕНЬ ТЕХНИКИ

Для достижения высокоэффективного исполнения программы реализация процессора может использовать конвейер, который работает с высокой тактовой частотой с наличием ступеней конвейера с короткой продолжительностью. Структура системы команд для такого типа процессора также может задавать набор регистров общего назначения, подлежащих использованию исполнительными блоками в качестве источников данных и адресатов для результатов. Каждая команда в качестве части кодирования команды включает в состав битовые поля, которые указывают адреса регистров, подлежащих использованию в качестве операндов источника или адресата. Эти описатели регистров называются номерами (НРК, IRN) регистров команд. Набор регистров общего назначения, доступных для использования исполнительными блоками, может изменяться в зависимости от операционного состояния процессора. Например, исполнение программы в конкретном операционном режиме может быть ограничено использованием команд, которые могут осуществлять доступ только к поднабору из полного набора регистров общего назначения. Процессор также может поддерживать исполнение команд «не в порядке следования» в ходе конвейерного исполнения и перед завершением команд в порядке следования в программе. Для поддержки глубоких конвейеров с исполнением «не в порядке следования» процессор может реализовывать бульшее количество физических регистров, чем может поддерживаться в соответствии с системой набора команд процессора. К реализованным в регистровом файле физическим регистрам обычно осуществляется доступ посредством использования адреса в виде номера (НФР, PRN) физического регистра. Тем не менее, имеются трудности, связанные с командой, непосредственно использующей PRN-адрес. Например, процессор, поддерживающий структуру системы команд с пространством IRN-адресов для шестнадцати регистров, может быть осуществлен с помощью пространства PRN-адресов шестидесяти четырех физических регистров. Чтобы решить проблему такого различия между пространством IRN-адресов и пространством PRN-адресов, процессор может использовать аппаратные средства переименования, чтобы отображать содержащийся в команде IRN-адрес на адрес в виде номера (PRN) физического регистра. Такое отображение может быть выполнено посредством использования ассоциативного запоминающего устройства CAM с наличием тегов, компараторов тегов и массивов данных. Аппаратные средства переименования могут использовать IRN-адрес в качестве тега для физического регистра, хранимого в массиве данных (в составе) CAM.

Проблема использования устройств CAM для таких целей состоит в том, что используемые в CAM компараторы тегов в типовом исполнении CAM определяются при каждом доступе к регистровому файлу. Для высокоэффективной реализации используемые в CAM компараторы являются динамическими схемами и потребляют энергию, поскольку они предварительно заряжаются и разряжаются. Дополнительно, поскольку регистровый файл является обычно многопортовым устройством, на каждый порт приходится множество CAM-компараторов, увеличивая дополнительно потребление мощности.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

В числе своих нескольких аспектов настоящее изобретение признает, что существует потребность в аппаратуре, которая обеспечивает энергоэкономичный управляемый регистровый файл, использующий ассоциативную память CAM. В одном аспекте аппаратура управления использует тег, который хранится в CAM, причем тег является адресом элемента CAM, и тег имеет внутри тега атрибут, описывающий операционное состояние процессора. Компаратор тегов сравнивает тег с адресом, сформированным процессором. Компаратор операционного состояния сравнивает атрибут с текущим операционным состоянием процессора, чтобы определить, разрешить (задействовать) или запретить (блокировать) компаратор тегов.

Другой аспект направлен на способ выбора подлежащих запрету компараторов адресов регистров в регистровом файле на основе ассоциативной памяти CAM. В этом способе компараторы адресов регистров, которые не могут вполне соответствовать в заданном доступе, идентифицируются на основании знания состояния процессора, используемого вместе с регистровым файлом на основе CAM. Идентифицированными компараторами адресов регистров управляют с тем, чтобы они входили в экономичное состояние. Другие аспекты изобретения исследуются, как описано дополнительно подробно ниже.

Более полное понимание настоящего изобретения, а также дополнительные признаки и преимущества изобретения будут очевидны из нижеследующего подробного описания и сопроводительных чертежей.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

Фиг.1 - иллюстрация примерной системы беспроводной связи, в которой может полезно использоваться вариант осуществления изобретения;

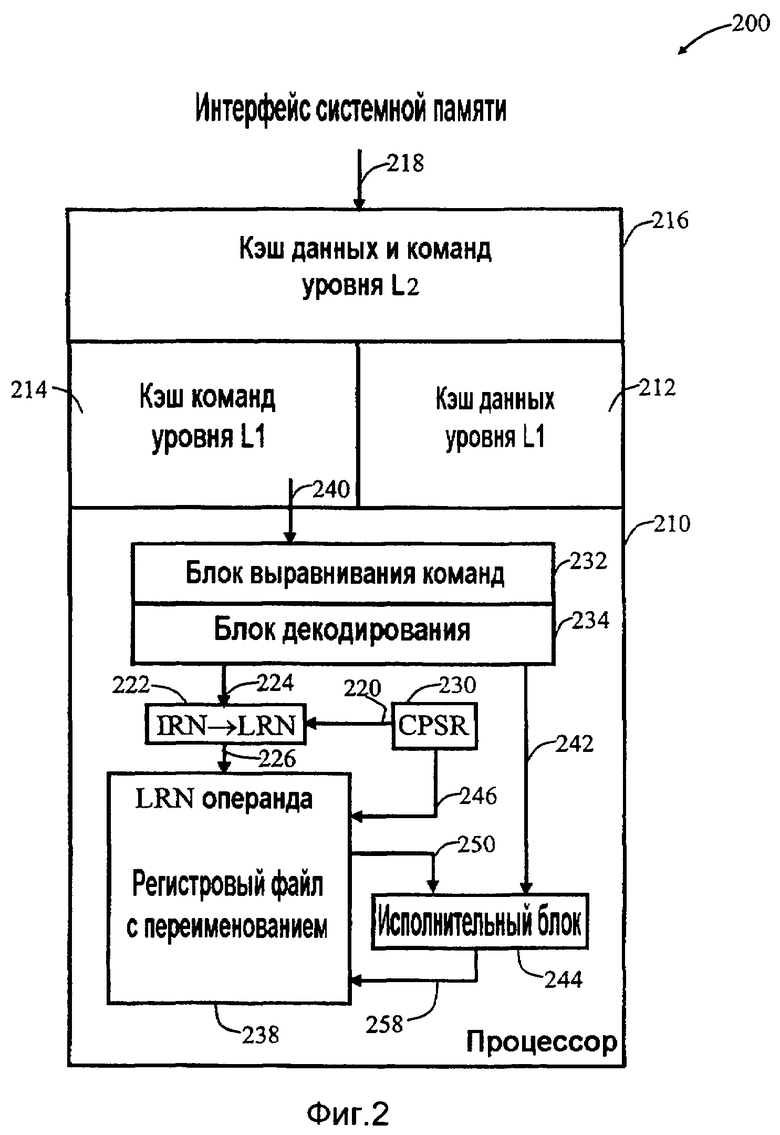

Фиг.2 - блок-схема процессорного комплекса в соответствии с настоящим изобретением;

Фиг.3A - иллюстрация в соответствии с настоящим изобретением примерного устройства для отображения номера (IRN) регистра команд на номер (PRN) физического регистра в комплексе переименования регистрового файла, имеющем в своем составе регистровый файл с возможностью переименования, блок отображения, регистр текущего состояния процессора (РТСП, CPSR) и исполнительный блок;

Фиг.3B - графическая иллюстрация в соответствии с настоящим изобретением примерного устройства для отображения IRN на PRN в комплексе переименования регистрового файла с множеством адресов портов, имеющем в своем составе регистровый файл с возможностью переименования, множество блоков отображения, CPSR и исполнительный блок;

Фиг.4 - графическая иллюстрация в соответствии с настоящим изобретением последовательности действий для избирательного разрешения компараторов тегов ассоциативной памяти (CAM) в переименовании регистрового файла; и

Фиг.5 - графическая иллюстрация в соответствии с настоящим изобретением другого примерного устройства отображения номера (IRN) регистра команд на номер (PRN) физического регистра в комплексе переименования регистрового файла, имеющем в своем составе регистровый файл с возможностью переименования с наличием в тегах бита достоверности и бита «последний по времени использования», блок отображения, CPSR и исполнительный блок.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

Настоящее изобретение теперь будет описано более полно со ссылкой на сопроводительные чертежи, на которых показываются несколько вариантов осуществления изобретения. Данное изобретение, тем не менее, может быть осуществлено в различных формах и не должно рассматриваться ограниченными вариантами осуществления, сформулированными в документе. Предпочтительнее эти воплощения представлены с тем, чтобы данное раскрытие было всесторонним и полным и полностью передало объем изобретения для специалистов в данной области.

Код программы для вычислительной машины или "программный код" для действия над ним или для выполнения операций в соответствии с особенностями изобретения может быть первоначально написан на высокоуровневом языке программирования, таком как C, C++, JAVA®, Smalltalk, JavaScript®, Visual Basic®, TSQL, Perl или на различных других языках программирования. Программа, написанная на одном из этих языков, компилируется в архитектуру целевого процессора. Программы, предназначенные для архитектуры целевого процессора, также могут быть написаны непосредственно на языке собственного ассемблера. Программа на языке собственного ассемблера использует мнемонические представления команд для двоичных команд машинного уровня. Программный код или машиночитаемая среда, как используется в настоящем документе, относятся к коду на машинном языке, такому как объектный код, формат которого является «понимаемым» процессором.

На фиг.1 показана примерная система 100 беспроводной связи, в которой может полезно использоваться вариант осуществления изобретения. С целью иллюстрации на фиг.1 показываются три удаленных устройства 120, 130 и 150 и две базовые станции 140. Следует принять во внимание, что типичные системы беспроводной связи могут иметь большее количество удаленных устройств и базовых станций. Удаленные устройства 120, 130 и 150 включают в состав аппаратные компоненты 125A, 125B и 125C соответственно, которые исполняют программный код в соответствии с настоящим изобретением. На фиг.1 показан сигнал 180 прямой линии связи от базовых станций 140 и удаленных устройств 120, 130 и 150 и сигнал 190 обратной линии связи от удаленных устройств 120, 130 и 150 на базовые станции 140.

На фиг.1 удаленное устройство 120 показано в виде мобильного телефона, удаленное устройство 130 показано в виде портативного компьютера и удаленное устройство 150 показано в виде стационарно установленного удаленного устройства в системе беспроводной связи местной линии. Например, удаленными устройствами могут быть карманные устройства персональных систем связи (ПСС, PCS), портативные устройства данных, такие как персональные помощники данных, или стационарно установленные устройства данных, такие как оборудование для считывания показаний измерений. Хотя фиг.1 иллюстрирует удаленные устройства в соответствии с особенностями изобретения, изобретение не ограничено этими примерными проиллюстрированными устройствами. Изобретение может соответствующим образом применяться в любом аппаратном компоненте, использующем конвейерный процессор с наличием регистрового файла с переименованием на основе CAM и структуру системы команд, которая ограничивает пространство адресов регистров операндов в зависимости от режима работы процессора.

На фиг.2 показана блок-схема процессорного комплекса 200, в котором может использоваться вариант осуществления изобретения. Процессорный комплекс 200 может соответствующим образом применяться в аппаратных компонентах 125A-C для исполнения программного кода. Процессорный комплекс 200 включает в состав конвейерный процессор 210, кэш 212 данных 1-го уровня (L1), кэш (I-кэш) 214 команд 1-го уровня, кэш 216 данных и команд 2-го уровня (L2-кэш) и интерфейс 218 системной памяти. Периферийные устройства, которые могут соединяться с процессорным комплексом, для ясности обсуждения настоящего изобретения не показываются. Процессор 210 непосредственно соединен с кэшем 212 данных уровня L1 и I-кэшем 214 уровня L1, из которых процессор 210, соответственно, извлекает данные и команды на основании организации иерархической памяти.

Структура системы команд процессора может иметь форматы 32-битовых команд с наличием 4-битовых полей адреса регистрового операнда, обозначаемых в документе как поля номера (IRN) регистра команд, которые идентифицируют вплоть до шестнадцати регистров для каждого 4-битового IRN. Структура системы команд может дополнительно задавать режимы работы, в которых 4-битовый IRN команды задает ссылку на различные регистры. Например, значения IRN 8-14 могут осуществлять ссылку на различные регистры в зависимости от операционного режима процессора. В результате такого изменения в интерпретации значений IRN в команде, в процессоре требуется большее количество регистров, чем указывал бы 4-битовый IRN. Например, в регистровом файле могут быть необходимы тридцать два регистра, чтобы поддерживать все регистры, которые могут быть адресованы в различных режимах работы процессора посредством полей 4-битовых IRN в командах. Тот же процессор также может поддерживать форматы команд, которые используют 3-битовые IRN, например, в форматах 16-битовых команд. Поскольку и 4-битовые, и 3-битовые IRN являются недостаточными, чтобы указывать все доступные тридцать два регистра, предоставляемые примерным процессором 210, кодирование режима работы 220 процессора используется в функции 222 отображения, чтобы преобразовать IRN в 5-битовый номер (НЛР, LRN) логического регистра. 5-битовый LRN дает возможность адресации заданного архитектурой набора регистров в регистровом файле. В целом, функция 222 отображения не является простой конкатенацией бита операционного режима с IRN, поскольку поднаборы пространства IRN могут представлять отображение на различные регистры. Например, архитектура процессора может указывать, чтобы IRN R14 отображался на многие различные регистры в зависимости от операционного режима.

В типичном использовании может ожидаться, что процессор 210 сначала исполняет прикладную программу пользователя в общем пользовательском режиме. Менее часто процессор 210 исполняет код в других операционных режимах, таких как режим супервизора, или других режимах, например, для обработки прерываний, или исключительных ситуаций. Обеспечение эффективной поддержки для часто используемого пользовательского режима является выгодным для работы с пониженной мощностью. Из соображений эффективности пользовательский режим процессора 210 задает ограниченное использование регистрового пространства для регистров, имеющих IRN, который отображается на LRN в диапазоне 0-15. Другие операционные режимы, другими словами, не пользовательские режимы, используют регистры в пределах области значений LRN, соответствующей 0-31. Таким образом, процессор 210, работая в пользовательском режиме, не имеет доступа к регистрам в пределах области значений LRN, соответствующей 16-31. Общее отображение IRN на LRN требует знания операционного режима процессора, который может быть задан кодированием 220 битового поля регистра (CPSR) 230 текущего состояния процессора. Например, 4-битовый IRN, обеспечиваемый на сигналах 224 адреса операнда, является соответственно преобразованным при помощи CPSR 230 в 5-битовый LRN в виде выходного сигнала 226 адреса порта считывания. Будет признано, что, несмотря на то, что настоящее изобретение описывается в конкретном контексте, оно будет применимо к другим режимам работы и распределениям регистров, отличающимся от конкретно описанных.

В конвейерном процессоре, таком как процессор 210, реализовано большее количество физических регистров, чем поддерживается в соответствии со структурой системы команд. Одним следствием наличия большого количества физических регистров в процессоре 210 является то, что многие значения одного и того же указанного в команде регистра могут храниться одновременно в однозначно определенных физических регистрах. При таком подходе может быть разрешен ряд зависимостей по данным между командами, что позволяет преодолеть границы последовательного исполнения без приостановки конвейера и посредством этого повысить производительность.

Процессор 210 составлен из блока 232 выравнивания команд, блока 234 декодирования, блока 238 переименования регистрового файла, регистра (CPSR) 230 текущего состояния процессора и многих исполнительных блоков, из которых для ясности иллюстрации показан только один исполнительный блок 244. Команды принимаются в блоке 232 выравнивания команд из иерархии памяти через интерфейс 240. После того как команды должным образом выровнены, они декодируются в блоке 234 декодирования. Операция декодирования использует управляющие сигналы 242, чтобы поставлять управляющую информацию на исполнительный блок 244. Сигналы 224 адреса операнда используются, чтобы поставлять IRN-адресы исходного и целевого операнда на блок 222 отображения. Блок 222 отображения отображает на LRN каждый IRN-адрес операнда на основании текущего состояния процессора. Например, для 32-битовых команд 4-битовый IRN-адрес A3-A0 операнда-источника преобразуется в соответствующий 5-битовый LRN A4-A0. Подобным образом для 16-битовых команд 3-битовые IRN преобразуются в 5-битовые LRN, как определено согласно текущему состоянию процессора, как задано в соответствии со структурой системы команд процессора. Регистровый файл 238 с переименованием также принимает бит или биты текущего состояния процессора от выходного сигнала 246 CPSR из CPSR 230.

Регистровый файл 238 с переименованием отображает LRN на номер (PRN) физического регистра. PRN используется для осуществления доступа к значению соответствующего регистра и значение, хранимое в регистре PRN, является выводимым на выходной порт 250 считывания. Также, когда выдается команда, регистр результатов помечается тегом в регистровом файле 238 с переименованием. В конце исполнения команды, которое может быть после ряда ступеней исполнения конвейера, результат, сформированный исполнительным блоком 244, посылается по выходной шине 258 на регистровый файл 238 с переименованием, где он сохраняется по предварительно помеченному тегом PRN-адресу результата.

На фиг.3A иллюстрируется примерное исполнение отображения номера (IRN) регистра команд на номер (PRN) физического регистра в комплексе 300 переименования регистрового файла, имеющем в составе регистровый файл 238 с переименованием, блок 301 отображения, CPSR 240 и исполнительный блок 244. Регистровый файл 238 с переименованием содержит файл (ФФР, PRF) 302 физических регистров, основанный на САМ, и массив 304 тегов CAM для одиночного порта считывания в составе регистрового файла. Блок 301 отображения отображает IRN, поставляемый на вход 305 IRN порта А, на LRN на выходе 306 LRN на основании состояния 307 CPSR. CAM-PRF 302 содержит бόльшее количество регистров, чем задано согласно архитектуре процессора, например шестьдесят четыре регистра, каждый из которых адресуем посредством PRN 308. Массив тегов CAM содержит шестьдесят четыре тега, таких как тег 310, и логическую схему сравнения, связанную с каждым тегом, такую как схему 312 OR (ИЛИ) и логику 314 сравнения. Тег и логика сравнения тегов вместе обозначаются как теговая функция 316. Каждый тег, такой как тег 310, хранит 5-битовый LRN, A4-A0 в массиве 304 тегов CAM. Тег ассоциируется с регистром, таким как регистр i 318, в CAM-PRF 302. В типичном устройстве CAM логика сравнения для всех тегов действует, чтобы сравнивать входящий адрес со всеми тегами, чтобы определить, есть ли совпадение между входящим адресом и хранимым тегом. В эффективном массиве 304 тегов CAM, согласно настоящему изобретению, логику сравнения для осуществления сравнения избирательно разрешают на основании операционного состояния процессора. Если логика сравнения тегов не разрешена, она находится в экономичном состоянии.

После декодирования, такого как выполняемое посредством ступени 234 декодирования по фиг.2, сформированный выход 306 LRN вводится в массив 304 тегов CAM. CPSR 240 выводит сигнал 322 «не пользовательский режим»  который также вводится в массив 304 тегов CAM. Сигнал 322 «не пользовательский режим»

который также вводится в массив 304 тегов CAM. Сигнал 322 «не пользовательский режим»  и выход 306 5-битового LRN операнда вводится в каждую теговую функцию, такую как теговая функция 316. В каждой теговой функции сигнал 322

и выход 306 5-битового LRN операнда вводится в каждую теговую функцию, такую как теговая функция 316. В каждой теговой функции сигнал 322  является логически сложенным по OR с инверсией самого старшего бита 5-битового LRN, хранимого в теге. Например, в теговой функции 316 сигнал 322

является логически сложенным по OR с инверсией самого старшего бита 5-битового LRN, хранимого в теге. Например, в теговой функции 316 сигнал 322  и логическое отрицание NOT (НЕ) A4

и логическое отрицание NOT (НЕ) A4  324 вводится на схему 312 OR. Биты A3-A0 хранятся в 4-битовой адресной части 330 тега 310. Назначением схем OR, таких как схема 312 OR, является формирование сигнала для разрешения логики сравнения в каждой теговой функции. Для процессора 210 из настоящего примера вся логика сравнения в каждой теговой функции действует, если процессор находится не в пользовательском режиме.

324 вводится на схему 312 OR. Биты A3-A0 хранятся в 4-битовой адресной части 330 тега 310. Назначением схем OR, таких как схема 312 OR, является формирование сигнала для разрешения логики сравнения в каждой теговой функции. Для процессора 210 из настоящего примера вся логика сравнения в каждой теговой функции действует, если процессор находится не в пользовательском режиме.

В теговой функции 316 сигналом 322  «не пользовательский режим» является 1 и выходом схемы 312 OR является 1, отпирающие компаратор 314, когда процессор не находится в пользовательском режиме. Если процессор находится в пользовательском режиме, сигналом 322

«не пользовательский режим» является 1 и выходом схемы 312 OR является 1, отпирающие компаратор 314, когда процессор не находится в пользовательском режиме. Если процессор находится в пользовательском режиме, сигналом 322  будет 0. Если самым старшим битом в A4 тега адреса является 0, сигналом 334 логического отрицания A4 будет 1, и затем схема 312 OR выведет сигнал 332 разрешения, которым является 1, чтобы разрешить логику сравнения 314 для значений LRN 0-15, которые имеют A4, равный 0. Альтернативно, если процессор находится в пользовательском режиме, сигналом 322

будет 0. Если самым старшим битом в A4 тега адреса является 0, сигналом 334 логического отрицания A4 будет 1, и затем схема 312 OR выведет сигнал 332 разрешения, которым является 1, чтобы разрешить логику сравнения 314 для значений LRN 0-15, которые имеют A4, равный 0. Альтернативно, если процессор находится в пользовательском режиме, сигналом 322  будет 0, и если самым старшим битом A4 тега LRN-адреса является 1, для значений LRN 16-31 сигналом 334 логического отрицания A4 будет 0, и затем схема 312 OR выведет разрешающий сигнал 332 в виде 0, удерживая логику сравнения 314 в экономичном состоянии. Логическая функция разрешающего сигнала 332 задается согласно следующему уравнению:

будет 0, и если самым старшим битом A4 тега LRN-адреса является 1, для значений LRN 16-31 сигналом 334 логического отрицания A4 будет 0, и затем схема 312 OR выведет разрешающий сигнал 332 в виде 0, удерживая логику сравнения 314 в экономичном состоянии. Логическая функция разрешающего сигнала 332 задается согласно следующему уравнению:  разрешающий сигнал 332, где символ

разрешающий сигнал 332, где символ  представляет операцию логического OR. Функция

представляет операцию логического OR. Функция  разрешающий сигнал 332 эквивалентна реализации NAND (НЕ-И) с использованием уравнения:

разрешающий сигнал 332 эквивалентна реализации NAND (НЕ-И) с использованием уравнения:  разрешающий сигнал 332, где символ

разрешающий сигнал 332, где символ  представляет операцию логического NOT, инвертирующую значение в круглых скобках, и символ

представляет операцию логического NOT, инвертирующую значение в круглых скобках, и символ  представляет операцию логического AND (И).

представляет операцию логического AND (И).

В зависимости от реализации логики сравнения может использоваться сигнал запрета в качестве альтернативы вышеописанного разрешающего сигнала 332. Сигнал запрета может быть получен путем замены схемы OR 312 схемой AND и подачи сигнала A4 в качестве одного входа и сигнала U «пользовательский режим» в качестве второго входа, как задается согласно нижеследующему уравнению:  сигнал запрета. В этом случае сигнал запрета будет активным, только если процессор находится в пользовательском режиме и тег LRN находится между 16-31.

сигнал запрета. В этом случае сигнал запрета будет активным, только если процессор находится в пользовательском режиме и тег LRN находится между 16-31.

Когда логика сравнения тегов разрешена и имеется соответствие между 5-битовым LRN-адресом 306 операнда и хранимым тегом A4 324 LRN в A3-A0 330, говорят, что произошло совпадение (попадание). Ситуация совпадения, логически указываемая посредством сигнала 340 совпадения, приводит к тому, что регистр PRN 318, связанный с совпавшим тегом, подлежит доступу из CAM-PRF 302 и выводится на порт 344 считывания в качестве вводимого на исполнительный блок 244.

На фиг.3B иллюстрируется отображение IRN на PRN в комплексе 350 переименования регистрового файла с наличием нескольких адресов 305 и 355 портов, имеющем в составе регистровый файл 358 с переименованием, множество блоков 301 и 360 отображения, CPSR 240 и исполнительный блок 244. Даже притом, что только два порта считывания операнда для регистрового файла 358 с переименованием показываются на фиг.3B, следует принять во внимание, что комплекс 350 переименования регистрового файла может быть расширен для поддержки дополнительных портов считывания операнда, таких как, например, шесть портов одновременного считывания в процессоре.

Для каждого порта считывания обеспечивается отдельный блок отображения, такой как блок 301 отображения, чтобы отображать IRN 305 порта А на LRN на выходе 306, и блок 360 отображения, чтобы отображать IRN 355 порта B на LRN на выходе 364. Порт А (RPA) 368 считывания и порт B (RPB) 370 считывания являются разрешающими сигналами, используемыми в схемах 372 и 374 логического умножения (AND) логики разрешения в составе теговой функции, чтобы запретить компараторы 314 и 376, соответственно, если порты считывания не используются.

Тег 310 подает адресные биты A4 324 и A3-A0 330 на оба компаратора 314 и 376. Если разрешающие сигналы RPA 368 и RPB 370 являются активными, указывающими порты считывания, подлежащие использованию, оба компаратора отпираются в зависимости от самого старшего бита A4 и операционного режима U CPSR, используя  разрешающий сигнал 332, обеспечивая такие же возможности экономии энергии для обоих компараторов, как было ранее описано по отношению к показанному на фиг.3A комплексу 300 переименования регистрового файла. При многих компараторах для каждого тега во многих арифметических операциях могут происходить многие совпадения, такие как сигналы 340 и 380 совпадения, как это происходит при умножении R7·R7, чтобы получить R72. При многих совпадениях один и тот же регистр, такой как регистр i 318, выводится на многие порты, такие как порт А 344 считывания и порт B 384 считывания.

разрешающий сигнал 332, обеспечивая такие же возможности экономии энергии для обоих компараторов, как было ранее описано по отношению к показанному на фиг.3A комплексу 300 переименования регистрового файла. При многих компараторах для каждого тега во многих арифметических операциях могут происходить многие совпадения, такие как сигналы 340 и 380 совпадения, как это происходит при умножении R7·R7, чтобы получить R72. При многих совпадениях один и тот же регистр, такой как регистр i 318, выводится на многие порты, такие как порт А 344 считывания и порт B 384 считывания.

На фиг.4 иллюстрируется последовательность действий 400, направленных на избирательное разрешение компараторов тегов ассоциативной памяти (CAM) в регистровом файле с переименованием в соответствии с настоящим изобретением. Первый этап 405 происходит, когда выдается команда и команда задает IRN операнда-источника, подлежащий считыванию из регистрового файла с возможностью переименования, такого как регистровый файл 358 с переименованием. На следующем этапе 410 IRN отображается на LRN в блоке отображения, таком как блок 301 отображения, в зависимости от операционного режима процессора, обеспечиваемого посредством регистра текущего состояния процессора (CPSR), такого как CPSR 240. На этапе 415 выбираются надлежащие теговые функции для порта считывания CAM, такие как теговая функция 316, при помощи разрешающих сигналов порта считывания в массиве тегов CAM, таком как массив 304 тегов CAM. На этапе 420, который происходит параллельно по всем выбранным теговым функциям портов считывания, проверяется, чтобы самый старший бит (msb) тега и пользовательский режим (U) из CPSR оба были активными, являясь оба 1. Если и msb тега, и пользовательский режим являются активными в теговой функции, то теговая функция на этапе 425 запрещает компаратор тегов CAM. На этапе 430 теговая функция останавливается для каждого запрещенного компаратора тегов CAM, и запрещенный компаратор остается в экономичном состоянии.

Если на этапе 420 и msb тега, и пользовательский режим не являются активными в теговой функции, то теговая функция на этапе 435 разрешает компаратор тегов CAM. На этапе 440, который происходит параллельно по всем разрешенным компараторам тегов CAM, LRN сравнивается с тегом, таким как тег 310, посредством компаратора, такого как компаратор 314. Если LRN не соответствует тегу, на этапе 445 теговая функция останавливается. Если LRN соответствует тегу, происходит совпадение, такое как обозначенное сигналом 340 совпадение, и на этапе 450 связанный с тегом физический регистр считывается из файла (PRF) физических регистров, такого как CAM-PRF 302. Считанное значение регистра подается через порт считывания, такой как порт 344 считывания, на соответствующий исполнительный блок, такой как исполнительный блок 244.

На фиг.5 иллюстрируется другой аспект осуществления отображения номера (IRN) регистра команд на номер (PRN) физического регистра в комплексе 500 переименования регистрового файла, имеющем в составе регистровый файл 538 с переименованием с битом 502 достоверности и битом 504 «последний по времени использования» (ПВ, MR) в тегах, таком как тег 510, блок 301 отображения, CPSR 240 и исполнительный блок 244. Бит 502 достоверности указывает, что связанный с тегом регистр PRN не разрешен, если бит достоверности есть 0. Когда бит достоверности есть 0, логика сравнения не разрешена и остается в экономичном состоянии. Бит 504 MR указывает, содержит ли связанный с тегом регистр PRN последнее по времени сформированное значение или не содержит. Когда выдается команда, указывающая результирующий LRN, выделяется элемент (файла) физического регистра для приема значения данных и тег записывается с LRN. Тег помечается как «последний по времени» путем установки бита MR для этого элемента, когда данные результата записываются на несколько тактов позже, далее в конвейере. Также повторно устанавливается бит 504 MR для элемента, который ранее содержал последнее значение данных для этого конкретного LRN-адреса. Если бит 504 MR является 0 для конкретного элемента, логика сравнения для этого элемента не разрешена и удерживается в экономичном состоянии.

Комплекс 500 переименования регистрового файла подобен комплексу 300 переименования регистрового файла по фиг.3 с дополнением бита 502 достоверности, бита 504 MR и новой логики для разрешения логики сравнения. Новая логика использует трехвходовую схему 520 AND между схемой 312 OR и логикой сравнения 314. Одним входом на схему 520 AND является бит 504 MR, вторым входом является бит достоверности 502 и третьим входом является выход 332 схемы OR. Всякий раз, когда, по меньшей мере, один из трех входов на схему 520 AND является 0, логика сравнения удерживается в экономичном состоянии. Чтобы разрешить логику сравнения, значение 318 данных должно быть действительным, V=l, «последние по времени» данные, MR=1, и выход схемы 312 OR должен быть 1, разрешая, чтобы выход схемы 524 AND был 1 и разрешил логику 314 сравнения.

Поскольку в среднем пользовательский режим является наиболее интенсивно используемым режимом в действии и пользовательский режим ограничивает пространство адресов регистров до 0-15, сорок восемь из шестидесяти четырех функций логического сравнения в массиве 304 тегов CAM для каждого порта считывания являются обычно неразрешенными и удерживаются в экономичном состоянии. Это представляет существенные энергосбережения в массиве тегов CAM по сравнению с конструктивным решением, в котором все шестьдесят четыре функции логического сравнения используются при каждом доступе независимо от режима работы процессора.

Альтернативный подход к использованию схемы 312 OR состоит в том, чтобы реализовывать схему-защелку выбранного режима (ВР, MS) в каждой теговой функции, такой как теговая функция 316. Схема-защелка MS может быть установлена или сброшена при каждом изменении режима, выполняемом посредством процессора, что является относительно нечастым событием, и поэтому изменение состояния схемы-защелки MS может занимать один или два такта, требуя соблюдения малого времени ожидания изменения режима. После входа в новый режим процессора каждый элемент тега будет определять новый режим и устанавливать или сбрасывать схему-защелку MS соответственно. Тогда выход схемы-защелки MS может быть использован, чтобы удерживать логику сравнения в экономичном состоянии, если элемент не может соответствовать, поскольку элемент доступен только из режимов, отличных от текущего режима процессора.

Тогда как настоящее изобретение было раскрыто в предпочтительном в настоящее время контексте, следует признать, что настоящие указания могут быть приспособлены к разнообразным контекстам, совместимым с данным раскрытием и нижеследующей формулой изобретения.

Например, в альтернативной архитектуре, которая разбивает использование регистрового файла на несовместные наборы регистров в зависимости от операционного режима, могут использоваться многие регистровые файлы с переименованием. Исполнение «не в порядке следования» для глубоко конвейеризованного процессора может быть определено с наличием двух различных операционных режимов. Например, могут использоваться два операционных режима, таких как пользовательский режим и режим супервизора для обработки системы, прерываний и исключительных ситуаций. В реализации процессора один регистровый файл с возможностью переименования может использоваться для пользовательского режима и один регистровый файл с возможностью переименования может использоваться для режима супервизора. Для этой альтернативной архитектуры пользовательский режим поддерживает 16 регистров, как задано согласно системе команд. Регистровый файл с переименованием для пользовательского режима потребует дополнительные регистры, например 16 дополнительных регистров, чтобы поддерживать команды «на лету» вследствие исполнения «не в порядке следования» и глубокого конвейера. В режиме супервизора регистровый файл с переименованием для режима супервизора будет поддерживать отдельный набор из 16 заданных архитектурой регистров и иметь 16 регистров «на лету» вследствие исполнения «не в порядке следования» и глубокого конвейера. Общее количество в 32 физических регистра для пользовательского режима использовалось бы в регистровом файле с переименованием для пользовательского режима. Всего 32 физических регистра режима супервизора использовалось бы в регистровом файле с переименованием для режима супервизора. В действии только один регистровый файл с переименованием будет активным в зависимости от операционного режима, а другой регистровый файл с переименованием будет в экономичном состоянии. Другие подобные модификации и адаптации, удовлетворяющие требованиям конкретного конструктивного применения, будут очевидны средним специалистам в данной области техники.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИСПОЛЬЗОВАНИЕ СИСТЕМЫ ПЕРЕИМЕНОВАНИЯ РЕГИСТРА ДЛЯ ПЕРЕДАЧИ ПРОМЕЖУТОЧНЫХ РЕЗУЛЬТАТОВ МЕЖДУ СОСТАВНЫМИ КОМАНДАМИ И РАСШИРЕННОЙ КОМАНДОЙ | 2008 |

|

RU2431887C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ИДЕНТИФИКАЦИИ ИНСТРУКЦИЙ ДЛЯ УДАЛЕНИЯ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ С ИЗМЕНЕНИЕМ ПОСЛЕДОВАТЕЛЬНОСТИ | 2013 |

|

RU2644528C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ДОСТУПА К ПАМЯТИ В КЛАСТЕРНОЙ МАШИНЕ ШИРОКОГО ИСПОЛНЕНИЯ | 2013 |

|

RU2662394C2 |

| МОДУЛЬ СОПРОЦЕССОРА КЭША | 2011 |

|

RU2586589C2 |

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

| КОМАНДА И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ СОРТИРОВКИ И ВЫГРУЗКИ КОМАНД СОХРАНЕНИЯ | 2014 |

|

RU2663362C1 |

| СИСТЕМЫ И СПОСОБЫ ПРЕДОТВРАЩЕНИЯ НЕСАНКЦИОНИРОВАННОГО ПЕРЕМЕЩЕНИЯ СТЕКА | 2014 |

|

RU2629442C2 |

| ИСПОЛЬЗОВАНИЕ АУТЕНТИФИЦИРОВАННЫХ МАНИФЕСТОВ ДЛЯ ОБЕСПЕЧЕНИЯ ВНЕШНЕЙ СЕРТИФИКАЦИИ МНОГОПРОЦЕССОРНЫХ ПЛАТФОРМ | 2014 |

|

RU2599340C2 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

| УСТРОЙСТВО И СПОСОБ РЕВЕРСИРОВАНИЯ И ПЕРЕСТАНОВКИ БИТОВ В РЕГИСТРЕ МАСКИ | 2014 |

|

RU2636669C2 |

Изобретение относится к способам снижения мощности (энергопотребления) в процессоре. Техническим результатом является сохранение мощности при считывании регистра из регистрового файла. Устройство сохранения мощности при считывании регистра из регистрового файла содержит процессор для считывания операндов, обеспечивающий исполнение команд; файл (PRF) физических регистров с наличием операндов, подлежащих считыванию процессором; массив тегов, имеющий адрес, связанный с операндом в PRF, и атрибут, описывающий операционное состояние процессора; массив компараторов тегов, причем каждый компаратор тегов действует, чтобы сравнивать сформированный процессором адрес операнда с тегом, совпадение тега при сравнении является требуемым для считывания операнда из PRF; и массив компараторов операционного состояния, причем каждый компаратор операционного состояния связан с тегом и действует, чтобы сравнивать атрибут с текущим операционным состоянием процессора и активировать или блокировать связанный компаратор тегов, причем активируются не все компараторы тегов. Способ описывает работу этого устройства. 3 н. и 17 з.п. ф-лы, 6 ил.

1. Устройство управления ассоциативной памятью (САМ), содержащее:

тег, который хранится в САМ, причем тег является адресом элемента САМ и атрибут внутри тега описывает операционное состояние процессора;

компаратор тегов, который сравнивает тег с адресом, сформированным процессором; и

компаратор операционного состояния, который сравнивает атрибут с текущим операционным состоянием процессора, причем компаратор тегов является активированным или блокированным в зависимости от результатов сравнения атрибута с текущим операционным состоянием процессора.

2. Устройство управления САМ по п.1, в котором компаратор тегов является блокированным, если атрибут соответствует текущему операционному состоянию процессора.

3. Устройство управления САМ по п.1, в котором компаратор тегов находится в состоянии пониженной мощности, когда блокирован.

4. Устройство управления САМ по п.1, в котором компаратор тегов является активированным, если атрибут не соответствует текущему операционному состоянию процессора.

5. Устройство управления САМ по п.1, в котором компаратор тегов, когда активирован, формирует указатель совпадения, когда тег соответствует адресу, сформированному процессором.

6. Устройство управления САМ по п.5, дополнительно содержащее:

файл физических регистров САМ, содержащий множество физических регистров, действующих так, что при указании совпадения выбирается физический регистр, связанный с совпавшим тегом.

7. Устройство управления САМ по п.1, в котором атрибут является самым старшим битом тега.

8. Устройство управления САМ по п.1, в котором текущее операционное состояние процессора указывают посредством бита, хранимого в регистре текущего состояния процессора.

9. Устройство управления САМ по п.1, в котором сформированный процессором адрес является номером (LRN) логического регистра.

10. Устройство управления САМ по п.9, в котором LRN получают посредством преобразования номера (IRN) регистра команд в LRN в зависимости от текущего операционного состояния процессора.

11. Устройство управления САМ по п.1, дополнительно содержащее:

множество хранимых в САМ тегов, причем каждый тег имеет атрибут, который описывает операционное состояние процессора;

компаратор тегов, связанный с каждым тегом; и

компаратор операционного состояния, связанный с каждым тегом,

причем компаратор операционного состояния сравнивает атрибут в каждом теге с текущим операционным состоянием процессора, причем связанный с каждым тегом компаратор тегов является активированным или блокированным в зависимости от результатов сравнения атрибута, находящегося в теге, с текущим операционным состоянием процессора.

12. Устройство управления САМ по п.1, дополнительно содержащее:

множество портов доступа;

множество хранимых в САМ тегов, причем каждый тег имеет атрибут, который описывает операционное состояние процессора;

компаратор тегов, связанный с каждым тегом для каждого порта доступа; и

компаратор операционного состояния, связанный с каждым тегом, причем компаратор операционного состояния сравнивает атрибут в каждом теге с текущим операционным состоянием процессора, причем множество компараторов тегов, связанных с каждым тегом для каждого порта доступа, является активированным или блокированным в зависимости от результата сравнения атрибута в теге с текущим операционным состоянием процессора.

13. Устройство сохранения мощности при считывании регистра из регистрового файла, причем устройство содержит:

процессор для считывания операндов, обеспечивающий исполнение команд;

файл (PRF) физических регистров с наличием операндов, подлежащих считыванию процессором;

массив тегов, причем тег имеет адрес, связанный с операндом в PRF, тег имеет атрибут, описывающий операционное состояние процессора;

массив компараторов тегов, причем каждый компаратор тегов действует, чтобы сравнивать сформированный процессором адрес операнда с тегом, совпадение тега при сравнении является требуемым для считывания операнда из PRF; и

массив компараторов операционного состояния, причем каждый компаратор операционного состояния связан с тегом и действует, чтобы сравнивать атрибут с текущим операционным состоянием процессора, и активировать или блокировать связанный компаратор тегов, причем активированы не все компараторы тегов для осуществления сравнения на основании сравнения атрибута с текущим операционным состоянием процессора.

14. Устройство по п.13, в котором атрибутом является самый старший бит тега.

15. Устройство по п.13, в котором теги дополнительно содержат бит «последний по времени», причем бит «последний по времени» в теге указывает состояние связанного операнда в PRF, и компаратор тегов дополнительно является активированным или блокированным в зависимости от бита «последний по времени» в сравниваемом теге.

16. Устройство по п.13, дополнительно содержащее:

множество портов доступа;

массив компараторов тегов для каждого порта доступа и

массив компараторов операционного состояния, причем каждый компаратор операционного состояния связан с тегом и действует, чтобы сравнивать атрибут с текущим операционным состоянием процессора и активировать или блокировать связанный компаратор тегов для каждого порта доступа, причем на основании сравнения атрибута с текущим операционным состоянием процессора для каждого порта доступа активируют не все компараторы тегов для осуществления сравнения.

17. Способ выбора подлежащих блокированию компараторов адресов регистров в регистровом файле на основе ассоциативной памяти (САМ), причем способ содержит этапы, на которых:

идентифицируют, какие компараторы адресов регистров возможно не могут соответствовать в данном доступе на основании знания состояния процессора, подлежащего использованию вместе с регистровым файлом на основе САМ; и

управляют компараторами адресов регистров, идентифицированными в качестве не имеющих возможности вероятно соответствовать, с тем, чтобы они входили в состояние малой мощности.

18. Способ по п.17, дополнительно содержащий этапы, на которых:

сравнивают атрибут тега САМ с текущим операционным состоянием процессора и

идентифицируют компараторы адресов регистров, которые не могут вероятно соответствовать в данном доступе в качестве таких компараторов адресов регистров, у которых атрибут тега соответствует текущему операционному состоянию процессора.

19. Способ по п.17, в котором этап управления компараторами адресов регистров, идентифицированными в качестве не имеющих возможности вероятно соответствовать, дополнительно содержит этапы, на которых:

сравнивают атрибут тега САМ с текущим операционным состоянием процессора и

управляют компараторами адресов регистров, подлежащими блокированию, в зависимости от сравнения атрибута тега САМ с текущим операционным состоянием процессора.

20. Способ по п.17, дополнительно содержащий этапы, на которых:

формируют в процессоре номер логического регистра и

подают номер логического регистра на компараторы адресов регистров, которые подлежат сравнению с тегом САМ.

| US 6317819 В1, 13.11.2001 | |||

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

Авторы

Даты

2010-05-10—Публикация

2006-03-03—Подача