Изобретение относится к вычислиельной технике и предназначено для втоматического определения адреса еисправности в цифровой вычислиельной машине, состоящей не менее ем из двух процессоров.

Цель изобретения - повышение точости диагностики за счет одновремен-

ния обработк сигнал Окон Прерывание лам

ости диагностики за счет одновремен- rnp.,

ого сравне1шя выходных сигналов про- to V I 1 ,

I (г eccoDOB.. L -I

Пр, (TOpl nf.-

15

coИ, .P

25

30

ессоров

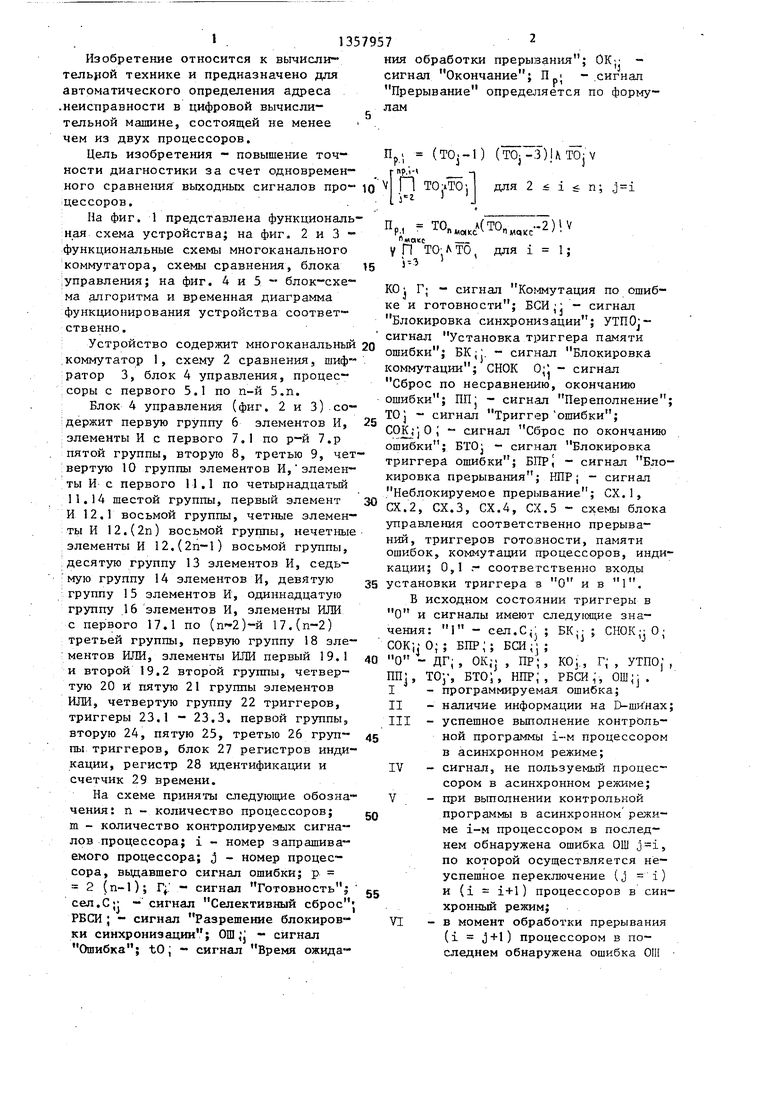

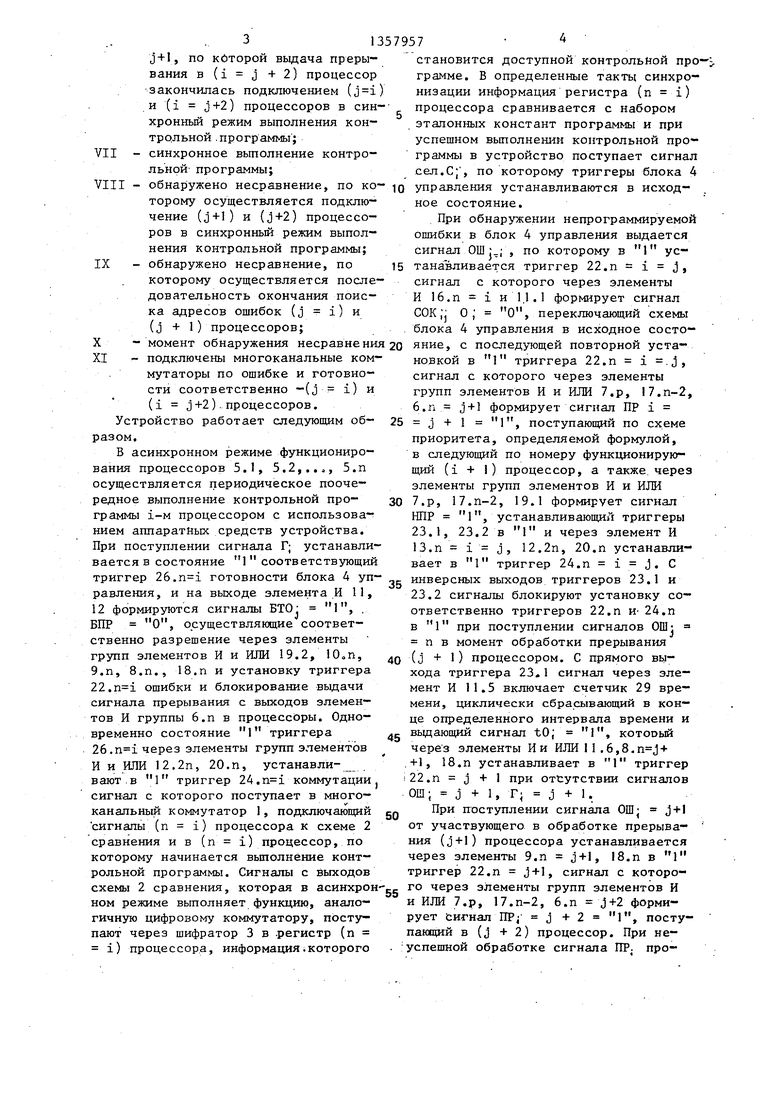

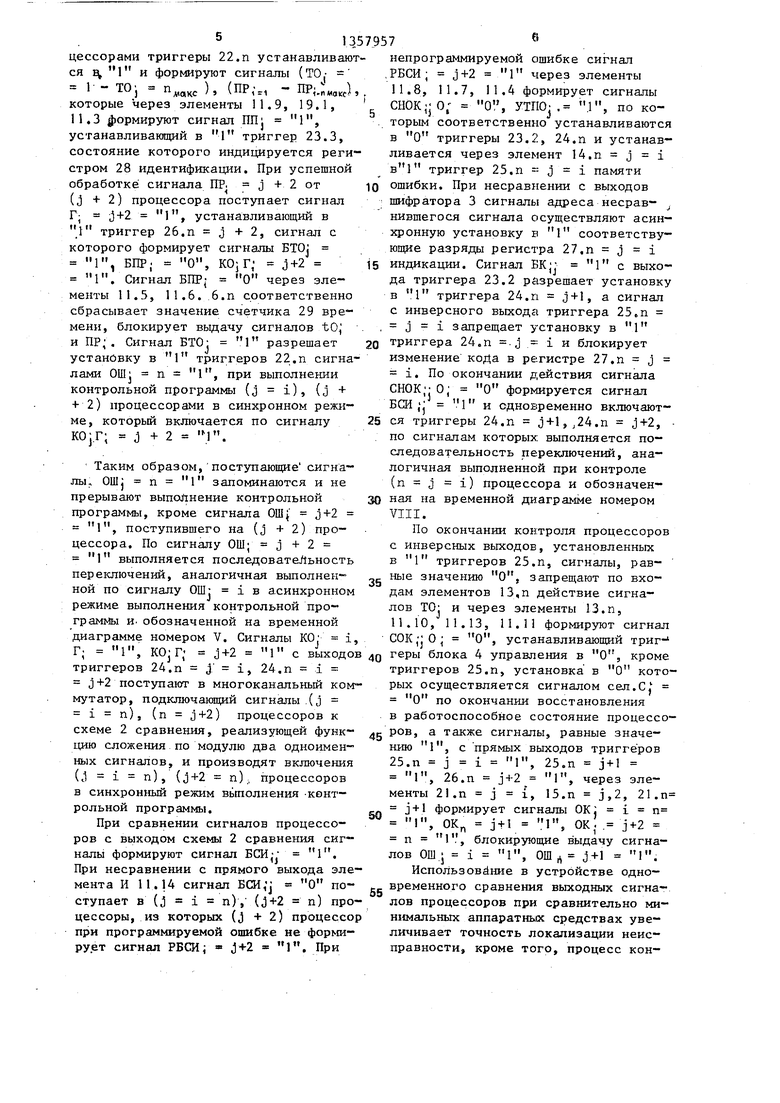

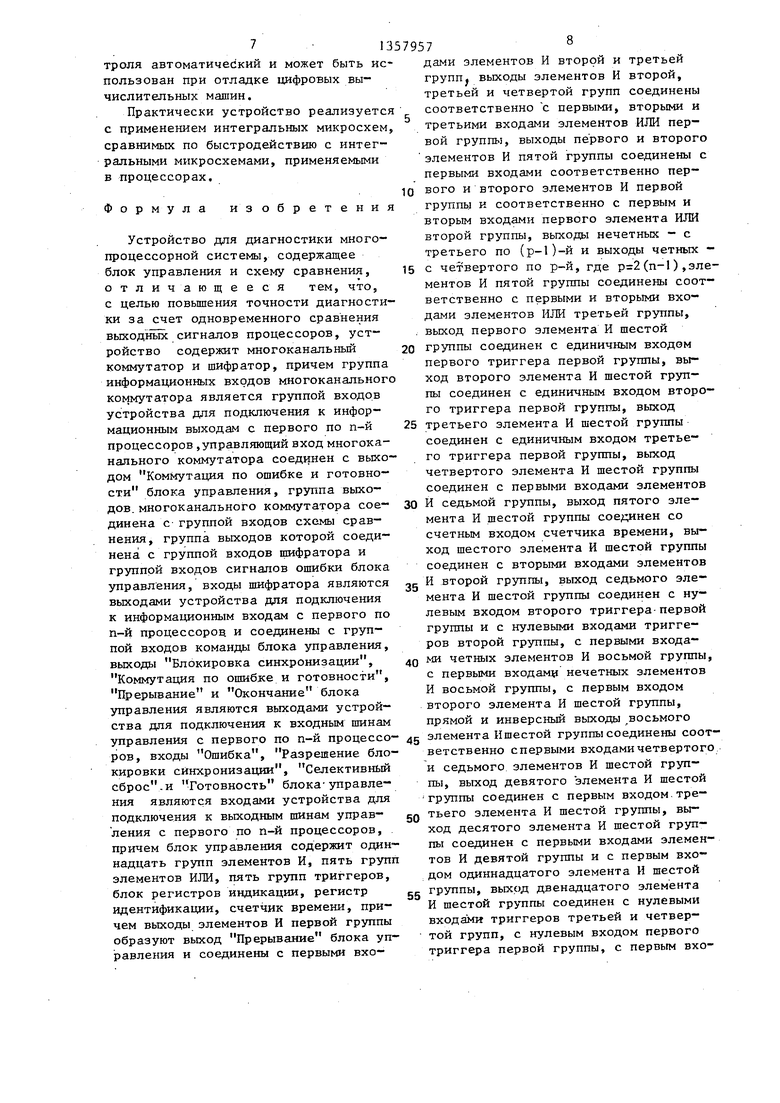

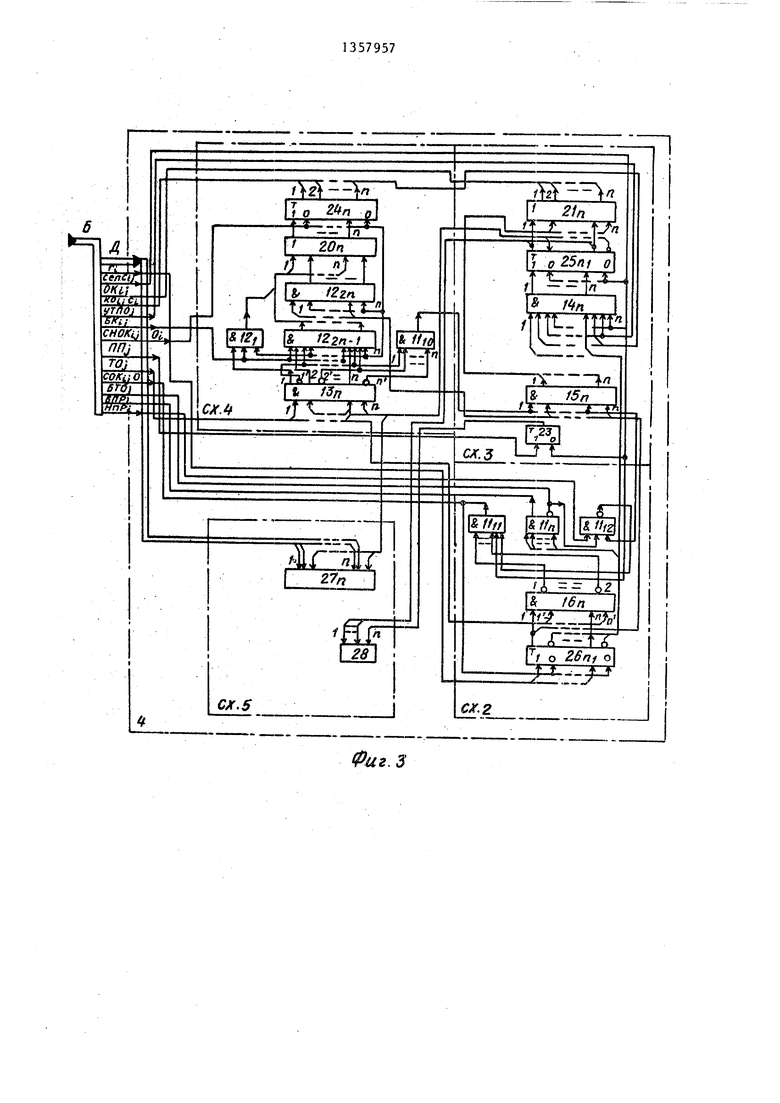

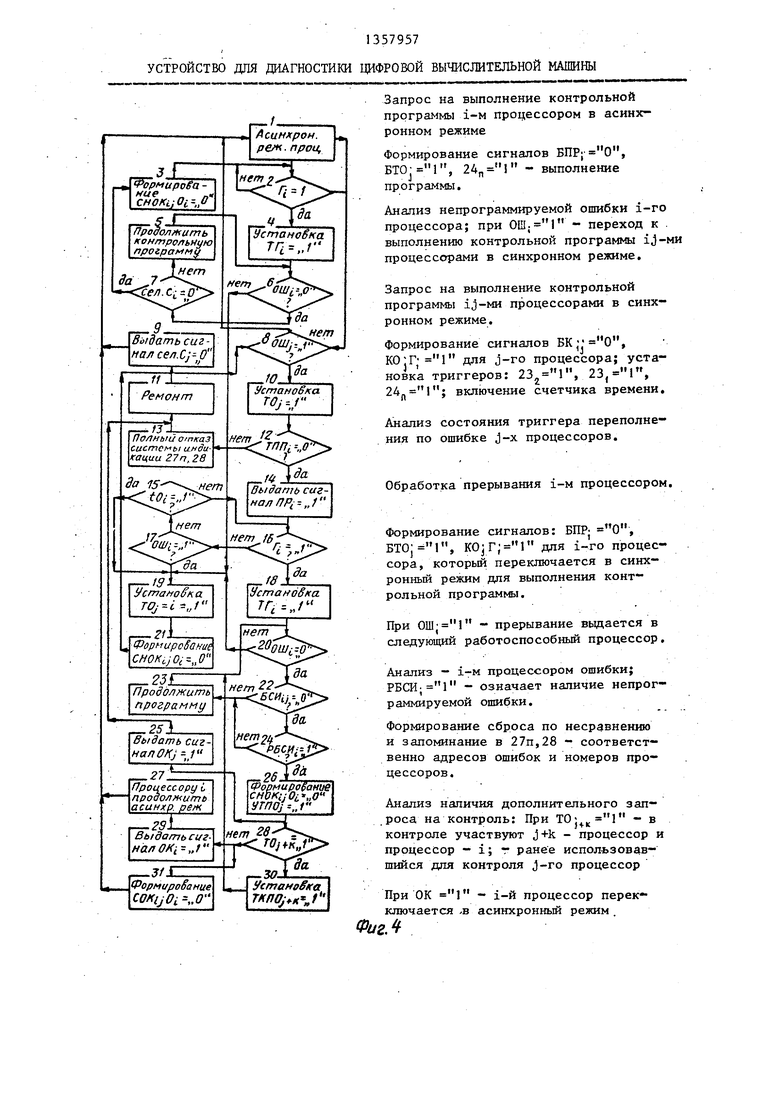

Ha фиг. 1 представлена функциональая схема устройства; на фиг, 2 и 3 - ункциональные схемы многоканального коммутатора, схемы сравнения, блока правления; на фиг. 4 и 5 блок-схема алгоритма и временная диаграмма Функционирования устройства соответственно,

Устройство содержит многоканалытый 20 коммутатор 1, схему 2 сравнения, шифратор 3, блок 4 управления, процес- соры с первого 5.1 по п-й 5.п.

Блок 4 управления (фиг. 2 и 3) держит первую группу 6 элементов элементы И с первого 7,1 по р-й 7 пятой группы, вторую 8, третью 9, чет- вертую 10 группы элементов И, элементы И с первого 11.1 по четырнадцатый 11.14 шестой группы, первый элемент И 12.1 восьмой группы, четные элементы И 12.(2п) восьмой группы, нечетные элементы И 12.(2n-l) восьмой группы, десятую группу 13 элементов И, седь- мую группу 14 элементов И, девятую группу 15 элементов И, одиннадцатую группу 16 элементов И, элементы ИЛИ с первого 17.1 по ()-й 17.(п-2) третьей группы, первую группу 18 эле- ментов ИЛИ, элементы ИЛИ первый 19.1 и второй 19.2 второй группы, четвертую 20 и пятую 21 группы элементов ИЛИ, четвертую группу 22 триггеров, триггеры 23.1 - 23.3. первой группы, вторую 24, пятую 25, третью 26 группы триггеров, блок 27 регистров индикации, регистр 28 идентификации и счетчик 29 времени.

На схеме приняты следую1дие обозна™ чения: n - количество процессоров; m - количество контролируемых сигналов процессора; i - номер запрашиваемого процессора; j - номер процессора, выдавшего сигнал ошибки; р 2 (п-1); Г; - сигнал Готовность 5

П

ТОп.«.с

Р-1

макс™

у П ТО; л ТО Г-Э

ко

Г; сиг

ке и готовно II

35

Блокировка сигнал Уста ошибки ; БК; коммутации ; Сброс по не ошибки ; ПП; TOj - сигнал COKj jO, - си ошибки ; ETO триггера оши кировка прер Неблокируем СХ.2, СХ.З, управления с ний, триггер ошибок, комм кации; 0,1 г установки тр

В исходно О и сигнал чения: 1 4Q

COKij о- ; БПР

О - ДГ; , О

пи;, ТО;-, БТ

45

I

II

III

IV

V

50

сел.С;; - сигнал Селективный сброс ; РБСИ; - сигнал Разрешение блокировки синхронизации ; ОШ , j - сигнал Ошибка ; tO; - сигнал Время ожида55

VI

/ I JJ

прогр налич успеш ной п в аси сигна сором при в прогр ме iнем о по ко успеш и (i хронн

в мом {i следн

ния обработки прерывания ; ОК- - сигнал Окончание ; П ; -.сигнал Прерывание определяется по форму лам

rnp.,

Пр, (TOpl) (TOj-3)UTOjV nf.-

для

n;

j-i

П

ТОп.«.с(ТО„м,кс--2)И

Р-1

макс™

у П ТО; л ТО Г-Э

для 1

5

0

ко

Г; сигнал Ко1Ф1утация по ошибке и готовности II

.

БСИ

м

- сигнал .

5

Блокировка синхронизации ; УТПО;- сигнал Установка триггера памяти ошибки ; БК;:. - сигнал Блокировка коммутации ; СНОК 0; - сигнал Сброс по несравнению, окончанию ошибки ; ПП; - сигнал Переполнение ; TOj - сигнал Триггер ошибки ; COKj jO, - сигнал Сброс по окончанию ошибки ; ETOj - сигнал Блокировка триггера ошибки ; Б1ТР - сигнал Блокировка прерывания ; НПР; - сигнал Неблокируемое прерывание ; СХ.1, СХ.2, СХ.З, СХ.4, СХ.5 - схемы блока управления соответственно прерываний, триггеров готовности, памяти ошибок, коммутации процессоров, индикации; 0,1 г- соответственно входы установки триггера в О и в 1.

В исходном состоянии триггеры в О и сигналы имеют следуюпще значения: 1 сел., ; БК;СПОК- О;

Q

COKij о- ; БПР ; БСИ;| ;

О - ДГ; , ОК,- , ПР; , KOj., Г; , УТПО) ,

пи;, ТО;-, БТО;, НПР;, РБСИ , ош;;

5

I

II

III

IV

V

0

5

VI

/ I JJ V/ 1} у ча f J I. uw2i. у ft

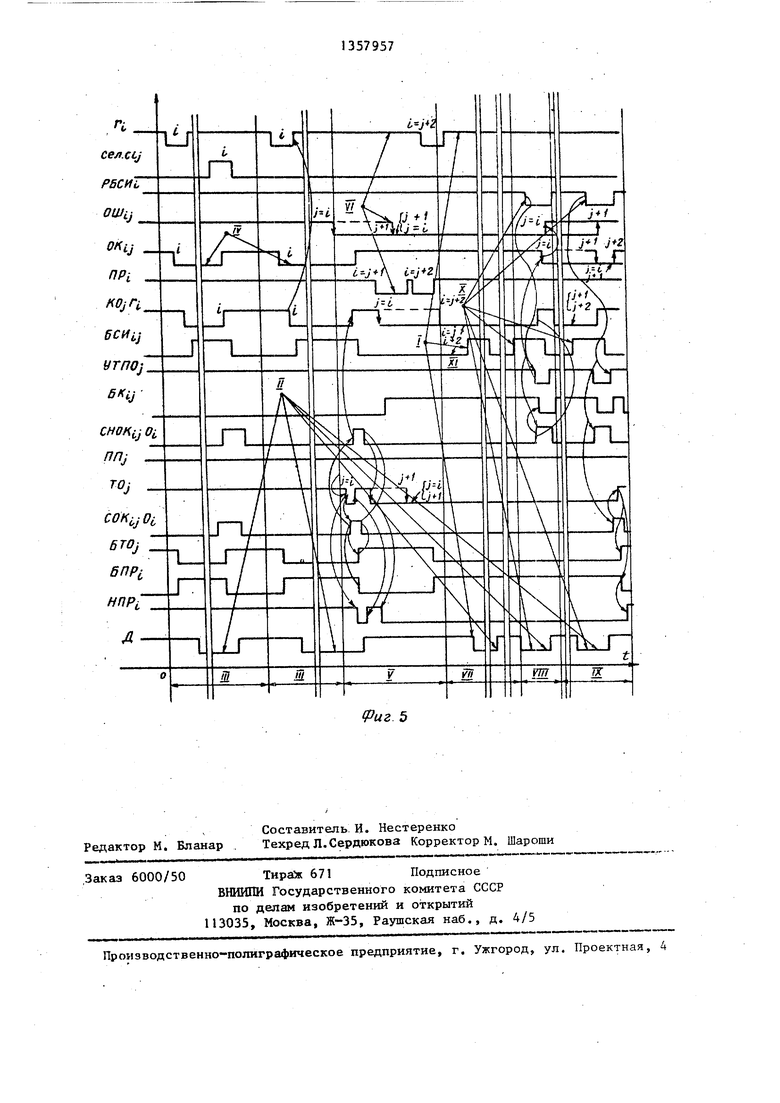

программируемая ошибка; наличие информации на D-ши нах; успешное выполнение контрольной программы i-M процессором в асинхронном режиме; сигнал, не пользуемый процессором в асинхронном режиме; при выполнении контрольной прогрсгммы в асинхронном режиме iM процессором в последнем обнаружена ошибка ОШ , по которой осуществляется неуспешное переключение (j i) и (i i+1) процессоров в синхронный режим;

в момент обработки прерывания {i J+1) процессором в последнем обнаружена ошибка OIII

j+I, по кйторой вьщача прерывания в (i j +2) процессор закончилась подключением () и (1 J+2) процессоров в син-- хронньш режим выполнения контрольной .программы; синхронное вьтолнение контрольной- программы;

становится доступной контрольной про грамме. В определенные такты синхронизации информация регистра (п i) процессора сравнивается с набором эталонных констант программы и при успешном выполнении контрольной программы в устройство поступает сигнал сел., по которому триггеры блока 4

VIII - обнаружено несравнение, по ко- IQ управления устанавливаются в исходX

торому осуществляется подключение (j+l) и (j+2) процессоров в синхронньй режим выполнения контрольной программы; обнаружено несравнение, по которому осуществляется последовательность окончания поиска адресов ошибок (j i) и (j + 1) процессоров;

X

XI

- момент обнаружения несравнения 20 яние, с последующей повторной уста- подключены многоканальные коммутаторы по ошибке и готовности соответственно -(j i) и (i j+2).процессоров.

Устройство работает следующим образом,

В асинхронном режиме функционирования процессоров 5.1, 5.2,...,, 5.п осуществляется периодическое поочередное выполнение контрольной программы i-M процессором с использованием аппаратных средств устройства. При поступлении сигнала Г; устанавливается в состояние 1 соответствующий триггер 26. готовности блока 4 управления, и на выходе элемента И 11, 12 формируются сигналы БТО: 1, , БПР О, осуществляющие соответственно разрешение через элементы групп элементов И и ИЛИ 19.2, 10,п, 9.п,8.п., 18.П и установку триггера 22. ошибки и блокирование выдачи сигнала прерывания с выходов элементов И группы 6.П в процессоры. Одновременно состояние 1 триггера 26. через элементы групп элементов

И и ИЛИ 12.2п, 20.п, устанавли-

вают.в 1 триггер 24. коммутациИ| сигнал с которого поступает в многоканальный коммутатор 1, подключающий сигналы (п i) процессора к схеме 2 сравнения и в (п i) процессор, по которому начинается выполнение контрольной программы. Сигналы с выходов схемы 2 сравнения, которая в асинхронном режиме выполняет функцию, аналогичную цифровому коммутатору, поступают через шифратор 3 в .регистр (п i) процессора, информация.которого

новкой в 1 триггера 22.п i .j, сигнал с которого через элементы групп элементов И и ИЛИ 7.р, 17.П-2, 6.П j+l формирует сигнал ПР i

25 j + 1 1, поступающий по схеме приоритета, определяемой формулой, в следующий по номеру функционирующий (i + 1) процессор, а также, через элементы групп элементов И и ИЛИ

30 7.р, 17.П-2, 19.1 формирует сигнал НПР 1, устанавливающий триггеры 23.1, 23.2 в 1 и через элемент И 13.П i j, 12.2n, 20.n устанавливает в 1 триггер 24.П i j. С

25 инверсных выходов триггеров 23.1 и 23.2 сигналы блокируют установку соответственно триггеров 22.п и- 24.п в 1 при поступлении сигналов ОШ- п в момент обработки прерывания (j +1) процессором. С прямого выхода триггера 23.1 сигнал через элемент И 11.5 включает счетчик 29 времени, циклически сбрасывающий в конце определенного интервала времени и вьщающий сигнал tO; 1, котооый чере з элементы И и ИЛИ I 1 .6,8, + .+1, 18.П устанавливает в 1 триггер i22.n j + 1 при отсутствии сигналов ОШ; j + 1, F j + 1.

При поступлении сигнала Offlj j+l от участвующего в обработке прерывания (j+l) процессора устанавливается через элементы 9.п j+l, IS.n в 1 триггер 22.п j+l, сигнал с которого через элементы групп элементов И и ИЛИ 7.р, 17.П-2, 6.П j+2 формирует сигнал ПР j + 2 1, поступающий в (j +2) процессор. При неуспешной обработке сигнала ПР. про40

45

50

55

становится доступной контрольной про- грамме. В определенные такты синхронизации информация регистра (п i) процессора сравнивается с набором эталонных констант программы и при успешном выполнении контрольной программы в устройство поступает сигнал сел., по которому триггеры блока 4

управления устанавливаются в исходное состояние.

При обнаружении непрограммируемой ошибки в блок 4 управления выдается сигнал ОШ ;, по которому в 1 ус- танавливается триггер 22.п i j, сигнал с которого через элементы И 16.п i и1.1.1 формирует сигнал СОК , j О; О, переключающий схемы блока 4 управления в исходное состоновкой в 1 триггера 22.п i .j, сигнал с которого через элементы групп элементов И и ИЛИ 7.р, 17.П-2, 6.П j+l формирует сигнал ПР i

5 j + 1 1, поступающий по схеме приоритета, определяемой формулой, в следующий по номеру функционирующий (i + 1) процессор, а также, через элементы групп элементов И и ИЛИ

0 7.р, 17.П-2, 19.1 формирует сигнал НПР 1, устанавливающий триггеры 23.1, 23.2 в 1 и через элемент И 13.П i j, 12.2n, 20.n устанавливает в 1 триггер 24.П i j. С

5 инверсных выходов триггеров 23.1 и 23.2 сигналы блокируют установку соответственно триггеров 22.п и- 24.п в 1 при поступлении сигналов ОШ- п в момент обработки прерывания (j +1) процессором. С прямого выхода триггера 23.1 сигнал через элемент И 11.5 включает счетчик 29 времени, циклически сбрасывающий в конце определенного интервала времени и вьщающий сигнал tO; 1, котооый чере з элементы И и ИЛИ I 1 .6,8, + .+1, 18.П устанавливает в 1 триггер i22.n j + 1 при отсутствии сигналов ОШ; j + 1, F j + 1.

При поступлении сигнала Offlj j+l от участвующего в обработке прерывания (j+l) процессора устанавливается через элементы 9.п j+l, IS.n в 1 триггер 22.п j+l, сигнал с которого через элементы групп элементов И и ИЛИ 7.р, 17.П-2, 6.П j+2 формирует сигнал ПР j + 2 1, поступающий в (j +2) процессор. При неуспешной обработке сигнала ПР. про0

5

0

5

цессорами триггеры 22.п устанавливаюся Е 1 и формируют сигналы (ТО; - ТО; п..„„ ), (ПР,-, - ПР;.пма«)

)

макс

которые через элементы 11.9, 19.1, 11.3 формируют сигнал IIIIj 1, устанавливающий в 1 триггер 23.3, состояние которого индицируется регистром 28 идентификации. При успешной обработке сигнала ПР j + 2 от (j +2) процессора поступает сигнал Г; J+2 1, устана:вливающий в Д триггер 26.п j + 2, сигнал с которого формирует сигналы BTOj БПР; О, КО Г,- J+2

Сигнал БПР; О через эле менты 11.5, 11.6.6.П соответственно сбрасывает значение счетчика 29 времени, блокирует вьщачу сигналов tO, и ПР;. Сигнал ВТО: 1 разрешает установку в лами ОШ: п

контрольной программы (j i), (j + +2) процессорами в синхронном режиме, который включается по сигналу KOj.r; J + 2 М.

1 Г 1

1 триггеров 22.п сигна 1, при выполнении

Таким образом, поступаюпще сигналы, ОШ; п 1 запоминаются и не прерывают выполнение контрольной программы, кроме сигнала ОШ| j+2 1, поступившего на (j +2) процессора. По сигналу ОШ; j + 2 1 выполняется последовательность переключений, аналогичная выполнен- ной по сигналу ОШ: i в асинхронном режиме выполнения контрольной программы и. обозначенной на временной диаграмме номером V. Сигналы КО; 1, Г; 1, KOjT; j+2 1 триггеров 24.п j i, 24.n i j+2 поступают в многоканальный коммутатор, подключающий сигналы .(j - i n), (n j+2) процессоров к схеме 2 сравнения, реализующей функцию сложения по модулю два одноименных сигналов, и производят включения (j i п), (j+2 n), процессоров в синхронный режим вьтолнения -контрольной программы.

При сравнении сигналов процессоров с выходом схемы 2 сравнения сигналы формируют сигнал ВСИ,-у 1. При несравнении с прямого выхода элемента И 11.14 сигнал BCH, j О поступает в (j i n) , (j+2 n) процессоры, из которых (j+2) процессор при программируемой ошибке не форьш- рует сигнал РБСИ; j+2 1. При

ся триггеры 24.п j+l,,24.n j+2, - по сигналам которых выполняется последовательность переключений, аналогичная выполненной при контроле (п j i) Процессора и обозначен- 30 нал на временной диаграмме номером VIII.

По окончании контроля процессоров с инверсных выходов, установленных в 1 триггеров 25.п, сигналы, равные значению О, запрещают по вхо35

дам элементов 13,п действие сигналов ТО: и через элементы 13.п,

11.10, 11.13, 11.11 формируют сигнал СОК;: О; О, устанавливаюш;ий триг- с выходов 40 геры блока 4 управления в О, кроме триггеров 25.п, установка в О которых осуществляется сигналом сел.С, О по окончании восстановления в работоспособное состояние процессоре ров, а также сигналы, равные значению 1, с прямых выходов триггеров 25.п j i 1, 25.п j + 1 1, 26.n j+2 1, через элементы 21.n j i, 15.n 3,2, 21.n j +1 формирует сигналы OK j i п 1, ОК„ jtl 1, OK;. j+2 n 1, блокирующие выдачу сигналов ОШ,| i 1, ОШ rt j+1 I. ИспоЛьзовйние в устройстве одновременного сравнения выходных сигналов процессоров при сравнительно минимальных аппаратных средствах увеличивает точность локализации неисправности, кроме того, процесс кон50

55

0

5

0

непрограммируемой ошибке сигнал ,РБСИ; J+2 1 через элементы 11.8, 11.7, 11.4 формирует сигналы СНОК-О,- О, yTnOj. .., по которым соответственно устанавливаются в О триггеры 23.2, 24.п и устанавливается через элемент 14.п j i триггер 25.п - j i памяти ошибки. При несравнении с выходов шифратора 3 сигналы адреса несрав- пившегося сигнала осуществляют асинхронную установку в 1 соответству- юш;ие разряды регистра 27.п j i индикации. Сигнал БК - 1 с выхода триггера 23.2 разрешает установку в 1 триггера 24.п J+1, а сигнал с инверсного выхода триггера 25.п j i запрещает установку в 1 триггера 24.п j i и блокирует изменение кода в регистре 27.п j i. По окончании действия сигнала СНОК;- Oj О формируется сигнал БСИ 1 и одновременно включают5

ся триггеры 24.п j+l,,24.n j+2, - по сигналам которых выполняется последовательность переключений, аналогичная выполненной при контроле (п j i) Процессора и обозначен- 0 нал на временной диаграмме номером VIII.

По окончании контроля процессоров с инверсных выходов, установленных в 1 триггеров 25.п, сигналы, равные значению О, запрещают по вхо35

дам элементов 13,п действие сигналов ТО: и через элементы 13.п,

11.10, 11.13, 11.11 формируют сигнал СОК;: О; О, устанавливаюш;ий триг- 40 геры блока 4 управления в О, кроме триггеров 25.п, установка в О которых осуществляется сигналом сел.С, О по окончании восстановления в работоспособное состояние процессоре ров, а также сигналы, равные значению 1, с прямых выходов триггеров 25.п j i 1, 25.п j + 1 1, 26.n j+2 1, через элементы 21.n j i, 15.n 3,2, 21.n j +1 формирует сигналы OK j i п 1, ОК„ jtl 1, OK;. j+2 n 1, блокирующие выдачу сигналов ОШ,| i 1, ОШ rt j+1 I. ИспоЛьзовйние в устройстве одновременного сравнения выходных сигналов процессоров при сравнительно минимальных аппаратных средствах увеличивает точность локализации неисправности, кроме того, процесс контроля автоматический и может быть ис пользован при отладке цифровых вы числительных машин.

Практически устройство реализуетс с применением интегральных микросхем сравнимых по быстродействию с интегральными микросхемами, применяемыми в процессорах.

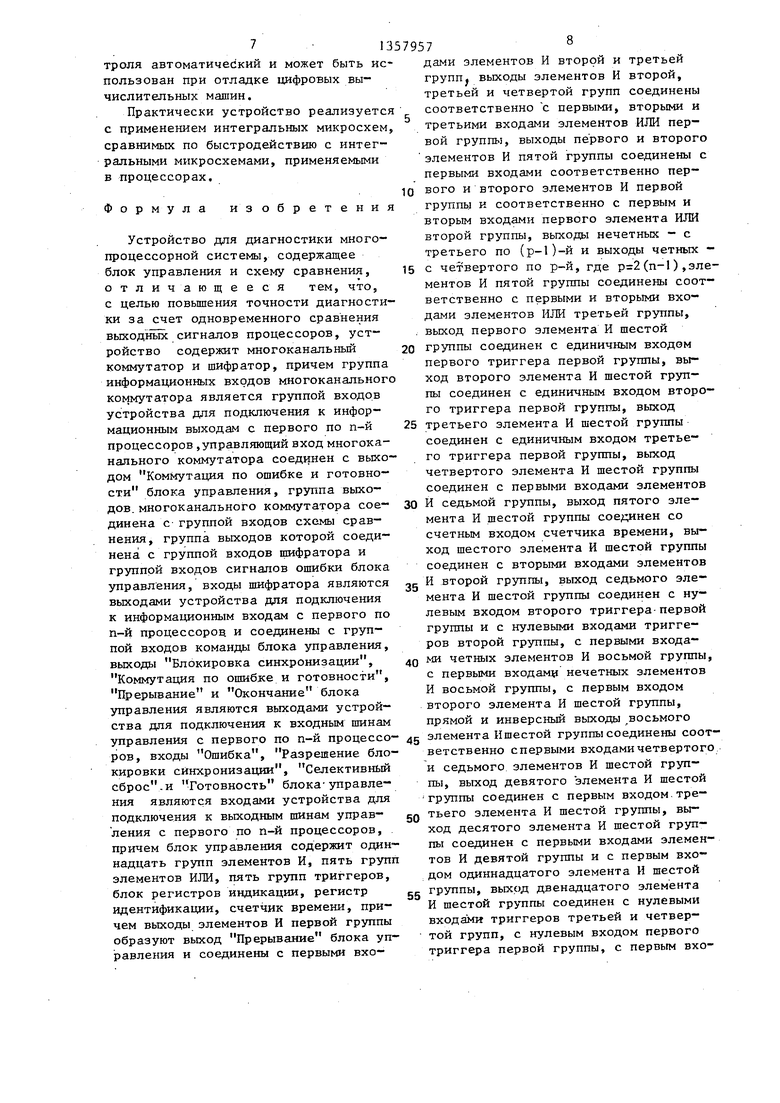

Формула изобретени

Устройство для диагностики многопроцессорной системы, содержащее блок управления и схему сравнения, отличающееся тем, что, с целью повьщ1ения точно-сти диагности ки за счет одновременного сравнения выходных сигналов процессоров, устройство содержит многоканальньш коммутатор и шифратор, причем группа информационных входов многоканальног коммутатора является группой входов устройства для подключения к информационным выходам с первого по п-й процессоров.управляющий вход многоканального коммутатора соединен с выходом Коммутация по ошибке и готовности блока управления, группа выходов, многоканального коммутатора соединена с-группой входов схемы сравнения, группа выходов которой соединена с группой входов шифратора и группой входов сигналов ощибки блока управления, входы шифратора являются выходами устройства для подключения к информационным входам с первого по п-и процессоров и соединены с группой входов команды блока управления, выходы Блокировка синхронизации, Коммутация по ошибке и готовности, Прерывание и Окончание блока управления являются выходами устройства для подключения к входным шинам

управления с первого по п-й процессо- 45 элемента И шестой группы соединены соот- ров, входы Ошибка, Разрешение бло- ветственно с первыми входами четвертого кировки синхронизации, Селективный и седьмого элементов И шестой группы, выход девятого элемента И шестой

сброс -И Готовность блока-управления являются входами устройства для подключения к выходным шинам управления с первого по п-й процессоров, причем блок управления содержит одиннадцать групп элементов И, пять групп элементов ИЛИ, пять групп триггеров, блок регистров индикации, регистр идентификации, счетчик времени, причем выходы элементов И первой группы образуют выход Прерывание блока управления и соединены с первыми вхо-

50

группы соединен с первым входом.третьего элемента И шестой группы, выход десятого элемента И шестой группы соединен с первыми входами элементов И девятой группы и с первым входом одиннадцатого элемента И шестой 55 группы, выход двенадцатого элемента И шестой группы соединен с нулевыми входами триггеров третьей и четвер- той групп, с нулевым входом первого триггера первой группы, с первым вхо0

5

0

дами элементов И второй и третьей групп выходы элементов И второй, третьей и четвертой групп соединены соответственно с первыми, вторьп {и и третьими входами элементов ИЛИ первой группь, выходы первого и второго элементов И пятой группы соединены с первыми входами соответственно первого и второго элементов И первой группы и соответственно с первым и вторым входами первого элемента ИЛИ второй группы, выходы нечетных - с третьего по (р-1)-й и выходы четных - с четвертого по р-й, где (п-1),элементов И пятой группы соединены соответственно с первыми и вторыми входами элементов ИЛИ третьей группы, выход первого элемента И шестой группы соединен с единичным входом первого триггера первой группы, выход второго элемента И шестой группы соединен с единичным входом второго триггера первой группы, выход

5 третьего элемента И шестой группы соединен с единичным входом третьего триггера первой группы, выход четвертого элемента И шестой группы соединен с первыми входами элементов

0 И седьмой группы, выход пятого элемента И шестой группы соединен со счетным входом счетчика времени, выход шестого элемента И шестой группы соединен с вторыми входами элементов И второй грзшпы, выход седьмого элемента И шестой группы соединен с нулевым входом второго триггера-первой группы и с нулевыми входами триггеров второй группы, с первыми входаQ ми четных элементов И восьмой группы, с первыми входаму нечетных элементов И восьмой группы, с первым входом второго элемента И шестой группы, прямой и инверсный выходы восьмого

5

группы соединен с первым входом.третьего элемента И шестой группы, выход десятого элемента И шестой группы соединен с первыми входами элементов И девятой группы и с первым входом одиннадцатого элемента И шестой группы, выход двенадцатого элемента И шестой группы соединен с нулевыми входами триггеров третьей и четвер- той групп, с нулевым входом первого триггера первой группы, с первым входом первого и вторыми входами четвер Torcv, седьмого элементов .И шестсэй труппы и с первыми вхЪдами элементов И четвертой группы, прямой выход три- надцаэ ого элемента И шестой группы соединен с вторыми входами элементов И первой группы и с первыми входами пятого, шестого элементов И шестой группы, инверсный выход тринадцатого элемента И шестой группы соединен с первым входом второго элемента ИЛИ второй группы и с вторым входом одиннадцатого элемента И шее™ той группы, инверсньй выход одиннадцатого элемента И шестой группы сое динен с первым входом двенадцатого элемента и. шестой группы, прямой выход четырнадцатого элемента И шестой группы является выходом блокировки синхронизации блока управления, инверсный выход четырнадцатого элемента И шестой группы соединен с первым входом восьмого элемента И шестой группы, выходы элементов И седьмой группы соединены с .единичны ги входами триггеров пятой группы, выходы четных и нечетных элементов ,И восьмой группы соединены соответственно с первыми-и вторыми входами элемен™ тов ИЛИ четвертой группы, выходы элементов И девятой группы соединены с Первыми входами элементов ИЛИ пятой

и

группы, прямые выходы элементов И десятой группы соединены с вторыми входами нечетных элементов И восьмой. Группы, инверсные выходы с первого по п-й элементов И девятой группы соединены соответственно с третьими входами с третьего по (2п-1)-й элементов И восьмой группы, с четверты ми входами с пятого по (2п-1)-й элементов И восьмой группы, с (п+1)-ми входами, начиная с 2п-1, элементов И восьмой группы, инверсные выходы элементов И одиннадцатой группы соединены с второго по (п+1)-й входами двеннадцатого элемента И шестой группы, выходы элементов ИЛИ первой группы соединены с единичными входами триггеров четвертой группы, прямой выход первого элемента ИЛИ второй группы соединен с вторыми входами первого и второго элементов И шестой

группы и с третьим входом одиннадца- gg той группы, прямые выходы триггеров

того элемента И шестой группы, инверсный выход первого элемента ИЛИ второй группы соединен с вторым входом третьего элемента И.шестой груп

пятой группы соединены с вторьми вхо дами элементов ИЛИ пятой группы и с информационными входами регистра идентификации, инверсные выходы триг

пы, выход второго элемента ИЛИ второй группы соединен с вторыми входами элементов И четвертой группы, выходы элементов ИЛИ третьей группы . соединены с первыми входами с третьего по п-й элементов И первой группы и с третьего по п-й входами первого элемента ИЛИ второй группы, выходы элементов ИЖ четвертой группы со- : единены с единичными входами триггеров второй группы, выходы элементов ИЛИ пятой группы образуют выход Окончание блока -управления, пря5 мой выход первого триггера первой группы соединен с вторыми входами пятого и шестого элементов И шестой группы, инверсный выход пер- , вого триггера первой группы соединен

0 с вторым входом второго элемента ИЛИ второй группы, инверсньй выход второго триггера первой группы соединен с третьим входом первого элемента И восьмой группы и с четвертыми входа5 ми нечетных элементов И восьмой группы, выход третьего триггера первой группы соединен с входом эаписи регистра идентификации., выходы триггеров второй группы соединены с вторы0 ми входами элементов И седьмой группы и образуют выход Коммутация по ошибке и готовности блока управлении, прямые выходы триггеров третьей группы соединены с первыми входами элементов И одиннадцатой и вторыми входами четных элементов И восьмой групп и с вторыми входами элементов И девятой группы, инверсные выходы триггеров третьей соединены 40 с входами тринадцатого элемента И шестой группы и с третьими входами элементов И седьмой группы, прямые выходы триггеров четвертой группы со,- единены с первыми входами элементов 45 И пятой группы и с (п-1)-ми входами четных элементов И пятой группы, с входами девятого элемента И шестой группы, с вторыми .входами элементов И одиннадцатой группы и с первыми gn входами элементов И десятой группы, инверсные выходы триггеров четвертой группы соединены с вторыми входами элементов И пятой группы и с (п-2)- ми входами нечетных элементов И пя35

той группы, прямые выходы триггеров

пятой группы соединены с вторьми входами элементов ИЛИ пятой группы и с информационными входами регистра идентификации, инверсные выходы триггеров пятой rpynnbi соединены с вторыми входами элементов И десятой группы и с блокировочными входами регистров индикации блока регистров индикации, входы Готовность, Разрешение блокировки синхронизации.и Ошибка блока управления соединены соответственно с единичными входами триггеров третьей группы, с вторым входом восьмого элемента И тестой группы, с вторыми и третьими входами элементов И соответственно третьей и четвертой групп, вход Селективный сброс блока управления соединен с нулевыми входами триггеров пятой

группы, с четвертыми входами элементов И седьмой группы, с (п+2)-м входом двенадцатого элемента И шестой группы и с нулевым входом третьего триггера первой группы, группа входов сигналов ошибки блока управления соединена с входами четырнадцатого элемента И шестой группы, группа входов команды блока управления соединена с информационными входами регистров индикации блока регистров индикации, выход счетчика времени соединен с третьим входом шестого элемента: И шестой группы.

фиг. 2

Фиг. 3

1357957 УСТРОЙСТЮ ДЛЯ ДИАГНОСТИКИ ЦИФРОЮЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ

./.

9 Асинхрон.

I /7СЖ. ПрОи,

Запрос на выполнение контрольной программы i-M процессором в асинхронном режиме

Формирование сигналов БПР| 0, , - выполнение

программы.

Анализ непрограммируемой ошибки 1-го процессора; при - переход к выполнению контрольной программы ijпроцессорами в синхронном режиме.

Запрос на выполнение контрольной программы ij-ми процессорами в синхронном режиме.

Формирование сигналов , КО;Г; 1 для j-ro процессора; устаТ

.11I tt

новка триггеров: 23, 23,1 24(, включение счетчика времени.

Анализ состояния триггера переполнения по ошибке J-X процессоров.

Обработка прерывания i-м процессором.

игЛ

Формирование сигналов: BIIPj 0, , для i-ro процессора, который переключается в синхронный режим для выполнения контрольной программы.

При - прерывание выдается в следующий работоспособный процессор.

Анализ - i-M процессором ошибки; РВСИ; 1 - означает наличие непрограммируемой ошибки.

Формирование сброса по несравнеиию и запоминание в 27п,28 - соответственно адресов ошибок и номеров процессоров.

Анализ наличия дополнительного запроса на контроль: При T0j.l - в контроле участвуют j+k - процессор и процессор - i; г ранее использовавшийся для контроля j-ro процессор

При ОК 1 - i-й процессор перек- ключается ,в асинхронный режим .

Составитель. И. Нестеренко Редактор М. Бланар . Техред Л.Сердюкова Корректор М, Шароши

.Заказ 6000/50Тира5к 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

(риг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| БОРТОВОЙ СПЕЦВЫЧИСЛИТЕЛЬ | 2013 |

|

RU2522852C1 |

| Устройство для согласования системных магистралей | 1989 |

|

SU1674143A1 |

| Устройство для обнаружения ошибок в блоках контроля процессора | 1980 |

|

SU903886A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1992 |

|

RU2066877C1 |

| ТЕПЛОВИЗОР НА ОСНОВЕ "СМОТРЯЩЕЙ" МАТРИЦЫ ФОРМАТА 256×256 | 2008 |

|

RU2382516C2 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для сопряжения двух электронных вычислительных машин (эвм) | 1984 |

|

SU1187172A1 |

| Устройство для отладки программ | 1988 |

|

SU1624461A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1596341A1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

Изобретение может быть использовано для автоматического обнаружения неисправности в цифровой вычислительной машине, состоящей не менее чем из двух процессоров. Целью изобретения является повьппение точности диагностики за счет одновременного сравнения выходных сигналов процессоров. Устройство для диагностики многопроцессорной системы содержит многоканальный коммутатор 1, осуществляющий подключение одноименных сигналов процессоров к схеме сравнения 2, шифратор 3, преобразующий результат сравнения в форму, приемлемую дпя последуюцей обработки процессорами, блок управления 4, осуществляющий приоритетное подключение процессоров в режим контроля, а также прием и выдачу сигналов синхронизации и управления, процессоры с первого 5.1 по п-й 5.п. 5 ил. (Л 00 СП Ч СО ел Фиг.1

| Многоканальное устройство для автоматического контроля микропроцессоров | 1982 |

|

SU1104519A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3921141, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1984-10-17—Подача