Уровень техники

Настоящее изобретение относится к способу и устройству для обработки операндов в процессоре, имеющем по меньшей мере два исполнительных блока, а также для переключения между по меньшей мере двумя режимами работы, и к соответствующему процессору.

Такие процессоры, имеющие по меньшей мере два интегрированных исполнительных блока, известны как процессоры двухядерной или многоядерной архитектуры. По состоянию техники на сегодняшний день двухядерная или многоядерная архитектура предлагается в основном по двум причинам.

Прежде всего, она позволяет добиться прироста производительности за счет того, что два исполнительных блока или ядра рассматриваются и функционируют как два отдельных вычислительных устройства на базе одного полупроводникового компонента. В этой конфигурации два исполнительных блока или ядра выполняют разные программы, решая соответствующие задачи. Тем самым достигается повышение производительности, и потому эту конфигурацию называют режимом повышенной производительности.

Кроме применения многоядерных процессоров в качестве суперскалярных процессоров, вторая причина в пользу реализации двухядерной или многоядерной архитектуры заключается в возможности повышения безопасности или степени достоверности результатов выполняемых процессором вычислений за счет того, что два исполнительных блока выполняют одну и ту же программу с избыточностью, дублируя друг друга. При этом результаты, выдаваемые обоими исполнительными блоками, сравниваются между собой, и по результатам сравнения их на соответствие друг другу можно выявить ошибку или отказ. Далее по тексту эта конфигурация называется безопасным режимом.

Вообще, две вышеназванные конфигурации в двухядерной или многоядерной архитектуре являются взаимоисключающими, т.е. вычислительное устройство, имеющее по меньшей мере два исполнительных блока, в принципе способно работать только в одном режиме, а именно в режиме повышенной производительности или в безопасном режиме.

В основу изобретения была положена задача обеспечить возможность функционирования такого двух- или многоядерного процессора в комбинированном режиме, т.е. с комбинированием по меньшей мере двух режимов, и при этом достичь оптимизированной стратегии переключения режимов, в частности переключения между безопасным режимом, обеспечивающим повышенную степень достоверности результатов вычислений, и режимом повышенной производительности, обеспечивающим повышенную производительность процессора.

Преимущества изобретения

К подобным процессорам предъявляются во многом противоречивые требования: с одной стороны, из соображений безопасности желательно обеспечить избыточность или дублирование при обработке операндов или выполнении программ и соответствующих задач, а с другой стороны, при выполнении функций, не являющихся критичными с точки зрения безопасности, держать в наличии дублирующие аппаратные средства экономически нерационально. В соответствии с изобретением вышеуказанное противоречие разрешается за счет оптимизированного переключения между по меньшей мере двумя режимами работы процессора.

Итак, объектами изобретения являются способ и устройство для обработки операндов в процессоре, имеющем по меньшей мере два исполнительных блока, работающих на заданной тактовой частоте (т.е. с заданным машинным тактом), причем управление исполнительными блоками при обработке операндов осуществляется посредством управляющих сигналов, предусмотрена возможность переключения между первым и вторым режимами работы, и для решения поставленной задачи в соответствии с изобретением при работе в первом режиме в два исполнительных блока подают одинаковые операнды, а при работе во втором режиме в эти два исполнительных блока подают разные операнды, причем управление исполнительными блоками при обработке операндов в первом режиме осуществляют посредством одинаковых управляющих сигналов, а во втором режиме - посредством разных управляющих сигналов.

При этом в предпочтительном варианте осуществления настоящего изобретения подачу операндов в исполнительные блоки при работе в первом режиме осуществляют в зависимости от тактовой частоты исполнительных блоков, используемой в качестве номинальной тактовой частоты (т.е. частоты при полном машинном такте), а при работе во втором режиме подачу операндов на обработку осуществляют на второй тактовой частоте, более высокой, или "ускоренной", по сравнению с номинальной.

Предпочтительно, чтобы тактовая частота, на которой работают оба исполнительных блока, и вышеуказанная номинальная тактовая частота выбирались одинаковыми, причем в одном из частных вариантов осуществления изобретения вторая, более высокая, тактовая частота вдвое превышает номинальную, выступая в качестве удвоенной тактовой частоты (т.е. частоты при машинном полутакте).

В предпочтительном варианте осуществления настоящего изобретения происходит обработка в обоих режимах работы, обработку операндов исполнительными блоками ведут синхронно, хотя изобретением допускается, например, синхронная обработка операндов в первом режиме и асинхронная - во втором.

По соображениям безопасности операнды или производные от них данные, например сформированные на основе операндов коды с исправлением ошибок (ЕСС-коды, сокр. от англ. "Error Correction Code"), могут сравниваться между собой на предмет их соответствия друг другу, и при их несоответствии можно сделать вывод о наличии ошибки. Точно так же состояния, возникающие при обработке операндов, например производные данные в форме кодов с исправлением ошибок, или результаты обработки операндов могут сравниваться между собой на предмет их соответствия друг другу, причем и в этом случае при их несоответствии делают вывод о наличии ошибки. В обоих случаях операции сравнения могут выполняться или не выполняться в зависимости от конкретного режима работы процессора, причем от режима работы процессора может зависеть и то, какие операнды, данные, состояния или результаты проверяются на предмет идентичности путем сравнения.

Затем дальнейшую обработку состояний, возникающих при обработке операндов, или результатов такой обработки перед их записью в шину разрешают посредством разрешающего сигнала в зависимости от режима работы и результатов сравнения, в результате чего такое "высвобождение" состояний, возникающих при обработке операндов, или результатов такой обработки происходит одновременно или последовательно.

Предлагаемое в настоящем изобретении устройство или содержащий его процессор помимо по меньшей мере двух исполнительных блоков, работающих на заданной тактовой частоте, содержит блок управления, который, выступая, в частности, в качестве переключательного устройства, переключает процессор между первым и вторым режимами работы и управляет исполнительными блоками при обработке операндов посредством управляющих сигналов, причем этот блок управления связан с исполнительными блоками, а также с дополнительными блоками подачи, или ввода, операндов и взаимодействует с блоками подачи операндов таким образом, чтобы при работе в первом режиме подавать в два исполнительных блока одинаковые операнды, а при работе во втором режиме подавать в эти два исполнительных блока разные операнды, причем блок управления выполнен с возможностью управления обоими исполнительными блоками при обработке операндов в первом режиме посредством одинаковых управляющих сигналов, а во втором режиме - посредством разных управляющих сигналов.

При этом в предпочтительном варианте осуществления настоящего изобретения блок управления и блоки подачи операндов выполнены таким образом, чтобы при работе в первом режиме подавать операнды на обработку в исполнительные блоки в зависимости от тактовой частоты работы исполнительных блоков, используемой в качестве номинальной тактовой частоты, а при работе во втором режиме подавать операнды на обработку со второй тактовой частотой, более высокой по сравнению с номинальной.

При этом два исполнительных блока могут быть выполнены просто в виде вычислительных, или арифметико-логических, устройств (АЛУ) или же в виде ядра процессора, либо в виде целого процессора (ЦПУ). В соответствии с этим настоящее изобретение предпочтительно применимо ко всем подобным по меньшей мере двукратно продублированным компонентам, способным осуществлять соответствующую изобретению обработку операндов, соответственно способным выступать в качестве соответствующих изобретению исполнительных блоков процессора.

Блоки подачи операндов могут быть выполнены в виде набора регистров таким образом, чтобы был предусмотрен по меньшей мере один регистр операнда, а между регистром операнда и каждым исполнительным блоком был предусмотрен по меньшей мере один промежуточный регистр, причем блоки подачи операндов и исполнительные блоки выполнены таким образом, чтобы во втором режиме, представляющем собой режим повышенной производительности, работать с разными тактовыми частотами, и в частности, блоки подачи операндов выполнены с возможностью их работы во втором режиме с тактовой частотой, более высокой, в частности удвоенной, по сравнению с тактовой частотой, на которой работают исполнительные блоки.

В предпочтительном варианте осуществления настоящего изобретения может быть предусмотрен декодер, позволяющий распознавать условие переключения режимов и работающий с той же тактовой частотой, что и блок подачи операндов.

При этом дополнительно могут быть предусмотрены первые переключательные средства, выполненные с возможностью управления средствами подачи операндов в зависимости от первого или второго режима работы процессора, и/или вторые переключательные средства, выполненные с возможностью управления исполнительными блоками в зависимости от первого или второго режима работы процессора.

Целесообразно выполнять блоки подачи операндов и исполнительные блоки с возможностью их работы с одной и той же тактовой частотой, прежде всего с возможностью их синхронной работы при работе предлагаемого в изобретении устройства в первом, безопасном, режиме.

Иные преимущества и предпочтительные варианты осуществления изобретения рассмотрены в описании, а также указаны в признаках формулы изобретения.

Чертежи

Ниже изобретение более подробно пояснено со ссылкой на прилагаемые чертежи, на которых показано:

на фиг.1 и 2 - процессор с двумя одинаковыми АЛУ и с набором регистров, имеющим по одному регистру операнда и по одному промежуточному регистру,

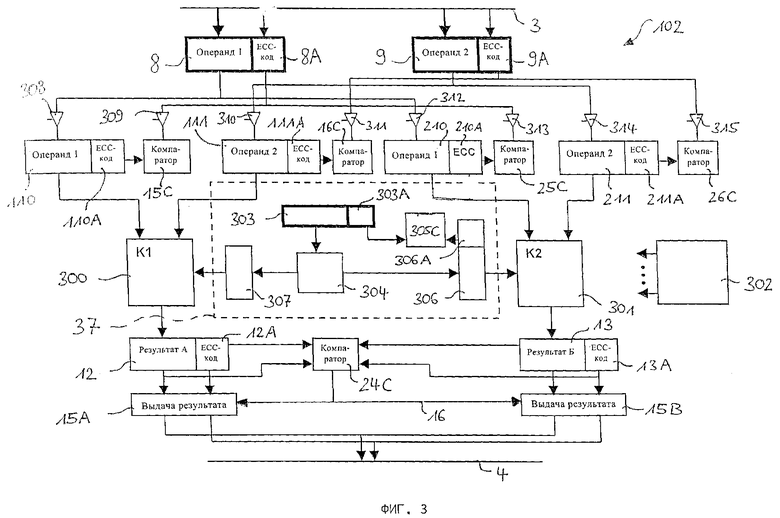

на фиг.3 - аналогичный процессор с двумя одинаковыми АЛУ и с набором регистров, отличным от показанного на фиг.1 и 2 тем, что он имеет по две пары регистров операнда на каждое АЛУ и соответствующее количество промежуточных регистров,

на фиг.4 - различные такты, используемые для подачи и обработки операндов, в частности полный такт (при номинальной тактовой частоте) и полутакт (при удвоенной тактовой частоте),

на фиг.5 - еще один вариант выполнения процессорного блока с двумя одинаковыми АЛУ, отличающийся от показанного на фиг.3 наличием лишь одного входа для подачи операндов, соответственно наличием у набора регистров лишь одного регистра операнда.

Описание вариантов осуществления изобретения

Если не указано иного, на фиг.1, 2, 3 и 5 одинаковые и/или выполняющие одинаковые функции элементы обозначены одинаковыми позициями.

Для упрощения на фиг.1 и 2 не показаны или не показаны подробно не существенные в контексте настоящего изобретения компоненты процессора, такие как модули памяти, периферийные устройства, а также остальные ядра или ЦПУ. Однако, как указано ниже со ссылкой на фиг.3 и 5, оба соответствующих изобретению АЛУ А и Б могут представлять собой устройства для выполнения операций с плавающей точкой, целые процессорные ядра или даже целые процессоры, иными словами настоящее изобретение применимо в том числе и к полнофункциональным двухядерным архитектурам. Тем не менее, предпочтительными являются варианты осуществления изобретения, показанные на фиг.1 и 2, поскольку ими предусматривается дублирование лишь самих АЛУ, в то время как для защиты других компонентов процессора могут использоваться иные механизмы выявления ошибок.

На фиг.1 и 2 показаны исполнительные блоки 1 и 2, каждый из которых может представлять собой АЛУ или устройство для выполнения операций с плавающей точкой (встроенный сопроцессор). В показанных на указанных чертежах вариантах осуществления настоящего изобретения из всех компонентов процессора избыточное исполнение имеет лишь само АЛУ. Каждое такое АЛУ 1, 2 имеет два входа и один выход. В режиме проверки подлежащие обработке операнды могут поступать во входы АЛУ 1, 2 непосредственно по шине 3, однако в другом варианте они могут предварительно сохраняться в специально отведенном для этой цели регистре 8, 9 операнда. Эти регистры 8, 9 операндов непосредственно соединены с шиной 3 данных. Иными словами, подлежащие обработке операнды поступают в оба АЛУ 1, 2 из одинаковых регистров 8, 9 операндов. В дополнение к этому для передачи по шине соответствующие операнды могут защищаться посредством кода с исправлением ошибок, который сохраняется в областях 8А, 9А соответствующих регистров. Иными словами, все данные, хранящиеся во всех показанных на фиг.1 и 2 (а также, как более подробно пояснено ниже, на фиг.3 и 5) регистрах операндов, имеющих обозначенные на чертежах области для хранения кода с исправлением ошибок, могут быть защищены посредством указанного кода.

Известны многочисленные методы выявления возникающих в данных ошибок, причем основной предпосылкой для применения этих методов является предварительная защита таких данных при помощи кода с обнаружением ошибок или кода с исправлением ошибок, иными словами, при помощи цифровой подписи. В простейшем случае такая подпись может иметь лишь один бит, например бит контроля четности. Однако защита хранимых в памяти данных может быть реализована и с использованием более сложных кодов с обнаружением ошибок (ED-коды, сокр. от англ. "Error Detection"), например кода Бергера или Бозе-Лина (Bose-Lin), или же с использованием еще более сложного кода с исправлением ошибок, например кода Хэмминга, или других подобных кодов, за счет увеличения количества используемых битов, обеспечивающих более высокую степень надежности обнаружения ошибок. В другом варианте может быть предусмотрено и использование генератора кода, например табличного (аппаратного или программного) генератора, позволяющего присваивать определенным последовательностям битов, записываемым в адресуемую ячейку памяти, определенные последовательности-подписи" любой длины. Такой подход позволяет обеспечить высокую степень защиты целостности данных путем надежного исправления возникающих в данных ошибок. Несмотря на все доступные возможности исправления возникающих ошибок при работе процессора в безопасном режиме, наиболее важном с точки зрения безопасности, в соответствии с изобретением предусмотрена обработка программ, критичных с точки зрения безопасности, с избыточностью или дублированием обоими исполнительными блоками, которые в рассматриваемом конкретном варианте осуществления изобретения выполнены в виде обоих АЛУ 1 и 2, причем возникающие при такой обработке ошибки обнаруживаются в соответствии с изобретением путем сравнения выдаваемых обоими АЛУ результатов обработки между собой на предмет их соответствия. В приведенном ниже описании для упрощения не делается различий между различными известными кодами с исправлением ошибок, причем все эти коды обобщенно называются кодами с исправлением ошибок.

Для ускорения обработки несущественные или некритичные с точки зрения безопасности программы или задачи, соответственно части программ, блоки программного кода или отдельные команды могут обрабатываться обоими исполнительными блоками распределенным образом, что позволяет увеличить скорость обработки, а тем самым и производительность. Такая обработка осуществляется в так называемом режиме повышенной производительности.

При подаче в АЛУ 1, 2 подлежащих обработке операндов важно обеспечить корректность обрабатываемых исходных данных. При подаче в оба АЛУ 1, 2 на обработку одинаково некорректных операндов обнаружить ошибку путем анализа выдаваемых на выход АЛУ 1, 2 результатов обработки невозможно. В соответствии с этим для того, чтобы в соответствии с изобретением не допустить получения недостоверных результатов обработки операндов в безопасном режиме, необходимо либо гарантировать подачу корректных исходных данных по меньшей мере в одно из АЛУ 1 или 2, либо по меньшей мере обеспечить неодинаковость подаваемых в оба АЛУ 1, 2 некорректных исходных данных. Это обеспечивается за счет формирования контрольной суммы по меньшей мере для одного из подаваемых в АЛУ 1, 2 двух блоков исходных данных, иными словами за счет применения по меньшей мере к одному из них вышеописанного кода с исправлением ошибок. В компараторе 5С, 6С, предусмотренном на входе предлагаемого в изобретении устройства, код 10А, 11А с исправлением ошибок, содержащийся в дополнительных регистрах данных или промежуточных регистрах 10, 11, сравнивается с кодом 8А, 9А с исправлением ошибок, содержащимся в исходном регистре 8, 9. Сами исходные данные, содержащиеся в регистрах 10, 11, также могут необязательно сравниваться с данными, содержащимися в исходных регистрах 8, 9. Обнаружение взаимного несоответствия сравниваемых кодов с исправлением ошибок, соответственно операндов, рассматривается как признак наличия ошибки, в ответ на которую может выдаваться сигнал об ошибке, причем при определенных условиях может также выдаваться сообщение об ошибке, и при определенных условиях обнаруженная ошибка может исправляться. Указанное сравнение предпочтительно осуществляется во время обработки операндов в АЛУ 1, 2, что позволяет осуществлять процедуру обнаружения и исправления ошибок в исходных данных практически без снижения производительности. В случае регистрации компараторами 5С, 6С ошибки соответствующее вычисление осуществляется повторно на следующем цикле. При этом может использоваться буферный регистр, сохраняющий обрабатываемые операнды до начала обработки следующих операндов и тем самым ускоряющий доступ к ним в случае необходимости их повторной обработки. Однако применение такого буферного регистра является излишним в том случае, когда содержимое соответствующих промежуточных регистров 10, 11 перезаписывается новыми/следующими исходными данными лишь после получения разрешающего сигнала, свидетельствующего об отсутствии ошибок в процессе обработки этих данных. В случае же обнаружения ошибки компараторами 5С, 6С выдается сигнал об ошибке, препятствующий перезаписи содержимого промежуточных регистров 10, 11 новыми исходными данными.

Полученные результаты вычислений выдаются АЛУ 1, 2 на их соответствующие выходы. Выдаваемые АЛУ 1, 2 результаты и/или относящиеся к ним коды с исправлением ошибок сохраняются в регистрах 12, 13, 12А, 13А результатов. Эти результаты и/или относящиеся к ним коды сравниваются между собой в компараторе 14С, 24С. При отсутствии ошибки формируется разрешающий сигнал 16. Этот разрешающий сигнал 16 подается в разрешающее устройство 15, которое при получении этого сигнала передает результаты вычислений по шине 4. По этой шине 4 результаты передаются для дальнейшей обработки.

Разрешающий сигнал 16 может использоваться в том числе и для открытия регистров 8-11 для записи в них новых исходных данных, соответственно для подготовки к получению по шине 3 следующих подлежащих обработке АЛУ 1, 2 операндов.

Показанное на фиг.1 устройство не имеет средств для проверки результата как такового. Оно лишь посредством компаратора 14С сравнивает между собой результаты вычислений, выдаваемые обоими АЛУ. Проверка относящихся к результатам вычислений кодов с исправлением ошибок возможна лишь в устройстве, показанном на фиг.2 и способном посредством компаратора 24С сравнивать между собой как сами результаты, так и относящиеся к ним коды с исправлением ошибок.

Средства обнаружения ошибок, предусмотренные в показанных на фиг.1 и 2 вариантах выполнения предлагаемого в изобретении устройства, способны обнаруживать все перемежающиеся ошибки, систематические ошибки и ошибки, возникающие во время выполнения программ. Ошибки, возникающие в АЛУ 1, 2 во время выполнения программ, обнаруживаются за счет того, что при непоступлении или слишком позднем поступлении одного из результатов в соответствующий компаратор и/или регистр результата в контрольном сравнении участвует в лучшем случае лишь часть "запоздавшего" результата. Использование для защиты данных, хранящихся в регистрах операндов и промежуточных регистрах 8, 9, 10, 11, кода с исправлением ошибок, а также сравнение конечных результатов позволяет точно установить место и время возникновения ошибки. Такой подход позволяет весьма оперативно реагировать на случайные ошибки.

Предлагаемое в изобретении устройство делает возможным следующие подходы к локализации ошибок:

Расхождение, выявленное при осуществляемом в компараторах 14С или 24С сравнении данных, относящихся к результатам вычислений, является признаком ошибки, возникшей в АЛУ 1, 2.

Расхождение, выявленное при осуществляемом в компараторах 5С, 6С сравнении кодов с исправлением ошибок, является признаком ошибки в сигнале, поступившем по шине 3, соответственно ошибки, возникшей в одном из компонентов, от которых предлагаемое в изобретении устройство получает подлежащие обработке операнды.

Расхождение, выявленное при осуществляемом в компараторе 24С сравнении кодов с исправлением ошибок, является признаком ошибки в процессе кодирования результата.

Для переключения между указанным безопасным режимом, в котором осуществляется избыточная обработка и проверка, и режимом повышенной производительности, в котором за счет раздельного выполнения программ достигается повышение производительности, предусмотрен блок 17 управления, выполняющий прежде всего функцию переключательного устройства. Такое переключательное устройство 17 переключает по меньшей мере элементы 8, 9 и 1, 2 таким образом, чтобы в одном случае, иными словами при работе процессора в безопасном режиме, осуществлялось избыточное, прежде всего синхронное выполнение программ, а при работе во втором режиме, иными словами при работе процессора в режиме повышенной производительности, могла осуществляться параллельная обработка различных программ, соответственно операндов. С этой целью могут быть предусмотрены необязательные переключатели (коммутаторы) или переключательные средства, которые могут, например, располагаться в элементах 8, 9, соответственно 1, 2, или же в переключательном устройстве, соответственно блоке 17 управления, или же могут представлять собой дополнительные, отдельные от элементов 8, 9, 1, 2 соответственно 17 схемные элементы.

В целях такого переключения программы прикладные программы или части программ, иными словами блоки программного кода или даже отдельные команды и операнды, могут, например, маркироваться путем присвоения им идентификаторов, которые характеризуют их либо как подлежащие выполнению в безопасном режиме, либо как подлежащие выполнению в режиме повышенной производительности, и на основании которых они выполняются в том или ином режиме. Такой идентификатор может иметь по меньшей мере один бит, или же в качестве идентификатора режима обработки целой последовательности может использоваться встречающаяся в начале этой последовательности особая команда. Переключение может осуществляться и путем доступа к ячейке памяти с определенным заданным адресом, иными словами переключение в режим повышенной производительности или в безопасный режим может инициироваться обращением к соответствующему заданному адресу ячейки памяти.

При этом, с одной стороны, процессор может переключаться из одного режима в другой для выполнения, например, прикладных функций той или иной программы, прежде всего функций управления происходящими в автомобиле рабочими процессами, однако переключение может осуществляться и для выполнения в заданном режиме отдельных элементов операционной системы, которые также могут иметь идентификаторы, позволяющие, например, соотносить отдельные процессы самой операционной системы с тем или иным режимом.

Путем оценки вышеуказанных идентификаторов блок 17 управления, выполняющий функцию переключательного устройства, определяет, является ли следующее вычисление важным с точки зрения безопасности, иными словами следует ли для его выполнения переключаться в безопасный режим или нет. В случае, когда вычисление подлежит выполнению в безопасном режиме, соответствующие исходные данные передаются в оба исполнительных блока 1 и 2. В случае, когда вычисление может выполняться в текущем режиме повышенной производительности, соответствующие исходные данные передаются в один из исполнительных блоков, и одновременно с этим во второй исполнительный блок передаются данные для другого вычисления, при наличии таких данных и при условии, что это другое вычисление также не является важным с точки зрения безопасности.

В первом случае, когда операнды подлежат обработке в безопасном режиме, синхронное осуществление обоими исполнительными блоками соответствующих вычислений, соответственно получение результата таких вычислений, занимают/-ет одинаковое время. Таким образом, при осуществляемой в безопасном режиме синхронной обработке результаты обработки выдаются одновременно. Полученные в результате обработки и выданные на выход 12, соответственно 13 результаты защищаются посредством кода, после чего эти результаты (обозначенные на указанных чертежах как "результат А" и "результат Б") и/или относящиеся к ним коды поясненным со ссылками на фиг.1 и 2 образом сравниваются между собой. При их совпадении выдается разрешение на дальнейшую обработку соответствующих данных, в противном случае следует одна из ранее упоминавшихся реакций на возникновение ошибки. Во втором случае, иными словами в режиме повышенной производительности, в котором данные обрабатываются распределенно, предусмотренный на выходах обоих АЛУ компаратор 14С, соответственно 24С, не используется, и результаты "результат А" и "результат Б" последовательно записываются в регистры памяти, из которых могут так же последовательно выдаваться для их дальнейшей обработки, как это обычно происходит в суперскалярных процессорах.

Поскольку в безопасном режиме одни и те же программы выполняются параллельно, иными словами с избыточностью, переключение осуществляется только в том случае, когда о необходимости такого переключения свидетельствуют идентификаторы обоих "потоков данных", иными словами как данных, поступающих в АЛУ 1 из регистра 8, так и данных, поступающих в АЛУ 2 из регистра 9. При полностью синхронной, иными словами одновременной обработке программы иного и не возможно, однако при асинхронной обработке программы исполнительному блоку, который первый закончил вычисление, приходится ждать завершения вычислений вторым исполнительным блоком, и лишь после этого, иными словами только при наличии обоих идентификаторов, соответственно после обработки последних, блок 17 управления может переключить процессор в другой режим. Аналогичным образом и осуществляемое блоками 12, 13 и 14С, 24С, а также 12А и 13А сравнение между собой результатов и/или кодов с коррекцией ошибок должно осуществляться либо также синхронно, либо должны быть предусмотрены обеспечивающие синхронность задержки.

На фиг.3 приведено схематичное изображение процессора с двумя исполнительными блоками, функцию которых выполняют изображенные на чертеже компоненты К1 (поз.300) и К2 (поз.301). В отличие от показанных на фиг.1 и 2 АЛУ каждый из этих компонентов может представлять собой, например, самостоятельное ядро процессора или целый процессор. Каждый из двух компонентов К1 и К2 также имеет два входа и один выход. И в рассматриваемом варианте подлежащие обработке операнды могут либо поступать на входы компонентов непосредственно по шине 3, либо предварительно сохраняться в предназначенных для этого регистрах 8 и 9 операндов. Используемые в этом варианте осуществления изобретения принципы работы регистров 8 и 9 операндов и их защиты посредством соответствующих кодов с исправлением ошибок сравнимы с поясненными выше со ссылкой на фиг.1 и 2 и применимы в том числе и в рассматриваемом варианте. В принципе сказанное относится и к показанным на фиг.3 выходным регистрам 110, 111, 210, 211 данных, необязательно имеющим области 110А, 111А, 210А, 211А для хранения кодов с коррекцией ошибок. Однако отличие рассматриваемого варианта осуществления изобретения от поясненных со ссылкой на фиг.1 и 2 заключается в том, что в рассматриваемом варианте на входе каждого из компонентов предусмотрено по две пары промежуточных регистров. Как упоминалось со ссылкой на фиг.1 и 2, для обнаружения ошибок на стадии подачи операндов, иными словами ошибок в исходных данных, используется метод формирования контрольных сумм (код с исправлением ошибок). В рассматриваемом случае для обнаружения ошибок применяются аналогичные показанным на фиг.1 и 2 компараторы 15С, 16С, 25С и 26С, количество которых соответствует количеству подлежащих сравнению регистров. В случае выявления путем сравнения взаимного несоответствия кодов с исправлением ошибок, соответственно операндов, такое несоответствие позволяет сделать вывод о наличии ошибки с выдачей сигнала об ошибке, сохранением информации об ошибке, индикацией наличия ошибки и принятием зависящих от конкретной ошибки ответных мер, которые могут заключаться прежде всего в переключении в аварийный режим работы или в исправлении ошибки. И в рассматриваемом варианте осуществления изобретения, по аналогии с описанным со ссылкой фиг.1 и 2, при обнаружении ошибки соответствующее вычисление выполняется повторно на следующем такте / цикле, причем и в рассматриваемом варианте может применяться буферный регистр.

Результаты или состояния "результат А" или результат "Б", полученные путем обработки операндов, описанным со ссылкой на фиг.2, контролируются путем их сравнения между собой (причем необязательно сравниваются в том числе и коды с исправлением ошибок), и по результатам сравнения делается заключение о наличии или отсутствии ошибок. По аналогии с вариантом осуществления изобретения, рассмотренным со ссылкой на фиг.2, для этого применяются регистры 12 и 13 с областями памяти 12А и 13А, предназначенными для хранения кодов с исправлением ошибок, а также компаратор 24С. В отличие от варианта, рассмотренного со ссылкой на фиг.2, в рассматриваемом варианте осуществления изобретения используются два разрешающих устройства 15А и 15В, которые посредством разрешающего сигнала 16 разрешают передачу результатов вычислений по шине 4.

На фиг.3 изображены соответствующие изобретению элементы процессора 102, причем ниже более подробно пояснен принцип работы блока управления, обозначенного на указанном чертеже позицией 302. При этом для упрощения выходы этого блока обозначены на этом чертеже лишь схематично, стрелками, направленными от блока 302 управления, причем посредством этих выходов блок 302 управления управляет работой первых переключательных средств 308-315, схемы 37 управления, соответственно ее компонентов, необязательно регистров 8 и 9 операндов и также необязательно промежуточных регистров 110, 111 и 210, 211.

И в рассматриваемом случае блок 302 управления выполняет в определенном смысле функцию переключения, переключая процессор из одного режима работы в другой. Под переключением процессора из одного режима работы в другой понимается прежде всего переключение его из безопасного режима работы в режим повышенной производительности, причем переключение в каждый режим осуществляется, например, посредством специально предназначенных для переключения в этот конкретный режим управляющих сигналов.

В соответствии с этим в зависимости от наличия необходимого для переключения условия, поясненного выше со ссылкой на фиг.1 и 2, в зависимости от распознанного режима осуществляется управление работой вышеуказанных элементов. При этом схема 37 управления имеет декодер 303, второе переключательное средство 304, а также необязательно два регистра или две схемы 307 и 306 с фиксацией состояния. И в рассматриваемом случае по соображениям безопасности компаратором 305С может осуществляться сравнение кодов с исправлением ошибок, хранящихся в соотнесенной с декодером области 303А памяти и в относящейся к регистру 306 области 306А памяти. Схема 37 управления или ее компоненты могут быть размещены в блоке 302 управления, соответственно могут быть идентичными с последним.

При применении в качестве условия для переключения, по аналогии с приведенным выше со ссылкой на фиг.1 и 2 описанием, идентификатора или заданного адреса ячейки памяти блок управления может по соответствующему условию определить, является ли следующее вычисление важным с точки зрения безопасности или нет. В таком случае, иными словами при необходимости осуществить обработку операндов в безопасном режиме работы процессора, в оба исполнительных блока 300 и 301 передаются одинаковые операнды, в рассматриваемом случае операнды "операнд 1" и "операнд 2". При этом необходимое для обработки операндов управление исполнительными блоками осуществляется посредством одинаковых управляющих сигналов. Процесс подачи операндов в исполнительные блоки и тактовая частота, с которой осуществляется обработка операндов этими блоками, согласованы друг с другом. В предпочтительном варианте осуществления изобретения блоки подачи операндов (иными словами, по меньшей мере регистры 8 и 9 операндов) и исполнительные блоки, а также декодер 303 работают с одинаковой тактовой частотой, иными словами синхронно. Прежде всего синхронно друг с другом работают компоненты первой части процессора, а именно блок подачи операндов с регистром 8 операндов и исполнительный блок 300, а также синхронно друг с другом работают компоненты второй части процессора, а именно блок подачи операндов с регистром 9 операндов и исполнительный блок 301. В предпочтительном варианте осуществления изобретения обе указанные части процессора работают еще и синхронно друг с другом, что позволяет при работе процессора в безопасном режиме осуществлять синхронную обработку операндов, при которой обе части процессора могут одновременно выдавать в регистры 12, соответственно 13, результаты "результат А", соответственно "результат Б" обработки или соответствующие состояния.

В соответствии с этим соответствующий блок подачи операндов имеет по меньшей мере соответствующий регистр 8 или 9 операндов. Помимо этого в зависимости от конкретного варианта осуществления изобретения в блоке подачи операндов может быть предусмотрен по меньшей мере один промежуточный регистр, обозначенный на фиг.1 или 2 поз.10 или 11, соответственно на фиг.3 поз.110, 111 или 210, 211. В блоке подачи операндов могут также предусматриваться первые переключательные средства, способные осуществлять переключения с учетом тактовой частоты, с которой обрабатываются операнды. Эти первые переключательные средства 308, 310, 312, 314 могут быть либо отдельными, как показано на фиг.3, либо встроенными по меньшей мере в один соответствующий регистр (регистр 8 или 9 операндов или соответствующий промежуточный регистр 10 или 11, 110, 111, 210, 211). В зависимости от того, применяется ли код с исправлением ошибок, соответствующие области (10А, 11А по фиг.1 и 2 или 110А, 111А, 211А по фиг.3), а также соответствующие компараторы (5С, 6С по фиг.1 и 2, а также 15С, 16С, 25С, 26С по фиг.3) могут необязательно быть встроены в соответствующий блок подачи операндов. Это относится и к первым переключательным средствам в рамках кода (поз.309, 311, 313, 315 по фиг.3), иными словами и эти средства могут необязательно быть встроены в соответствующий блок подачи операндов либо также могут быть выполнены отдельными или встроенными в один из соответствующих регистров (в предназначенную для хранения кода с исправлением ошибок область 8А или 9А регистра операнда, соответственно в соответствующий промежуточный регистр 10А или 11А, 110А, 111А, 210А, 211А). В соответствии с этим отдельные блоки подачи операндов соответствуют отдельным элементам схемы, обеспечивающей подачу операндов в исполнительные блоки, причем может применяться либо одна из схем, показанных на фиг.1, 2, 3 или 5, или же некоторые, соответственно все компоненты могут быть интегрированы в единый схемный элемент.

В случае, когда результаты или состояния осуществляемой в безопасном режиме, иными словами при работе в первом режиме процессора обработки операндов, выдаются одновременно, на выходе, при их сохранении в соответствующие регистры 12 и 13, они могут защищаться посредством кода с исправлением ошибок, сохраняемого в соответствующие области 12А и 13А этих регистров, после чего результаты, соответственно состояния "результат А" и "результат Б", обработки этих операндов и/или соответствующие им коды с исправлением ошибок сравниваются между собой. Сравнение осуществляется компаратором 24С. При выявлении идентичности посредством разрешающего сигнала 16 дается разрешение на передачу соответствующих данных для дальнейшей обработки, после чего компонентами 15А и/или 15В эти данные передаются по шине 4. Разрешающий сигнал предпочтительно формируется компаратором, но может формироваться и блоком управления. В защищенном режиме разрешенные для передачи для дальнейшей обработки результаты вычислений идентичны, соответственно по шине 4 передается любой из них. В случае, когда результаты не соответствуют друг другу, разрешение на их передачу не выдается, соответственно результаты по шине не передаются, и вместо этого, например, в регистр ошибок заносится соответствующая запись или формируется флаг, соответственно сигнал об ошибке, позволяющий принять соответствующие ошибке ответные меры. В рассматриваемом случае возможно прежде всего применение буферного регистра с исходными данными, рассмотренное выше в описании принципа функционирования регистров операндов со ссылками на фиг 1, 2 и 3. В особом варианте осуществления изобретения операнды в безопасном режиме могут сначала подаваться в один исполнительный блок, затем может осуществляться проверка кодов с исправлением ошибок, и после этого операнды могут подаваться во второй исполнительный блок, причем все указанные операции осуществляются на одном и том же полном такте работы процессора, работающего с номинальной тактовой частотой.

Если в соответствии с условием для переключения устанавливается необходимость обработки операндов при работе во втором режиме процессора, иными словами в режиме повышенной производительности, соответствующий операнд или операнды подается или подаются лишь в один исполнительный блок, причем практически одновременно с этим (на том же полном такте работы процессора, работающего с номинальной тактовой частотой), иными словами на следующем полутакте, следующий или следующие операнды (в случае наличия нескольких следующих операндов и при условии, что ни один из них не является важным с точки зрения безопасности) подается или подаются во второй исполнительный блок. При этом блоки подачи операндов работают с более высокой, прежде всего удвоенной по отношению к обоим исполнительным блокам тактовой частотой, соответственно один такт блоков подачи операндов соответствует одному полутакту исполнительных блоков. При некритичной с точки зрения безопасности обработке операндов контроль результатов путем их сравнения между собой не осуществляется, и соответствующие результаты или состояния соответствующим образом, прежде всего с чередованием, передаются по шине 4. В этом случае разрешений на такую передачу не требуется. Прежде всего при работе процессора в этом втором режиме, иными словами, в режиме повышенной производительности, обе части процессора, иными словами оба исполнительных блока, могут работать и асинхронно. Конфликтов при передаче результатов по шине при этом можно избежать посредством введения временных условий, например временных слотов, посредством управления на основе событий или посредством арбитража.

На фиг.4 позицией TS1 обозначен тактовый сигнал с номинальной тактовой частотой - полный такт, а позицией TS2 - тактовый сигнал с удвоенной тактовой частотой - полутакт. В соответствии с этим в безопасном режиме на каждом полном такте TS1 операнды подаются в оба исполнительных блока и предпочтительно на том же полном такте обрабатываются в них. При синхронной обработке операндов результаты можно сравнивать непосредственно, в противном случае перед последующим сравнением результатов необходима дополнительная синхронизация. В режиме повышенной производительности, иными словами при работе во втором режиме, блок подачи операндов работает с удвоенной тактовой частотой, соответственно в момент Т1 первый операнд или первые операнды подаются в один исполнительный блок, а в момент Т1/2 следующий операнд или следующие операнды подаются в другой исполнительный блок, что позволяет за два такта сигнала с удвоенной тактовой частотой (полутакта), соответствующих по времени одному полному такту сигнала с номинальной тактовой частотой, обработать в исполнительных блоках и первые, и следующие за ними операнды. В соответствии с этим в режиме повышенной производительности соответствующие блоки подачи операндов, иными словами прежде всего регистры 8 и 9 операндов, работают с более высокой, прежде всего удвоенной по сравнению с исполнительными блоками тактовой частотой. С такой же более высокой, прежде всего удвоенной, тактовой частотой работает и декодер 303, взаимодействующий со вторым переключательным средством 304, подающим в исполнительные блоки соответствующие управляющие сигналы.

Предлагаемый в изобретении принцип может применяться не только к исполнительным блокам, аналогично изображенным на фиг.1, 2 и 3, имеющим по меньшей мере два входа для подлежащих обработке операндов, иными словами к исполнительным блокам, обрабатывающим, соответственно способным обработать несколько операндов, но и к исполнительным блокам, аналогично изображенному на фиг.5, имеющим лишь один вход для подлежащих обработке операндов.

На фиг.5 показаны компоненты, в основном аналогичные описанным выше со ссылкой на фиг.3 и отличающиеся от них наличием у исполнительных блоков 500 и 501 лишь одного входа для операндов. Соответственно показанный на указанном чертеже процессор имеет лишь один регистр 8 операндов и лишь один промежуточный регистр 110 и 210. Это относится и к соответствующим компонентам, участвующим в обработке кодов с исправлением ошибок, иными словами к элементам 110А, 210А и соответствующим компараторам 15С и 25С. Первые переключательные средства 508 и 510 соответствуют показанным на фиг.3 переключательным средствам 308 и 310, а первые переключательные средства 509 и 511 - переключательным средствам 309 и 311 соответственно. И в рассматриваемом варианте элементы, обеспечивающие возможность обработки кодов с исправлением ошибок, не являются обязательными. И в рассматриваемом варианте первые переключательные средства могут быть выполнены либо в виде отдельных элементов, либо встроенными в соответствующий регистр. В рассматриваемом варианте осуществления изобретения подлежащие обработке операнды подаются последовательно, а в режиме повышенной производительности, иными словами во втором режиме - с удвоенной тактовой частотой (полутакт) и с чередованием то в один, то в другой исполнительный блок. В безопасном режиме операнды подаются в исполнительные блоки с номинальной тактовой частотой (полный такт), иными словами в оба исполнительных блока подается один и тот же операнд, который обрабатывается ими избыточно. Обеспечивающая такую работу процессора показанная на фиг.5 схема 57 управления в основном соответствует показанной на фиг.3 схеме 37 управления, но модифицирована с учетом наличия лишь одного входа для подачи операндов. Блок 502 управления также соответствует показанному на фиг.3 блоку 302 управления с теми же оговорками и модификациями.

Выдаваемые при работе процессора в безопасном режиме результаты и/или состояния (а дополнительно к ним - и коды с исправлением ошибок, но лишь при необходимости контролировать корректность работы в том числе и схемных элементов, формирующих такие коды) сравниваются между собой в соответствии с приведенным выше со ссылкой на фиг.3 описанием. Предпочтительно для того, чтобы гарантировать корректность защищаемого посредством кода результата, уже после сравнения результатов для подтвержденного/корректного результата формируется код с исправлением ошибок. В режиме повышенной производительности выдаваемые исполнительными блоками результаты последовательно передаются по шине, причем последовательность передачи результатов соответствует последовательности подачи в исполнительные блоки соответствующих операндов. Степень достоверности результатов вычислений может быть дополнительно повышена путем формирования и проверки, а также передачи по шине всех вышеупомянутых кодов с исправлением ошибок, причем изобретение позволяет обеспечить различные степени достоверности результатов.

Все вышеописанные варианты осуществления изобретения сравнимы между собой и могут использоваться в произвольных сочетаниях. Возможны и другие варианты осуществления изобретения, соответствующие положенным в основу изобретения принципам, соответственно изобретение не ограничивается описанными выше конкретными вариантами его осуществления. Общие принципы изобретения, поясненные на примере любого из конкретных вариантов его осуществления, распространяются и на любые другие возможные варианты осуществления изобретения в той мере, в которой в этих вариантах применяются те же принципы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК | 1991 |

|

RU2037271C1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С КОМАНДОПОДОБНЫМИ ЛОГИЧЕСКИМИ УПРАВЛЯЮЩИМИ ЭЛЕМЕНТАМИ | 1997 |

|

RU2143726C1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Система асинхронной двусторонней передачи данных между передающей и приемной станциями | 1983 |

|

SU1521297A3 |

| Устройство для обмена информацией | 1982 |

|

SU1070536A1 |

| ФОРМУЛЬНЫЙ ПРОЦЕССОР С РАСШИРЕННЫМ СЛОВОМ СОСТОЯНИЯ | 1999 |

|

RU2149444C1 |

| Устройство для обнаружения и исправления ошибок кодом Рида-Соломона | 1986 |

|

SU1429324A1 |

Изобретения относятся к процессорам многоядерной архитектуры. Техническим результатом является расширение функциональных возможностей устройства за счет обеспечения функционирования процессора в комбинированном режиме. Устройство содержит, по меньшей мере, два исполнительных блока, выполненных в виде арифметико-логических устройств (АЛУ А, АЛУ Б), работающих на заданной тактовой частоте, блок управления, связанный с арифметико-логическими устройствами и с дополнительными блоками подачи операндов и взаимодействующий с блоками подачи операндов таким образом, чтобы при работе в первом режиме подавать в два арифметико-логических устройства одинаковые операнды, а при работе во втором режиме подавать в два арифметико-логических устройства разные операнды, причем блок управления выполнен с возможностью управления обоими арифметико-логическими устройствами при обработке операндов в первом режиме посредством одинаковых управляющих сигналов, а при обработке операндов во втором режиме - посредством разных управляющих сигналов, и переключающий процессор между первым и вторым режимами работы. 2 н. и 18 з.п. ф-лы, 5 ил.

1. Способ обработки операндов в процессоре, имеющем, по меньшей мере, два исполнительных блока, работающих на заданной тактовой частоте, причем управление исполнительными блоками при обработке операндов осуществляется посредством управляющих сигналов и предусмотрена возможность переключения между первым и вторым режимами работы, отличающийся тем, что исполнительные блоки выполнены в виде арифметико-логических устройств (АЛУ А, АЛУ Б), связанных, по меньшей мере, с одним блоком подачи операндов, при работе в первом режиме в два арифметико-логических устройства (АЛУ А, АЛУ Б) посредством блока подачи операндов подают одинаковые операнды, а при работе во втором режиме - разные операнды, причем управление двумя арифметико-логическими устройствами (АЛУ А, АЛУ Б) при обработке операндов в первом режиме осуществляют посредством одинаковых управляющих сигналов, а во втором режиме - посредством разных управляющих сигналов.

2. Способ по п.1, отличающийся тем, что подачу операндов в арифметико-логические устройства (АЛУ А, АЛУ Б) осуществляют в зависимости от тактовой частоты, необходимой для обработки операндов арифметико-логическими устройствами (АЛУ А, АЛУ Б) и используемой в качестве номинальной тактовой частоты, а при работе во втором режиме подачу операндов на обработку осуществляют на второй тактовой частоте, более высокой по сравнению с номинальной.

3. Способ по п.2, отличающийся тем, что при работе в первом режиме подачу операндов осуществляют на тактовой частоте работы арифметико-логических устройств (АЛУ А, АЛУ Б), используемой в качестве номинальной тактовой частоты.

4. Способ по п.2, отличающийся тем, что вторая, более высокая, тактовая частота вдвое превышает номинальную, выступая в качестве удвоенной тактовой частоты.

5. Способ по п.1, отличающийся тем, что в обоих режимах работы обработку операндов арифметико-логическими устройствами (АЛУ А, АЛУ Б) ведут синхронно.

6. Способ по п.1, отличающийся тем, что обработку операндов при работе в первом режиме ведут синхронно, а при работе во втором режиме - асинхронно.

7. Способ по п.1, отличающийся тем, что операнды или производные от них данные сравнивают между собой на предмет их соответствия друг другу и при несоответствии делают вывод о наличии ошибки.

8. Способ по п.1, отличающийся тем, что состояния, возникающие при обработке операндов, или результаты (результат А, результат Б) такой обработки сравнивают между собой на предмет их соответствия друг другу и при несоответствии делают вывод о наличии ошибки, причем указанное сравнение выполняют в зависимости от конкретного режима работы.

9. Способ по п.8, отличающийся тем, что дальнейшую обработку состояний, возникающих при обработке операндов, или результатов такой обработки разрешают посредством разрешающего сигнала в зависимости от режима работы и результатов сравнения.

10. Способ по п.9, отличающийся тем, что дальнейшую обработку состояний, возникающих при обработке операндов, или результатов такой обработки разрешают посредством разрешающего сигнала в зависимости от режима работы одновременно или последовательно.

11. Устройство для обработки операндов в процессоре, имеющем, по меньшей мере, два исполнительных блока, работающих на заданной тактовой частоте, содержащее блок управления, управляющий исполнительными блоками при обработке операндов посредством управляющих сигналов и переключающий процессор между первым и вторым режимами работы, отличающееся тем, что исполнительные блоки выполнены в виде арифметико-логических устройств (АЛУ А, АЛУ Б), блок управления связан с арифметико-логическими устройствами (АЛУ А, АЛУ Б) и с дополнительными блоками подачи операндов и взаимодействует с блоками подачи операндов таким образом, чтобы при работе в первом режиме подавать в два арифметико-логических устройства (АЛУ А, АЛУ Б) одинаковые операнды, а при работе во втором режиме подавать в два арифметико-логических устройства (АЛУ А, АЛУ Б) разные операнды, причем блок управления выполнен с возможностью управления обоими арифметико-логическими устройствами (АЛУ А, АЛУ Б) при обработке операндов в первом режиме посредством одинаковых управляющих сигналов, а при обработке операндов во втором режиме - посредством разных управляющих сигналов.

12. Устройство по п.11, отличающееся тем, что блок управления и блоки подачи операндов выполнены таким образом, чтобы при работе в первом режиме подавать операнды на обработку в арифметико-логические устройства (АЛУ А, АЛУ Б) в зависимости от тактовой частоты работы арифметико-логических устройств (АЛУ А, АЛУ Б), используемой в качестве номинальной тактовой частоты, а при работе во втором режиме подавать операнды на обработку со второй тактовой частотой, более высокой по сравнению с номинальной.

13. Устройство по п.11, отличающееся тем, что блоки подачи операндов и арифметико-логические устройства (АЛУ А, АЛУ Б) выполнены таким образом, чтобы в первом режиме работать синхронно с одинаковой тактовой частотой.

14. Устройство по п.11, отличающееся тем, что блоки подачи операндов выполнены в виде набора регистров таким образом, чтобы был предусмотрен, по меньшей мере, один регистр операнда, а между регистром операнда и каждым арифметико-логическим устройством (АЛУ А, АЛУ Б) был предусмотрен, по меньшей мере, один промежуточный регистр.

15. Устройство по п.11, отличающееся тем, что блоки подачи операндов и арифметико-логические устройства (АЛУ А, АЛУ Б) выполнены таким образом, чтобы во втором режиме работать с разными тактовыми частотами.

16. Устройство по п.11, отличающееся тем, что блоки подачи операндов выполнены с возможностью их работы во втором режиме с тактовой частотой, удвоенной по сравнению с тактовой частотой работы арифметико-логических устройств (АЛУ А, АЛУ Б).

17. Устройство по п.11, отличающееся тем, что оно имеет декодер, позволяющий распознавать условие переключения режимов и работающий с той же тактовой частотой, что и арифметико-логические устройства (АЛУ А, АЛУ Б).

18. Устройство по п.11, отличающееся тем, что оно имеет средства сравнения, выполненные таким образом, чтобы сравнивать между собой операнды или производные от них данные на предмет их соответствия друг другу и при несоответствии делать вывод о наличии ошибки.

19. Устройство по п.11, отличающееся тем, что оно имеет средства сравнения, выполненные таким образом, чтобы сравнивать между собой состояния, возникающие при обработке операндов, или результаты (результат А, результат Б) такой обработки, на предмет их соответствия друг другу и при несоответствии делать вывод о наличии ошибки.

20. Устройство по п.11, отличающееся тем, что оно имеет первые переключательные средства, выполненные с возможностью сквозной передачи операндов, поступающих от средств подачи операндов, в зависимости от первого или второго режима работы процессора.

21. Устройство по п.11, отличающееся тем, что оно имеет вторые переключательные средства, выполненные с возможностью управления арифметико-логическими устройствами (АЛУ А, АЛУ Б) в зависимости от первого или второго режима работы процессора.

| US 2002073357 А, 13.06.2002 | |||

| МНОГОПРОЦЕССОРНАЯ СИСТЕМА ОБРАБОТКИ ДАННЫХ | 1997 |

|

RU2139566C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| US 6615366 B1, 02.09.2003. | |||

Авторы

Даты

2009-06-27—Публикация

2004-08-07—Подача