сриг,1

Изобретение относится к измерительной технике и может быть использовано для измерения сседнекоадрагического значения переменного напряжения и в качестве базового устройства в фазочувстви- тельных вольтметрах, корреляционных измерительных устройстпх, преобразователях мощности по лощения, измерителе добротности, i операторах стандартных сиг- н,,,1ов

Целью изобретение является повышение точности измерения

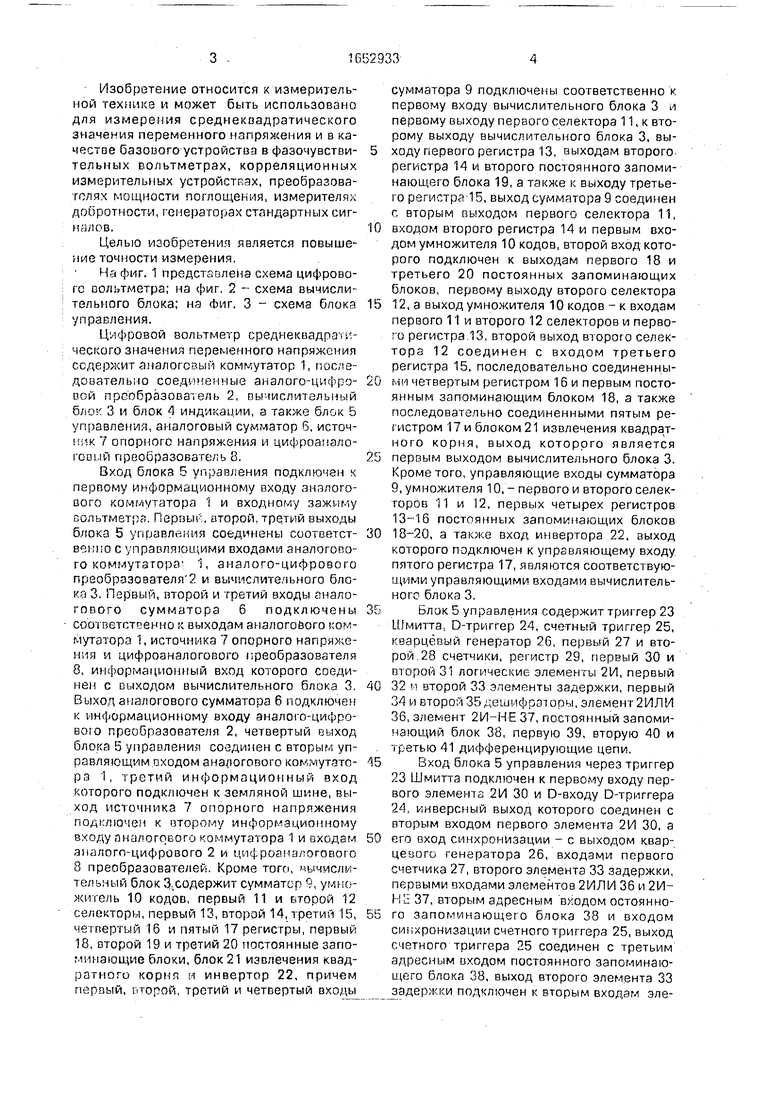

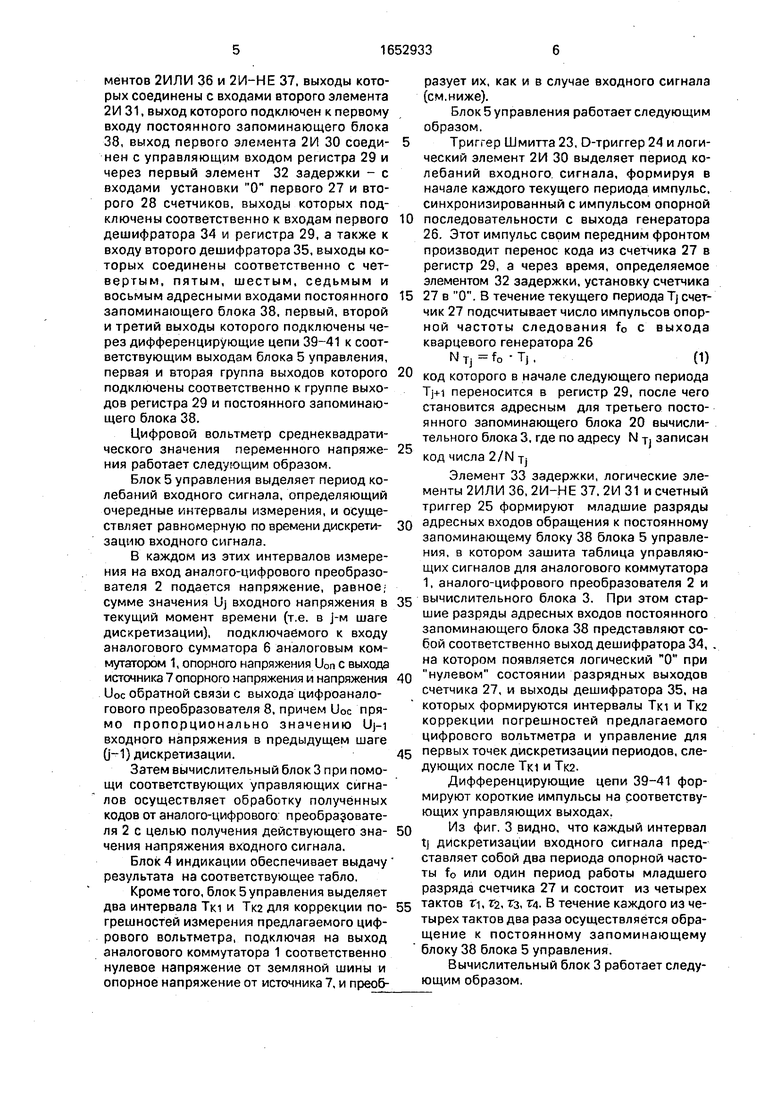

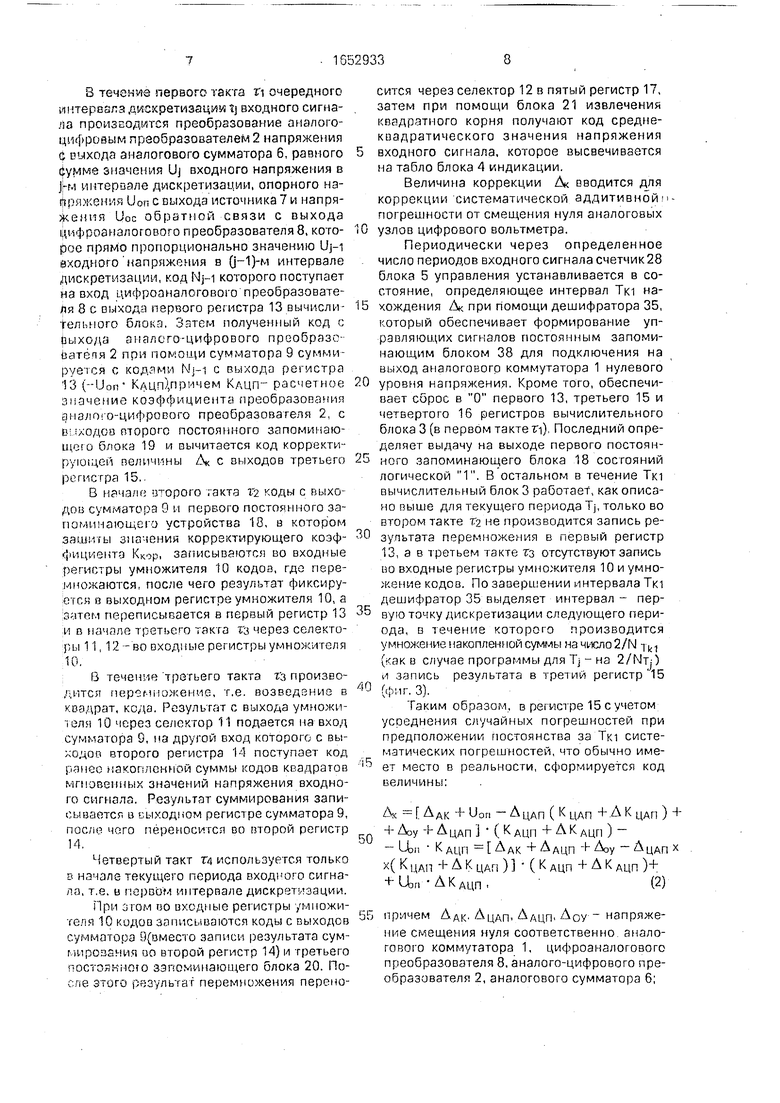

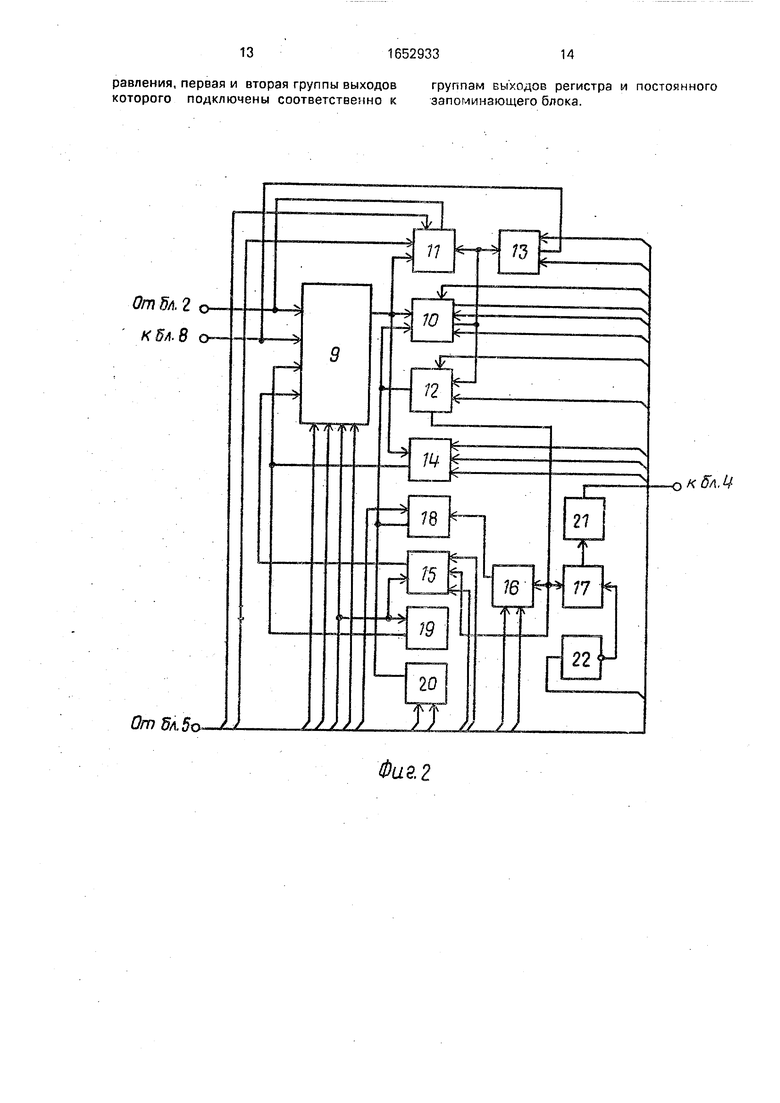

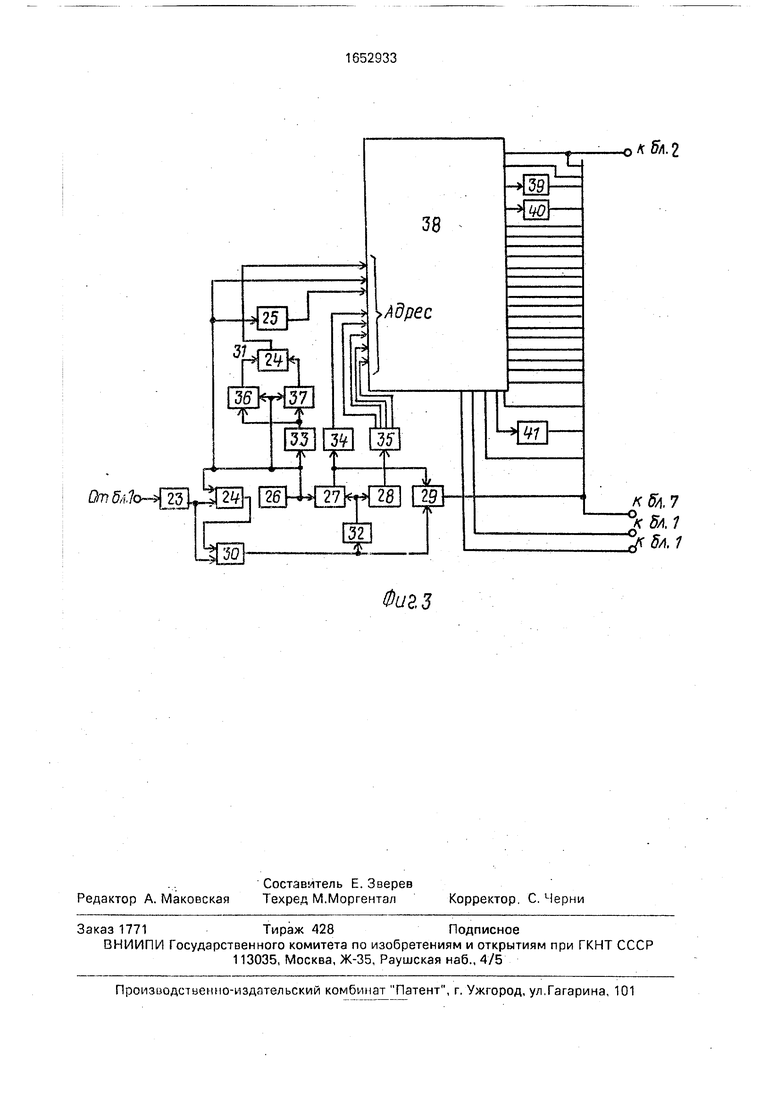

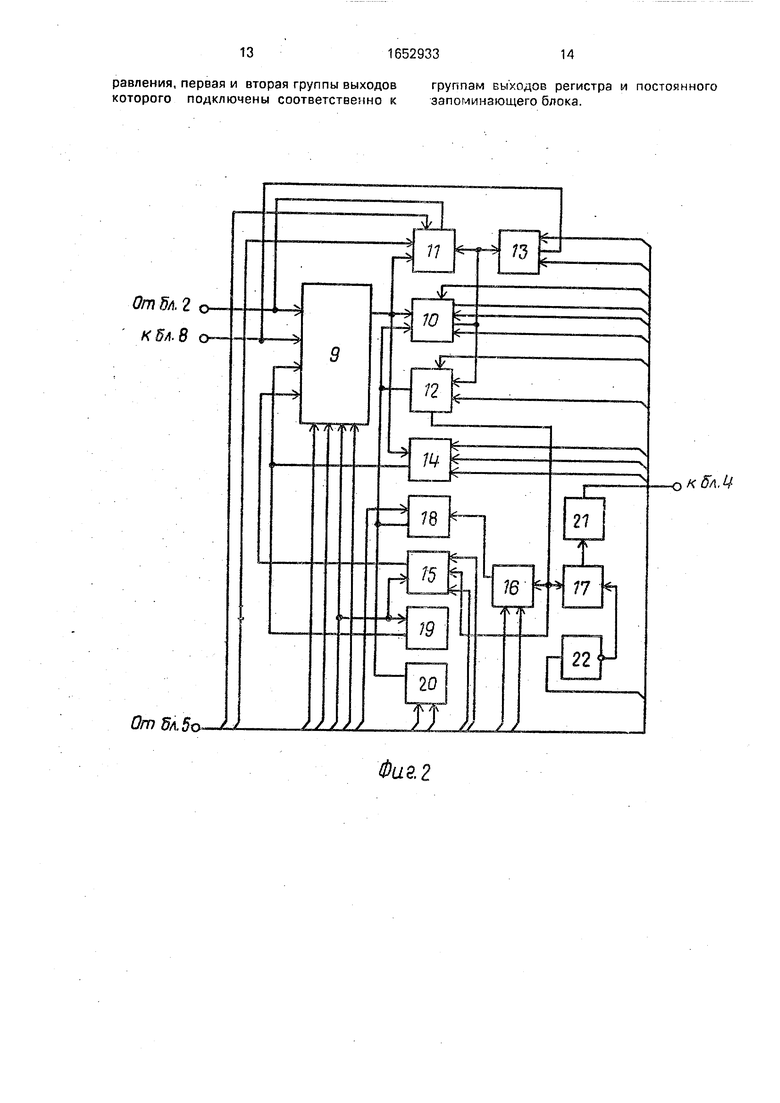

Ч | фиг 1 прпдс1Г.г.1лена схема цифрового вольтметра; на фиг 2 - схема вычислительного блока, на Фиг 3 - схема блокт управления.

Ц/}Фовой волюметр среднекиадпти- неского значения переменного напряжения ссдержиг аналогсмьм коммутатор 1, после- дооателЬ|Ю соединенные аналою циг| ро- впй преобразователь 2 сьнислчтольнь и 3 и блок 4 индикации, а также блг,к b управления аналоговый сумматор 6, источ- гчк 7 опорного напряжения и цис) роачало- i ОБПЙ преоирззова rtr ь 8.

Вход блока 5 подключен ч первому информационному влоцу аналого- вого коммутатора 1 и входному зажину оольтмет} а Пераьп .второй третий выходы блока 5 фавлг.нил соединены соответственно с , чрапляющими входами аналоговJ- го коммутатора i, аналого-цифровою преобразователя 2 и вычислите ного бло- v 3 Первый, пторсй и третий входы аналогового сумматора 6 подключены СООПСТГУГ емко к выходам аналогового г of- мутгпорз 1( источника 7 опорного напряжения и цифроэналогопого преобразователя 8, информационный вход которого соединен с выходом вычислительного блока 3 Выхог; аналогового сумматора 6 п.щключен к информационному входу аналою цифровою преобразователя 2, четвертый М1ход блока 5 управление соединен г вторым управляющим г.ходом аналоговою коммутатора 1 третий информационный вход которого подключен к земляной шине, выход источника 7 опорного напряжения по/;1лючеч У чтоглму информационному в « оду П илогоього коммутатора 1 и ьхсдам аналого-цифрового 2 и nucj рог1111 -oronom 3 преобразователем Кроме тогг ьчисли- тнльчий блок 3 содержит суммам р г- жнюль 10 кодов, первый 11 и ьгорои 12 селекторы, первый 13, второй 14, т ретин 15, ргпертмй 16 и пятый 17 регистры, первый 18 второй 19 и третий 20 постоянные запоминающие блоки, блок 21 извлечения квад- |)атного корня и инвертор 22, причем первый, третий и четвертый входы

сумматора 9 подключены соответственно к первому входу вычислительного блока 3 и первому выходу первого селектора 11, к второму выходу РЫЧИСЛГТСЛЬНОГО блока 3. выходу первого регистра 13 выходам второго регистра 14 и второго постоянного запоминающею блока 19, а также н выходу третье- ю 1, выход сумматора 9 соединен г вторым выходом первого селектора 11,

0 входом второго регистра 14 и первым входом умножителя 10 кодов, агорой вход которого подключен к выходам пррвого 18 и третьего 20 постоянных запоминающих бпоков первому выходу второго селектора

5 12, а выход умножителя 10 кодов - к входам первого 11 и второго 12 селекторов и перво- 1 о регистра 13 второй пыход второю селектора 12 соединен с входом третьего регистра 15, последовательно соединенны0 м 1 четвертым регистром 16 и первым постоянным запоминающим блоком 18, а также погледоваючьно соединенными пятым ре- i нстром 17 и блоком 21 извлечения квадратного корня, выход которого является

Ь перпым выходом вычислительного блока 3. Кроме того управляющие входы сумматора °, умножителя 10, - первого и второго селекторов .1 и 12, первых четырех регистров 13 16 постоянных запоминающих блоков

0 18-20, а так-ч е вход инвертора 22 выход i-оторого подключен к управляющему входу пятого регистра 17, являются соответсгвую- дими управляющими входами вычислительно г блока 3

ГЬлок 5 упр ленгя содержит триг гер 23

Шмитта D триггер 24, счетный 25, i p 1РЦСПЫИ генератор 6, первый 27 и второй 28 счетчики, решстр 29, поррый 30 и торой 31 логинесчис олемеч. ы 2И, первый

U 3° и второй 33 ЧТОМРНТЫ задержки, первый А и вторе 1 3е) f с.иифроюпч, элемонт2ИЛИ .элег-ент 2И НЕ 37, постоянный запоми- нзющии блок 38, первую 39. вторую 40 и i| егью 41 дифференцирующие цепи

5Sxo/; блока 5 управления через триггер

23 Шмитта подклю ен к первому входу первого элемент,, 2И 30 и D-входу D триггера 21 инверсный выход которого соединен с вторым входом первого элемента 2И 30. а

0 по пход синхронизации - с выходом квар- цв /jru (сн-фагора 26, входами первого счетчика 27 второго элемента 33 задержки пго }ыми ч хода ми эпементов 2ИЛИ 36 и 21/1- г 37, вторим адресным остоянно5 го запог пнающ г о бпока 38 и входом синхронизации счетного т риг г ера 25,выход г четного триггера 25 соединен с третьим адресным иродом постоянного запоминающего finci-a 38, выход второго элег ентэ 33 задер i r и подключен к вторым входам элементов 2ИЛИ 36 и 2И-НЕ 37, выходы которых соединены с входами второго элемента 2И 31, выход которого подключен к первому входу постоянного запоминающего блока 38, выход первого элемента 2И 30 соеди- нен с управляющим входом регистра 29 и через первый элемент 32 задержки - с входами установки О первого 27 и второго 28 счетчиков, выходы которых подключены соответственно к входам первого дешифратора 34 и регистра 29, а также к входу второго дешифратора 35, выходы которых соединены соответственно с четвертым, пятым, шестым, седьмым и восьмым адресными входами постоянного запоминающего блока 38, первый, второй и третий выходы которого подключены через дифференцирующие цепи 39-41 к соответствующим выходам блока 5 управления, первая и вторая группа выходов которого подключены соответственно к группе выходов регистра 29 и постоянного запоминающего блока 38.

Цифровой вольтметр среднеквадрати- ческого значения переменного напряже- ния работает следующим образом.

Блок 5 управления выделяет период колебаний входного сигнала, определяющий очередные интервалы измерения, и осуществляет равномерную по времени дискрети- зацию входного сигнала.

В каждом из этих интервалов измерения на вход аналого-цифрового преобразователя 2 подается напряжение, равное, сумме значения Uj входного напряжения в текущий момент времени (т.е. в j-м шаге дискретизации), подключаемого к входу аналогового сумматора б аналоговым коммутатором 1, опорного напряжения Uon с выхода источника 7 опорного напряжения и напряжения Uoc обратной связи с выхода цифроанало- гового преобразователя 8, причем Uoc прямо пропорционально значению Uj-i входного напряжения в предыдущем шаге Q-1)дискретизации.

Затем вычислительный блок 3 при помощи соответствующих управляющих сигналов осуществляет обработку полученных кодов от аналого-цифрового преобразователя 2 с целью получения действующего зна- чения напряжения входного сигнала.

Блок 4 индикации обеспечивает выдачу результата на соответствующее табло.

Кроме того, блок 5 управления выделяет два интервала TKI и Тк2 для коррекции по- грешностей измерения предлагаемого цифрового вольтметра, подключая на выход аналогового коммутатора 1 соответственно нулевое напряжение от земляной шины и опорное напряжение от источника 7, и преобразует их, как и в случае входного сигнала (см. и иже).

Блок 5 управления работает следующим образом.

Триггер Шмитта 23, D-триггер 24 и логический элемент 2И 30 выделяет период колебаний входного сигнала, формируя в начале каждого текущего периода импульс, синхронизированный с импульсом опорной последовательности с выхода генератора 26. Этот импульс своим передним фронтом производит перенос кода из счетчика 27 в регистр 29, а через время, определяемое элементом 32 задержки, установку счетчика 27 в О. В течение текущего периода Tj счетчик 27 подсчитывает число импульсов опорной частоты следования f0 с выхода кварцевого генератора 26

,.(1)

код которого в начале следующего периода Tj-и переносится в регистр 29, после чего становится адресным для третьего постоянного запоминающего блока 20 вычислительного блока 3, где по адресу N TJ записан

код числа 2/N TJ

Элемент 33 задержки, логические элементы 2ИЛИ 36, 2И-НЕ 37, 2И 31 и счетный триггер 25 формируют младшие разряды адресных входов обращения к постоянному запоминающему блоку 38 блока 5 управления, в котором зашита таблица управляющих сигналов для аналогового коммутатора 1, аналого-цифрового преобразователя 2 и вычислительного блока 3. При этом старшие разряды адресных входов постоянного запоминающего блока 38 представляют собой соответственно выход дешифратора 34, на котором появляется логический О при нулевом состоянии разрядных выходов счетчика 27, и выходы дешифратора 35, на которых формируются интервалы TKI и Ткз коррекции погрешностей предлагаемого цифрового вольтметра и управление для первых точек дискретизации периодов, следующих после TKI и Тк2.

Дифференцирующие цепи 39-41 формируют короткие импульсы на соответствующих управляющих выходах.

Из фиг. 3 видно, что каждый интервал t| дискретизации входного сигнала представляет собой два периода опорной частоты f0 или один период работы младшего разряда счетчика 27 и состоит из четырех тактов Г|, Г2, гз, r/j. В течение каждого из четырех тактов два раза осуществляется обращение к постоянному запоминающему блоку 38 блока 5 управления.

Вычислительный блок 3 работает следующим образом.

3 течение первого такта ri очередного интервала дискретизации tj входного сигнала ГФОИЗЕОДИТСЯ преобразование аналого- цифровым преобразователем 2 напряжения с рихода аналогового сумматора 6, разного сумме значения Uj входного напряжения в J-м интервале дискретизации, опорного на- пр 1 жени я Uon с выходп источника 7 и напряжения Uoc обратной связи с выхода цифроаналогоо ко преобразователя 8, которое прлмо пропорционально значению Uj-1 входного напряжения в ()M интервале дискретизации,код NJ-Iкоторого поступает на вход цифроаналогоно о преобразователя 8 с выхода первого регистра 13 вычислительного блокч. Ззтем полученный код г: выхода анаг.с го-цифрового прообрязо иотппя 2 пои помощи сумматора 9 су мм и pve -оя с кодлми NJ-I с выхода регистра 13 (/-U -iir Кдцп ,пр 1чем клцп расчетное тчачснио коэффициенту преобрпзотмип ЛНЭУО о-цпФрспого преобразовагетя 2 с ii лодов второго постоянного запоминающею блока 19 ч вычитается код корректи- г/, ЮЩРЙ величины с выходов грртььго рогисфя 15.

В iVOpOKl ;ЯКТЗ VI ОДЫ С f.bSXG

дои с мматсмл ° и первого постоянного за- поминающи .) устройства 10, в котором зашиш зпаюний корректирующего коэффициента записываются по входные регистры умножителя 10 кодов, гдо перемножаются, после Ч зт результат фиксиру- OICH i3 выходном регистре умножителя 10, а л-пем переписывается в первый регистр 13 и в начало третьего гакга гз через сслекго- (Ч 1 12 - во оход1|Ые регистры умно-1 .поля 10.

В гечен и третьего такта гз произво- М1тся перемножения, г.е возредэниз в коадрат, кэ/,а. Резулыаг с выхода умножи

ел.ч 10 чг.рез сслокшр 11 подается на вход сумма юра 9, па другой вход которого с вы хо.чо второго ренютра 1-1 поступает код рано.5 liOKOti юнной суммы кодов ксадр.пов мгновенных значений напряжения входного сигнала. Результат суммирования запи- (М;ваотсг1 и ииходном регистре сумматора 9, поен с1 ч ;го переносите: во торой регистр 14

Четвертый такт Г4 использу гея только LI начале текущего г риода входгр о сигнала, т е. ь персом интервале дискр .эции.

При июм по и сдные pet , мпожи- re. ifl 1C кодов апписыиаются коды с выходов сумматора П(омеспо записи результата сум- г inpCiJSHnq no торой регистр 14) м третьего остзяннего зэг .о инающето блока 20. По.е зтиго результа перемнсжения перепоо

5

0

0

5

O

сится через селектор 12 в пятый регистр 17, затем при помощи блока 21 извлечение кврдрттпого корня получают код средне- квадратического значения напряжения входного сигнала, которое высвечивается на табло блока 4 индикации.

Величина коррекции А вводится для коррекции систематической аддитивной погрешности от смещения нупя аналоговых узлов цифрового вольтметра.

Периодически через определенное число периодов входного сигнала счетчик 28 блока 5 управления устанавливается в состояние, определяющее интервал TKI нахождения А при помощи дешифратора 35. который обеспечивает формирование уп- равляющих сигголов постоянным запоминающим блоком 38 для подключения на ьы/од анапогогого коммутатора 1 нулевого уровня напряжения. Кроме того, обеспечивает сирое в О первого 13, третьего 15 и четвертою 16 регистров вычислительного блока 3 (в первом такте ri) Последний определяет выдачу на выходе первого постоянного запоминающего блока 18 состояний логической 1. R остальном в течение TKI вычислители ныи блок 3 работает, как описано дчя т о периода 11, только во втором г; не производится запись результата ппрем г;,к«ния ь i сг.пый регистр 13 а в трг-тьем шкт тз отсутствуют запись но входные pel истры умножителя 10 и умножение кодов. По завершении интервала TKI дешифратор 35 выделяет ишервал - первую точку диск р-л изации след7ющего периода, ь течение которого Г1рпизподится .oiav наюпломопсумгин н.ччюю2/М в случпе программы для Г, - на 2/NT.) ,i т;п-игь результата в третий регистр 15 oi u.3)

Таким образом, в peincipe 15 с учетом услэидиенич случайных погрешностей при предположение постоянства за Тки систематических пог|,ел|ностей, что обычно име- ег место в (Г,пыюсги, сформируется код величины:

Лч-ГАдк ( иэ„ --ЛЦАП(КЦЛМ +ЛКЦАП ) 4

+ Аоу - Д ЦАП J ( К лцп + Л К дцп ) - Нэп К дщ, Лдк Ь А дцп -Ь Азу - А ЦАП х

л( К ,Лп -i- А К ц/.г, ) ( К дцп + А К АЦП ) +

+ и„, АКдцп,(2)

причем ЛАК. Ацлм лип, ОУ напряжение смещения пуля соответственно аналоговою коммутатора 1, цифроэналоговогс преобразовагеля 8, аналого-цифрового преобразователя 2, аналогового сумматора 6;

КЦАП - расчетное значение коэффициента преобразования цифроаналогочого преобразователя 8;

Л Кцлп и Д Кдцп - магические и к/юнения реальных знамений кооффнциен- i08 преобразорзния соответственно цифроаналогового 8 и аналого-цифрового преобразователей от расчетных

Полученное значениеАк а дальнейшем используется в программе выполняемой вычислительным блоком 3, и хранится третьем регистре 15 до следующего интервала ее определения.

Корректирующий коэффициент Ккор вводится для коррекции погрешности отклонения от расчетного значения клффи циента преобразогания цифроанзлсгового преобразователя 8 Периодически, ка и в случае Ты, счетчиком 2 и еилп1 раторомГ рыдезлястся итервап Тк определения К/ )р в течение ю орого на пчход аналогового коммутатора 1 подключается напояжгние Don с выхода источника 7, а четвертый регистр 16 устанап/.ивг-ется о состоя1 ие логи ческой 1.

При этом на вы оде первого постоянно го запоминаю цегс блока 18 по юляется код Uo-r Кдцп1 который в конце г.ерпого такта Г пс реписыиается п первнй регистр 13, т четьертыи регистр 1C гб; ясывается в О .

В остальном работа вычислительного блока 3 пнало ична сличаю TKL По занрршо нии дешифратор 35 блока 5 упражнения выделяет интервал первой точки дискр ти ззч,ии следующего периоде, и течение которого производится умножение кода из рторого о°гистра 14 на число 2/N Гк-2 и запись результата в четвертый регистр 16 для обращения к первому постоянному запоминающему блоку 18 где записаны соответствующие коды Ккср В результате к концу интервала, выделенного на выходе дешифратора 35 блока 5 управления, в регистре 16 сформируется код величины

Мкср - Uon + ЛАК Unn ( UOP К л цп -( + А ЦАП ) ( к ЦАП Л К цдп ) - ЛОУ + ААЦ

х С К АЦП + АК дцп - Unn К дцр fiJor К I I1/( л ЦЛП ч,0,

- Лк - Uon К f цп ( 1 - - ) (3;

ЦЛп К цлп

По адресу в постоянном запоминающем блоке 18 записано значение oppt ,- тпрующего коэффициента

Ккор (НДКцЛП/Кцлп)(4)

Введение в цифровой вольтметр кор- ректируюи|их вепичин А и ККор в процессе преобразования входного сигнала на

0

roKVbu м г/ тнтеовале дискретизации с смостно с введением отрпцятельчой

Г чра м v лЛ С ЦИ (фСЛНаЛОГОгЗЫМ Г.рОО

счзг .толем 8 предыдущего резу тишл .ззгпания и flj6asKn опорною напряжения приводит к работе аналого циф- ровогс преобразователя 2 прчк тески в

ОКрПСгНО«,1 Л ОДНОЙ ТО 1КИ Uon ± U; -U, l|

тс позполяе: значи.ельноуточнигьрезультат преобразования входного сигнача.

N, - {| Uj -I Адг + Uon - ( NJ - 1 ДАЦП ) t v Кцдл 4-AKj.n ) + АОу + АЛЦП х

-- К АЦПч

0

: ( К л цп

Л 1 1/

+ AKj.n / -v, + AKAun) + Nj. ,

U, -KAqn+CUj-Ujл rv т

- Al Ккорwj .ч АЦ| I

., v . к ап ./-и х К Л-п + ( Uj

- 1 - Uon

Ох

-Uj - 1 ) КАЦПх

А К лип ,.,,АК;цАП А К цлп

Х к п--и -КАип-у--ТГЦА-

|,,А К цдп А К дцп

- Ц - 1 К ,,---Г7-

ЦАП к АЦП

(5)

ГДР Л Кщдп отклонение коэффициента преобоазованич цифроаналогового претб- разосзтелп 8 в J-M интеррчле дискретизации у мтыпающре как мутътипликатвную dorprujHC Tb так и погрешность от нелинейности

При -ком для периодического входного сипыла относительная пш реичюсть измерения гоеднекпздрат1,ческого значения нэ- пряжесил составит

IЙ1

KJHAfl

,

К АЦП

АК

АЦП

,/2 к ЦАП

5

0

5

(6)

Введение аналогового сумматора 6, источника 7 опорного напряжения и цифроа- налоговогс преобразователя 8 обеспечивает работу аналого-цифрового преобразователя 2 в окрестностях одной то11ки ( Uon ± I Uj -U; ij), следствием ег является практически полное исключение систематической составляющей аддитивной погрешности устройства и значительное снижение погрешностей от изменения коэффициентов преобразования преобразователей 2 и 8 при введении корректирующих поправок ДкиКкор программы вычисления среднеквадратического значения напряжения вычислительным блоком 3

Увеличение точности измерения сред- некоадратического значения переменного напрягг ния промышленной сети в цифровом ю. метре по сравнению с прототипом приводит к улучшению контроля за качеством производства и распределения элект- ооэнергии з следовательно, ее рациональному использованию в случае использования цифрового вольтметра в энергосистемах промышленной сети, Формула изобретения Цифровой вольтметр среднеквадрати- чсского значения переменного напряжения, содержащий аналоговый коммутатор, последовательно соединенные аналого- цифровой преобразователь, вычислительный блок и блок индикации, а также блок управления, охсд которого подключен к первому информационному входу аналогового коммутатора и входному зажиму вольтметра, а первый, второй и третий выходы блока управления соединены соответствен но с управляющими вхчдамм аналогового комм/та- торэ, аналого-цифргвого пресЬраюпэтеля и гычислтельного блока, о т л и ч з ю щ и и с л тем, ч го, с целью повышения точности измерения, в него введены аналоговый сум- мят ор, источник опорного напряжения и цифроималоговыйпреобразователь, причем ппррый, агорой и третий входы аналогового сумматора подключены соответственно к вы- одам аналогового коммутатора, источника спорного .пряжения и цифроаналогового прообразоваг4ля, информационный вход которого гоединен с выходом вычислительного блока, выход аналогового сумматора подклю - .зн к информационному входу ана- лою-цифрового преобразователя, четвертый пмход блока управления соединен с пторым управляющим входом аналогового коммутатора, третий информационный вход которого подключен к земляной шине, выход источника опорного напряжения подключен к второму информационному входу аналогового коммутатора и входам аналого- цифрового и цифро-аналогового преобразователя, кроме того, вычислительный блок содержит суммагср, умножитель кодов, первый и вюрой селекторы, с первого по пятый регистры, первый, второй и третий постоянные запоминающие блоки, блок извлечения квпдратного корня и инвертор, причем первый,второй,третий и четвертый входы сумматора подключены соответственно к первому входу вычислительного блока и первому выходу первого селектора, пгорому гыходу вычислительно1 о блока и виходу первого регистра, выходам второго регистра и второгс постоянного упоминающего блока, а также к выходу третьего регистра, выход сумматора соединен с вторым выходом первого с«;лектора, входом второго регистра и первым входом умножителя кодов, второй вход которого подключен к выходам первого и третьего постоянных

запоминающих блоков и первому выходу второго селектора, а выход умножителя кодов - к входам первого и второго селекторов и первого регистра, второй выход второго

селектора соединен с входом третьего регистра, с последовательно соединенными четвертым регистром и первым постоянным запоминающим блоком, а также последовательно соединенными пятым регистром и

0 блоком извлечения квадратного корня, выход которого является первым выходом вы- числительного блока, кроме того, управляющие входы сумматора, умножителя, селекторов, первых четырех регистров,

5 постоянных запоминающих блоков, а также вход инвертора, выход которого подключен к управляющему входу пятого регистра, являются соответствующими управляющими входами вычислительного блока, кроме то0 го, блок управления содержит триггер Шмитгя, D-триггер, счетный триггер, кварцевый генератор, первый и второй счетчики, регистр, первый и второй логические элементы 2И, первый и второй элемент ы задер5 жки.первый и второй дешифраторы, элемент ИЛИ, элемент 2И-НЕ, постоянный запоминающий блок, первую, вторую и третью дифференцирующие цепи, причем вход блока управления через триггер Шмит0 та подключен к первому входу первого элемента 2И и D-ьходу D-триггера, инверсный выход которою соединен с вторым входом пг-рвого элемента 2И, а его ьход синхронизации - с выходом кварцевого генератора,

5 входами первого счетчика, второго элемента задержки, первыми входами элементов ИЛИ и И-НЕ вторым адресным входом постоянною запоминающего блока и входом синхронизации счетного триггера, вы0 ход которого соединен с третьим адресным входом постоянного запоминающего блока, выход второго элемента задержки подключен к вторым входам элементов ИЛИ и 2И- НЕ, выходы которых соединены с входами

5 второго элемента 2И, выход которого подключен к первому адресному входу постоянного запоминающего блока, пыход первого элемента 2И соединен с управляющим входом регистра и через первый элемент задер0 жки - с вводами установки в нулевое состояние первого и второго счетчиков, выходы которых подключены соответственно к входам первого дешифратора и регистра, а также к входу второго дешифратора, выходы

5 первого и второго дешифраторов соответственно - с четвертым-восьмым адресными входами постоянного запоминающего блока, первый, второй и третий выходы которого подключены через дифференцирующие цепи к соответствующим выходам блока управления, первая и вторая группы выходов группам выходов регистра и постоянного которого подключены соответственно к запоминающего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| ТАНКОВЫЙ БАЛЛИСТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 1987 |

|

RU2226715C2 |

| Аналого-цифровой преобразователь напряжения в код системы остаточных классов | 1990 |

|

SU1732470A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ СИГНАЛОВ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ | 2004 |

|

RU2278795C2 |

| Регистратор сигналов с усреднением | 1982 |

|

SU1112230A1 |

| Быстродействующий датчик составляющих тока | 1983 |

|

SU1205039A1 |

| Многоканальный программируемый аналого-цифровой преобразователь | 1985 |

|

SU1266002A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для воспроизведения функций двух переменных | 1987 |

|

SU1517046A1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1797161A1 |

Изобретение относится к электроизмерительной технике и может быть использовано для измерения среднеквадратического значения переменного напряжения. Цель изобретения - повышение точности измерения, достигается тем, что в устройство, содержащее аналоговый коммутатор 1, аналого-цифровой преобразователь 2,вычислительное 3, блок 4 индикации и блок 5 управления, дополнительно введены дифференциальный операционный усилитель 6, источник 7 опорного напряжения и цифроа- налоговый преобразователь 8 с соответствующими связями. Повышение точности измерения позволяет улучшить контроль качества производства и распределения электроэнергии. 3 ил.

О К

Фиг 2

МЖЬ-ЗЖ Ш.

ц

о к 6л. 2

кбл.7 5л. 1 %бл.1

Фигз

| Смеляков В.В | |||

| Цифровая измерительная аппаратура инфранизких частот | |||

| - М : Энергия | |||

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Горлач А | |||

| А., Минц М.Я., Чинков В.Н | |||

| Цифровая обработка сигналов в измерительной технике | |||

| - Киев, Техника, 1985, с.59, рис | |||

| Насос | 1917 |

|

SU13A1 |

Авторы

Даты

1991-05-30—Публикация

1988-05-04—Подача