(54) СЕЛЕКТОР ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для определения оптимальных траекторий | 1983 |

|

SU1223240A1 |

| Сигнатурный анализатор | 1983 |

|

SU1140123A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Стробоскопический осциллографический регистратор однократных электрических сигналов | 1986 |

|

SU1363078A1 |

| Устройство для сбора,кодирования,передачи и приема информации с исправлением ошибок | 1980 |

|

SU960898A1 |

| Логический анализатор | 1988 |

|

SU1654822A1 |

| Устройство для сопряжения двух ЭВМ | 1988 |

|

SU1559351A1 |

1

Изобретение относится к импульсной технике.

Известен селектор импульсов, содержащий два регистра сдвига, блок управления и ввода, логические элементы И, генератор опорного сигнала

Данный селектор импульсов не обеспечивает достаточной точности.

Наиболее близким по технической сущности к предлагаемому является селектор, содержащий входной элемент И, один вход которого соединен с входной шиной, второй вход соединен с первым входом переключателя и первым выходом блока управления, а выход - с первым входом блока памяти и первым входом элемента И, второй вход которого соединен с выходом блока памяти, а третий вход - с вторым выходом блока управления, входы разрядов блока памяти соединены с соответствующими выхЬдами блока управления, а второй и третий входы блока памяти соединены с выходами переключателя, второй

вход которого подключен к Третьему выходу блока управления, четвертый выход которого соединен с первым входом выходного элемента И, а вход блока управления соединен с шиной сигнала сброса 2.

Однако такое устройство обладает недостаточной точностью селектирования.

Цель изобретения - повышение точ10ности селектирования отдельных импульсов .

Поставленная цель достигается тем, что в селектор, содержащий входной ,5 лементИ,од1т вход которого соединен С . входной шиной,второй вход соединен с первым входон переключателя и первым выходом блока управления,а выход - с яервым входом блока памяти и первым входом элемента И,второй вход которого

30 соединен с выходом блока памяти, а третий вход - с вторым выходом блока травления, входы разрядов блока памяjГИ соединены с соответствующими вы-

ходами блока управления, а второй и третий входы блока памяти соединены с выходами переключателя, второй вход которого подключен к третьему выходу блока управления, четвертый выход которого соединен с первым входом выходного элемента И, а вход блока управления соединен с шиной сигнала сброса, введены блок сравнения, сумматор рассогласования и элемент задержки, первый вход которого соединен с входом сумматора рассогласования и третьим выходом блока управления, второй вход сумматора -рассогласования подключен к выходу входного элемента И, а выходы сумматора рассогласования соединены соответственно со вторыми входами выходного элемента И и элемента задержки, третий вход которого подключен к i шине сигнала запуска, а выход - ко вто рому входу блока управления,пятый и шестой выходы которого соединены с первым и вторым входами блока сравнения, третий вход которого Подключен к выходу элемента И, а четвертый входк шине сигнала,кода, блок сравнения со держит счетчик, входы которого сое динейы с первым и третьим входами блока сравнения, буферный регистр, входы которого соединены со вторым и четвер-зо

тым входами блока сравнения, и сумматор по модулю два, входы которого подключены к выходам упомянутых счетчика и буферного регистра.

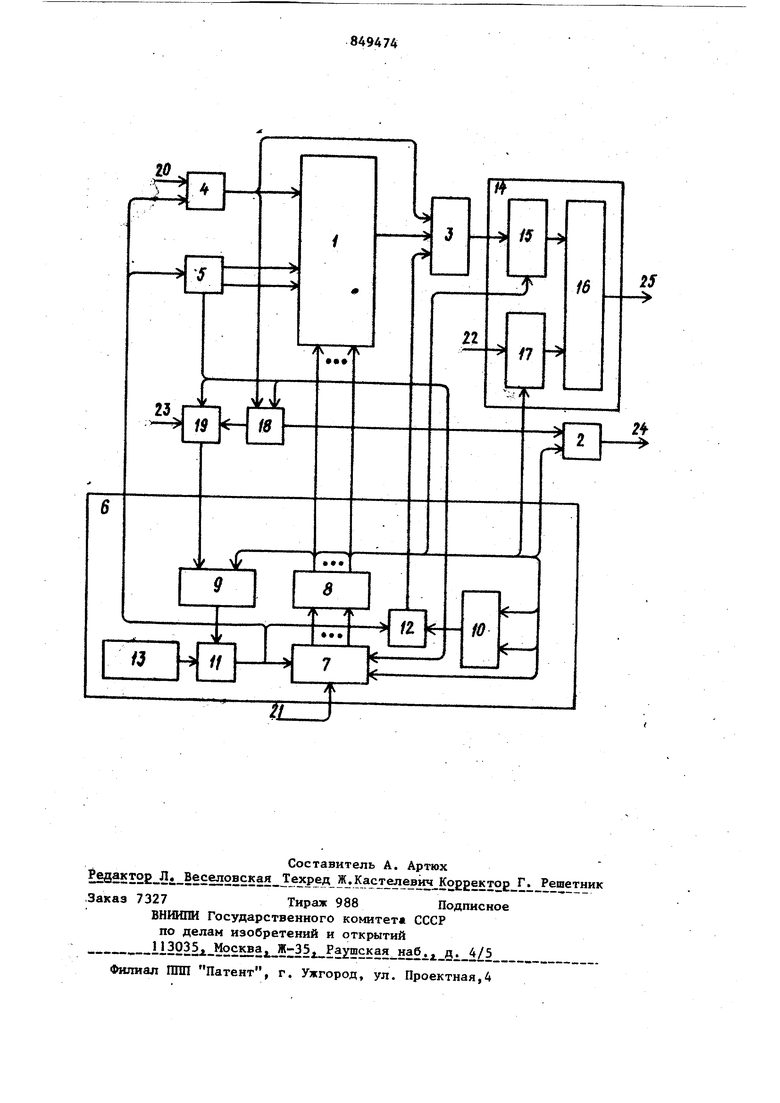

На чертеже изображена структурная 35 электрическая схема селектора.

Описываемый селектор содержит блок 1 памяти, элементы И 2-4, переключатель 5, блок 6 управления,состоящий из счетчика 7, дешифратора 8, 40 триггеров 9,10, элементов И 11 и 12, генератора 13, блока 14 сравнения, состоящего из счетчика 15, сумматора 16 по модулю ..два, буферного регистра 17, сумматор 18 рассогласования, элемент 45 19 задержки. Входной сигнал подан на шину 20, на шины 21, 22 и 23 поданы сигналы сброса, кода и запуска. Выходные сигналы снимаются с выходов 24 и 25.50

Селектор работает следующим образом.

Под действием внешнего импульса сброса, подаваемого на шину 2I, счетчики 7 и 15 устанавливаются в нулевое 55 1исходное состояние, а в буферный регистр 17 с шины 22 вводится код, опре(Деляющий длительность селектируемых

импульсов, При этом, под действием возбужденной нулевой шины дешифратора 8 срабатьшают тоиггепы 9 и 10. Триггер 9 отключает элемент И if, а триггер 10 обеспечивает установку переключателя 5 в положение Запись, счетчика 7 и сумматора 18 рассогласований в режим сложения и обеспечивает отключение элементов И I2 и 3 на время, равное первой половине заданного строба. Внешний импульс Запуск, поступающий на шину 23, пройдя через элемент 19 задержки обеспечивает срабатывание триггера 9, который подключает элемент И II, при этом импульсы поступают на счетный вход счетчика 7, который вместе с дешифратором 8 последовательно формирует все адреса на адресных шинах блока 1 , по

срабатывание триггера 10, который устанавливает переключатель 5 в положение считывания, счетчик 7 и сумматор рассогласования 18 - в режим вычитания и обеспечивает подключение элементов И 12 и 3 на время существования второй половийы заданного строба, но при наличии импульсов на выходе элемента И П. Счетчик 7 формирует последовательно все адреса относительно середины строба на адресных шинах запоминающего устройства 1, по которым из него выбирается информация, записанная в течение первой половины строба. Одновременно с этим в сумматоре 18 рассогласования из суммы квантованных импульсов, совпадающих во времени с полезным сигналом в период существования первой половины строба, вычитается количество квантованных импульсов, совпадающих во времени с полезным сигналом в период существования второй половины строба. Результат вычисления (т.е. рассогласование) во время существования последнего адреса вводится в элемент 19 задержки (с запоминанием в нем) и выводится на выход 24 селектора импульсов. которым записывается информация, поступающая с шины 20 через элемент И 4 в течение времени существования первой половины строба. Одновременно С5 матор 18 рассогласований подсчитывает (точнее суммирует) количество квантованных импульсов, совпадающих с временем существования полезного сигнала. Последний адрес в первой половине строба, сформированный на выходе дешифратора 8, обеспечивает Одновременно с этим счетчик 15 подсчитьюает пары равноудаленных импуль сов, каждый из которых расположен в противоположных частях от временно-го положения середины строба, которые поступают с выхода элемента И 3. При совпадении кода, формируемого на выходе счетчика 5, с кодом, записанным в буферном регистре 17,на выходе 25 селектора импульсов формирует ся импульс, указывающий о наличии импульса заданной длительности в середине строба. При этом на выходе 24 формируется код, соответствующий нулевому или минимальному рассогласованию, который обеспечивает установку средней задержки в элементе 2. При, отсутствии импульса на выходе 25, но при наличии импульса заданной длитель ности в стробе, временное расположение которого смещено относительно се редчны строба в сторону первой (второй) половины строба,, на выходе 24 формируется положительный (отрицатель ный) код рассогласования,который обес пе чивает смещение строба в соответствующую сторону путем уменьшения(увеличения) задержки в элементе 19.Послед ний адрес во время существования второй половины строба, сформированный на выходе дешифратора 8, обес печивает установку устройства в исходное состояние т.е. действует как внешний Сброс). После прихода следующего импульса Запуск цикл работы повторяется. Формула изобретения. 1. Селектор импульсов, содержащий входной элемент И, один вход которого соединен с входной шиной, второй вход соединен с первьгм входом переключате,ля и первым выходом блока управления а пыход - с первым входом блока памяти и первым входом элемента И, втофой вход которого соединен с выходом блока памяти, а третий вход - с вторьм выходом блока управления, входы разрядов блока памяти соединены с соответствующими выходами блока управления, а второй и третий входы блока памяти соединены с выходами переключателя , второй вход которого подключен к третьему выходу блока управления, четвертый выход которого соединен с первым входом выходного элемента-И,а вход блока управления соединен с шиной сигнала сброса , отличающийся тем, что, с целью повышения точности селектирования отдельных Щ1пульсов, в него введены блок сравнения, сумматор рассогласования и элемент задержки, первый вход которого соединен с входом сумматора рассогласования иг третьим выходом блока управления, второй вход сумма,тора рассогласования подключен к выходу входного элемента И, а вьпсоды сумматора рассогласования соединены соответственно со вторыми входами выходного элемента И и элемента задержки, третий вход которого подключен к шине сигнала запуска, а вьпсод - ко второму входу блока управления, пятый и шестой выхода которого соединены с первым и вторым входами блока сравнения, третий вход которого подключен к выходу элемента И, а четвертый вход - к шине сигнала кода. 2. Селектор по п. 1, отличающ и и с я тем, что блок сравнения содержит счетчик, входы которого соединены с первым и третьим входами лока сравнения, буферный регистр, входы которого соединены со вторым и четвертым входами блока сравнения, и сумматор по модулю два, входы которого подключены к выходам упомянутых счетчика и буферного регистра. Источники информации, : принятые во внимание при экспертизе I. Патент США. № 3550017, кл. 340174, от 22.12.70. 2« Авторское свидетельство СССР по заявке 2539870/18-21, кл. Н 03 К 5/18 от 01.11.77.

Авторы

Даты

1981-07-23—Публикация

1979-05-23—Подача