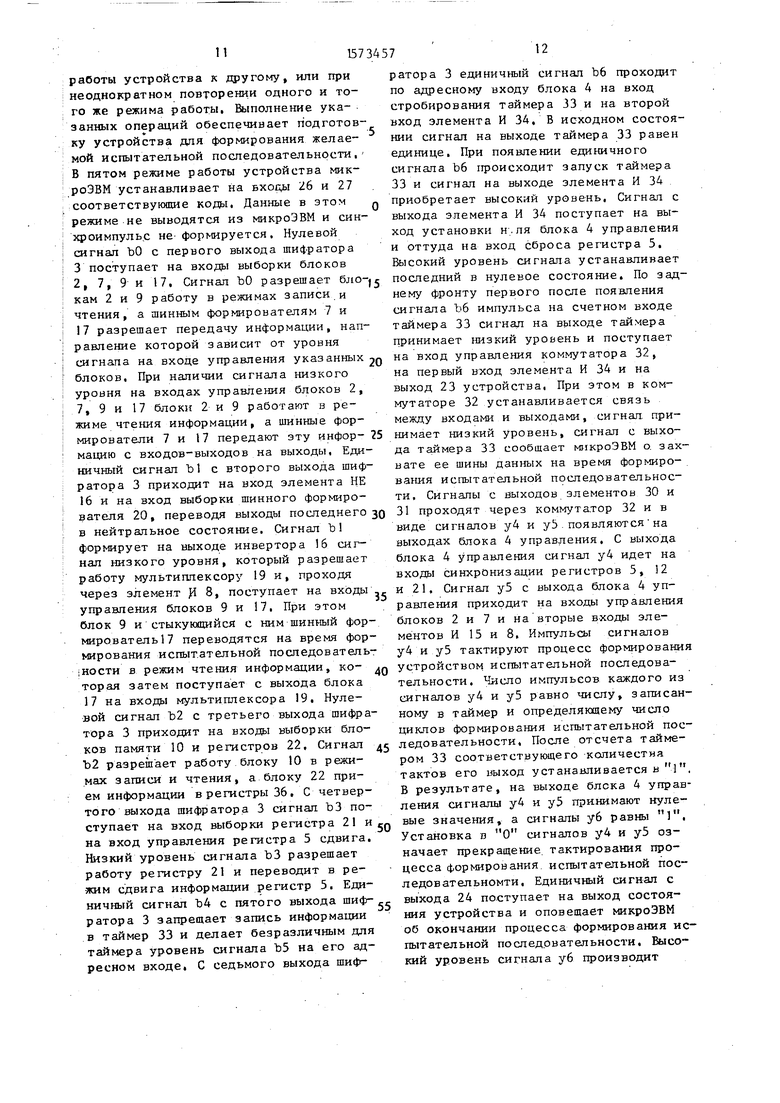

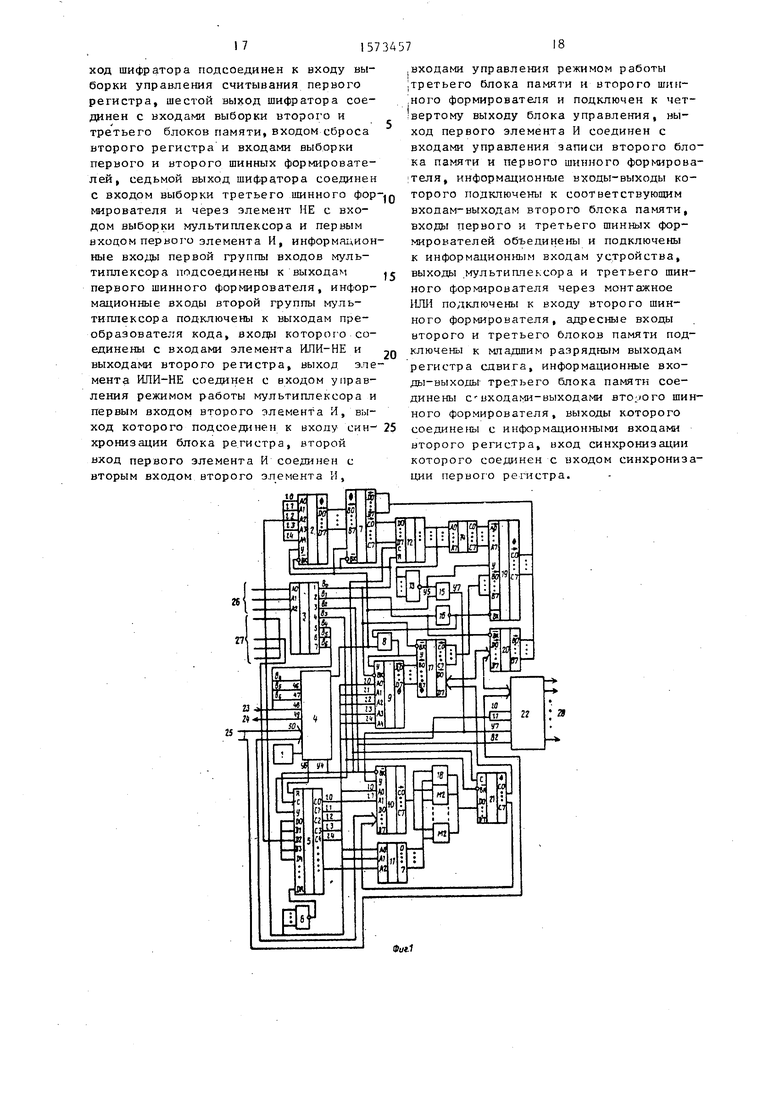

вход 23 синхронизации, выход 24 состояния, информационные входы 25, группы адресных входов 26 и 27, выходы 28, выходы Ъ0-Ъ „, шифратора 3, выходы ес-en регистра 5, выходы у4-у (, Штока выход у7 элемента И 15,

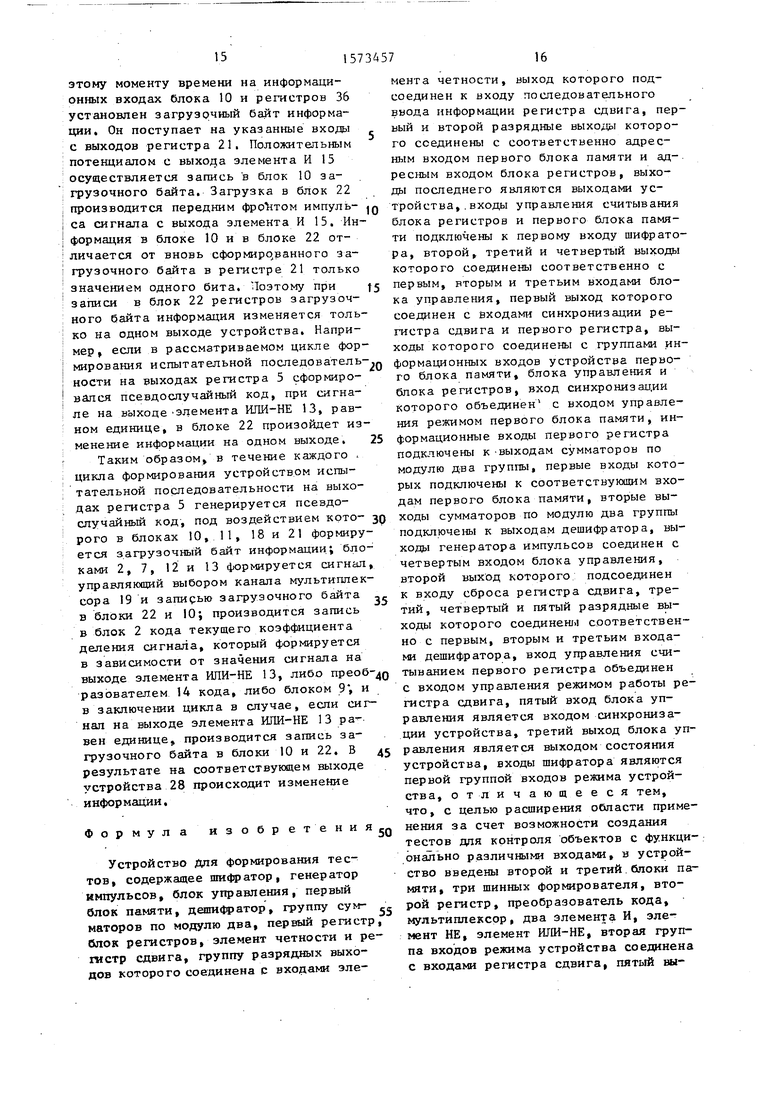

Блок 4 управления (фиг. 2) содержит триггер 29, элементы ИЗО и 31, коммутатор 32, таймер 33, элемент И 34.

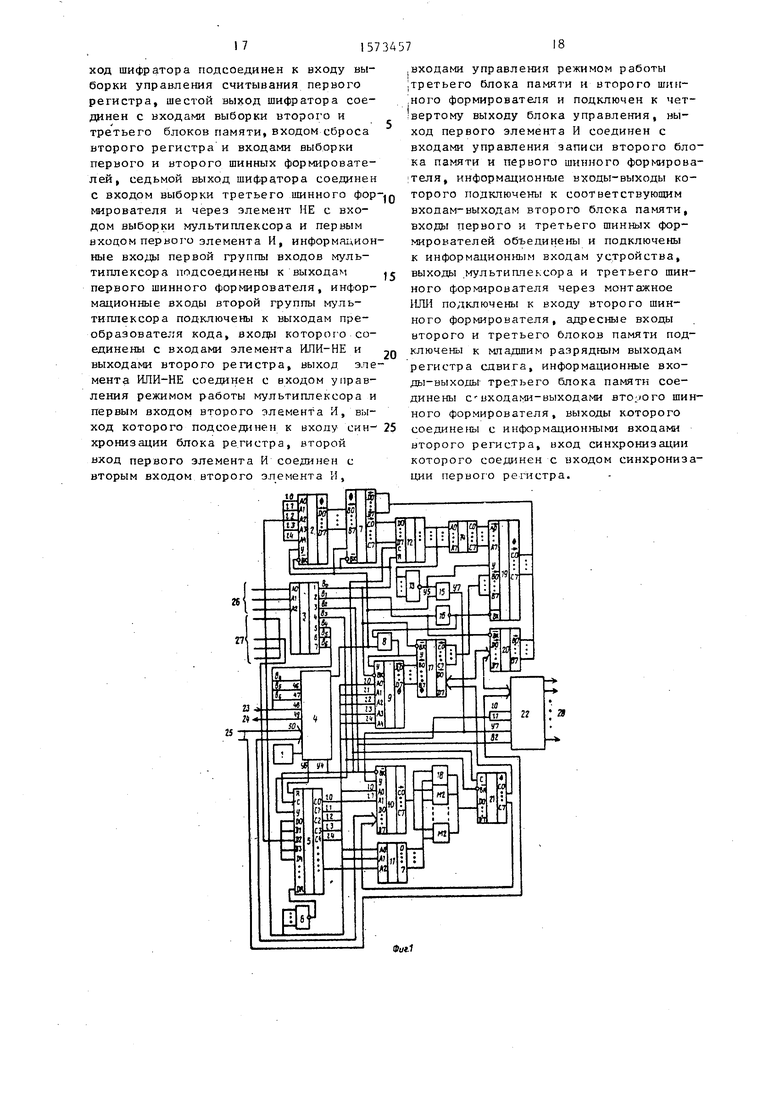

Блок 22 регистров (фиг. 3) содержит дешифратор 35, регистры 36,

Преобразователь 14 может быть построен на основе микросхемы типа КР 55 6РТ5, программируемой в соответствии с десятичным эквивалентом двоичного кода

Л-, при 4 е{1,2,,..254};(1)

С L255, при Ад 10,255}, где с - десятичный эквивалент двоич- ного кода СОС1С2СЗС4С5С6С7 на выходах преобразователя; А - десятичный эквивалент двоичного кода ЛОА1А2АЗА4А5А6А7 на входах преооразователя,

Преобразователь 14 кода осуществляет преобразование кода АОА1А2АЗА4А5А6А7, поступающего на его входы, а код СОС1С2СЗС4С5С6С7 в соответствии с (1)

Устройство работает следующим об- разом,

В процессе формирования испытательной последовательности устройство может работать в различных режимах. Выбор режима работы осуществляет микро ЭВМ, воздействуя на устройство по ад ресным входам 26 и 27, подключенным к шине адреса микроЭВМ. Причем по входам 26 задается код режима работы устройства, а по входам 27-адресная ин- формация. Ввод информации в устройство производится из микроЭВМ, шина данных соединена с информационным входом устройства 25. Синхронизацию этого ввода осуществляет сама микроЭВМ, фор мируя синхроимпульс, поступающий с шины управления микроЭВМ на вход 23 устройства. Низкий уровень сигнала с выхода 24 устройства оповещает микроЭВМ о протекании процесса формиро- вания устройством испытательной последовательности. Выход устройства 24 соединен с входом запроса прерывания шины управления микроЭВМ. В исходном состоянии на адресных входах устройства 26 и 27 присутствует нулевой код, шина данных микроЭВМ находится в нейтральном состоянии, синхроимпульс, сопровождающий нывод

д з д

5

данных из микроЭВМ, отсутствует. Сигнал с выхода шифратора 3 поступает на входы выборки блоков 2 и 9, шинных формирователей 7 и 17 и на вход сброса регистра 12, Единичный сигнал запрещает работу указанных блоков, переводит их выходы в нейтральное состояние и удерживает на выходах регистра 12 нулевой код. Единичный сигнал с второго выхода шифратора 3 приходит на вход выборки шинного формирователя

20и через инвертор 16 на вход выборки мультиплексора 19. При этом запрещается работа шинного формирователя 20, переводятся его выходы в нейтральное состояние и разрешается работа мультиплексора 19. С третьего выхода шифратора 3 единичный сигнал поступает на вход выборки блока 10 и на вход выборки блока регистров 22, Сигнал запрещает работу блока 10 и дешифратора 35 блока 22 (фиг, 3), С выходов дешифратора 35 единичные сигналы поступают на входы разрешения записи регистров 36 и запрещают запись в них информации. На входе выборки регистра

21и на входе управления режимом работы регистра 5 в исходном состоянии присутствует единичный сигнал, поступающий с четвертого, выхода шифратора 3. Этот сигнал запрещает работу регистра 21, переводит его выходы в нейтральное состояние и устанавливает регистр 5 в режим параллельной записи информации. Сигнал с пятого выхода шифратора 3 поступает на вход блока 4 управления, оттуда на вход выборки таймера 33 (фиг. 2). Единичный сигнал запрещает запись информации в таймер. Сигнал, поступающий

на адресный вход А таймера 33, не оказывает на последний никакого воздействия, так как на входе выборки таймера присутствует сигнал высокого уровня. С выхода генератора 1 импульсов сигнал по тактовому входу блока 4 управления приходит на тактовый вход счетного триггера 29 и на вторые входы логических элементов ИЗО и 31.

Элементы И24 и 25 преобразуют сигналы в две последовательности несовпадающих во времени импульсов, которые поступают на входы ВО, В1 коммутатора 32. Сигнал с прямого выхода трип ера 29 постоянно поступает на счетный вход таймера 33. Запуск тай5157

мера в режим счета производится передним фронтом сигнала, поступающего с седьмого выхода шифратора 3, В исходном состоянии сигнал имеет низкий уровень, поэтому таймер удерживается в режиме покоя, сигнал на его выходе имеет высокий уровень и на выходе элемента 34 присутствует сигнал низкого уровня. Единичный сигнал с выхода таймера 33 поступает на выход блока 4 управления и на вход управления коммутатора 32, С управляющего выхода единичный сигнал приходит на выход состояния устройства 24 и оттуда в микроЭВМ, оповещая ее об отсутствии процесса формирования устройством испытательной последовательности. Единичный сигнал на управляющем входе коммутатора 32 производит в последнем подключение к выходам входов АО, А1, на которых из-за отсутствия в исходном состоянии синхроимпульса имеет место сигнал низкого уровня, Поэтому на выходах блока 4 управления присутн ствуют нулевые сигналы, В результате, в исходном состоянии в устройстве отсутствуют сигналы синхронизации, вырабатываемые блоком 4 управления, шифратор 3 запрещает обращение к блокам 2, 7, 9, 10, 17, 20, 21 и 22, информация в блоках, содержащих элементы памяти, остается неизменной.

Первый режим работы устройства предназначен для проведения инициализации таймера 33, которая осуществляется путем записи в таймер и-з микро- ЭВМ .кода управляющего слова. Результатом инициализации таймера 33 является его готовность выполнять функцию одновибратора с программируемой длительностью импульса, причем запуск одновибратора производится по переднему фронту сигнала, поступающего на вход стробирования таймера 33, В первом режиме работы устройства микро- L ЭВМ устанавливает на адресных входах 26 и 27 устройства соответствующие коды и выводит по шине данных на информационные входы устройства 25 код управляющего слова, Этот код поступает на информационные входы блока 4 управления и оттуда на информационные входы таймера 33. Вывод из мик- роЭВМ кода управляющего слова сопровождается синхроимпульсом, поступающим из микроЭВМ на вход 23 устройства и оттуда на вход синхронизации блока 4 управления. Код с адресных вхо457

дов 26 проходит на входы шифратора 3, который преобразует входной код. Нулевой сигнал поступает с пятого разрядного выхода шифратора 3 на адресный вход блока 4 управления и оттуда на вход выборки таймера 33. При этом разрешается запись в таймер информации, Единичный сигнал с шестого раэQ рядного выхода шифратора 3 поступает на вход блока 4 управления и оттуда приходит на вход А таймера 33, переводя последний в режим записи управляющего слова. Запись кода управляюc щего слова в таймер 33 производится синхроимпульсом, поступающим на вход записи таймера с входа синхронизации.

Второй режим работы устройства предназначен для загрузки из микроЭВМ

0 в таймер 33 числа циклов формирования, определяющего длину генерируемой устройством псевдослучайной последова- ельности. В этом режиме микроЭВМ устанавливает на адресные входы 26 и 27

5 устройства соответствующие коды, на информационный вход 25 устройства - код числа и формирует синхроимпульс, поступающий на синхровход устройства. Код поступает с адресных входов ус0 тройства на входы шифратора 3. С информационного входа 25 устройства код приходит на информационные входы блока 4 управления и оттуда на информационные входы таймера 33, С синхро- входа устройства 23 на вход синхронизации олока 4 управления приходит синхроимпульс. Шифратор 3 преобразует код, равный 010, в код, равный 1111000, отличающийся от кода § л 1111100 исходного состояния () значением бита ъ4, низкий уровень которого разрешает запись информации в таймере 33. Запись кода числа в таймер 33 производится синхроимпульсом,

с поступающим на вход записи таймера с входа 23 синхронизации.

Инициализация таймера 33 и аагруз- ка в него данных обеспечивают подготовку таймера к работе. В процессе

0 формирования испытательной последовательности таймер 33 формирует на своем выходе сигнал длительностью

n- T1, (2)

где п - число циклов формирования испытательной последовательности, загруженное в таймер из микроЭВМ;

Т1 - длительность периода сигнала на входе Т таймера 33.

5

5

Третий режим работы устройства предназначен для вывода информации Из микроЭВМ в регистры 36 блока 22, 5тот режим дает возможность формировать псевдослучайную последовательность с любого начального состояния, Предварительно выведенного из микро- ЭВМ в регистры 36; позволяет побайтно выводить из микроЭВМ на объект Контроля, подключенный к выходам 28 устройства, заранее рассчитанный тест В третьем режиме микроЭВМ устанавливает на адресные входы 26 и 27 устройства коды, выводит на информационный вход 25 устройства байт информации, формирует синхроимпульс, проходящий по синхровходу 23 устройства на выход синхронизации блока 4 управления,. Коды на входах 26 и 27 являются адрес ной информацией, причем в третьем режиме используются информация только двух младших битов, указывающих код адреса одного из регистров 36 блока 22, Остальные биты кода могут при- нимать произвольные значения, С входов 26 и 27 устройства информация поступает на адресные входы шифратора 3 и на входы параллельной записи регистра 5 сдвига. Шифратор 3 преобразует код. Нулевой сигнал Ъ2 с третьего разрядного выхода шифратора 3 приходит на вход выборки блока 10 и на вход выборки блока 22 регистров, к которому подключен .вход выборки дешифрато ра 35 (фиг, 3). Сигнал Ь2 разрешает работу блока 10 в режимах записи и считывания информации, а также производит выборку дешифратора 35, Единичный сигнал ЪО с первого выхода шиф ратора 3 поступает на вход установки нуля регистра 12, обнуляет его и тем самым обеспечивает единичный сигнал управления элементом И15 на выходе элемента ИЛИ-НЕ 13, Высокий уровень сигнала на первом входе элемента И15 открывает последний для прохождения сигнала синхронизации у5. Единичный сигнал ТэЗ с четвертого выхода шифратора 3 поступает на вход управления режимом работы регистра 5 сдвига и на вход выборки регистра 21, Сигнал ЪЗ устанавливает регистр 5 в режим приема параллельной информации, запрещает запись данных в регистр 21 и переводит его выходы в нейтральное состояние. Байт данных, выведенных из микроЭВМ, проходит с информационных входов устройства 25 на входы блоков 10 и 22, на входы регистров 36. Единичный сигнал с выхода таймера 33 присутствует на входе управления коммутатора 32 и обеспечивает прохождение через указанный коммутатор синхроимпульса с входа 23 синхронизации на выходы у4 и у5 блока 4 управления, Далее синхроимпульс в виде сигнала у4 блока 4 управления приходит на вход синхронизации регистра 5 и своим передним фронтом производит запись кода в указанный регистр. На выходах регистра 5 появляется код. Сигналы еО, el с выходов регистра 5 поступают на адресные входы блока 10 и по адресным входам блока 22 проходят на входы дешифратора 35, Последний в соответствии с комбинацией кода А6 производит выборку одного из регистро 36 и разрешает запись в него информации ,

Одновременно синхроимпульс в виде сигнала у5 блока 4 управления преходит через элемент И15, поступает на вход управления режимом работы блока 10 и на входы синхронизации регистров 36, Синхроимпульс производит запись информации и в блок 10,и в один из регистров 36 блока 22, В результйте байт информации, выведенной из микро- ЭВМ на информационные входы 25 устройства, записывается в блоки 10 и 22, С выходов блока 22 информация поступает на выходы 28 устройства.

Таким образом, третий режим работы устройства позволяет вывести из микроЭВМ на входы объекта контроля любую предварительную последовательность сигналов. При этом подаваемая на входы объекта информация одновременно записывается в блок 10,

Четвертый режим работы устройства предназначен для одновременной загрузки блоков 2 и 9 кодами коэффициентов деления сигнала. Величина этих кодов задается пользователем для каждого конкретного выхода устройства и определяется в зависимости от объекта контроля и его режима работы. Множество возможных значений кода зависит от разрядности блоков 2 и 9. Коэффициенты деления сигнала задаются для каждого из выходов устройства, поэтому объем памяти для их хранения определяется количеством выходов устройства.

Загрузка кодов в блоки 2 и 9 производится следующим образом, В четвер

том режиме микроЭВМ устанавливает на адресные входы 26 и 27 устройства коды, выводят на информационные входы 25 устройства код, формирует синхроимпульс Код на входах 26 - это код четвертого режима работы устройства, а код на входах 27 является адресом ячеек блоков 2 и 9, в которые должен быть загружен код с входов 25.

В результате блокам 2 и 9 разрешается работа в режимах записи и чтения а шинным формирователям 7 и 17 разрешается передача информации, направле

3457Ю

ства 27 записывается в регистр 5 и с его выходов приходит на адресные входы блоков 2 и 9, При наличии сигнала низкого уровня на входах управления блоков 2, 7, 9, 17 блоки 2 и 9 находятся в режиме чтения информации, которая передается шинными формирователями 7 и 17. Одновременно в виде сигнала у5 блока 4 упра вления синхроимпульс поступает на входы управления блоков 2 и 7 и, проходя через элемент И 8, на входы управления блоков 9 и 17. При этом шинные формирователи 7

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Устройство для отладки микроЭВМ | 1985 |

|

SU1410708A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для подготовки данных | 1988 |

|

SU1617429A1 |

| Устройство для отображения информации | 1986 |

|

SU1441450A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для сопряжения микроЭВМ с внешним устройством | 1985 |

|

SU1283780A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении систем контроля и диагностики цифровых объектов. Целью изобретения является расширение области применения за счет возможности создания тестов для контроля объектов с функционально различными входами. Устройство для формирования тестов содержит генератор импульсов, три блока памяти, шифратор, блок управления, регистр сдвига, элемент четности, три шинных формирователя, два элемента И, дешифратор, два регистра, элемент ИЛИ-НЕ, преобразователь кода, инвертор, группу сумматоров по модулю два мультиплексор. В устройстве можно организовать управление по каждому из выходов устройства такими количественными характеристиками изменения сигнала, как количество переключений, частота переключений, вероятность появления сигналов "0" или "1" и т.д. Управление этими характеристиками осуществляется за счет регулирования коэффициента деления сигнала по каждому отдельному выходу устройства, который задается программно. В результате устройство становится программно-адаптируемым по отношению к объектам контроля, имеющим функционально различные входы. 3 ил.

ние которой зависит от уровня сигнала и 17 передают информацию с входов на

на входе управления указанных блоков. Нулевой сигнал Ы с второго разрядного выхода шифратора 3 приходит на вход инвертора 16, обеспечивая на его выходе сигнал высокого уровня, и на вход выборки шинного формирователя 20 С выхода инвертора 16 единичный сигнал поступает на вход выборки мультиплексора 19 и на первый вход элевходы-выходы, а блоки 2 и 9 принимают эту информацию в соответствующие ячей -ки памяти. Информация, выведенная из

микроЭВМ, одновременно записывается в 2Q блоки 2 и 9. Таким образом, четвертый режим работы устройства позволяет установить по любому выходу устройства требуемый коэффициент деления сигнала Пятый режим работы устройства яв35

40

мента И 8, При этом запрещается рабо- 25 ляется режимом формирования испыта- та мультиплексору 19, переводятся его выходы в нейтральное состояние и открывается элемент И 8 по отношению к сигналу у5. Разрешение работы шинного формирователя 20 делает возможным 30 передачу информации с входов формирователя на его выходы, Единичный сигнал ЪЗ с четвертого выхода шифратора 3 поступает на вход управления режимом работы регистра 5 сдвига и на вход выборки-регистра 21, Сигнал ЪЗ переводит регистр 5 в режим приема параллельной информации, а выходы регистра 21 - в нейтральное состояние. Код коэффициента деления сигнала с входов устройства 25 поступает на входы шинного формирователя 17 и через блок 20 на входы шинного формирователя 7. Синхроимпульс, сопровождающий вывод кода из микроЭВМ, приходит по д5 синхроьходу устройства 23 на вход синхронизации блока 4 управления и оттуда поступает на входы коммутатора 32, Единичный сигнал с выхода таймера 33 присутствует на входе управления ком- „) мутатора 32 и обеспечивает прохождение синхроимпульса с входов коммутатора 32 на выходы у4 и у5 блока 4 управления. Далее синхроимпульс в виде сигнала у4 блока 4 управления прихо- ,, дит на вход синхронизации регистра 5 и своим передним фронтом производит запись параллельной информации в регистр 5. Код с адресных входов устроительной последовательности, В этом р жиме устройство генерирует псевдослу чайную последовательность регулируемой длины с любого заданного начального состояния и с управляемыми по каждому из выходов устройства количественными характеристиками изменен сигнала. Поэтому прежде чем реализовать пятый режим работы устройства н обходимо выполнить следующие подгото вительные операции: с помощью режима 1 произвести инициализацию таймера 3 блока 4 управления; используя режим загрузить в таймер 33 код числа, определяющий длину желаемой испытатель ной последовательности; воспользовав шись режимом 3, загрузить в блок 22 регистров и в блок 10 желаемое начал ное состояние, с которого начинается процесс формирования испытательной последовательности; применяя режим 4 загрузить в блоки 2 и 9 двоичные код желаемых коэффициентов деления сигна ла по каждому выходу устройства,

Эти операции выполняются с помощь микроЭВМ, причем -переход от одного машинного цикла вывода к другому дол жен происходить через установку на а ресных входах устройства 26 и 27 код которому соответсвует исходное состо ние устройства. Это гарантирует сохг ранность информации в блоках 2, 9, 1 22 и 27 при переходе от одного режим

и 17 передают информацию с входов на

входы-выходы, а блоки 2 и 9 принимают эту информацию в соответствующие ячей- -ки памяти. Информация, выведенная из

микроЭВМ, одновременно записывается в блоки 2 и 9. Таким образом, четвертый режим работы устройства позволяет установить по любому выходу устройства требуемый коэффициент деления сигнала. Пятый режим работы устройства яв5

0

5 ляется режимом формирования испыта- 0 5 ) ,

тельной последовательности, В этом режиме устройство генерирует псевдослучайную последовательность регулируемой длины с любого заданного начального состояния и с управляемыми по каждому из выходов устройства количественными характеристиками изменения сигнала. Поэтому прежде чем реализовать пятый режим работы устройства необходимо выполнить следующие подготовительные операции: с помощью режима 1 произвести инициализацию таймера 33 блока 4 управления; используя режим 2, загрузить в таймер 33 код числа, определяющий длину желаемой испытательной последовательности; воспользовавшись режимом 3, загрузить в блок 22 регистров и в блок 10 желаемое начальное состояние, с которого начинается процесс формирования испытательной последовательности; применяя режим 4, загрузить в блоки 2 и 9 двоичные коды желаемых коэффициентов деления сигнала по каждому выходу устройства,

Эти операции выполняются с помощью микроЭВМ, причем -переход от одного машинного цикла вывода к другому должен происходить через установку на адресных входах устройства 26 и 27 кода, которому соответсвует исходное состояние устройства. Это гарантирует сохг ранность информации в блоках 2, 9, 10, 22 и 27 при переходе от одного режима

работы устройства к другому, или при неоднократном повторении одного и того же режима работы, Выполнение указанных операций обеспечивает подготов

ку устройства для формирования желаемой испытательной последовательности, В пятом режиме работы устройства мик- роЭВМ устанавливает на входы 26 и 27 соответствующие коды, Данные в этом режиме не выводятся из микроЭВМ и синхроимпульс не формируется. Нулевой сигнал ЪО с первого выхода шифратора 3 поступает на входы выборки блоков 2, 7, 9 и 17, Сигнал Ъ0 разрешает блокам 2 и 9 работу в режимах записи и чтения, а шинным формирователям 7 и 17 разрешает передачу информации, направление которой зависит от уровня сигнапа на входе управления указанных блоков. При наличии сигнала низкого уровня на входах управления блоков 2, 7, 9 и 17 блоки 2 и 9 работают в режиме чтения информации, а шинные формирователи 7 и 17 передают эту информацию с входов-выходов на выходы, Единичный сигнал Ъ1 с второго выхода шифратора 3 приходит на вход элемента НЕ

16и на вход выборки шинного формирователя 20, переводя выходы последнего в нейтральное состояние. Сигнал Ъ1 формирует на выходе инвертора 16 сигнал низкого уровня, который разрешает работу мультиплексору 19 и, проходя через элемент J1 8, поступает на входы управления блоков 9 и 17, При этом блок 9 и стыкующийся с ним шинный формирователь 17 переводятся на время формирования испытательной последовательности в режим чтения информации, которая затем поступает с выхода блока

17на входы мультиплексора 19, Нулевой сигнал Ъ2 с третьего выхода шифратора 3 приходит на входы выборки блоков памяти 10 и регистров 22, Сигнал Ъ2 разрешает работу блоку 10 в режимах записи и чтения, а блоку 22 прием информации в регистры 36, С четвертого выхода шифратора 3 сигнал ЪЗ поступает на вход выборки регистра 21 и на вход управления регистра 5 сдвига. Низкий уровень сигнала ЪЗ разрешает работу регистру 21 и переводит в режим сдвига информации регистр 5, Единичный сигнал Ъ4 с пятого выхода шифратора 3 запрещает запись информации

в таймер 33 и делает безразличным для таймера уровень сигнала Ъ5 на его адресном входе, С седьмого выхода шиф5

0

5

0

5

0

5

0

5

ратора 3 единичный сигнал Ь6 проходит по адресному входу блока 4 на вход стробирования таймера 33 и на второй вход элемента И 34, В исходном состоянии сигнал на выходе таймера 33 равен единице. При появлении единичного сигнала Ъ6 происходит запуск таймера 33 и сигнал на выходе элемента И 34 приобретает высокий уровень, Сигнал с выхода элемента И 34 поступает на выход установки н ля блока 4 управления и оттуда на вход сброса регистра 5. Высокий уровень сигнала устанавливает последний в нулевое состояние. По заднему фронту первого после появления сигнала Ъ6 импульса на счетном входе таймера 33 сигнал на выходе таймера принимает низкий уровень и поступает на вход управления коммутатора 32, на первый вход элемента И 34 и на выход 23 устройства, При этом в коммутаторе 32 устанавливается связь между входами и выходами, сигнал принимает низкий уровень, сигнал с выхода таймера 33 сообщает микроЭВМ о захвате ее шины данных на время формирования испытательной последовательности. Сигналы с выходов элементов 30 и 31 проходят через коммутатор 32 и в виде сигналов у4 и уЬ появляются на выходах блока 4 управления, С выхода блока 4 управления сигнал у4 идет на входы синхронизации регистров 5, 12 и 21, Сигнал у5 с выхода блока 4 управления приходит на входы управления блоков 2 и 7 и на вторые входы элементов И 15 и 8, Импульсы сигналов у4 и у5 тактируют процесс формирования устройством испытательной последовательности. Число импульсов каждого из сигналов у4 и у5 равно числу, записанному в таймер и определяющему число циклов формирования испытательной последовательности, После отсчета таймером 33 соответствующего количества тактов его выход устанавливается в 1, В результате, на выходе блока 4 управления сигналы у4 и у5 принимают нулевые значения, а сигналы уб равны 1, Установка в О сигналов у4 и у5 означает прекращение тактирования процесса формирования испытательной пос ледовательномти. Единичный сигнал с выхода 24 поступает на выход состояния устройства и оповещает микроЭВМ об окончании процесса формирования испытательной последовательности, Высо кий уровень сигнала уб производит

„ 5

сброс в нулевое состояние выходов ре- ги стр а 5 .

Каждый цикл формирования разбивается на три фазы.

В течение первой фазы цикла устройство формирует на выходах регистра 5 псевдослучайный код, Формирование этого кода происходит в результате сдвига вправо информации в регистре 5 и JQ одновременной записи сигнала с выхода элемента 6 четности в младший разряд регистра. Сдвиг информации в регистре происходит по переднему фронту импульса сигнала у4. Регистр 5 сдвига, oxi a- 5 ченный обратными связями, через элемент 6 четности выполняет функцию генератора псевдослучайных чисел.

В течение второй фазы цикла устройство формирует и записывает в регистр JQ 21 загрузочный байт информации, формирует на выходе элемента ИЛИ-НЕ 13 сигнал управления, устанавливает на входы шинного формирователя 7 код текущего коэффициента деления сигнала, 25 Происходит это следующим образом. В течение второй фазы цикла импульс сигнала у5 отсутствует, поэтому на выходе элемента И 15 присутствует нулевой сигнал, который обеспечивает ра- 30 боту блока 10 в режиме чтения. Сигналы с первых двух выходов регистра 5 поступают на адресные входы блока 0 и по адресным входам блока 22 проходят на входы дешифратора 35. При этом

в блоке 10 происходит выборка и чтение содержимого соответствующей ячейки } а в блоке регистров 22 дешифратором 35 разрешается запись информации в соответсвующий регистр. На од- ном из выходов дешифратора 11 устанавливается единичный сигнал. Сигналы с выходов блока 10 и дешифратора 11 поразрядно суммируются в сумматорах 18 по модулю два. Выходной восьмиразряд- ный сигнал блока 18 отличается от сигнала на выходе блока 10 только значением одного бита, номер которого указывает дешифратор П, Сигналы с выходов сумматора 18 по модулю два посту- пают на информационные входы регистра 21. Запись информации в регистр 21 происходит в период действия импульса сигнала у4, поступающего с выхода блока управления 4, Байт информации, за- писанный в регистр 21, называется загрузочным, так как в дальнейшем предназначен для загрузки в блок регистров 22, Одновременно с выходов регист5

JQ5JQ2530

35

JQ45дра 5 код поступает на адресные входы блоков 2 и 9, Из блоков 2 и 9 содержимое соответствующих ячеек памяти передается шинными формирователями 7 и 17 на входы соответственно регистра 12 и мультиплексора 19, Положительным потенциалом импульса сигнала у4 на тестовом входе регистра 12 производится запись параллельной информации в регистр 12. Эта информация поступает с выходов указанного регистра на входы преобразователя 14 кода и на входы элемента ИЛИ-НЕ 13, Преобразователь 14 кода преобразует входную информацию и передает ее на входы мультиплексора 19, Элемент ИЛИ-НЕ 13, анализируя состояние выходов регистра 12, формирует сигнал управления, который управляет выбором канала мультиплексора 19, и с помощью элемента И 15 управляет записью загрузочного байта в блок регистров 22 и в блок 10, Если сигнал управления с элемента ИЛИ-НЕ 13 равен нулю, на входы блока 7 в качестве кода текущего коэффициента дет ления сигнала устанавливается код с выходов преобразователя 14 кода. При этом запрещается запись загрузочного байта в блок 22 регистров и в блок 10, Если сигнал с выхода элемента ИЛИ-НЕ 13 равен единице, на входы блока 7 устанавливается код с выходов шинного формирователя 17, Это код эталонного (программно заданного) коэффициента деления сигнала, хранящегося в блоке 9, Кроме того, сигнал Элемента ИЛИ-НЕ , равный единице, разрешает запись в блок 22 регистров и в блок 10.

В течение третьей фазы цикла в устройстве производится запись в блок 2 кода текущего коэффициента деления и производится запись загрузочного байта в блок 22 регистров и в блок 10. Происходит это следующим образом. Импульс сигнала у5 с выхода блока 4 управления поступает нэ входы управления блоков 2 и 7 и на второй вход элемента И 15, При этом блок 2 и стыкующийся с ним шинный формирователь 7 переводятся в режим приема информации, В результате код текущего коэффициента записывается в блок 2, Одновременно импульс сигнала у5 проходит через- элемент И 15. С выхода указанного элемента И 15 импульс поступает на вход управления блока 10 и проходит на .входы синхронизации регистров 36, К

этому моменту времени на информационных входах блока 10 и регистров 36 установлен загрузочный байт информации. Он поступает на указанные входы с выходов регистра 21. Положительным потенциалом с выхода элемента И 15 осуществляется запись в блок 10 загрузочного байта. Загрузка в блок 22 производится передним фронтом импуль- . са сигнала с выхода элемента И 15. Информация в блоке 10 и в блоке 22 отличается от вновь сформированного загрузочного байта в регистре 21 только

значением одного бита. Поэтому при 1 записи в блок 22 регистров загрузочного байта информация изменяется только на одном выходе устройства. Например, если в рассматриваемом цикле формирования испытательной последователь-. ности на выходах регистра 5 сформировался псевдослучайный код, при сигнале на выходе Элемента ИЛИ-НЕ 13, равном единице, в блоке 22 произойдет изменение информации на одном выходе, 2

Таким образом, в течение каждого цикла формирования устройством испытательной последовательности на выходах регистра 5 генерируется псевдослучайный код, под воздействием кото- з рого в блоках 10, 11, 18 и 21 формируется загрузочный байт информации блоками 2, 7, 12 и 13 формируется сигнал, управляющий выбором канала мультиплексора 19 и записью загрузочного байта „ в блоки 22 и 10; производится запись в блок 2 кода текущего коэффициента деления сигнала, который формируется в зависимости от значения сигнала на выходе элемента ИЛИ-НЕ 13, либо преоб-д разователем 14 кода, либо блоком 9, и в заключении цикла в случае, если сигнал на выходе элемента ИЛИ-НЕ 13 равен единице, производится запись загрузочного байта в блоки 10 и 22. В 4 результате на соответствующем выходе устройства 28 происходит изменение информации.

Формула изобретения J

Устройство для формирования тестов, содержащее шифратор, генератор импульсов, блок управления, первый блок памяти, дешифратор, группу сум- маторов по модулю два, первый регистр, блок регистров, элемент четности и регистр сдвига, группу разрядных выходов которого соединена с входами элемента четности, выход которого подсоединен к входу последовательного ввода информации регистра сдвига, первый и второй разрядные выходы которого соединены с соответственно адресным входом первого блока памяти и адресным входом блока регистров, выходы последнего являются выходами устройства, входы управления считывания блока регистров и первого блока памяти подключены к первому входу шифратора, второй, третий и четвертый выходы которого соединены соответственно с первым, вторым и третьим входами блока управления, первый выход которого соединен с входами синхронизации регистра сдвига и первого регистра, выходы которого соединены с группами информационных входов устройства первого блока памяти, блока управления и блока регистров, вход синхронизации которого объединен1 с входом управления режимом первого блока памяти, информационные входы первого регистра подключены к выходам сумматоров по модулю два группы, первые входы которых подключены к соответствующим входам первого блока памяти, вторые выходы сумматоров по модулю два группы подключены к выходам дешифратора, выходы генератора импульсов соединен с четвертым входом блока управления, второй выход которого подсоединен к входу сброса регистра сдвига, третий, четвертый и пятый разрядные выходы которого соединен;. соответственно с первым, вторым и третьим входами дешифратора, вход управления считыванием первого регистра объединен с входом управления режимом работы регистра сдвига, пятый вход блока управления является входом синхронизации устройства, третий выход блока управления является выходом состояния устройства, входы шифратора являются первой группой входов режима устройства, отличающееся тем, что, с целью расширения области применения за счет возможности создания тестов для контроля объектов с функционально различными входами, в устройство введены второй и третий блоки памяти, три шинных формирователя, второй регистр, преобразователь кода, мультиплексор, два элемента И, элемент НЕ, элемент ИЛИ-НЕ, вторая группа входов режима устройства соединена с входами регистра сдвига, пятый выход шифратора подсоединен к входу выборки управления считывания первого регистра, шестой выход шифратора соединен с входами выборки второго и третьего блоков памяти, входом сброса второго регистра и входами выборки первого и второго шинных формирователей, седьмой выход шифратора соединен с входом выборки третьего шинного фор мирователя и через элемент НЕ с входом выборки мультиплексора и первым входом первого элемента И, информационные входы первой группы входов мультиплексора подсоединены к выходам первого шинного формирователя, информационные входы второй группы мультиплексора подключены к выходам преобразователя кода, входы которого соединены с входами элемента ИЛИ-НЕ и выходами второго регистра, выход эте- мента ИЛИ-НЕ соединен с входом управления режимом работы мультиплексора и первым входом второго элемента И, выход которого подсоединен к входу син- хронизации блока регистра, второй вход первого элемента И соединен с вторым входом второго элемента И,

0 5

5

0

,входами управления режимом работы ,третьего блока памяти и второго шинного формирователя и подключен к четвертому выходу блока управления, выход первого элемента И соединен с входами управления записи второго блока памяти и первого шинного формирователя, информационные входы-выходы которого подключены к соответствующим входам-выходам второго блока памяти, входы первого и третьего шинных формирователей объединены и подключены к информационным входам устройства, выходы мультиплеьсора и третьего шинного формирователя через монтажное ИЛИ подключены к входу второго шинного формирователя, лпресные входы второго и третьего блоков памяти подключены к младшим разрядным выходам регистра сдвига, информационные входы-выходы третьего блока памяти соединены С входами-выходами второго шинного формирователя, выходы которого соединены с информационными входами второго регистра, вход синхронизации которого соединен с входом синхронизации первого регистра.

а

Фиг.1

| Устройство для перемешивания жидкостей | 1978 |

|

SU866003A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-06-23—Публикация

1988-07-18—Подача