Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и поиска неисправностей в цифровых узлах, бло- с ках, типовых элементах замены.

Цель изобретения - расширение класса решаемых задач за счет увеличения режимов контроля,

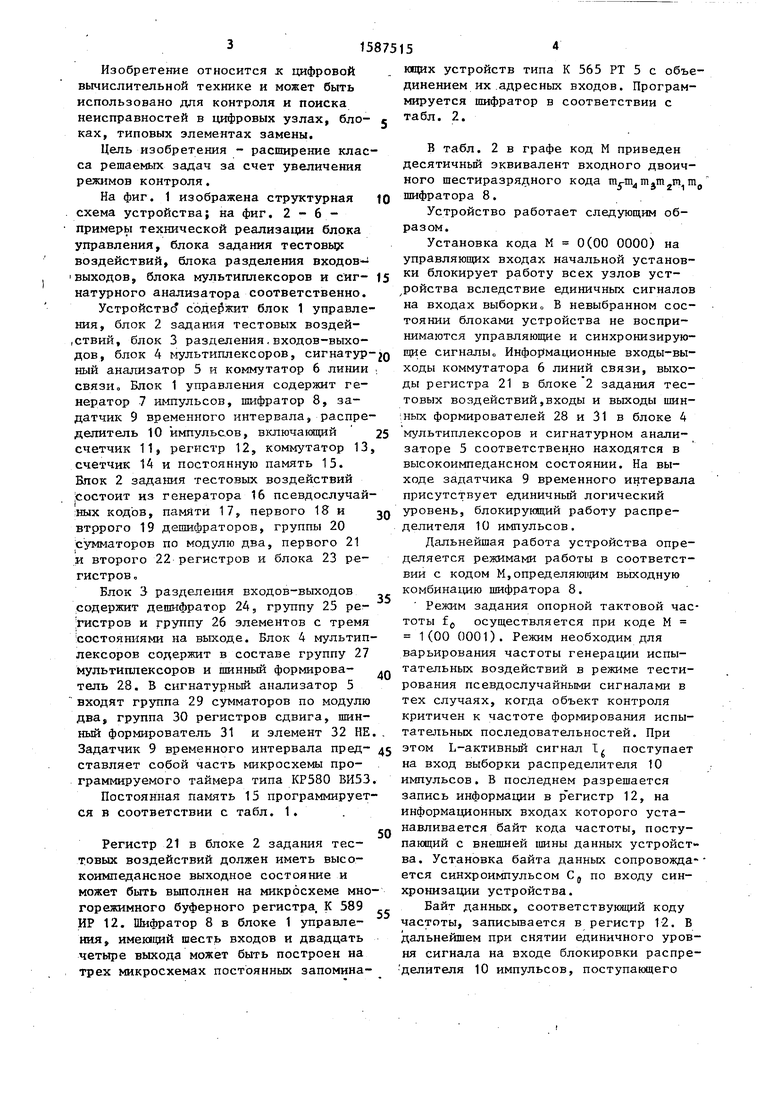

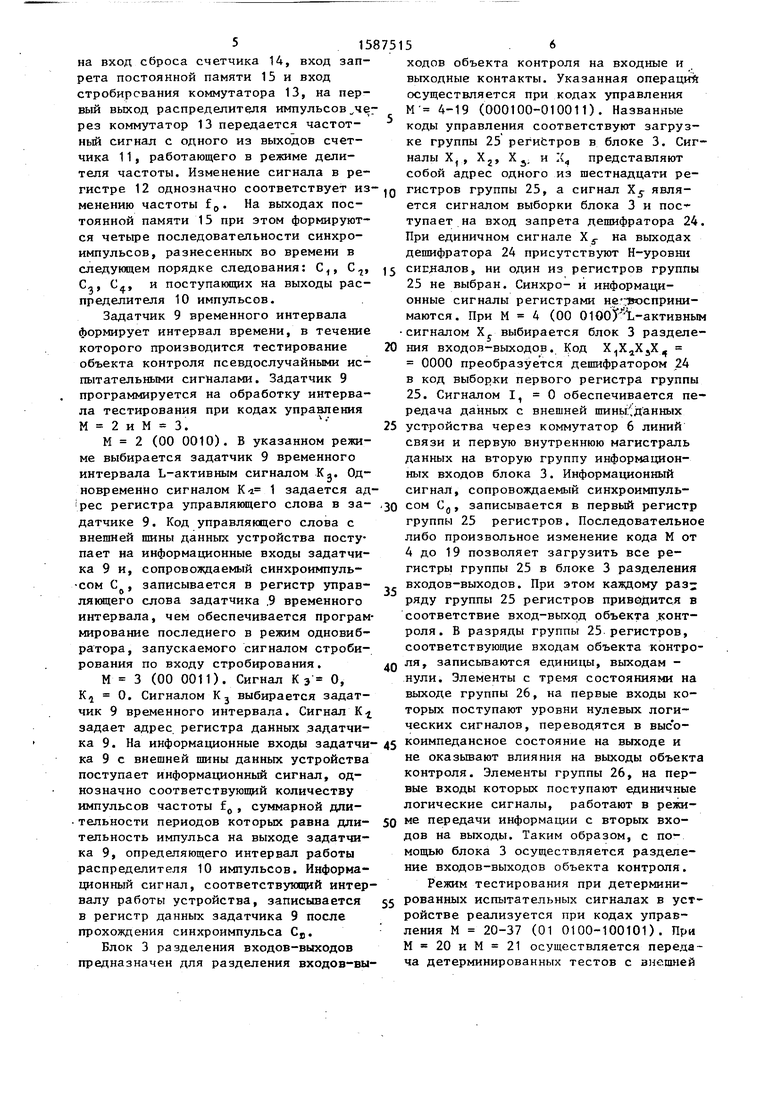

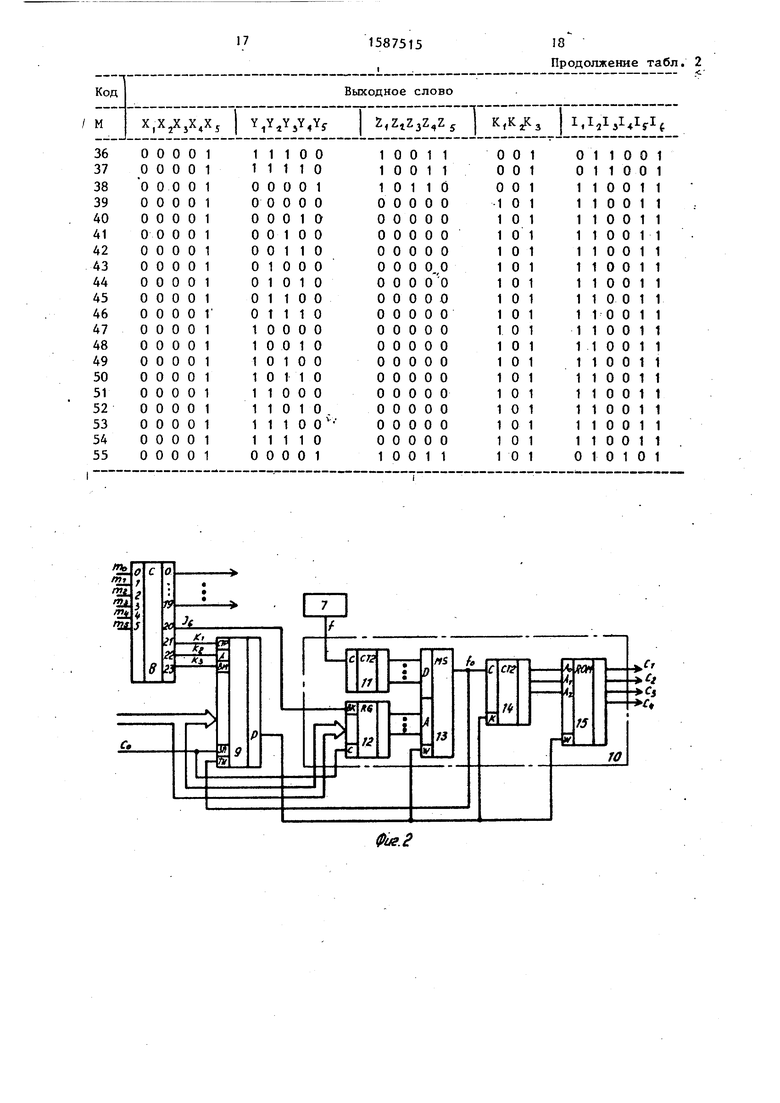

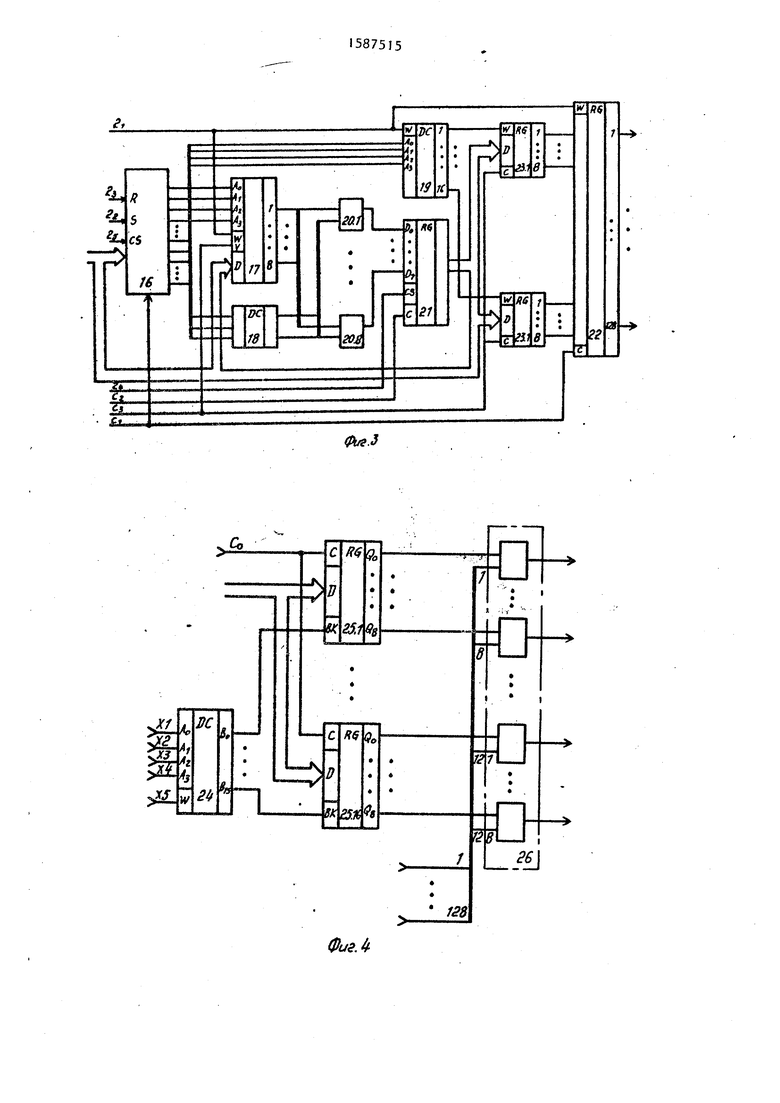

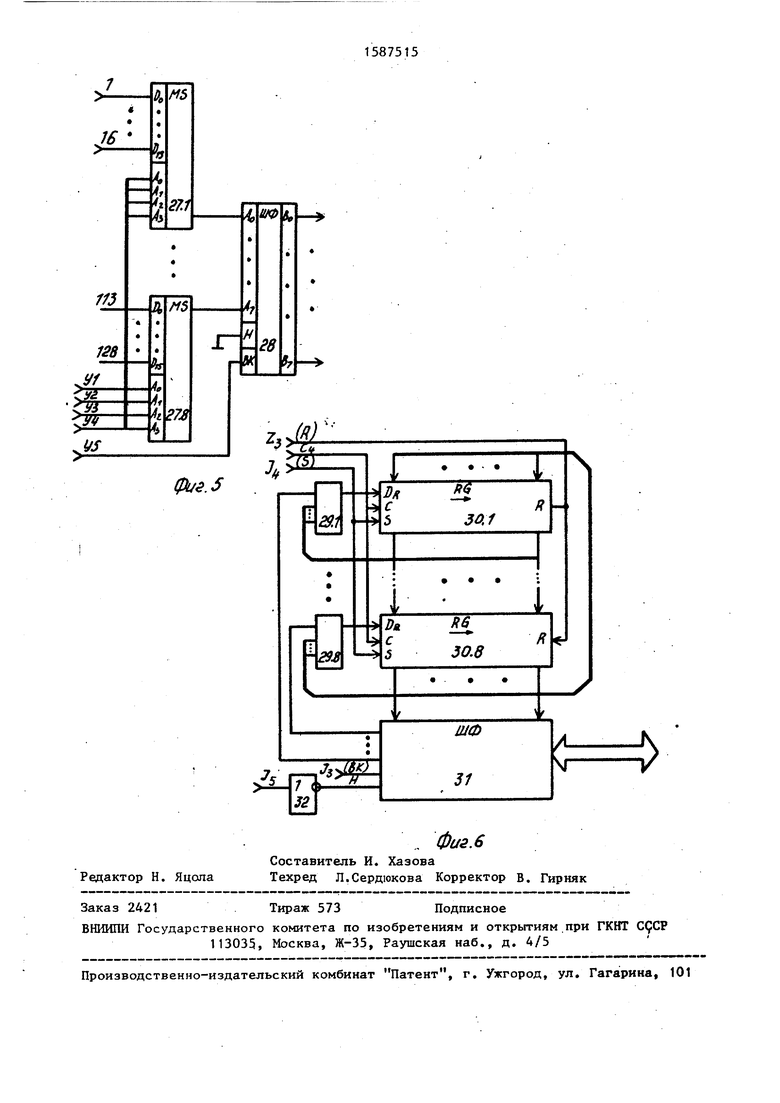

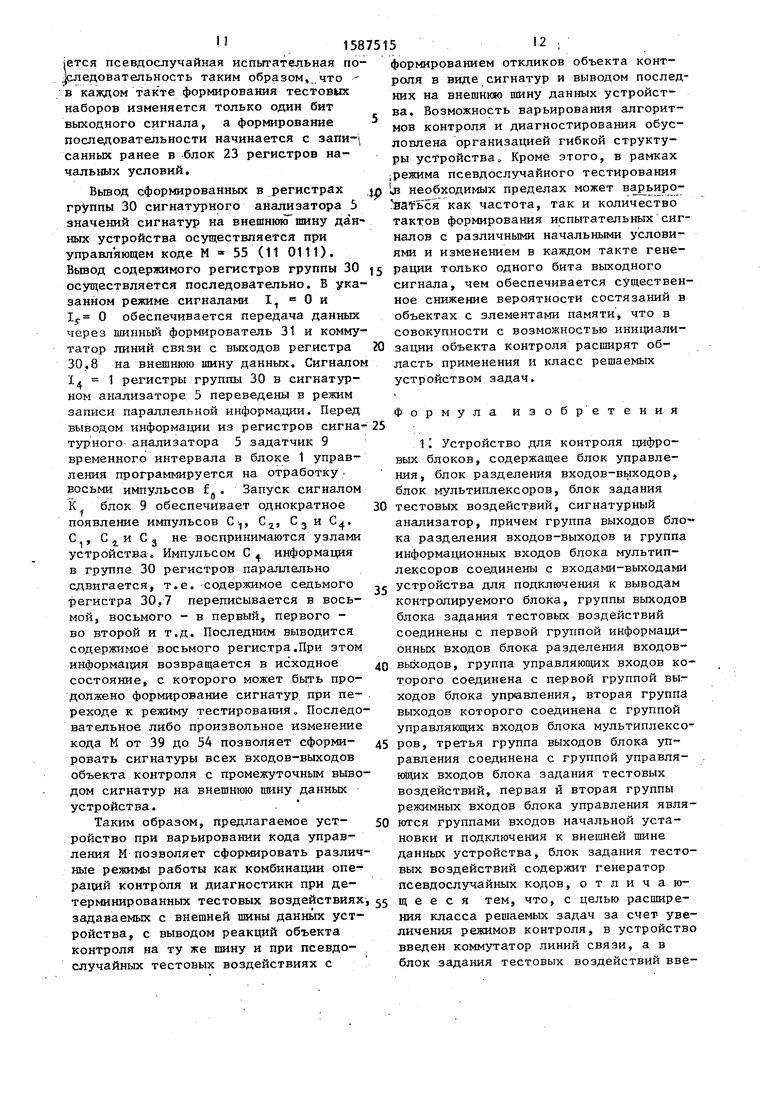

На фиг. 1 изображена структурная Ю схема устройства; на фиг. 2 - 6 - примеры технической реализации блока правления, блока задания тестовь с воздействий, блока разделения входов- ЫХОДОВ, блока мультиплексоров и сиг- 15 натурного анализатора соответственно.

Устройстве содержит блок 1 управления, блок 2 задания тестовых воздей- твий, блок 3 разделения,входов-выхоов, блок 4 г ультиплексоров, сиг на ный анализатор 5 и коммутатор 6 линии . связио Блок 1 управления содержит генератор 7 импульсов, шифратор 8, за- атчик 9 временного интервала, распреелитель 10 импульсов, включакщий 25 счетчик 11, регистр 12, коммутатор 13, счетчик 14 и постоянную память 15. Блок 2 задания тестовых воздействий состоит из генератора 16 псевдослучай- ных кодов, памяти 17, первого 18 и Q втррого 19 дешифраторов, группы 20 сумматоров по модулю два, первого 21 и второго 22 регистров и блока 23 регистров о

Блок 3 разделе1шя входов-выходов содержит дешифратор 24, группу 25 ре- гистров и группу 26 элементов с тремя состояниями на выходе. Блок 4 мультиплексоров содержит в составе группу 27 мультиплексоров и шинный формирова- .Q тель 28. В сигнатурный анализатор 5 входят группа 29 сумматоров по модулю два, группа 30 регистров сдвига, шинный формирователь 31 и элемент 32 НЕ. . Задатчик 9 временного интервала пред- 45 ставляет собой часть микросхемы программируемого таймера типа КР580 ВИ53.

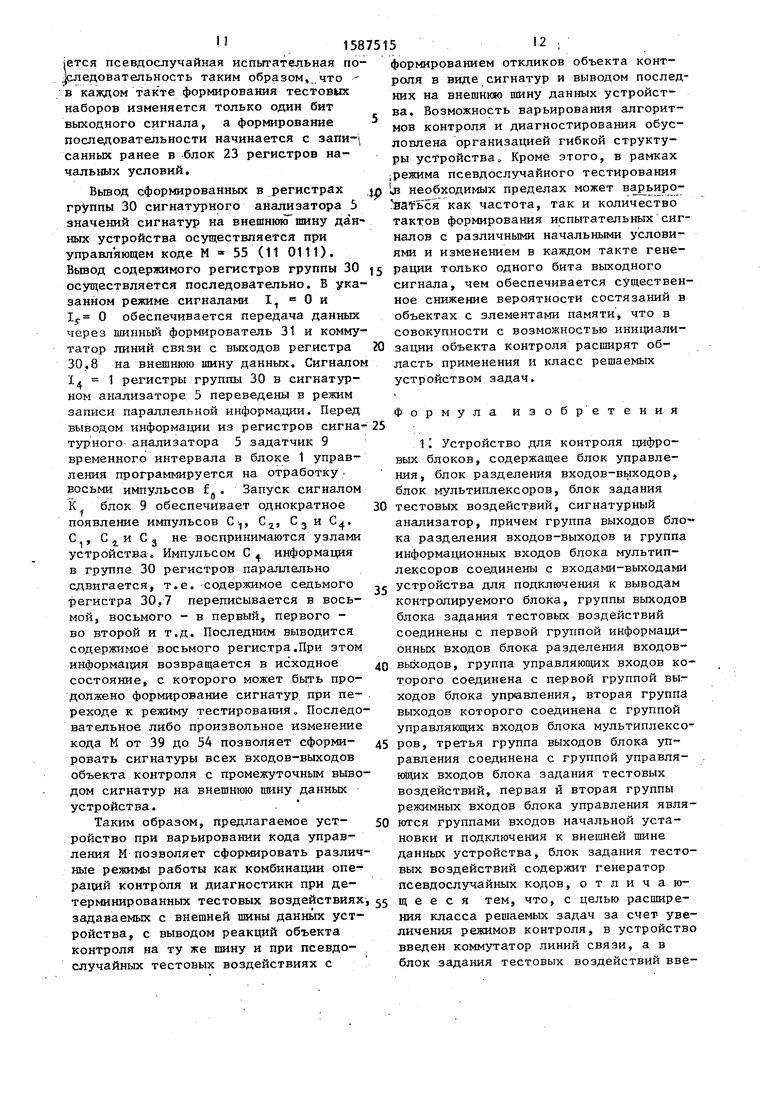

Постоянная память 15 программируется в соответствии с табл. 1.

50

Регистр 21 в блоке 2 задания тестовых воздействий должен иметь высо- коимпедансное выходное состояние и может быть выполнен на микросхеме многорежимного буферного регистра. К 589 ИР 12. Шифратор 8 в блоке 1 управления, имеющий шесть входов и двадцать четыре выхода может быть построен на трех микросхемах постоянных запомина- с

1387515

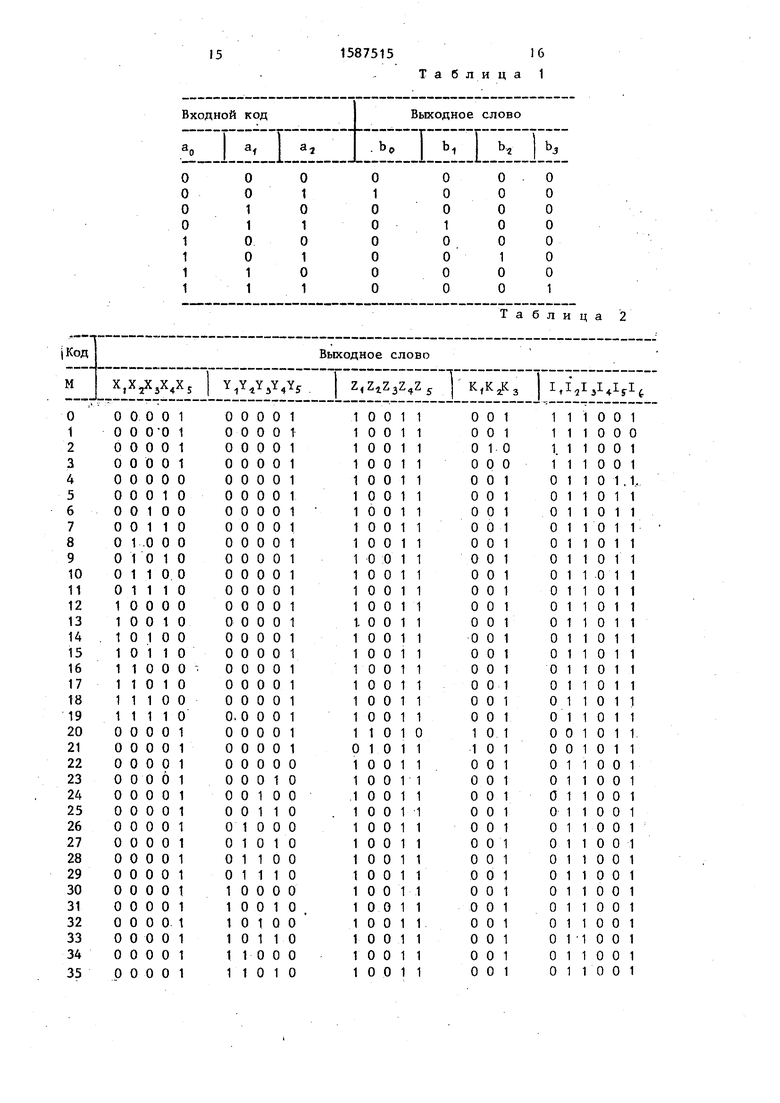

кщих устройств типа К 565 РТ 5 с объединением их .адресных входов. Программируется шифратор в соответствии с табл. 2.

В табл. 2 в графе код М приведен десятичньй эквивалент входного двоичного шестиразрядного кода т шифратора 8.

Устройство работает следующим образом.

Установка кода М 0(00 0000) на управляющих входах начальной установки блокирует работу всех узлов уст- ройства вследствие единичных сигналов на входах выборки В невыбранном состоянии блоками устройства не воспринимаются управляющие и синхронизирующие сигналы Инфор1мационные входы-выходы коммутатора 6 линий связи, выходы регистра 21 в блоке 2 задания тестовых воздействий,входы и выходы шин- ;ных формирователей 28 и 31 в блоке 4 мультиплексоров и сигнатурном анализаторе 5 соответственно находятся в высокоимпедансном состоянии. На выходе задатчика 9 временного интервала присутствует единичный логический уровень, блокирующий работу распределителя 10 импульсов.

Дальнейшая работа устройства определяется режимами работы в соответствии с кодом М,определяю:цим выходную комбинацию шифратора 8.

Режим задания опорной тактовой частоты f осуществляется при коде М 1(00 0001). Режим необходим для варьирования частоты генерации испытательных воздействий в режиме тестирования псевдослучайными сигналами в тех случаях, когда объект контроля критичен к частоте формирования испытательных последовательностей. При этом L-активньй сигнал 1 поступает на вход выборки распределителя 10 импульсов. В последнем разрешается запись информации в р егистр 12, на информационных входах которого устанавливается байт кода частоты, поступающий с внешней шины данных устройства. Установка байта данных сопровожда ется синхроимпульсом С по входу синхронизации устройства.

Байт данных, соответствукиций коду частоты, записьшается в регистр 12. В дальнейшем при снятии единичного уровня сигнала на входе блокировки распре делителя 10 импульсов, поступавощего

515

на вход сброса счетчика 14, вход запрета постоянной памяти 15 и вход стробирсвания коммутатора 13, на первый выход распределителя импульсов че рез коммутатор 13 передается частотный сигнал с одного из выходов счетчика 11, работающего в режиме делителя частоты. Изменение сигнала в регистре 12 однозначно соответствует из менению частоты f. На выходах постоянной памяти 15 при этом формируются четыре последовательности синхроимпульсов, разнесенных во времени в следующем порядке следования: С, С,, Сд, С, и поступаюпщх на выходы распределителя 10 импульсов.

Задатчик 9 временного интервала формирует интервал времени, в течение которого производится тестирование объекта контроля псевдослучайными испытательными сигналами, Задатчик 9 программируется на обработку интервала тестирования при кодах управления М 2 и М 3.

М 2 (00 0010). В указанном режиме выбирается задатчик 9 временного интервала L-активным сигналом Kg. Одновременно сигналом К 1 задается ад рес регистра управляющего слова в за- датчике 9. Код управляющего слова с внешней шины данных устройства поступает на информационные входы задатчи- ка 9 и, сопровождаемый синхроимпуль- сом С, записывается в регистр управ- лянмцего слова задатчика ,9 временного интервала, чем обеспечивается программирование последнего в режим одновиб- ратора, запускаемого сигналом строби- рования по входу стробирования.

М 3 (00 0011). Сигнал Кэ О,

К 0. Сигналом К выбирается задат- чик 9 временного интервала. Сигнал К- задает адрес регистра данных задатчика 9. На информационные входы задатчи- ка 9 с внешней шины данных устройства поступает информационный сигнал, однозначно соответствующий количеству импульсов частоты f, суммарной длительности периодов которых равна дли- тельность импульса на выходе задатчика 9, определяющего интервал работы распределителя 10 импульсов. Информационный сигнал, соответствующий интервалу работы устройства, записывается в регистр данных задатчика 9 после прохождения синхроимпульса Сд.

Блок 3 разделения входов-выходов предназначен для разделения входов-вы

5. 6

ходов объекта контроля на входные и выходные контакты. Указанная операций осуществляется при кодах управления М- 4-19 (000100-010011). Названные коды управления соответствуют загрузке группы 25 региЬтров в блоке 3. Сигналы X, , Xj, X д, и Х представляют собой адрес одного из шестнадцати регистров группы 25, а сигнал является сигналом выборки блока 3 и пос- тупает на вход запрета дешифратора 24. При единичном сигнале на выходах дешифратора 24 присутствуют Н-уровни сиЕлалов, ни один из регистров группы 25 не выбран. Синхро- и информационные сигналы регистрами не : сприни- маются. При М 4 (00 ОТОО Х-активным сигналом Х- выбирается блок 3 разделе- кия входов-выходов. 1|;од ,iXjX 0000 преобразуется дешифратором 24 в код выборки первого регистра группы

0

5

5

0

З 0

25. Сигналом I, О обеспечивается передача данных с внешней шины д анных устройства через коммутатор 6 линий связи и первую внутреннюю магистраль данных на вторую группу информационных входов блока 3. Информационный сигнал, сопровождаемый синхроимпульсом Cj, записывается в первый регистр группы 25 регистров. Последовательное либо произвольное изменение кода М от 4 до 19 позволяет загрузить все регистры группы 25 в блоке 3 разделения входов-выходов. При этом калщому раз; ряду группы 25 регистров приводится в соответствие вход-выход объекта контроля. В разряды группы 25 регистров, соответствующие входам объекта контроля, записьшаются едини1ц 1, выходам - нули. Элементы с тремя состояниями на выходе группы 26, на первые входы которых поступают уровни нулевых логических сигналов, переводятся в выс о- коимпедансное состояние на выходе и не оказывают влияния на выходы объекта контроля. Элементы группы 26, на первые входы которых поступают единичные логические сигналы, работают в режиме передачи информации с вторых входов на выходы. Таким образом, с помощью блока 3 осуществляется разделение входов-выходов объекта контроля. Режим тестирования при детерминированных испытательных сигналах в устройстве реализуется при кодах управления М 20-37 (01 0100-100101). При М 20иМ 21 осуществляется передача детерминированных тестов с анешней

шины данных устройства на входы объек- , та Остальные коды соответствуют выводу на внешнюю шину данных устройства реакций объекта контроля на детер- минированный тест.

М 20 (01 0100). Режим позволяет записать в генератор 16 псевдослучайных кодов информацию с внешней шины данных устройства, соответствующую JQ коду выборки одного из регистров блока 23. При этом сигналами I, 0; Ij 0; Ij 1 обеспечивается передача данных с внешней шины данных устдешифратора 19 и адресные входы памяти 17. Дешифратор 19 формирует сигнал выборки одного из регистров блока 23. Предварительно на внешней шине данных устанавливается байт данных,-а задат- чик 9 запрограммирован на обработку восьми импульсов fo. Сигналом К за-, пускается задатчик 9, Распределитель 10 импульсов формирует последовательность из четырех импульсов. Импульсом С содержимые блока 23 регистров пе- реписьшаются в регистр 22.С не воспринимается генератором 16 псевдослуройства через коммутатор 6 линий свя- j чайных кодов, а С не воспринимается

зи на вторую внутреннюю магистраль данных. Сигнал Z 1 обеспечивает работу генератора 16 псевдослучайных кодов в режиме записи параллельного

регистром 21. Импульсом Cj осущест- вляется запись байта данных, поступающего с внешней шины данных через коммутатор 6 линий связи на информациОнЗадатчик 9 временного интервала 20 le входы блока 23 регистров, в выбкода,

предварительно запрограммирован на обработку восьми импульсов частоты , а на внешнюю пину данных предварительно выведена записываемая в генератор 16 информация. Одновременно с установкой сигналов 1,12, iy формируется сигнал К, запускающий задатчик- 9. На .выходе задатчика 9 формируется нулевой сигнал Р, разре- шакщий работу распределителя 10 импульсов в течение восьми периодов частоты fQ. На выходах распределителя 10 импульсов формируются четыре разнесенных во времени синхроимпульса С:,, С, Cj, Cj, Синхроимпульсом С, осуществляется запись информации в генератор 16 псевдослучайных кодов. Остальные синхроимпульсы не воспринимаются блоками устройства, так как последние находятся в невыбранном - 40 состоянии. С. также не воспринимается регистром 22. Последовательное прохождение заднего и переднего фронтов . сигнала Р сигнализирует об обработранньй регистр и ячейку памяти 17 с одноименным адресом. С выходов регистра 22 информация, записанная в блок.-. 23 регистров в предьщущем такте форми25 рования испытательного сигнала, через и Zf блок 3 разделения входов-выходов передается на входы объекта контроля. Запись при управляющем коде М , 20 в генератор 16 псевдослучайных кодов

30 другого значения позволяет при коде М 21 осуществить запись информации в любой из регистров блока 23 и передать указанную информащю на объект контроля. Информация, записанная в гистры блока 23, дублируется в ячейках памяти 17.

Анализ реак.ций объекта контроля .осуществляется при М 22-37 (01 0110- 10 0101) .При этом сигналами 1, О и

ке заданного временного интервала. Из-45 ;блоке 4 мультиплексоров. Код

Ij О обеспечивается передача данных с выходов блока 4 мультиплексоров через коммутатор 6 линий связи на внешнюю шину данных. Сигналом Y выбирается шинный Формирователь 28 в

.

менение информационного сигнала внешней шины данных осуществляется только при е,циничном уровне Р в режиме с кодом М 20, так же как и в остальных режимах, сопровождаемых запуском задатчика 9 временного интервала.

М 21 (01 0101). Режим обеспечивает передачу данных с внешней шины данных устройства на объект контроля.

50

соответствует адресу байта, передаваемого с входов блока 4 мультиплексоров на внешнюю шину данньпс. Изменение кода управления М от 22 до 37 позволяет последовательно вывести на внешнюю шину данных полную информацию о состоянии входов-выходов объекта контроля. г

Для начальной установки генератоСигналом Z О выбирается регистр 22,55 16 псевдослучайных кодов в блоке

.-«л-Л ач1-г з т ггтст rfr i irr r Taurv ппЬгтойг т DWU ы- т о

память 17 и дешифратор 19 в блоке 2 задания тестовых воздействий. Сигнал, ранее записанньш в генератор 16 псевдослучайных кодов поступает на входы

2 задания тестовых воздействий и- регистров 30 группы в сигнатурном анализаторе 5 предусмотрен режим с управ- лякщим кодом М 38 (10 0110). При

дешифратора 19 и адресные входы памяти 17. Дешифратор 19 формирует сигнал выборки одного из регистров блока 23. Предварительно на внешней шине данных устанавливается байт данных,-а задат- чик 9 запрограммирован на обработку восьми импульсов fo. Сигналом К за-, пускается задатчик 9, Распределитель 10 импульсов формирует последовательность из четырех импульсов. Импульсом С содержимые блока 23 регистров пе- реписьшаются в регистр 22.С не воспринимается генератором 16 псевдослучайных кодов, а С не воспринимается

регистром 21. Импульсом Cj осущест- вляется запись байта данных, поступающего с внешней шины данных через коммутатор 6 линий связи на информациОн;блоке 4 мультиплексоров. Код

Ij О обеспечивается передача данных с выходов блока 4 мультиплексоров через коммутатор 6 линий связи на внешнюю шину данных. Сигналом Y выбирается шинный Формирователь 28 в

.

блоке 4 мультиплексоров. Код

соответствует адресу байта, передаваемого с входов блока 4 мультиплексоров на внешнюю шину данньпс. Изменение кода управления М от 22 до 37 позволяет последовательно вывести на внешнюю шину данных полную информацию о состоянии входов-выходов объекта контроля. г

Для начальной установки генерато 16 псевдослучайных кодов в блоке

ач1-г з т ггтст rfr i irr r Taurv ппЬгтойг т DWU ы- т о

2 задания тестовых воздействий и- регистров 30 группы в сигнатурном анализаторе 5 предусмотрен режим с управ- лякщим кодом М 38 (10 0110). При

- 1587515 О

осуществляется ка- 15 псевдослучайных кодов поступают нд

адресные входы памяти 17 и дешифрато ра 19, чем обеспечивается опрос адресуемой ячейки памяти 17 и разрешение записи в один из регистров блока 23. На одном из выходов второго дешифратора 18 устанавливается единичный сигнал в

/.-, ., ,, „.„чсоответствии со значением сигналов на

(10 0111-11 0110).В указанньк режимах ,о

осзлцествляется генерация псевдослучайных тестовых воздействий блоком 2 и . передача их на объект контроля с одновременной сверткой откликов одного из байтов входных-выходных сигналов объекта сигнатурным анализатором 5.

этом сигналом Z, 1

чальная установка указанных регистров.

Тестирование объекта контроля с помощью псевдослучайных испытательных сигналов и сверткой откликов объекта контроля сигнатурным анапи- jB TopoM 5 осуществляется при входных управляющих сигналах М 39 - 54

его входах, подключенных к трем из оставшихся, свободными выходов генератора 16. Сигналы с выходов памяти 17 и дешифратора 18 поразрядно суммируются группой 20 сумматоров по модулю 15 два-, В результате, выходной сигнал группы 20 сумматоров по модулю два отличается от сигнала на выходе памяти 1 7 значением только одного,бита, номер которого указьшает дешифратор 18. Сигнал с выходов группы 20 сумматоров по модулю два поступает на информационные входы регистра 21. Им- пульсом С, указанный сигнал записывается в регистр 21 и с его вькодов посДля работы в указанных режимах предварительно в режиме при М 38 осуществляется начальная установка генератора 16 псевдослучайных кодов в блоке 2 и обнуляются регистры группы 30 в сигнатурном анализаторе 5.

При управляюп1ем коде М 39 шины данных устройства функционируют разего входах, подключенных к трем из оставшихся, свободными выходов генератора 16. Сигналы с выходов памяти 17 и дешифратора 18 поразрядно суммируются группой 20 сумматоров по модулю 15 два-, В результате, выходной сигнал группы 20 сумматоров по модулю два отличается от сигнала на выходе памяти 1 7 значением только одного,бита, номер которого указьшает дешифратор 18. Сигнал с выходов группы 20 сумматоров по модулю два поступает на информационные входы регистра 21. Им- пульсом С, указанный сигнал записывается в регистр 21 и с его вькодов пос20

дельно без обмена информацией. Сигнал 25 упает на информационные входы памяти 1у - 1 обеспечивает передачу информа- 7 и входы блока 23 регистров. Импуль

сом Сэ, следующим во времени за импульсом С2, сигнал с выходов, регистра

ции с выходов блока 4 мультиплексоров на входы сигнатурного анализатора 5. Сигнал Z О разрешает работу гене21 записывается в ранее адресованную

21 записывается в ранее адресованную

ратора 16 в режиме формирования псев- ЗО ячейку памяти 17 ив выбранный регистр

блока 23.

дослучайных кодов. Сигналы Z О,

Z4

О и Zj о обеспечивают работу блока 2 в режиме генерации псевдослучайных испытательных сигналов. Задат,- чик 9 временного интервала в блоке 1 управления предварительно запрограммирован на обработку требуемого количества тактов формирования испытательной выходной последовательности. Число, записанное в задатчик 9 должно быть кратно восьми. Тогда число тактов выходной последовательности п

Тестовая комбинация с выходов регистра 22 через блок 3 разделения вхо, дов-выходов передается на объект контроля.Причем тестовая комбинация,поступающая на объект в первом такте формирования испытательнойпсевдослучайной пос- iледовятбшьности,представляет собой на-

40 бор начальных условий,предваряющих псевдослучайный т ее т. Байт информации с входов-выходов объекта контроля через блок

f(,/8. Одновременно с установкой наз- 4 мультиплексоров и коммутатор 6 лини

его входах, подключенных к трем из оставшихся, свободными выходов генератора 16. Сигналы с выходов памяти 17 и дешифратора 18 поразрядно суммируются группой 20 сумматоров по модулю ва-, В результате, выходной сигнал группы 20 сумматоров по модулю два отличается от сигнала на выходе памяти 1 7 значением только одного,бита, номер которого указьшает дешифратор 18. Сигнал с выходов группы 20 сумматоров по модулю два поступает на инормационные входы регистра 21. Им- пульсом С, указанный сигнал записывается в регистр 21 и с его вькодов пос

упает на информационные входы памяти 7 и входы блока 23 регистров. Импуль

21 записывается в ранее адресованную

ячейку памяти 17 ив выбранный регистр

Тестовая комбинация с выходов регистра 22 через блок 3 разделения входов-выходов передается на объект контро ля.Причем тестовая комбинация,поступающая на объект в первом такте формирования испытательнойпсевдослучайной пос- iледовятбшьности,представляет собой на-

бор начальных условий,предваряющих псевдослучайный т ее т. Байт информации с входов-выходов объекта контроля через блок

| название | год | авторы | номер документа |

|---|---|---|---|

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Устройство для контроля логических блоков | 1987 |

|

SU1432529A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Автоматизированная система тестового контроля и диагностирования цифровых микропроцессорных блоков | 1989 |

|

SU1705782A1 |

| Многоканальный сигнатурный анализатор | 1990 |

|

SU1714605A1 |

| Устройство для формирования тестов | 1986 |

|

SU1336013A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для формирования тестов | 1990 |

|

SU1800458A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля и поиска неисправностей в цифровых узлах, блоках, типовых элементах замены. Цель изобретения - расширение класса решаемых задач за счет увеличения режимов контроля. Устройство содержит блок 1 управления, блок 2 задания тестовых воздействий, блок 3 разделения входов-выходов, блок 4 мультиплексоров, сигнатурный анализатор 5, коммутатор 6 линии связи. Устройство при варьировании кода управления М позволяет сфорсировать различные режимы работы как комбинации операций контроля и диагностики при детерминированных тестовых воздействиях, задаваемых с внешней шины данных устройства, с выводом реакций объема контроля на ту же шину и при псевдослучайных тестовых воздействиях с формированием откликов объекта контроля в виде сигнатур и выводом последних на внешнюю шину данных. 1 з.п. ф-лы, 2 табл., 6 ил.

ванных сигналов сигналом К., запускается задатчик 9. Сигнал Р на его выходе устанавливается в нулевое состояние, разрешая работу распределителя 10 импульсов в режиме формирования последовательности синхроимпульсов

С, С, Cj, С. Импульсом С осзпцест- вляется запись информации с выходов блока 23 регистров в регистр 22.

Указанная информация представляет собой набор начальных условий и за- дается в режимах с управлякщими кодами М 20 и М 21. Одновременно импульсом С синхронизируется генератор 16 псевдослучайных кодов. Сигналы с выходов мпадпшх разрядов генератора

-связи поступает на входы сигнатур1Гого д5 анализатора 5, в котором после прохождения импульса С 4 начинается формирование восьми сигнатур. При этом информация с входов сигнатурного анализатора 5 через шинный формирователь 50 31 поступает на первые входы сумматоров по модулю два группы 29. Процесс генерации псевдослучайной испытательной последовательности и формирования сигнатур повторяется в течение п тактов. По окончании п тактов в регистрах группы 30 сигнатурного анализатора сформированы сигнатуры восьми входов- выходов объекта контроля. В указанном режиме на входах регистра 22 формиру55

ieTCH псевдослучайная испытательная по- ,рледовательность таким образом, что - в каждом такте формирования тестовых наборов изменяется только один бит выходного сигнала, а формирование последовательности начинается с запи- санных ранее в блок 23 регистров начальных условий.

Вьшод сформированных в регистрах группы 30 сигнатурного анализатора 5 значений сигнатур на внешннло шину данформированием откликов объекта контроля в виде сигнатур и выводом последних на внешнюю шину данных устройства. Возможность варьирования алгоритмов контроля и диагностирования обусловлена организацией гибкой структуры устройства о Кроме этого, в рамках Iрежима псевдослучайного тестирования 4р 1л необходимых пределах может вар ьиро- ВЯ гься как частота, так и количество тактов формирования испытательных сигналов с различными начальными условиями и изменением в каждом такте гененых устройства осуществляется при управляющем коде М 55 (11 0111). Вьшод содержимого регистров группы 30 5 рации только одного бита выходного осуществляется последовательно. В ука- сигнала, чем обеспечивается существен- занном режиме сигналами I, О и ное снижение вероятности состязаний в

объектах с элементами памяти, что в совокупности с возможностью инициализации объекта контроля расширят об1,. О обеспечивается передача данных через шинньв формирователь 31 и коммутатор линий связи с выходов регистра 20 30,8 на внешнюю шину данных. Сигналом I. 1 регистры группы 30 в сигнатурном анализаторе 5 переведены в режим записи параллельной информации. Перед выводом информации из регистров сигна- 25 турного анализатора 5 задатчик 9 временного интервала в блоке 1 управления программируется на отработку

ласть применения и устройством задач.

класс решаемых

восьми импульсов f . Запуск сигналом

Формула изобретения

блок мультиплексоров, блок задания 30 тестовых воздействий, сигнатурный

К блок

9 обеспечивает однократное

Сз и

появление импульсов С , Cj, С , Cg не воспринимаются узлами устройства. Импульсом С информация в группе 30 регистров параллельно сдвигается, т.е. содержимое седьмого регистра 30,7 переписывается в восьмой, восьмого - в первый, первого - во второй и т.д. Последним выводится содержимое восьмого регистра.При этом информатщя возвращается в исходное состояние, с которого может быть продолжено формирование сигнатур при переходе к режиму тестирования„ Последовательное либо произвольное изменение кода М от 39 до 54 позволяет сформировать сигнатуры всех входов-выходов объекта контроля с промежуточным выводом сигнатур на внешнюю шину данных устройства.

Таким образом, предлагаемое уст- ройство при варьировании кода управления М позволяет сформировать различные режимы работы как комбинации опе- раций контроля и диагностики при детерминированных тестовых воздействиях задаваемых с внешней шины данных устройства, с выводом реакций объекта контроля на ту же шину и при псевдо- случайных тестовых воздействиях с

формированием откликов объекта контроля в виде сигнатур и выводом последних на внешнюю шину данных устройства. Возможность варьирования алгоритмов контроля и диагностирования обусловлена организацией гибкой структуры устройства о Кроме этого, в рамках Iрежима псевдослучайного тестирования р 1л необходимых пределах может вар ьиро- ВЯ гься как частота, так и количество тактов формирования испытательных сигналов с различными начальными условиями и изменением в каждом такте гене5 рации только одного бита выходного сигнала, чем обеспечивается существен- ное снижение вероятности состязаний в

ласть применения и устройством задач.

класс решаемых

ормула изобретения

блок мультиплексоров, блок задания тестовых воздействий, сигнатурный

анализатор, причем группа выходов блока разделения входов-выходов и группа информационных входов блока мультиплексоров соединены с входами-выходами устройства для подключения к выводам контролируемого блока, группы выходов блока задания тестовых воздействий соединены с первой группой информационных входов блока разделения входов- выходов, группа управляющих входов ко- т.орого соединена с первой группой выходов блока управления, вторая группа выходов которого соединена с группой управляющих входов блока мультиплексо- ров, третья группа выходов блока управления соединена с группой управляющих входов блока задания тестовых воздействий, первая и вторая группы режимных входов блока управления являются группами входов начальной установки и подключения к внешней шине данных устройства, блок задания тестовых воздействий содержит генератор псевдослучайных кодов, отличающееся тем, что, с целью расширения класса решаемых задач за счет увеличения режимов контроля, в устройство введен коммутатор линий связи, а в блок задания тестовых воздействий вве

дены память, два дешифратора, группа сумматоров по модулю два, два регистра и блок регистров, причем в устройстве группа управляющих входов коммутатора линий связи.соединена с четвертой группой выходов .блока управления, синхровход которого является син хровходом устройства, первая, вторая, и третья группа информационных входов - выходов коммутатора линий связи соединены соответственно с группой информационных входов-выходов сигнатурного анализатора, второй группой информационных входов блока разделе- кия входов-выходов и группой информационных входов-выходов блока задания тестовых воздействий, группа выходов блока мультиплексоров соединена с группой информационных входов коммутатора линий связи, четвертая группа информационных входов-выходов которого подключена к группе входов-выходов устройства для подключения к внешней шине данных, синхровход блока р&зде- ления входов-выходов соединен с син- хровходом устройства, а в блоке задания тестовых воздействий группа выходов первого регистра является группой выходов блока, а группа информационных входов соединена с группой выходов блока регистров, группа входов выбора регистра которого соединена с группой выходов первого дешифратора, группа информационных входов которого соединена с первой группой выходов генератора псевдослучайного кода и группой адресных входов памяти, группа информационных входов которой, группы информационных входов генератора псевдослучайного кода и блока регистров и группа выходов второго регистра образуют группу информационных входов-выходов блока задания тестовых воздействий, выходы памяти и выходы второго дешифратора соединены - соответственно с первьми и вторыми входа

ми сумматоров по модулю два группы, выходы которых соединены с информаци - онными входами второго регистра, входы второго дешифратора соединены с второй группой выходов генератора псевдослучайного кода, синхровход, входы сброса, установки, выборки генератора псевдослучайного кода, объединенные стробирующие входы памяти и первого дешифратора, вход разрешения памяти,/синхровходы, входы выборки первого и второго регистров, синхровход блока регистров образуют группу ,управляю1цих входов блока задания тестовых воздействий, входы синхроимпульсов, установки, сброса и разрешения сигнатурного анализатора соединены с пятой группой выходов блока управления .

2 о Устройство по п. 1, отличающееся тем, что блок управления содержит генератор импульсов, распределитель импульсов, задатчик . времеиного интервала и шифратор, причем генератора импульсов соединен с входом опорной частоты распределителя импульсов, вход выборки, синхроаход и вход режима которого соединены с еоотйвтствующим выходом шифратора, синхровходом блока и выходом эадатчика аременног-о интервала, а первый выход - с входом опорной частоты аадатчйка временного интервала, группы кодовых входов задатчика временного интервала и распределителя импульсов образуют вторую группу режимных входов блока, первая группа режимных входов блока соединена с группой входов шифратора, выходы которого соединены со стробирующим, адресным, разрешающим входами задатчика временного интервала и в совокупности с групгтой выходов распределителя импульсов образуют первую, вторую, третью и четвертую группы выходов блока.

ФигЛ

| Устройство для контроля времени выполнения программ | 1984 |

|

SU1223235A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-04-27—Подача