Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики цифровых устройств.

Целью изобретения является повышение достоверности контроля.

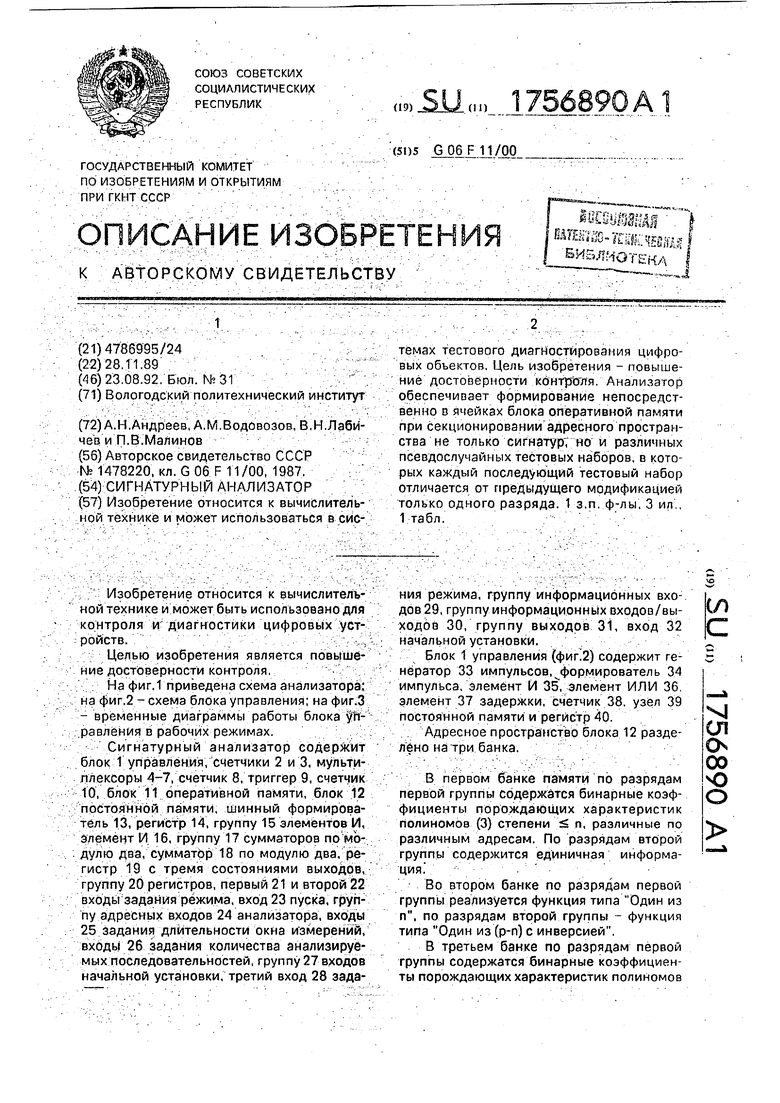

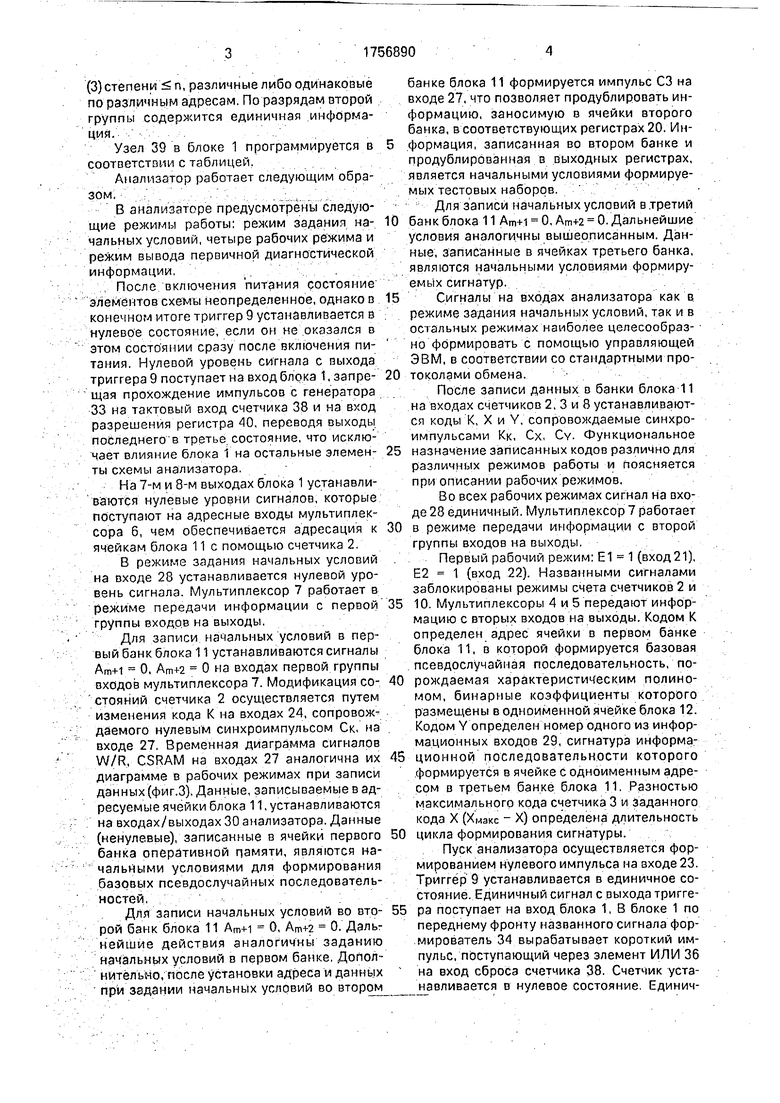

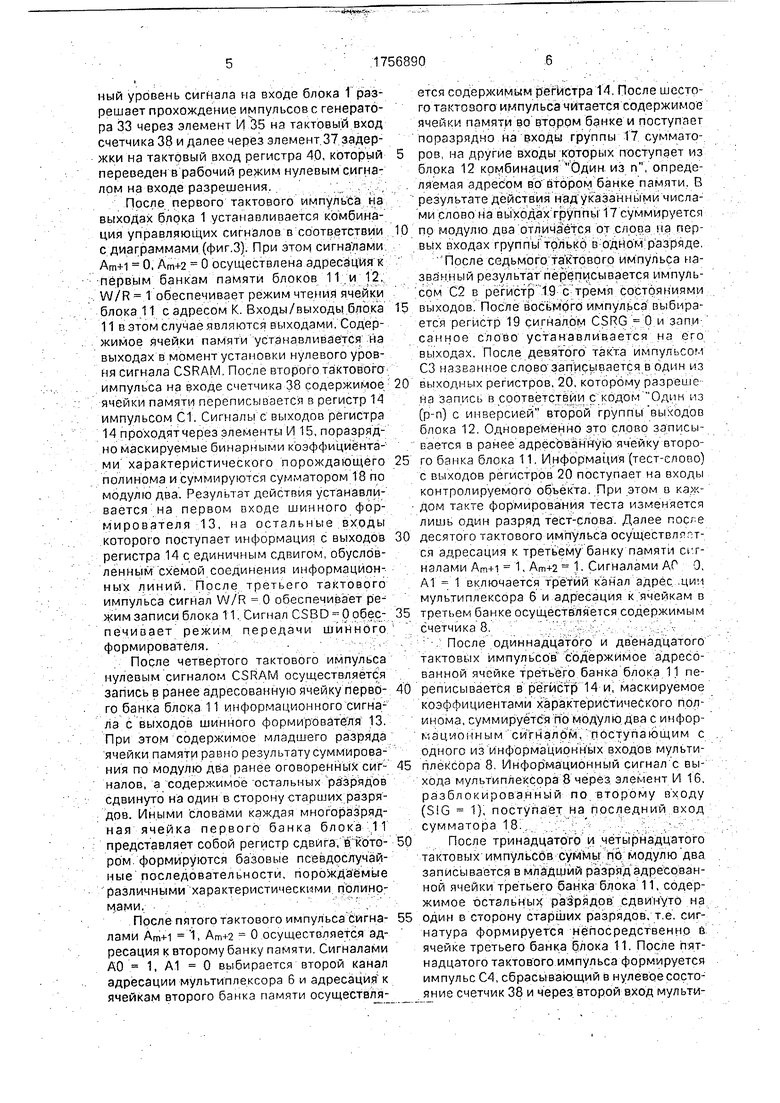

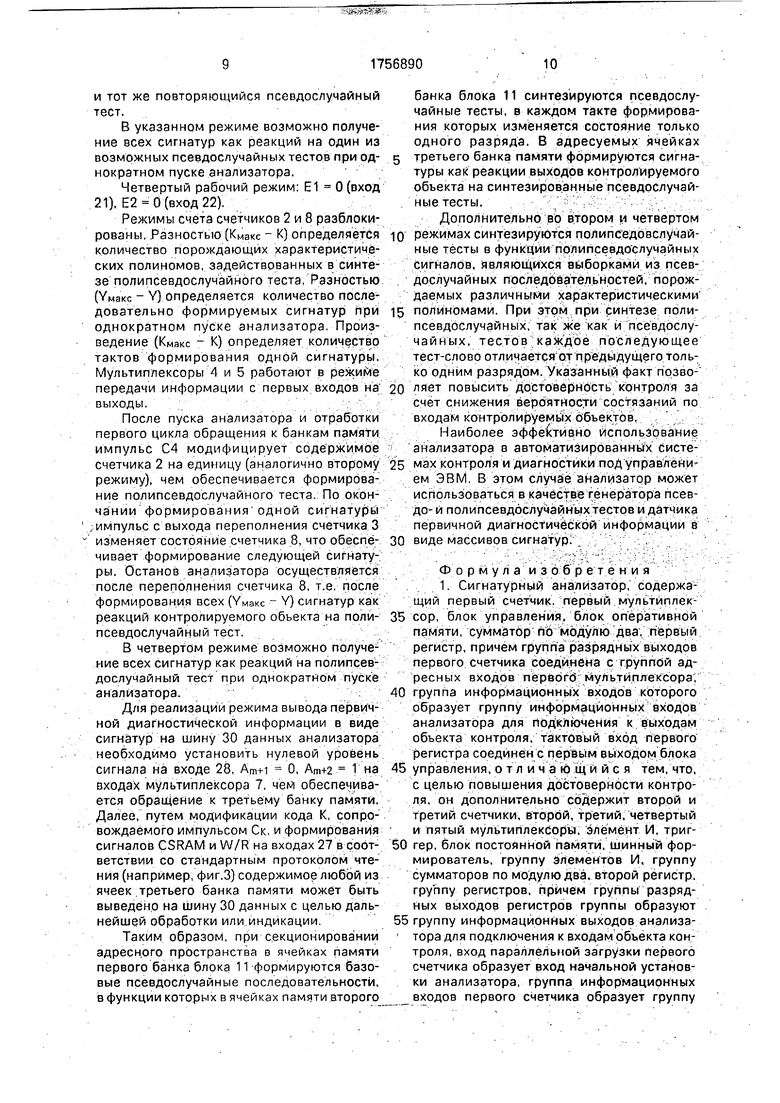

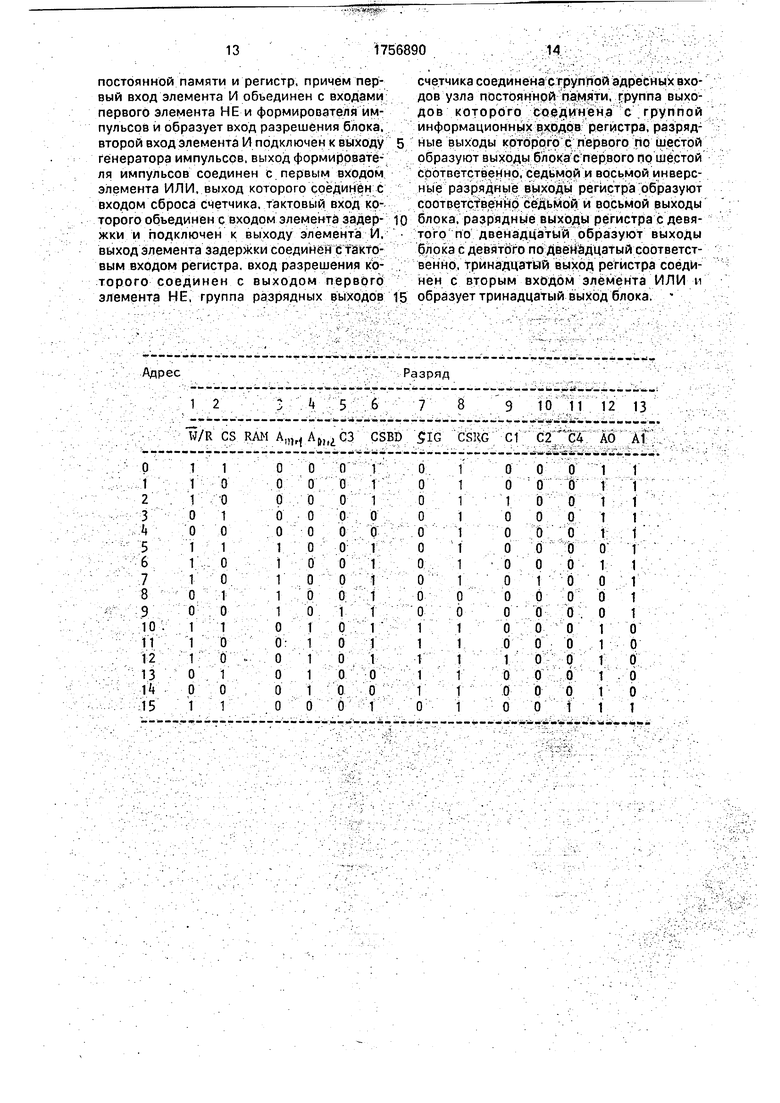

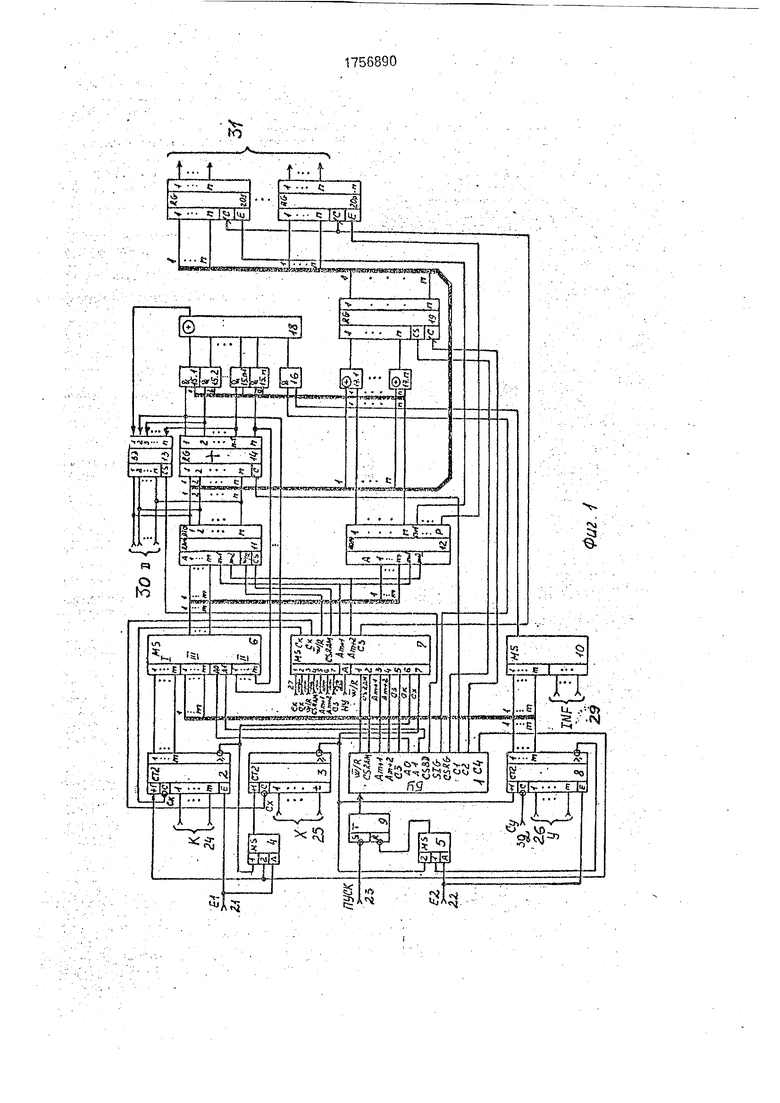

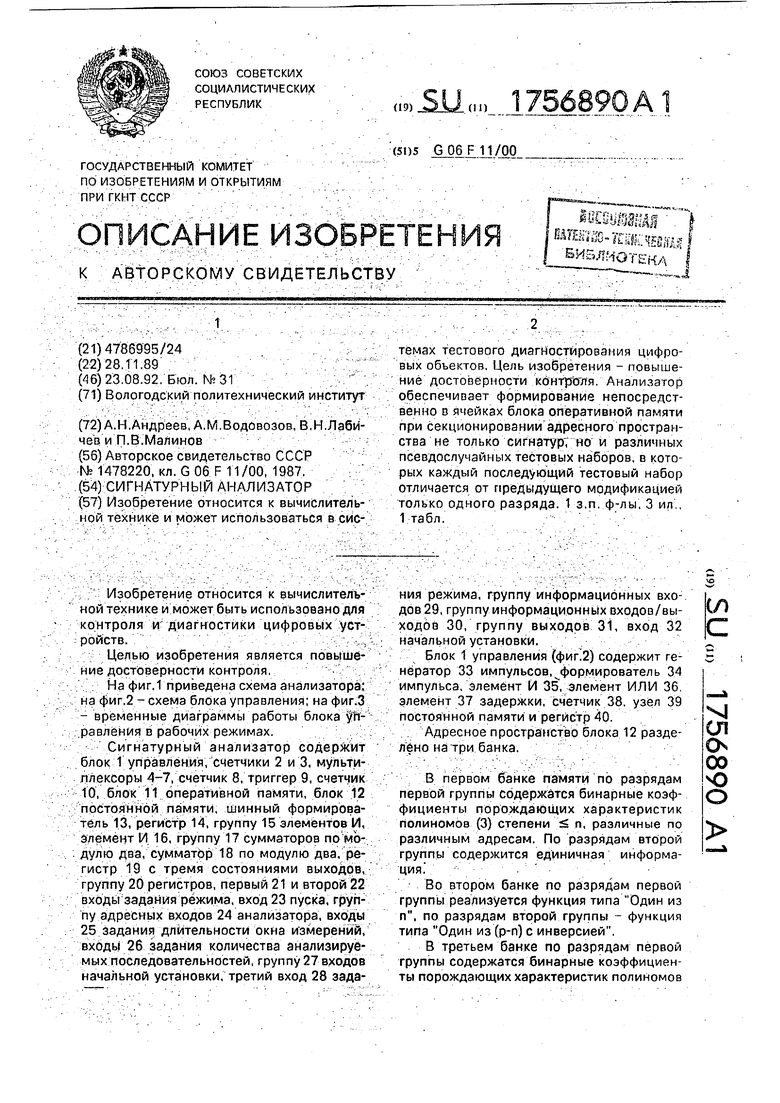

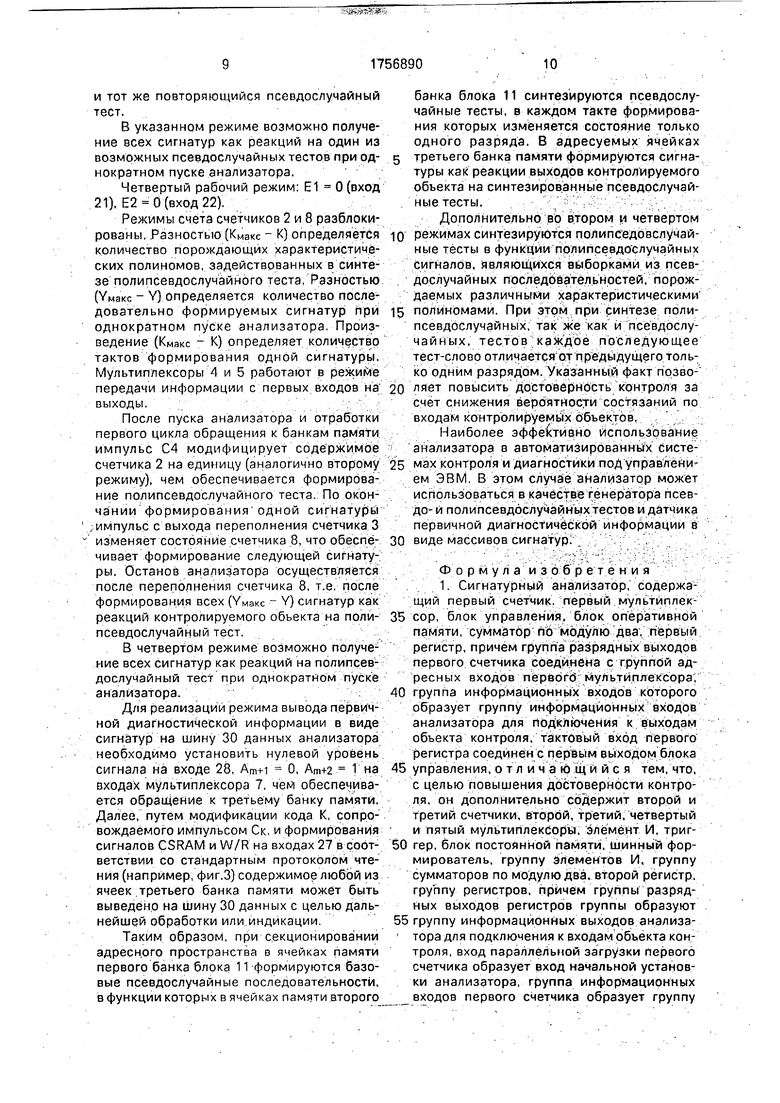

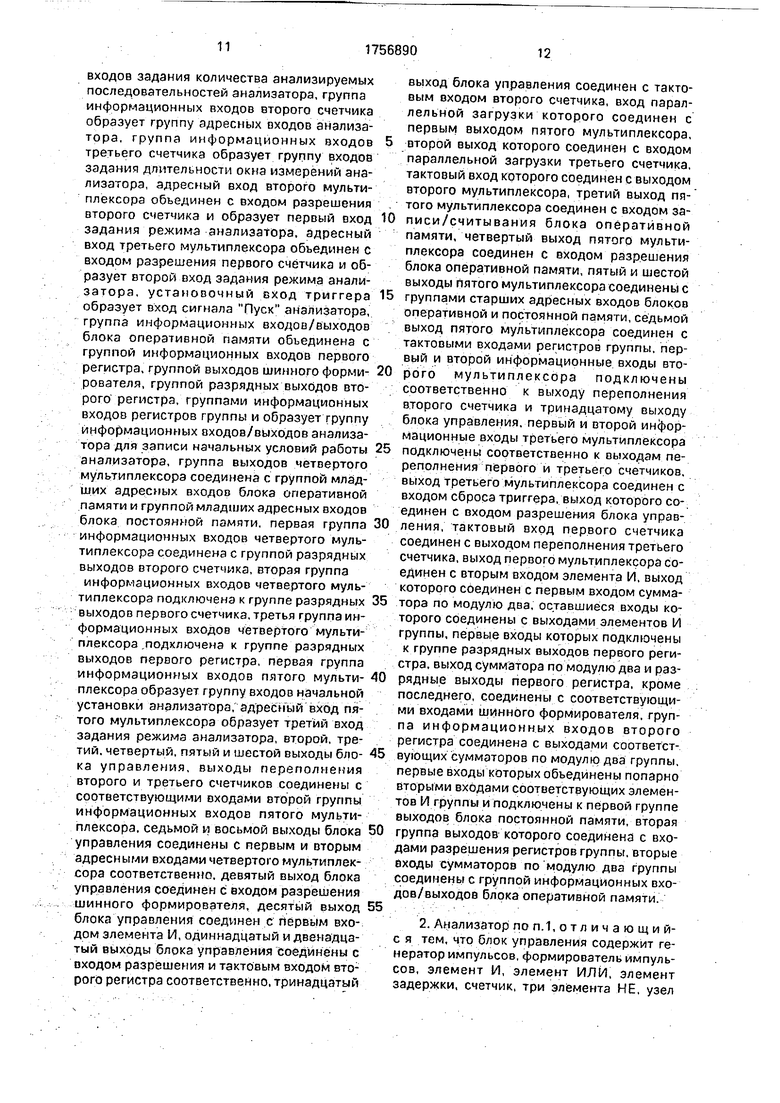

На фиг.1 приведена схема анализатора; на фиг.2 - схема блока управления; на фиг.З - временные диаграммы работы блока управления в рабочих режимах.

Сигнатурный анализатор содержит блок 1 управления, счетчики 2 и 3, мультиплексоры 4-7, счетчик 8, триггер 9, счетчик 10, блок 11 оперативной памяти, блок 12 постоянной памяти, шинный формирователь 13, регистр 14, группу 15 элементов И, элемент И 16, группу 17 сумматоров по модулю два, сумматор 18 по модулю два, регистр 19 с тремя состояниями выходов, группу 20 регистров, первый 21 и второй 22 входы задания режима, вход 23 пуска, группу адресных входов 24 анализатора, входы 25 задания длительности окна измерений, входы 26 задания количества анализируемых последовательностей, группу 27 входов начальной установки, третий вход 28 задания режима, группу информационных входов 29, группу информационных входов/выходов 30, группу выходов 31, вход 32 начальной установки.

Блок 1 управления (фиг.2) содержит генератор 33 импульсов, формирователь 34 Импульса, элемент И 35, элемент ИЛИ 36 элемент 37 задержки, счетчик 38. узел 39 постоянной памяти и регистр 40.

Адресное пространство блока 12 разделено на три банка.

В первом банке памяти по разрядам первой группы содержатся бинарные коэффициенты порождающих характеристик полиномов (3) степени п, различные по различным адресам. По разрядам второй группы содержится единичная информация.

Во втором банке по разрядам первой группы реализуется функция типа Один из п, по разрядам второй группы - функция типа Один из (р-n) с инверсией.

В третьем банке по разрядам первой группы содержатся бинарные коэффициенты порождающих характеристик полиномов

(Л

С

X СЛ О 00 О О

(3) степени п, различные либо одинаковые по различным адресам. По разрядам второй группы содержится единичная информация.

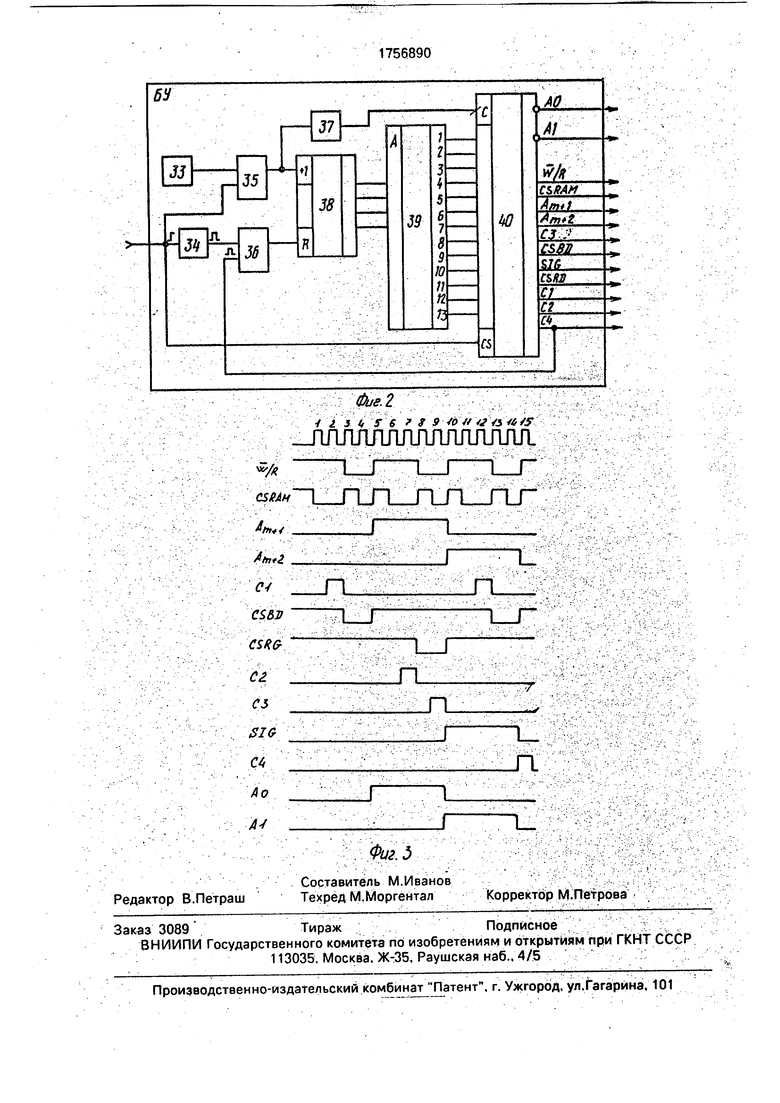

Узел 39 в блоке 1 программируется в соответствии с таблицей.

Анализатор работает следующим образом.

В анализаторе предусмотрены следующие режимы работы: режим задания начальных условий, четыре рабочих режима и режим вывода первичной диагностической информации.

После включения питания состояние элементов схемы неопределенное, однако в конечном итоге триггер 9 устанавливается в нулевое состояние, если он не оказался в этом состоянии сразу после включения питания. Нулевой уровень сигнала с выхода триггера 9 поступает на вход блока 1, запрещая прохождение импульсов с генератора 33 на тактовый вход счетчика 38 и на вход разрешения регистра 40, переводя выходы последнего в третье состояние, что исключает влияние блока 1 на остальные элементы схемы анализатора.

На 7-м и 8-м выходах блока 1 устанавливаются нулевые уровни сигналов, которые поступают на адресные входы мультиплексора 6, чем обеспечивается адресация к ячейкам блока 11 с помощью счетчика 2.

В режиме задания начальных условий на входе 28 устанавливается нулевой уровень сигнала. Мультиплексор 7 работает в режиме передачи информации с первой группы входов на выходы.

Для записи начальных условий в первый банк блока 11 устанавливаются сигналы дт+1 о, О на входах первой группы входов мультиплексора 7. Модификация состояний счетчика 2 осуществляется путем изменения кода К на входах 24, сопровождаемого нулевым синхроимпульсом Ск. на входе 27. Временная диаграмма сигналов W/R, CSRAM на входах 27 аналогична их диаграмме в рабочих режимах при записи данных (фиг.З). Данные, записываемые в адресуемые ячейки блока 11. устанавливаются на входах/выходах 30 анализатора. Данные (ненулевые), записанные в ячейки первого банка оперативной памяти, являются начальными условиями для формирования базовых псевдослучайных последовательностей,

Для записи начальных условий во второй банк блока 11 Ат+1 0, Ат+2 0. Дальнейшие действия аналогичны заданию начальных условий в первом банке. Дополнительно, после установки адреса и данных при задании начальных условий во втором

банке блока 11 формируется импульс СЗ на входе 27, что позволяет продублировать информацию, заносимую в ячейки второго банка, в соответствующих регистрах 20. Информация, записанная во втором банке и продублированная в выходных регистрах, является начальными условиями формируемых тестовых наборов.

Для записи начальных условий в третий

0 банк блока 11 Am-n 0,Am+2 0. Дальнейшие условия аналогичны вышеописанным. Данные, записанные в ячейках третьего банка, являются начальными условиями формируемых сигнатур.

5 Сигналы на входах анализатора как в режиме задания начальных условий, так и в ссыльных режимах наиболее целесообразно формировать с помощью управляющей ЭВМ, в соответствии со стандартными про0 токолами обмена.

После записи данных в банки блока 11 на входах счетчиков 2, 3 и 8 устанавливаются коды К, X и Y, сопровождаемые синхроимпульсами KK, Cx, CY. Функциональное

5 назначение записанных кодов различно для различных режимов работы и поясняется при описании рабочих режимов.

Во всех рабочих режимах сигнал на входе 28 единичный. Мультиплексор 7 работает

0 в режиме передачи информации с второй группы входов на выходы.

Первый рабочий режим: Е1 1 (вход 21), Е2 1 (вход 22). Названными сигналами заблокированы режимы счета счетчиков 2 и

5 10. Мультиплексоры 4 и 5 передают информацию с вторых входов на выходы. Кодом К определен адрес ячейки в первом банке блока 11, в которой формируется базовая псевдослучайная последовательность, по0 рождаемая характеристическим полиномом, бинарные коэффициенты которого размещены в одноименной ячейке блока 12. Кодом Y определен номер одного из информационных входов 29, сигнатура информа5 ционной последовательности которого формируется в ячейке с одноименным адресом в третьем банке блока 11. Разностью максимального кода счетчика 3 и заданного кода X (Хмакс - X) определена длительность

0 цикла формирования сигнатуры.

Пуск анализатора осуществляется формированием нулевого импульса на входе 23. Триггер 9 устанавливается в единичное состояние. Единичный сигнал с выхода тригге5 ра поступает на вход блока 1, В блоке 1 по переднему фронту названного сигнала формирователь 34 вырабатывает короткий импульс, поступающий через элемент ИЛИ 36 4 на вход сброса счетчика 38. Счетчик устанавливается в нулевое состояние. Единичный уровень сигнала на входе блока 1 разрешает прохождение импульсов с генератора 33 через элемент И 35 на тактовый вход счетчика 38 и далее через элемент 37 задержки на тактовый вход регистра 40, который переведен в рабочий режим нулевым сигналом на входе разрешения.

После первого тактового импульса на выходах блока 1 устанавливается комбинация управляющих сигналов в соответствии с диаграммами (фиг 3). При этом сигналами Ат+1 0, Ат+2 0 осуществлена адресация к первым банкам памяти блоков 11 и 12. W/R 1 обеспечивает режим чтения ячейки блока 11 с адресом К Входы/выходы блока 11 в этом случае являются выходами. Содержимое ячейки памяти устанавливается на выходах в момент установки нулевого уровня сигнала CSRAM После второго тактового импульса на входе счетчика 38 содержимое ячейки памяти переписывается в регистр 14 импульсом С1, Сигналы с выходов регистра 14 проходятчерезэлементы И 15,поразрядно маскируемые бинарными коэффициентами характеристического порождающего полинома и суммируются сумматором 18 по модулю два. Результат действия устанавливается на первом входе шинного формирователя 13, на остальные входы которого поступает информация с выходов регистра 14 с единичным сдвигом, обусловленным схемой соединения информационных линий. После третьего тактового импульса сигнал W/R 0 обеспечивает режим записи блока 11 Сигнал CSBD-0 обес- печивает режим передачи шинного формирователя.

После четвертого тактового импульса пулевым сигналом CSRAM осуществляется запись в ранее адресованную ячейку перво- го банка блока 11 информационного сигнала с выходов шинного формирователя 13 При этом содержимое младшего разряда ячейки памяти равно результату суммирования по модулю два ранее оговоренных сиг- налов, а содержимое остальных разрядов сдвинуто на один в сторону старших разрядов. Иными словами каждая многоразрядная ячейка первого банка блока 11 представляет собой регистр сдвига, в кото- ром формируются базовые псевдослучайные последовательности, порождаемые различными характеристическими полиномами.

После пятого тактового импульса сигна- лами Ат+1 1, Ат+2 0 осуществляется адресация к второму банку памяти Сигналами АО 1, А1 0 выбирается второй канал адресации мультиплексора 6 и адресация к ячейкам второго банка памяти осуществляется содержимым регистра 14 После шестого тактового импульса читается содержимое ячейки памяти во втором банке и поступает поразрядно на входы группы 17 сумматоров на другие входы которых поступает из блока 12 комбинация Один из п, определяемая адресом во втором банке памяти В результате действия над указанными числами слово на выходах группы 17 суммируется по модулю два отличается от слова на первых входах группы только в одном разряде

После седьмого тактового импульса названный результат переписывается импульсом С2 в регистр 19 с тремя состояниями выходов После восьмого импульса выбирается регистр 19 сигналом CSRG 0 и запи санное слово устанавливается на его выходах После девятого такта импульсом СЗ названное слово записывается в один из выходных регистров, 20, которому разреше на запись в соответствии с кодом Один из (р-п) с инверсией второй группы выходов блока 12 Одновременно это слово записы- сается в ранее адресованную ячейку второго банка блока 11 Информация (тест-спово) с выходов регистров 20 поступает на входы контролируемого объекта При этом в каждом такте формирования теста изменяется лишь один разряд тест-слова Далее посг е десятого тактового импульса осуществл - т- ся адресация к третьему банку памяти ci r- налами АПН 1 1, Ат+2 1 Сигналами АО Э А1 1 включается третий канал адрес цич мультиплексора 6 и адресация к ячейкам в третьем банке осуществляется содержимым счетчика 8

После одиннадцатого и двенадцатого тактовых импульсов содержимое адресованной ячейке третьего банка блока 11 переписывается в регистр 14 и, маскируемое коэффициентами характеристического полинома, суммируется по модулю два с инфор- мзцмопиым сигналом, поступающим с одного из информационных входов мультиплексора 8 Информационный сигнал с выхода мультиплексора 8 через элемент И 16, разблокированный по второму входу (SiG 1), поступает на последний вход сумматора 18

После тринадцатого и четырнадцатого тактовых импульсов суммы по модулю два записывается в младший разряд адресованной ячейки третьего банка блока 11, содержимое остальных разрядов сдвинуто на один в сторону старших разрядов, т е. сигнатура формируется непосредственно в ячейке третьего банка блока 11 После пятнадцатого тактового импульса формируется импульс С4, сбрасывающий в нулевое состояние счетчик 38 и через второй вход мультиплексора 4 поступающий на тактовый вход счетчика 3. Содержимое последнего увеличивается на единицу.

Процесс формирования в адресованной ячейке первого банка блока 11 следующего псевдослучайного кода, адресация содержимым этой ячейки к ячейке второго банка памяти, формирование в ней нового слова1, отличающегося от предыдущего лишь в од- ном разряде, запись этого слова в один из выходных регистров 20 и формирование реакции одного из выходов контролируемого объекта на тест-слово в виде сигнатуры в адресованной ячейке третьего банка блока 11 повторяется до момента переполнения счетчика 3. Импульс переполнения с выхода переполнения счетчика 3 через второй вход мультиплексора 5 поступает на вход сброса триггера 9, устанавливает последний в нуле- вое состояние на выходе, чем блокируется прохождение импульсов с генератора 33 в блоке 1 на вход счетчика 38. Нулевой сигнал на выходе триггера 9 сигнализирует об окончании цикла формирования сигнатуры.

В первом режиме путем модификации кода К и повторного пуска анализатора возможно раздельное получение сигнатур последовательностей одного из входов анализатора как реакций объекта на все возможные псевдослучайные тесты, порождаемые различными базовыми псевдослучайными последовательностями. При модификации кода Y и повторном пуске возможно раздельное получение сигнатур последовательностей всех входов анализатора как реакций объекта на один из возможных псевдослучайных тестов, порождаемый одной из базовых псевдослучайных последовательностей. Модифика- цией кода X регулируется длительность цикла формирования сигнатуры.

Второй рабочий режим: Е1 0 (вход 21), Е2 1 (вход 22).

Названными сигналами заблокирован режим счета счетчика 10. Мультиплексор 4 передает информацию с первого входа на выход, мультиплексор 5 - с второго входа на выход. Во втором режиме разностью максимального кода счетчика 2 и кода К (Кмакс - К) определяется количество характеристических порождающих полиномов, участвующих в синтезе псевдослучайного теста. Произведение X (Кмакс - К) определяет количество тактов формирования сигнатуры. Ко- дом Y определен номер одного из информационных входов 29, сигнатура информационной последовательности которого формируется в ячейке с одноименным адресом в третьем банке блока 11.

Пуск анализатора и циклограмма обращения к трем банкам памяти осуществляется аналогично первому режиму, однако импульс С4 в этом случае воздействует на тактовый вход счетчика 2 и изменяет его состояние в сторону увеличения. При этом псевдослучайная последовательность формируется в функции состояния счетчика 2 из наборов псевдослучайных чисел последовательностей, порождаемых различными характеристиками полинома, и является полипсевдослучайной. Псевдослучайный тест, формируемый на выходах анализатора, также является полипсевдослучайным В одной из фиксированных ячеек третьего банка блока 11 формируется сигнатура как реакция одного из выходов контролируемого объекта на синтезируемый полипсездос- лучайный тест. Останов анализатора осуществляется после переполнения счетчика 3.

Во втором режиме при модификации кода К возможно изменение количества порождающих характеристических полиномов, задействуемых при синтезе полипсевдослучайного теста. При модификации кода Y и повторном пуске возможно раздельное получение сигнатур последовательностей всех входов анализатора. Модификацией кода X регулируется количество тактов формирования сигнатуры.

Третий рабочий режим: Е1 1 (вход 21), Е2 0 (вход 22).

В этом случае заблокирован режим счета счетчика 2. Мультиплексор 4 передает информацию с второго входа на выход, а мультиплексор 5 - с первого входа на выход. Код К определяет адрес ячейки в первом банке блока 11 оперативной памяти (аналогично первому режиму). Разностью (Умакс Y) определяется количество сигнатур, последовательно формируемых в третьем банке блока 11 при однократном пуске анализатора. Код X определяет количество тактов формирования одной сигнатуры. Процедура формирования псевдослучайного теста аналогична первому режиму. После переполнения счетчика 3 (окончание формирования одной сигнатуры) импульс с выхода переполнения последнего воздействует на тактовый вход счетчика 8 и изменяет его состояние в сторону увеличения. Изменяется адрес ячейки памяти в третьем банке блока 11 и формируется сигнатура информационной последовательности следующего входа 29.

Останов анализатора осуществляется после переполнения счетчика 8 т е после формирования всех (УМЗкс - Y) сигнатур как реакций контролируемого объекта на один

и тот же повторяющийся псевдослучайный тест.

В указанном режиме возможно получение всех сигнатур как реакций на один из возможных псевдослучайных тестов при однократном пуске анализатора.

Четвертый рабочий режим: Е1 0 (вход 21), Е2 0 (вход 22).

Режимы счета счетчиков 2 и 8 разблокированы. Разностью (Кмакс - К) определяется количество порождающих характеристических полиномов, задействованных в синтезе полипсевдослучайного теста, Разностью (Умакс - Y) определяется количество последовательно формируемых сигнатур при однократном пуске анализатора Произведение (Кмакс - К) определяет количество тактов формирования одной сигнатуры. Мультиплексоры А и 5 работают в режиме передачи информации с первых входов на выходы.

После пуска анализатора и отработки первого цикла обращения к банкам памяти импульс С4 модифицирует содержимое счетчика 2 на единицу (аналогично второму режиму), чем обеспечивается формирование полипсевдослучайного теста По окончании формирования одной сигнатуры .импульс с выхода переполнения счетчика 3 изменяет состояние счетчика 8, что обеспечивает формирование следующей сигнатуры. Останов анализатора осуществляется после переполнения счетчика 8, т.е. после формирования всех (Умакс - Y) сигнатур как реакций контролируемого объекта на полипсевдослучайный тест.

В четвертом режиме возможно получение всех сигнатур как реакций на полипсевдослучайный тест при однократном пуске анализатора.

Для реализации режима вывода первичной диагностической информации в виде сигнатур на шину 30 данных анализатора необходимо установить нулевой уровень сигнала на входе 28, Ат-м 0, Ат+2 1 на входах мультиплексора 7, чем обеспечивается обращение к третьему банку памяти. Далее, путем модификации кода К, сопровождаемого импульсом Ск, и формирования сигналов CSRAM и W/R на входах 27 в соответствии со стандартным протоколом чтения (например, фиг.З) содержимое любой из ячеек третьего банка памяти может быть выведено на шину 30 данных с целью дальнейшей обработки или индикации

Таким образом, при секционировании адресного пространства в ячейках памяти первого банка блока 11 формируются базовые псевдослучайные последовательности. в функции которых в ячейках памяти второго

банка блока 11 синтезируются псевдослучайные тесты, в каждом такте формирования которых изменяется состояние только одного разряда. В адресуемых ячейках

третьего банка памяти формируются сигнатуры как реакции выходов контролируемого объекта на синтезированные псевдослучайные тесты.

Дополнительно во втором и четвертом

режимах синтезируются полипседовслучай- ные тесты в функции полипсевдослучайных сигналов, являющихся выборками из псевдослучайных последовательностей, порождаемых различными характеристическими

полиномами. При этом при синтезе полипсевдослучайных, так же как и псевдослучайных, тестов каждое последующее тест-слово отличается от предыдущего только одним разрядом. Указанный факт позволяет повысить достоверность контроля за счет снижения вероятности состязаний по входам контролируемых объектов.

Наиболее эффективно использование анализатора в автоматизированных системах контроля и диагностики под управлением ЭВМ В этом случае анализатор может использоваться в качестве генератора псев- до- и полипсевдослучайных тестов и датчика первичной диагностической информации в

виде массивов сигнатур.

Формула изобретения 1. Сигнатурный анализатор, содержащий первый счетчик, первый мультиплексор, блок управления, блок оперативной памяти, сумматор по модулю два, первый регистр, причем группа разрядных выходов первого счетчика соединена с группой адресных входов первого мультиплексора,

группа информационных входов которого образует группу информационных входов анализатора для подключения к выходам объекта контроля, тактовый вход первого регистра соединен с первым выходом блока

управления, отличающийся тем, что, с целью повышения достоверности контроля, он дополнительно содержит второй и третий счетчики, второй, третий, четвертый и пятый мультиплексоры, элемент И, триггер, блок постоянной памяти, шинный формирователь, группу элементов И. группу сумматоров по модулю два, второй регистр, группу регистров, причем группы разрядных выходов регистров группы образуют

группу информационных выходов анализатора для подключения к входам объекта контроля, вход параллельной загрузки первого счетчика образует вход начальной установки анализатора, группа информационных входов первого счетчика образует группу

входов задания количества анализируемых последовательностей анализатора, группа информационных входов второго счетчика образует группу адресных входов анализатора, группа информационных входов третьего счетчика образует группу входов задания длительности окна измерений анализатора, адресный вход второго мультиплексора объединен с входом разрешения второго счетчика и образует первый вход задания режима анализатора, адресный вход третьего мультиплексора объединен с входом разрешения первого счетчика и образует второй вход задания режима анализатора, установочный вход триггера образует вход сигнала Пуск анализатора, группа информационных входов/выходов блока оперативной памяти объединена с группой информационных входов первого регистра, группой выходов шинного форми- рователя, группой разрядных выходов второго регистра, группами информационных входов регистров группы и образует группу информационных входов/выходов анализатора для записи начальных условий работы анализатора, группа выходов четвертого мультиплексора соединена с группой младших адресных входов блока оперативной памяти и группой младших адресных входов блока постоянной памяти, первая группа информационных входов четвертого мультиплексора соединена с группой разрядных выходов второго счетчика, вторая группа информационных входов четвертого мультиплексора подключена к группе разрядных выходов первого счетчика, третья группа информационных входов четвертого мультиплексора подключена к группе разрядных выходов первого регистра, первая группа информационных входов пятого мульти- плексора образует группу входов начальной установки анализатора, адресный вход пятого мультиплексора образует третий вход задания режима анализатора, второй, третий, четвертый, пятый и шестой выходы бло- ка управления, выходы переполнения второго и третьего счетчиков соединены с соответствующими входами второй группы информационных входов пятого мультиплексора, седьмой и восьмой выходы блока управления соединены с первым и вторым адресными входами четвертого мультиплексора соответственно, девятый выход блока управления соединен с входом разрешения шинного формирователя, десятый выход блока управления соединен с первым входом элемента И, одиннадцатый и двенадцатый выходы блока управления соединены с входом разрешения и тактовым входом второго регистра соответственно, тринадцатый

выход блока управления соединен с тактовым входом второго счетчика, вход параллельной загрузки которого соединен с первым выходом пятого мультиплексора, второй выход которого соединен с входом параллельной загрузки третьего счетчика, тактовый вход которого соединен с выходом второго мультиплексора, третий выход пятого мультиплексора соединен с входом за- писи/считывания блока оперативной памяти, четвертый выход пятого мультиплексора соединен с входом разрешения блока оперативной памяти, пятый и шестой выходы пятого мультиплексора соединены с группами старших адресных входов блоков оперативной и постоянной памяти, седьмой выход пятого мультиплексора соединен с тактовыми входами регистров группы, первый и второй информационные входы второго мультиплексора подключены соответственно к выходу переполнения второго счетчика и тринадцатому выходу блока управления, первый и второй информационные входы третьего мультиплексора подключены соответственно к выходам переполнения первого и третьего счетчиков, выход третьего мультиплексора соединен с входом сброса триггера, выход которого соединен с входом разрешения блока управления, тактовый вход первого счетчика соединен с выходом переполнения третьего счетчика, выход первого мультиплексора соединен с вторым входом элемента И, выход которого соединен с первым входом сумматора по модулю два, оставшиеся входы которого соединены с выходами элементов И группы, первые входы которых подключены к группе разрядных выходов первого регистра, выход сумматора по модулю два и разрядные выходы первого регистра, кроме последнего, соединены с соответствующими входами шинного формирователя, группа информационных входов второго регистра соединена с выходами соответствующих сумматоров по модулю два группы, первые входы которых объединены попарно вторыми входами соответствующих элементов И группы и подключены к первой группе выходов блока постоянной памяти, вторая группа выходов которого соединена с входами разрешения регистров группы, вторые входы сумматоров по модулю два группы соединены с группой информационных входов/выходов блока оперативной памяти.

2. Анализатор лоп.1,отличающий- с я тем, что блок управления содержит генератор импульсов, формирователь импульсов, элемент И, элемент ИЛИ, элемент задержки, счетчик, три элемента НЕ, узел

постоянной памяти и регистр, причем первый вход элемента И объединен с входами первого элемента НЕ и формирователя импульсов и образует вход разрешения блока, второй вход элемента И подключен к выходу генератора импульсов, выход формирователя импульсов соединен с первым входом элемента ИЛИ, выход которого соединен с входом сброса счетчика, тактовый вход которого объединен с входом элемента задержки и подключен к выходу элемента И, выход элемента задержки соединен с тактовым входом регистра, вход разрешения которого соединен с выходом первого элемента НЕ, группа разрядных выходов

0

5

счетчика соединена с группой адресных входов узла постоянной памяти, группа выходов которого соединена с группой информационных входов регистра, разрядные выходы которого с первого по шестой образуют выходы блока с первого по шестой соответственно, седьмой и восьмой инверсные разрядные выходы регистра образуют соответственно седьмой и восьмой выходы блока, разрядные выходы регистра с девятого по двенадцатый образуют выходы блока с девятого по двенадцатый соответственно, тринадцатый выход регистра соединен с вторым входом элемента ИЛИ и образует тринадцатый выход блока.

о

СП СО

со

LO Г/Ј

(- гпф

6У

А1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1987 |

|

SU1587515A1 |

| Сигнатурный анализатор для контроля устройств памяти | 1987 |

|

SU1506449A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| ГЕНЕРАТОР ПСЕВДОСЛУЧАЙНЫХ СИГНАЛОВ | 2009 |

|

RU2416157C1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1987 |

|

SU1520521A1 |

| Сигнатурный анализатор | 1988 |

|

SU1580366A1 |

Изобретение относится к вычислительной технике и может использоваться в системах тестового диагностирования цифровых объектов. Цель изобретения - повышение достоверности контроля. Анализатор обеспечивает формирование непосредственно в ячейках блока оперативной памяти при секционировании адресного пространства не только сигнатур, но и различных псевдослучайных тестовых наборов, в которых каждый последующий тестовый набор отличается от предыдущего модификацией только одного разряда. 1 з.п, ф-лы, 3 ил , 1 табл.

38

Л

Фие.2

11 S Ь 56 9 40 // tf /j /4 /5

-лтллллллгшлллла

Я I

CSfiAH

ttO

CJ-L

Ј3SS

S7g

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1992-08-23—Публикация

1989-11-28—Подача