Предлагаемый способ относится к классу изобретений в области синхронизации цифровых систем управления вентильными преобразователями и предназначен для использования в трехфазных управляемых мостовых выпрямителях с микропроцессорной системой управления и широким диапазоном регулирования углов управления силовых полупроводников.

Известен способ для фазовой синхронизации системы управления (патент №4941796/07, опубл. 07.03.1993. Бюл. №9), в котором напряжение синхронизации через разделительный трансформатор подают на два последовательно соединенных интегратора, обеспечивающих подавление импульсных помех, выходной сигнал с которых подают на входы компараторов, работающих в противофазе. На выходах компараторов формируют противофазные прямоугольные импульсы напряжения со скважностью, равной двум, синхронизированные основной гармоникой синхросигнала, причем фронты нарастания и спада импульсов совпадают по времени с моментами перехода через нуль основной гармоники синхросигнала.

Недостатком данного способа является то, что при скважности импульсов, отличной от двух, возможно накопление ошибки интегрирования с последующим насыщением интегратора.

Технический результат предлагаемого изобретения состоит в повышении точности синхронизации в условиях работы нескольких преобразователей на сеть ограниченной мощности или от преобразовательного трансформатора при непосредственной подаче синхронизирующего напряжения с входных шин управляемого мостового выпрямителя. Искажения синхронизирующего напряжения от идеальной синусоидальной формы обусловлены как работой других потребителей электрической энергии, так и работой самого выпрямителя.

Техническая задача решается тем, что в известном способе фазовой синхронизации системы управления, заключающемся в том, что формируют синхроимпульс путем сравнения фильтрованного синхронизирующего напряжения с опорным напряжением, для исключения накопительной ошибки интегрирования постоянной составляющей синхронизирующего напряжения ограничивают диапазон изменения выходного сигнала интегратора, причем скорость нарастания в два раза меньше, чем скорость спада сигнала, а для исключения фазовой погрешности при изменении частоты питающей сети напряжение выходного компаратора устанавливают равным половине максимального значения выходного интегратора, с учетом напряжения смещения, таким, что синхронизация цифровой системы управления осуществляется в момент наибольшего значения первой гармоники синхронизирующего напряжения.

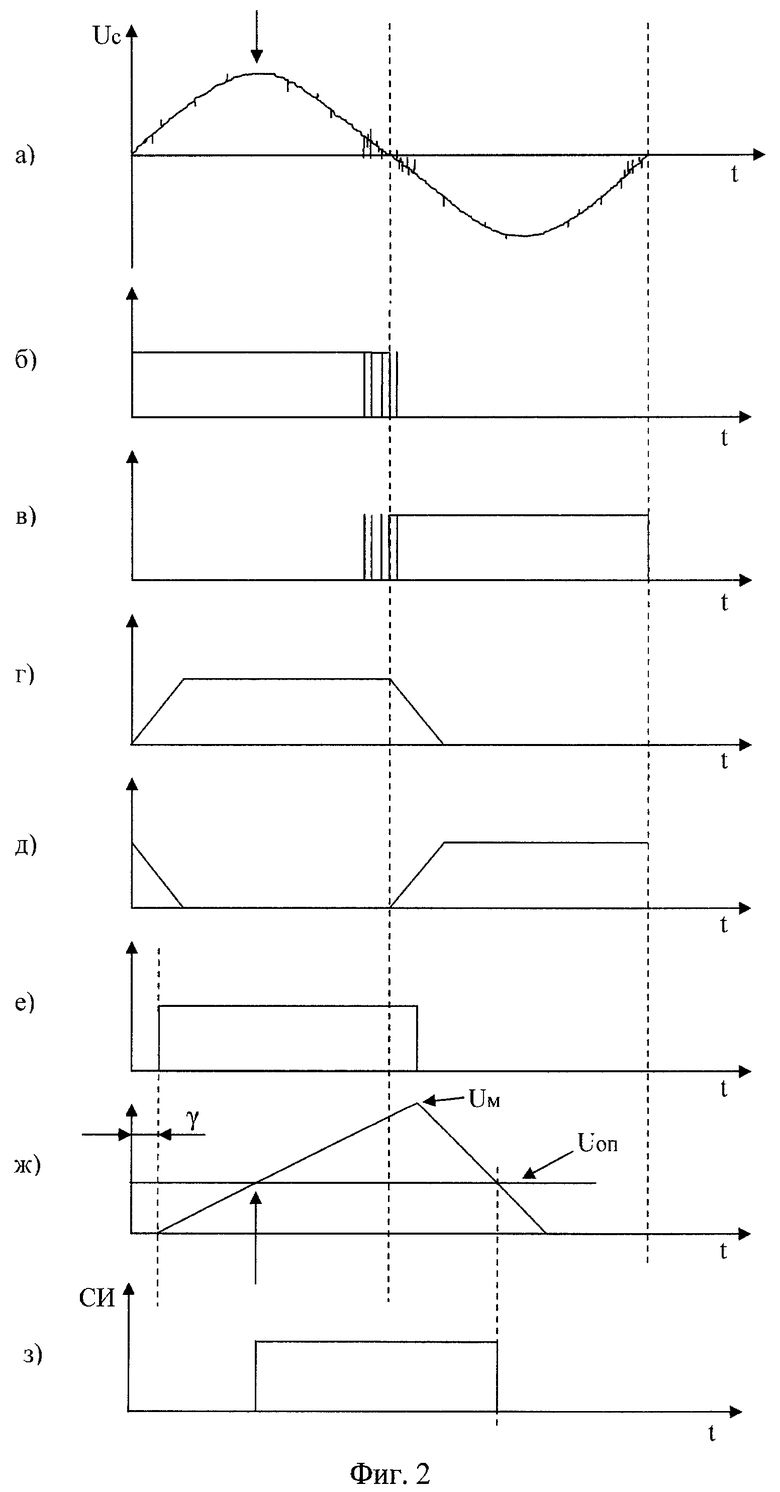

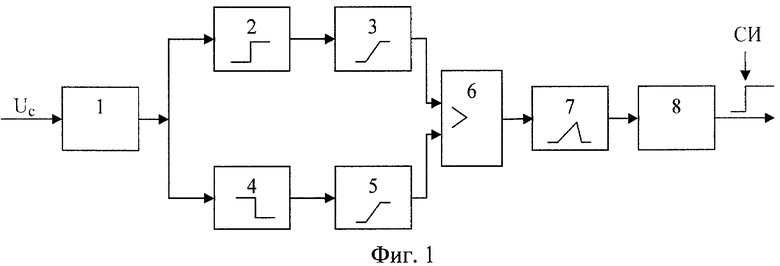

На фиг.1 изображена структурная схема изобретения, реализующего предлагаемый способ синхронизации; на фиг.2 - временные диаграммы, поясняющие принцип формирования синхроимпульса (СИ).

Блок 1 (фиг.1) представляет собой блок согласования синхронизирующего напряжения с входами микроконтроллера, блоки 2,4 - логические компараторы, блоки 3,5 - цифровые интеграторы с ограничением выходного сигнала, блок 6 - логическое устройство сравнения, 7 - цифровой интегратор, 8 - логический компаратор.

Синхронизирующее напряжение Uc с входных шин управляемого мостового выпрямителя подается на согласующий разделительный трансформатор и через него на блок 1 (фиг.2а), который обеспечивает дополнительную гальваническую развязку и согласование выходного сигнала с уровнями, приемлемыми для обработки микроконтроллером. Сигнал с выхода блока 1 подается на вход блоков 2 и 4 (фиг.2б, в), представляющих собой логические компараторы, работающие в противофазе. С выхода компараторов сигнал подается на фильтры, представляющие собой интеграторы с ограничением уровня выходного сигнала определенным максимальным значением и нулем (фиг.2г, д). При подаче логической единицы на вход интеграторов выходное напряжение нарастает, а при логическом нуле - спадает. Сигналы с выходов интеграторов подаются на логическое устройство сравнения 6. Уровень логической единицы устанавливается, если сигнал с выхода интегратора 3 больше, чем сигнал на выходе интегратора 5. В противном случае устанавливается уровень логического нуля (фиг.2е). Тем самым осуществляется помехозащищенность блока синхронизации от импульсов, как обусловленных работой силовых преобразователей (коммутационные провалы напряжения), так и другими источниками (например, коммутация индуктивных нагрузок).

Блок 7 представляет собой интегратор с ограничением минимального выходного сигнала нулевым значением. При подаче логической единицы с логического устройства сравнения 6 выходной сигнал интегратора 7 нарастает, а при логическом нуле спадает, причем темп нарастания в два раза медленней, чем темп спада. Это необходимо для исключения накопительной ошибки интегрирования постоянной составляющей входного сигнала. В блоке 8 происходит сравнение входного цифрового сигнала с опорным, значение которого определяется по формуле

где Uм - максимальное значение цифрового сигнала интегратора 7, Uсм - цифровой сигнал смещения, пропорциональный углу γ.

Угол γ определяется от момента отсчета до момента формирования логической единицы устройством сравнения 6 и зависит от постоянной времени интегратора 3.

В момент переключения компаратора (передний фронт) происходит формирование синхроимпульса (фиг.2ж, з). При этом синхронизация цифровой системы управления осуществляется при максимальном значении синхронизирующего напряжения.

Таким образом, повышение точности синхронизации заключается в том, что за счет использования двойного интегрирования сигнала эффективно подавляются импульсные помехи, и синхронизация цифровой системы управления осуществляется в момент наибольшего значения первой гармоники синхронизирующего напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ и устройство синхронизации системы управления преобразователями напряжения | 2021 |

|

RU2772321C1 |

| СПОСОБ ФАЗОВОЙ АВТОПОДСТРОЙКИ ЧАСТОТЫ С ФИЛЬТРАЦИЕЙ | 2015 |

|

RU2592887C1 |

| АДАПТИВНОЕ ИНТЕГРИРУЮЩЕЕ УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2013 |

|

RU2531530C1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ИЗМЕРИТЕЛЬ УГЛОВОЙ СКОРОСТИ | 1994 |

|

RU2112927C1 |

| Одноканальное устройство для управления выпрямителем | 1981 |

|

SU983976A1 |

| УСТРОЙСТВО УСКОРЕННОЙ СИНХРОНИЗАЦИИ ПРИЕМНИКА ШУМОПОДОБНЫХ СИГНАЛОВ С МИНИМАЛЬНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 2011 |

|

RU2446560C1 |

| Электропривод | 1988 |

|

SU1656652A1 |

| СПОСОБ СТУПЕНЧАТОГО РЕГУЛИРОВАНИЯ СКОРОСТИ АСИНХРОННОГО ЭЛЕКТРОДВИГАТЕЛЯ | 2000 |

|

RU2176127C1 |

| СПОСОБ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ ПРИ ПОМОЩИ МИКРОПРОЦЕССОРНОЙ СИСТЕМЫ | 1996 |

|

RU2107982C1 |

| СПОСОБ УПРАВЛЕНИЯ МОСТОВЫМ ИНВЕРТОРОМ НАПРЯЖЕНИЯ | 1993 |

|

RU2093949C1 |

Изобретение относится к области электротехники и может быть использовано для синхронизации цифровых систем управления вентильными преобразователями в трехфазных управляемых мостовых выпрямителях с микропроцессорной системой управления и широким диапазоном регулирования углов управления силовых полупроводников. Технический результат состоит в повышении точности синхронизации в условиях работы нескольких преобразователей на сеть ограниченной мощности или от преобразовательного трансформатора при непосредственной подаче синхронизирующего напряжения с входных шин управляемого мостового выпрямителя. В способе синхронизации цифровой системы управления формируют синхроимпульс путем сравнения фильтрованного синхронизирующего напряжения с опорным напряжением, для исключения накопительной ошибки интегрирования постоянной составляющей синхронизирующего напряжения ограничивают диапазон изменения выходного сигнала интегратора, причем скорость нарастания в два раза меньше, чем скорость спада сигнала, а для исключения фазовой погрешности при изменении частоты питающей сети напряжение выходного компаратора устанавливают равным половине максимального значения выходного интегратора с учетом напряжения смещения таким, что синхронизация цифровой системы управления осуществляется в момент наибольшего значения первой гармоники синхронизирующего напряжения. 2 ил.

Способ фазовой синхронизации системы управления трехфазным мостовым выпрямителем, заключающийся в том, что формируют синхроимпульс путем сравнения фильтрованного синхронизирующего напряжения с опорным напряжением, отличающийся тем, что для исключения накопительной ошибки интегрирования постоянной составляющей синхронизирующего напряжения ограничивают диапазон изменения выходного сигнала интегратора, причем скорость нарастания в два раза меньше, чем скорость спада сигнала, а для исключения фазовой погрешности при изменении частоты питающей сети напряжение выходного компаратора устанавливают равным половине максимального значения выходного интегратора с учетом напряжения смещения таким, что синхронизация цифровой системы управления осуществляется в момент наибольшего значения первой гармоники синхронизирующего напряжения.

| СПОСОБ СИНХРОНИЗАЦИИ СИСТЕМЫ УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕМ | 1996 |

|

RU2107981C1 |

| СПОСОБ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ВЫПРЯМИТЕЛЕМ И УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТИРИСТОРНЫМ ВЫПРЯМИТЕЛЕМ | 1991 |

|

RU2107381C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2008 |

|

RU2383985C1 |

| Устройство для фазовой синхронизации системы управления | 1991 |

|

SU1800562A1 |

| ГАЗОЖИДКОСТНЫЙ СЕПАРАТОР | 1996 |

|

RU2127630C1 |

| US 4891741 A, 02.01.1990 | |||

| JP 11178322 А, 02.07.1992 | |||

| JP 10290571 A, 27.10.1998 | |||

| CN 1937377 A, 28.03.2007. | |||

Авторы

Даты

2011-04-27—Публикация

2010-04-26—Подача