Изобретение относится к вычислительной технике и решает задачу повышения достоверности ввода последовательной информации путем обеспечения аппаратно-программного контроля ввода информации.

Известно «Устройство для сопряжения вычислительной машины с каналами связи» (см. патент РФ №2020565 от 11.06.1990 г., опубликован 30.09.1994 г.).

Устройство содержит блок контроля, блок интерфейса, блок синхронизации, вход задания режима работы устройства, вход сброса устройства, ключ, шину адреса/данных, блок приема, блок передачи, блок формирования сигналов прерывания, шину «0» питания, элемент индикации, внутреннюю шину адреса/данных устройства, входы устройства для подключения к каналу связи. В режиме контроля код в регистр сдвига блока приема поступает с выхода регистра сдвига блока передачи, а по окончании передачи байта содержимое регистра сдвига блока приема сравнивается с содержимым адресуемого регистра, куда в режиме контроля загружается тот же код, который загружается в буферный регистр передачи, причем сигнал сравнения используется для установки триггера, сброс которого осуществляется сигналом завершения передачи байта, а потенциальный сигнал с выхода триггера подается на адресуемую шину, доступную для считывания со стороны шины адреса/данных устройств, формирователь, блок контроля. Вышеуказанное устройство может быть использовано в режиме синхронной связи, для организации обмена информацией вычислительной системы с каналом связи и является наиболее близким к заявляемому устройству по технической сущности и поэтому выбрано в качестве прототипа.

Недостатком устройства является ограниченная область применения.

Решаемой технической задачей является создание контроллера интерфейса с расширенными функциональными возможностями.

Достигаемым техническим результатом является ввод дополнительных портов для подключения внешних устройств, повышение достоверности контроля передачи-приема данных.

Для достижения технического результата в контроллере интерфейса, содержащем блок приема, блок передачи, блок сопряжения с микроконтроллером, группа входов-выходов которого является группой входов-выходов контроллера для подключения к шине адреса/данных микроконтроллера, блок прерываний, выход которого является выходом контроллера для подключения к входу запроса прерывания микроконтроллера, новым является то, что дополнительно введены порт вывода, первый и второй порты ввода/вывода, блок защищенных портов, блок настройки частоты и блок программируемой логики, блок сопряжения с микроконтроллером включает в себя блок входа/выхода, первый, второй, третий, четвертый и пятый логические элементы, регистр, дешифратор и мультиплексор, первая, вторая, третья, четвертая и пятая группа входов которого соединены с группами выходов первого и второго портов ввода-вывода, группой выходов блока прерываний, третьей группой выходов блока приемника и первой группой выходов блока передатчика соответственно, группа выходов мультиплексора соединена с группой входов блока входа-выхода, группа выходов которого подключена к группе входов регистра, группе входов порта вывода, группам входов первого и второго портов ввода-вывода, к первой группе входа блока прерываний, группе входов блока защищенных портов, группе входов блока настройки частоты, к первой группе входов блока программируемой логики, группам входов блоков передатчика и приемника, вход блока входа/выхода соединен с выходом третьего логического элемента, первый вход которого соединен с выходом первого логического элемента и первым входом второго логического элемента, выход которого соединен с входом дешифратора, группа входов которого соединена с шестой группой входов мультиплексора, с группой входов пятого логического элемента и группой выходов регистра, вход которого является одним из управляющих входов контроллера, вторые входы третьего и четвертого логических элементов, третий вход четвертого логического элемента и первый вход первого логического элемента объединены между собой и являются одними из управляющих входов контроллера, вторые входы четвертого, первого и второго логических элементов являются одними из управляющих входов контроллера, группа выходов дешифратора соединена с первым входом порта вывода, первыми и вторыми входами первого и второго портов ввода/вывода, с первым, вторым, третьим входами блока прерываний, первым и вторым входами блока защищенных портов, первым входом блока настройки частоты, первыми и вторыми входами блока программируемой логики, первым и вторым входами блока передатчика и четвертым входом блока приемника, первые и вторые группы выходов блока передатчика и блока приемника объединены между собой соответственно, первые и вторые входы и выходы блока приемника и блока передатчика являются, соответственно, входами и выходами внешней линии связи, третий вход блока приемника соединен с третьим входом блока передатчика и выходом блока настройки частоты, второй вход которого является внешним сигналом тактовой частоты, вторая группа входов блока программируемой логики является входными сигналами контроллера, вторая группа входов блока прерываний соединяется с входными сигналами прерываний контроллера и соединена со вторыми группами выходов блока приемника и второй группой блока передатчика, группы выходов блока программируемой логики, блока защищенных портов, порта вывода и группы входов-выходов первого и второго портов ввода/вывода являются выходами микроконтроллера, вход пятого логического элемента соединен с выходом третьего логического элемента, а выход пятого логического элемента соединен с пятым входом блока приемника, второй вход порта вывода, третьи входы первого и второго портов ввода-вывода, четвертый вход блока прерываний, третьи входы блока защищенных портов, блока настройки частоты, блока программируемой логики, четвертый вход блока передатчика и шестой вход блока приемника объединены между собой и соединены с входом начальной установки контроллера, третий вход порта вывода, четвертый и пятый входы первого и второго портов ввода-вывода объединены соответственно между собой и соединены с входами начальной конфигурации портов контроллера, выход, шестой и седьмой входы блока приемника соединены с пятым входом, третьим и четвертым выходами блока передатчика соответственно.

Введение портов в заявляемое устройство позволяет подключить дополнительные устройства (например, внешнюю память, при этом порт вывода используется как защелка адреса), а использование блока программируемой логики позволяет осуществлять выборку различных устройств, мультиплексирование сигналов.

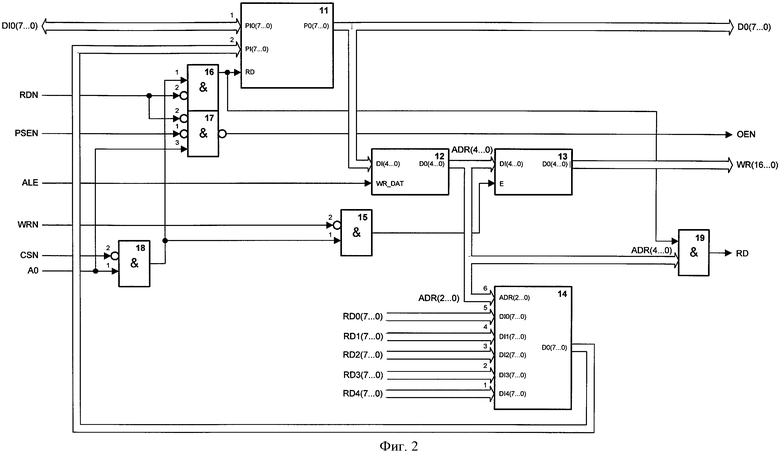

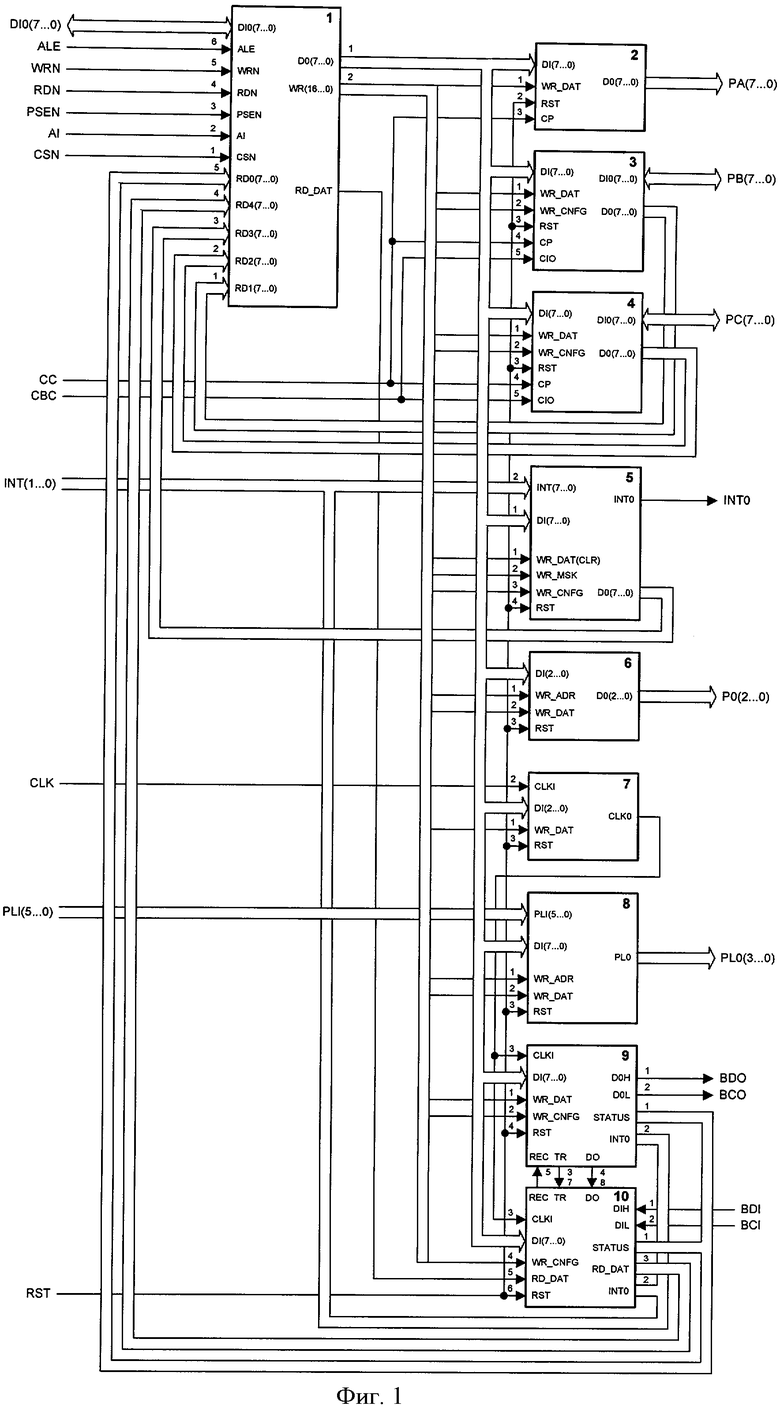

На фигуре 1 представлена блок-схема заявляемого устройства, на фигуре 2 представлена структурная схема блока сопряжения с микроконтроллером.

Контроллер интерфейса содержит блок приема 10, блок передачи 9, блок сопряжения с микроконтроллером 1, группа входов-выходов DIO (7…0) является группой входов-выходов контроллера для подключения к шине адреса/данных микроконтроллера, блок прерываний 5, выход INTO является выходом контроллера для подключения к входу запроса прерывания микроконтроллера, порт вывода 2, первый 3 и второй 4 порты ввода-вывода, блок защищенных портов 6, блок настройки частоты 7 и блок программируемой логики 8, блок сопряжения с микроконтроллером включает в себя блок входа-выхода 11, первый 15, второй 16, третий 17, четвертый 18 и пятый 19 логические элементы, регистр 12, дешифратор 13 и мультиплексор 14, первая DI4 (7..0), вторая DI3 (7..0), третья DI2 (7..0), четвертая DI1 (7..0) и пятая DI0 (7..0) группы входов соединены с группами выходов первого 3 и второго 4 портов ввода-вывода, группой выходов блока прерывания 5, первой группой выходов блока приемника 10 и группой выходов блока передатчика 9 соответственно, группа выходов мультиплексора 14 соединена с группой входов блока входа-выхода 11, группа выходов PO (7…0) подключена к группе входов DI (4…0) регистра 12, группе входов DI (7…0) порта вывода 2, группам входов DI (7…0) первого 3 и второго 4 портов ввода-вывода, к первой группе входа DI (7…0) блока прерываний 5, группе входов DI (2…0) блока защищенных портов 8, группе входов DI (2…0) блока настройки частоты 7, к первой группе входов DI (7…0) блока программируемой логики 8, группам входов DI (7…0) блоков передатчика 9 и приемника 10, вход ALE блока входа-выхода 11 соединен с выходом третьего логического элемента 16, первый вход которого соединен с выходом первого логического элемента 18 и первым входом второго логического элемента 15, выход которого соединен с входом Е дешифратора 13, группа входов DI (4..0) соединена с шестой группой входов ADR (2..0) мультиплексора 14, с группой входов пятого логического элемента 19 и группой выходов DO (4..0) регистра 12, вход WR_DAT является одним из управляющих входов ALE контроллера, вторые входы третьего 16 и четвертого 17 логических элементов, третий вход четвертого логического элемента 17 и первый вход первого логического элемента 18 объединены между собой и являются одними из управляющих входов А0 контроллера, вторые входы четвертого 17, первого 18 и второго 15 логических элементов являются одними из управляющих входов PSEN контроллера, группа выходов WR (16…0) дешифратора 13 соединена с входом WR_DAT порта вывода 2, первыми WR_DAT и вторыми входами WR_CNFG первого 3 и второго 4 портов ввода-вывода, с первым WR_DAT, вторым WR_MSK, третьим WR_CNFG входами блока прерываний 5, первым WR_ADR и вторым WR_DAT входами блока защищенных портов 6, первым входом WR_DAT блока настройки частоты 7, первыми WR_DAT1 и вторыми WR_DAT2 входами блока программируемой логики 8, первым WR_DAT и вторым WR_CNFG входами блока передатчика 9 и входом WR_CNFG блока приемника 10, первые группы выходов STATUS блока передатчика 9 и блока приемника 10 объединены между собой, первый DIH и второй DIL входы блока приемника 10 являются первым BDI и вторым BCI входами внешней линии связи, первый DOH и второй DOL выходы блока передатчика 9 являются первым BDO и вторым ВСО выходами внешней линии связи, третьи входы CLKI блока приемника 10 и блока передатчика 9 и соединены с выходом CLKO блока настройки частоты 7, второй вход блока настройки частоты 7 CLKI является внешним сигналом тактовой частоты CLK, вторая группа входов PLI (5..0) блока программируемой логики 8 является входными сигналами PLI (5…0), вторая группа входов INT (7…0) блока прерывания 5 соединена с входными сигналами внешних прерываний INT (1…0) контроллера и с выходами внутренних прерываний INTO блоков приемника 10 и передатчика 9, группы выходов PLO, DO (2…0), DO (7..0) блока программируемой логики 8, блока защищенных портов 6, порта вывода 2 и группы входов-выходов DIO (7…0), первого 3 и второго 4 портов ввода-вывода являются выходами контроллера PLO (3…0), PO (2…0), РА (7…0), РВ (7…0), РС (7…0) соответственно, выход пятого логического элемента 19 соединен с пятым входом RD_DAT блока приемника 10, второй вход порта вывода 2, третьи входы первого и второго портов ввода-вывода, четвертый вход блока прерываний 5, третьи входы блока защищенных портов 6, блока настройки частоты 7, блока программируемой логики 8, четвертый вход блока передатчика 9 и шестой вход блока приемника 10 объединены между собой и соединены с входом начальной установки RST контроллера, входы СР порта вывода, первого и второго портов ввода-вывода объединены между собой и соединены с управляющим входом СС настройки полярности портов контроллера, входы CIO первого и второго портов ввода-вывода объединены между собой и соединены с управляющим входом СВС настройки ввода/вывода портов контроллера, выход REC, входы TR и DI блока приемника 10 соединены с входом REC, выходами TR и DO блока передатчика 9 соответственно.

Устройство работает следующим образом.

С момента подачи сигнала высокого уровня на вход RST контроллер устанавливается в исходное состояние.

Обмен данными между микроконтроллером и контроллером устанавливается в момент подачи на вход CSN сигнала низкого уровня, а на вход А0 высокого. Высокий уровень на выходе логического элемента 18 устанавливает режим обмена данными. Если на входе RDN сигнал низкого уровня, то логический элемент 16 устанавливает блок входа-выхода в состояние вывода данных. Если на входе WRN сигнал низкого уровня, то логический элемент 15 - разрешение дешифратором 13 выбора функций.

Для записи данных в один из блоков на группу входов-выходов DIO (7…0) контроллера выставляется адрес функции, выполняемой блоком, который сохраняется в регистре 12 блока сопряжения с микроконтроллером 1 сигналом высокого уровня по входу ALE. Далее выставляются данные на группу входов-выходов DIO (7…0). По сигналу WRN данные сохраняются в регистре функции одного из блоков.

Для чтения данных в один из блоков на группу входов-выходов DIO (7…0) контроллера выставляется адрес функции, выполняемой блоком, который сохраняется в регистре 12 блока сопряжения с микроконтроллером 1 сигналом высокого уровня по входу ALE. Далее группа входов-выходов DIO (7…0) находится в Z-состоянии. По сигналу RDN данные считываются из регистра 12.

Для передачи по последовательному каналу предварительно необходимо сконфигурировать передатчик 9, по группе входов DI (7…0) поступают конфигурационные данные, записываемые по входу WR_CNFG (функция - новая конфигурация передатчика).

Далее в буфер передатчика 9 по группе входов передаются четыре байта, записываемые по входу WR_DAT (функция - запись данных передатчика), по завершению передачи последнего байта данные поступают к двум выходным линиям последовательного канала BDO и ВСО. С начала передачи на выходе TR устанавливается высокий уровень. Передаваемая информация может контролироваться блоком приемника 10. Для этого с выхода DO на вход DI блока приемника 10 поступает эталонный код, который сравнивается с полученным кодом по линия BDI и BDO. По окончании передачи с группы выходов INTO устанавливается сигнал окончания передачи, поступающий на группу входов INT (7…0) блока прерывания 5.

Для приема по последовательному каналу предварительно необходимо сконфигурировать приемник 10, по группе входов DI (7…0) поступают конфигурационные данные, записываемые по входу WR_CNFG (функция новая конфигурация приемника).

Данные в буфер приемника 10 поступают с двух входов BDI и BCI, с начала приема на выходе REC устанавливается высокий уровень для предотвращения передачи при работе на общую шину. По окончании передачи с группы выходов INTO устанавливается сигнал окончания приема, поступающий на группу входов INT (7…0) блока прерывания 5, выход REC устанавливается в низкий уровень.

В исходном состоянии все прерывания игнорируются. Для активации прерываний их необходимо разрешить в блоке прерываний 5. По группе входов DI (7…0) поступают данные разрешения различных прерываний, записываемые по входу WR_MSK (функция - маскирование прерываний). По группе входов DI (7…0) поступают данные о сбросе отдельных прерываний, записываемые по входу WR_CLR (функция - сброс прерываний). Если установлено хоть одно из разрешенных прерываний, то на выходе INTO устанавливается низкий уровень.

В исходном состоянии порты ввода/вывода 2 и 3 сконфигурированы в зависимости от состояния управляющих входов СС и СВС. Если на входе СВС установлен высокий (низкий) сигнал, тогда порт находится в состоянии ввода (вывода). Если порт находится в состоянии вывода, а на входе СС установлен высокий (низкий) сигнал, тогда линии порта устанавливаются в состоянии высокого (низкого) уровня. По окончанию сброса управляющие входы игнорируются.

Изменение состояния производится по группе входов DI (7…0), записываемых по входу WR_CNFG (функция - изменение состояния портов ввода/вывода).

Для регулировки скоростью обмена данными по последовательному каналу при различных частотах тактирования, предварительно в блок настройки частоты, по группе входов DI (2…0) поступают данные о тактовой частоте, записываемые по входу WR_DAT (функция - новая тактовая частота).

Для исключения возможности ошибочной установки отдельных линий введено усложнение алгоритма записью данных.

В исходном состоянии все защищенные линии блока защищенных портов сброшены. Для установки необходимо по группе входов DI (2…0) установить адрес выбираемой линии, записываемые по входу WR_ADR (функция - выбор защищенной линии). Далее несколько раз по группе входов DI (2…0) различными кодами подтвердить установку. Код записывается по входу WR_DAT (функция - подтверждение установки). Для каждой линии установлена своя последовательность кодов.

Был разработан и изготовлен опытный образец на микросхеме серии 5511БЦ1У, который подтвердил работоспособность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ КОТЕЛЬНОЙ | 2017 |

|

RU2656670C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| ПРОГРАММИРУЕМЫЙ КОНТРОЛЛЕР ПОСЛЕДОВАТЕЛЬНЫХ ШИН | 2007 |

|

RU2360282C2 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2011 |

|

RU2446559C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

Изобретение относится к вычислительной технике. Техническим результатом является повышение достоверности контроля передачи-приема данных. Контроллер интерфейса содержит блок приема, блок передачи, блок сопряжения с микроконтроллером, группа входов-выходов которого является группой входов-выходов контроллера для подключения к шине адреса/данных микроконтроллера, блок прерываний, выход которого является выходом контроллера для подключения к входу запроса прерывания микроконтроллера, порт вывода, первый и второй порты ввода-вывода, блок защищенных портов, блок настройки частоты и блок программируемой логики, блок сопряжения с микроконтроллером включает в себя блок входа-выхода, первый, второй, третий, четвертый и пятый логические элементы, регистр, дешифратор и мультиплексор, первая, вторая, третья, четвертая и пятая группа входов которого соединены с группами выходов первого и второго портов ввода-вывода, группой выходов блока прерываний, третьей группой выходов блока приемника и первой группой выходов блока передатчика соответственно. 2 ил.

Контроллер интерфейса, содержащий блок приема, блок передачи, блок сопряжения с микроконтроллером, группа входов-выходов которого является группой входов-выходов контроллера для подключения к шине адреса/данных микроконтроллера, блок прерываний, выход которого является выходом контроллера для подключения к входу запроса прерывания микроконтроллера, отличающийся тем, что дополнительно введены порт вывода, первый и второй порты ввода-вывода, блок защищенных портов, блок настройки частоты и блок программируемой логики, блок сопряжения с микроконтроллером включает в себя блок входа-выхода, первый, второй, третий, четвертый и пятый логические элементы, регистр, дешифратор и мультиплексор, первая, вторая, третья, четвертая и пятая группа входов которого соединены с группами выходов первого и второго портов ввода-вывода, группой выходов блока прерываний, третьей группой выходов блока приемника и первой группой выходов блока передатчика соответственно, группа выходов мультиплексора соединена с группой входов блока входа-выхода, группа выходов которого подключена к группе входов регистра, группе входов порта вывода, группам входов первого и второго портов ввода-вывода, к первой группе входа блока прерываний, группе входов блока защищенных портов, группе входов блока настройки частоты, к первой группе входов блока программируемой логики, группам входов блоков передатчика и приемника, вход блока входа-выхода соединен с выходом третьего логического элемента, первый вход которого соединен с выходом первого логического элемента и первым входом второго логического элемента, выход которого соединен с входом дешифратора, группа входов которого соединена с шестой группой входов мультиплексора, с группой входов пятого логического элемента и группой выходов регистра, вход которого является одним из управляющих входов контроллера, вторые входы третьего и четвертого логических элементов, третий вход четвертого логического элемента и первый вход первого логического элемента объединены между собой и являются одними из управляющих входов контроллера, вторые входы четвертого, первого и второго логических элементов являются одними из управляющих входов контроллера, группа выходов дешифратора соединена с первым входом порта вывода, первыми и вторыми входами первого и второго портов ввода-вывода, с первым, вторым, третьим входами блока прерываний, первым и вторым входами блока защищенных портов, первым входом блока настройки частоты, первыми и вторыми входами блока программируемой логики, первым и вторым входами блока передатчика и четвертым входом блока приемника, первые и вторые группы выходов блока передатчика и блока приемника объединены между собой соответственно, первые и вторые входы и выходы блока приемника и блока передатчика являются соответственно входами и выходами внешней линии связи, третий вход блока приемника соединен с третьим входом блока передатчика и выходом блока настройки частоты, второй вход которого является внешним сигналом тактовой частоты, вторая группа входов блока программируемой логики является входными сигналами контроллера, вторая группа входов блока прерываний является входными сигналами контроллера и соединена со вторыми группами выходов блока приемника и блока передатчика, группы выходов блока программируемой логики, блока защищенных портов, порта вывода и группы входов-выходов первого и второго портов ввода-вывода являются выходами микроконтроллера, вход пятого логического элемента соединен с выходом третьего логического элемента, а выход пятого логического элемента соединен с пятым входом блока приемника, второй вход порта вывода, третьи входы первого и второго портов ввода-вывода, четвертый вход блока прерываний, третьи входы блока защищенных портов, блока настройки частоты, блока программируемой логики, четвертый вход блока передатчика и шестой вход блока приемника объединены между собой и соединены с входом начальной установки контроллера, третий вход порта вывода, четвертые входы первого и второго портов ввода/вывода объединены между собой и соединены с управляющим входом настройки полярности портов контроллера, пятые входы первого и второго портов ввода/вывода объединены между собой и соединены с управляющим входом настройки ввода/вывода портов контроллера, выход, шестой и седьмой входы блока приемника соединены с пятым входом, третьим и четвертым выходами блока передатчика соответственно.

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Способ получения антималярийного средства | 1936 |

|

SU53030A1 |

| US 2009293071 A1, 26.11.2009 | |||

| US 2010005232 A1, 07.01.2010. | |||

Авторы

Даты

2011-05-20—Публикация

2010-02-19—Подача