Настоящее изобретение относится к области устройств ввода-вывода для процессоров и микроконтроллеров и более точно касается контроллеров последовательных интерфейсов SPI, Microwire, I2S, SPORT.

На современном этапе развития цифровой вычислительной техники остро стоит проблема нехватки внешних выводов микросхемы, а также проблема организации обмена данными процессора с периферийными устройствами без отвлечения вычислительной мощности процессора. Вторую задачу решают перекладыванием задачи управления передачей и обработки данных на контроллер периферийного интерфейса, а также введением каналов DMA (прямого доступа к памяти) для данного контроллера. Первая задача решается путем функционального объединения интерфейсов. Однако в большинстве случаев используется способ, при котором контроллеры различных интерфейсов аппаратно разделены и объединяются путем мультиплицирования сигналов на выходах, что приводит к необоснованному увеличению аппаратных затрат. Кроме того, не решена задача полного объединения функций контроллеров интерфейсов SPI, I2S и SPORT в одном контроллере. Усугубляет ситуацию и то, что нет полной совместимости стандартов SPI (Motorola) [1] и Microwire (National Semiconductor) [2], т.к. выводы последовательных данных MOSI/MISO для SPI могут иметь направление входа или выхода в зависимости от того, является устройство ведущим или ведомым, а направление выводов SDO, SDI у Microwire строго фиксировано.

Классическая реализация интерфейса SPI выполнена в микроконтроллере М68НС11 фирмы Motorolla. Явный недостаток контроллера - отсутствие буферизации по направлению передачи, не позволяющее вести непрерывную передачу, в силу того, что запись новых данных в процессе передачи приводит к потере данных, был исправлен в стандарте QSPI. Стандарт QSPI предполагает наличие буферизации как в направлении передачи, так и в направлении приема, что позволяет записывать и считывать данные непосредственно во время передачи.

Однако совмещение SPI с другими интерфейсами выполняется либо путем мультиплицирования выводов от аппаратно-разделенных контроллеров, либо же схема реализуется с использованием логики захвата внешних сигналов на системный тактовый сигнал, что заметно снижает максимальную частоту передачи по данному интерфейсу.

Наиболее близким техническим решением к заявляемому изобретению (ближайший аналог) является контроллер последовательных шин, входящий в состав микросхемы ADSP-BF537 [3], фирмы Analog Devices, включающий в себя функционал контроллеров SPORT и I2S.

Однако в микросхемах выпускаемых Analog Devices контроллер SPI по-прежнему делается отдельно от совмещенного контроллера SPORT-I2S. Объясняется это тем, что контроллер SPORT-I2S обладает рядом недостатков, затрудняющих его совмещение с SPI. Одним из них является тот факт, что после приема последнего бита порту нужен еще один фронт тактового сигнала для записи данных в буфер, а при передаче по шине SPI с приходом последнего бита формирование тактового сигнала может прекратиться. Использовать же управляющий сигнал SS для управления записью в буфер не представляется возможным, когда речь идет о контроллере, совмещающем несколько интерфейсов.

Кроме того, контроллер SPORT-I2S выполнен в виде независимых приемника и передатчика, а стандартный обмен по шине SPI предполагает управление приемом и передачей одним ведущим устройством, которое для выбора ведомого использует набор управляющих сигналов SS (выбор ведомого), поведение которых принципиально отличается от управляющих сигналов TWS (выбор канала передачи), RWS (выбор канала приема) в стандарте I2S [4], что также исключает возможность полного функционального совмещения контроллера SPORT-I2S с контроллером SPI.

Стремясь сделать процессор более универсальным, на интегральной схеме реализуют несколько контроллеров SPI и несколько контроллеров SPORT-I2S. Это приводит к увеличению количества необходимых выводов микросхемы, а так же к увеличению ее площади. В реальных задачах задействована только определенная часть этих контроллеров, поэтому такие аппаратные затраты являются нерациональными. Логичным шагом является реализация на схеме группы контроллеров, каждый их которых может работать с широким набором интерфейсов, что приводит к более гибкому и рациональному использованию схемы.

Объектом изобретения по настоящей заявке является структурная схема программируемого контроллера последовательных шин, функционально совмещающего в себе возможность работы по интерфейсам SPI, Microwire, I2S и SPORT.

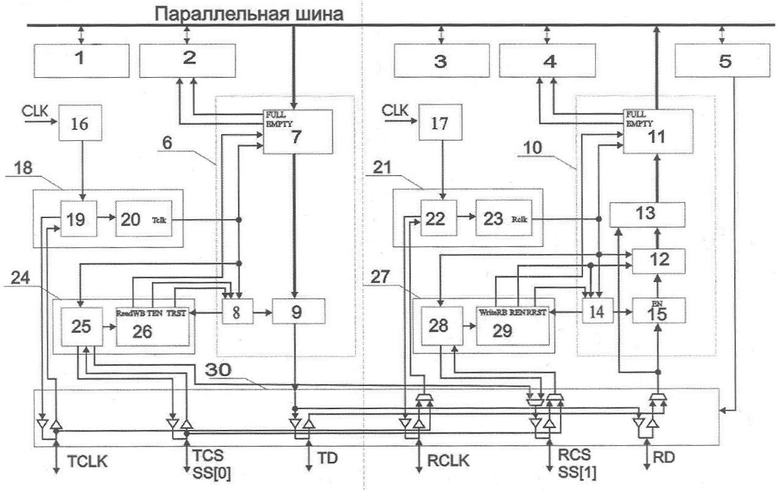

Блок-схема программируемого контроллера последовательных шин согласно настоящему изобретению показана на чертеже, где

1 - регистр управления передатчиком

2 - регистр состояния передатчика

3 - регистр управления приемником

4 - регистр состояния приемника

5 - регистр управления выводами

6 - блок передатчика

7 - буфер записи

8 - счетчик бит передатчика

9 - выходной мультиплексор

10 - блок приемника

11 - буфер чтения

12 - приемный регистр

13 - блок логики обмена

14 - счетчик бит приемника

15 - дешифратор

16 - делитель частоты передатчика

17 - делитель частоты приемника

18 - блок генерации синхроимпульсов передатчика

19 - мультиплексор тактового сигнала передатчика

20 - преобразователь тактового сигнала передатчика

21 - блок генерации синхроимпульсов приемника

22 - мультиплексор тактового сигнала приемника

23 - преобразователь тактового сигнала приемника

24 - блок генерации управляющих сигналов передатчика

25 - формирователь управляющего сигнала передатчика

26 - преобразователь управляющего сигнала передатчика

27 - блок генерации управляющих сигналов приемника

28 - формирователь управляющего сигнала приемника

29 - преобразователь управляющего сигнала приемника

30 - блок управления выводами

Схема контроллера функционально разделена на две части - приемник и передатчик. При этом приемник и передатчик могут работать как независимо (работая по разным интерфейсам и на разных частотах), так и в зависимом состоянии (при этом управляющие и тактовые сигналы передатчика дублируются для приемника), что позволяет приемнику и передатчику использовать один управляющий и один тактовый сигнал при работе порта по одному интерфейсу.

Внешние выводы TCLK, TCS, TD являются соответственно выводами тактового, управляющего сигналов и последовательных данных передатчика, а внешние выводы RCLK, RCS, RD соответственно выводами тактового, управляющего сигналов и последовательных данных приемника. В такой же конфигурации они могут быть использованы и в режиме SPI, однако существует возможность гибкой настройки выводов, позволяющей использовать передатчику оба вывода TCS и RCS в качестве двухразрядной шины выбора ведомого SS [1:0]. Также есть возможность изменять направления выводов TD и RD.

Непосредственно блок передатчика 6 состоит из буфера записи 7, выполненного в виде FIFO, и управляемого счетчиком бит 8 мультиплексора 9, через который выполняется выборка передаваемого бита.

Особенностью блока передатчика является то, что данные для передачи выбираются непосредственно из буфера записи 7. Такая организация позволяет получать на выходе передатчика последовательные данные сразу после записи передаваемого слова в буфер записи. Выборка бита для передачи по последовательному интерфейсу осуществляется из буфера записи через мультиплексор 9, управляемый счетчиком бит 8. Работа счетчика разрешается сигналом TEN (разрешение передачи), чтение из буфера записи осуществляется по фронту тактового сигнала tclk при разрешающем сигнале ReadWB (разрешение чтения из буфера), сброс счетчика осуществляется сигналом trst (сброс счетчика передатчика).

Блок приемника 10 состоит из буфера чтения 11, выполненного в виде FIFO, регистра приема 12, логики обмена 13, встроенной между регистром приема и буфером чтения 11, а также счетчика бит 14 и дешифратора 15. Для определения разряда регистра, в который будут записаны принимаемые данные, используются дешифратор 15, управляемый счетчиком бит 14. Работа счетчика разрешается сигналом REN (разрешение приема), запись в буфер чтения осуществляется по фронту тактового сигнала rclk, при разрешающем сигнале WriteRB (разрешение записи в буфер чтения), сброс счетчика осуществляется сигналом rrst (сброс счетчика приемника).

Логика обмена 13, входящая в состав приемника, выполняет обнуление или дополнение значением старшего разряда избыточных бит. Это позволяет избежать дополнительной программной обработки и возможных ошибок при приеме слов длиной меньше, чем разрядность регистра приема.

Также логика обмена выполняет функцию объединения данных из регистра приема и последнего принимаемого бита, значение которого берется непосредственно с внешнего вывода. Это позволяет записывать принятые данные в FIFO по фронту считывания для последнего бита одновременно с записью последнего бита в приемный регистр, не дожидаясь следующего фронта тактового сигнала.

Тот факт, что данные для передачи готовы сразу после записи передаваемого слова в буфер записи, а принятые данные записываются в буфер чтения одновременно с записью последнего бита в приемный регистр, позволяет без модификаций использовать вышеописанные блоки приема и передачи для работы в любых режимах SPI, SPORT и I2S.

Выборка данных через мультиплексор и запись с использованием дешифратора позволяют с минимальными аппаратными затратами реализовать передачу слов произвольной длины как старшим, так и младшим битом вперед.

Тот факт, что приемник и передатчик управляются шестью универсальными сигналами, не зависящими от выбранного протокола передачи, и срабатывают по фиксированному фронту тактового сигнала, позволяет значительно упростить логику приемника и передатчика и использовать одни и те же блоки для передачи данных по разным интерфейсам. Также это позволяет использовать тактовые и управляющие сигналы, не производя их захват на системный тактовый сигнал, что в результате дает возможность вести передачу с частотой внешнего тактового сигнала, равной FCLK/2, где FCLK - частота системного тактового сигнала.

Контрольные регистры 1, 3 позволяют производить независимую программную настройку передатчика и приемника.

Регистры состояния передатчика и приемника 2, 4 содержат информацию о состоянии буфера чтения и буфера записи, а также флаги прерывания.

Регистр управления выводами 5 содержит биты, позволяющие задавать направление каждого вывода.

Делители частоты 16, 17 позволяют формировать тактовые сигналы для приемника и передатчика путем деления частоты системного тактового сигнала.

Блок генерации синхроимпульсов передатчика 18 состоит из мультиплексора тактового сигнала передатчика 19 и преобразователя тактового сигнала передатчика 20.

Мультиплексор тактового сигнала передатчика позволяет использовать для управления блоком передатчика как внешний тактовый сигнал, так и тактовый сигнал, принимаемый от делителя частоты передатчика.

Преобразователь тактового сигнала передатчика инвертирует тактовый сигнал при необходимости работы передатчика по отрицательному фронту.

Блок генерации синхроимпульсов приемника 21 состоит из мультиплексора тактового сигнала приемника 22 и преобразователя тактового сигнала приемника 23.

Мультиплексор тактового сигнала приемника позволяет использовать для управления блоком приемника как тактовый сигнал, принимаемый от блока управления выводами (который в свою очередь может либо приниматься с внешнего вывода либо дублировать тактовый сигнал передатчика), так и тактовый сигнал, принимаемый от делителя частоты приемника.

Преобразователь тактового сигнала приемника инвертирует тактовый сигнал при необходимости работы приемника по отрицательному фронту.

Использование преобразователей тактового сигнала позволяет использовать в схеме блоки приемника и передатчика, срабатывающие по фиксированному фронту тактового сигнала.

Блок генерации управляющих сигналов передатчика 24 состоит из блоков формирователя управляющего сигнала передатчика 25 и преобразователя управляющего сигнала передатчика 26.

Формирователь управляющего сигнала передатчика в соответствии с настройками выводов выполняет либо формирование управляющего сигнала для выбранного интерфейса (при этом используется тактовый сигнал, принимаемый от логики генерации синхроимпульсов), либо его прием с внешних выводов схемы.

Преобразователь управляющего сигнала передатчика выполняет преобразование интерфейсного управляющего сигнала, принимаемого от формирователя управляющего сигнала передатчика к трем универсальным контрольным сигналам: TEN (разрешение передачи), ReadWB (разрешение чтения из буфера записи) и trst (сброс счетчика передатчика).

Блок генерации управляющих сигналов передатчика содержит логику формирования двухразрядной шины выбора ведомого устройства. При этом младший разряд шины направляется на вывод контрольного сигнала передатчика, а старший разряд на вывод контрольного сигнала приемника, позволяя таким образом в режиме полнодуплексного SPI работать с двумя параллельно подключенными ведомыми устройствами.

Блок генерации управляющих сигналов приемника 27 состоит из блоков формирователя управляющего сигнала приемника 28 и преобразователя управляющего сигнала приемника 29.

Формирователь управляющего сигнала приемника в соответствии с настройками выводов выполняет либо формирование управляющего сигнала для выбранного интерфейса (при этом используется тактовый сигнал, принимаемый от логики генерации синхроимпульсов), либо его прием с внешних выводов схемы.

Преобразователь управляющего сигнала приемника выполняет преобразование интерфейсного управляющего сигнала, принимаемого от формирователя управляющего сигнала приемника к трем универсальным контрольным сигналам: REN (разрешение приема), WriteRB (разрешение записи в буфер чтения) и rrst (сброс счетчика приемника).

Контрольные сигналы, формируемые блоками генерации управляющих сигналов для приемника и передатчика, универсальны и не зависят от выбранного протокола передачи. Это позволяет использовать в схеме универсальные блоки приемника и передатчика, что заметно упрощает логику схемы. Кроме того, управляющие сигналы формируются в автоматическом режиме, что дает возможность контроллеру вести передачу данных без участия процессора.

Блоки генерации управляющих сигналов приемника и передатчика также содержат логику автоматического определения канала для работы в режиме I2S, а блок генерации управляющих сигналов передатчика - логику формирования двухразрядного сигнала выбора ведомого для полнодуплексного режима SPI.

В состав контроллера входят два буфера типа FIFO - буфер записи 7 и буфер чтения 11. Оба буфера представляют собой двухпортовую память. При этом один порт управляется запросами системной шины, а другой - запросами, формируемыми контроллером в процессе передачи. Блоки FIFO также играют роль единственного связующего звена между двумя клоковыми доменами: приемника/передатчика и системной шины. Это позволяет избежать проблем с синхронизацией при работе устройства в режиме ведомого. Кроме того, оба буфера позволяют производить запись и чтение как слов, так и полуслов, что дает возможность порту работать в режиме паковки/распаковки.

Наличие буферов чтения и записи позволяет непосредственно во время передачи считывать уже принятые данные либо записывать данные для новой передачи.

Блок управления выводами 30 позволяет выполнять гибкую настройку выводов, устанавливая направление для каждого вывода, и дублировать управляющие и тактовые сигналы передатчика для приемника. Кроме того, возможно перенаправление данных с выхода передатчика на вывод приемника и с вывода передатчика на вход приемника, что позволяет организовывать передачу в режиме SPI как по стандарту Microwire (SDO, SDI), так и по стандарту Mototrola (MOSI, MISO). Также данный блок содержит логику, позволяющую всему контроллеру работать в режиме полнодуплексного SPI, используя выводы TCS и RCS для выбора двух ведомых устройств, либо в режиме независимых SPI-приемника и SPI-передатчика. В последнем случае приемник и передатчик могут отдельно работать как в режиме ведомого, так и в режиме ведущего, используя каждый свой собственный сигнал выбора ведомого (вывод TCS для передатчика и RCS для приемника).

В общем случае приемник и передатчик могут работать независимо. Однако возможна работа приемника в зависимом от передатчика режиме.

Если передатчик включен и была произведена запись в буфер записи, то в силу того, что данные для передачи выбираются непосредственно из буфера записи, на выходе последовательных данных передатчика сразу появляется первый бит (или последний в зависимости от выбранного порядка передачи бит) передаваемого слова и передатчик готов к передаче данных с приходом первого фронта тактового сигнала. Номер передаваемого бита определяется состоянием счетчика бит передатчика. Счетчик инкрементируется по фронту тактового сигнала при установленном сигнале "разрешение передачи". В случае если значение счетчика бит передатчика стало равным длине передаваемого слова, тогда счетчик сбрасывается и блоком генерации управляющих сигналов передатчика формируется сигнал "Разрешение чтения из буфера записи", после чего на выходе буфера записи появляется следующее передаваемое слово. Счетчик бит передатчика также может быть сброшен сигналом "сброса счетчика передатчика", который формируется либо при программном отключении передатчика, либо при определенном сочетании внешних сигналов (например, переход в высокий уровень шины SS в режиме SPI).

Если приемник включен, то с приходом отрицательного фронта тактового сигнала осуществляется запись принятого бита в регистр приема. Номер бита регистра приема, в который будет произведена запись, определяется состоянием счетчика бит приемника. Счетчик инкрементируется по фронту тактового сигнала при установленном сигнале "разрешение приема". В случае, если значение счетчика бит приемника на единицу меньше длины передаваемого слова, то блоком генерации управляющих сигналов приемника формируется сигнал "Разрешение записи в буфер чтения" и с приходом следующего отрицательного фронта тактового сигнала осуществляется одновременная запись последнего бита в приемный регистр и запись всего принятого слова в буфер чтения. В следующем такте счетчик сбрасывается. Счетчик бит приемника также может быть сброшен сигналом "сброса счетчика приемника", который формируется либо при программном отключении приемника, либо при определенном сочетании внешних сигналов (например, переход в высокий уровень шины SS в режиме SPI).

Блоки генерации синхроимпульсов и генерации управляющих сигналов приемника используются для управления приемником. Блоки генерации синхроимпульсов и генерации управляющих сигналов передатчика используются для управления передатчиком. Приемник и передатчик настраиваются независимо.

На выходе делителя частоты передатчика формируется тактовый сигнал с частотой, равной частоте системного тактового сигнала, поделенной на значение делителя частоты передатчика. Далее, если направление вывода тактового сигнала задано как выход, то на преобразователь тактового сигнала подается сигнал с выхода делителя, этот же сигнал подается на вывод тактового сигнала TCLK, если же направление вывода тактового сигнала задано как вход, то на вход преобразователя тактового сигнала подается тактовый сигнал непосредственно с вывода TCLK. В случае, если порт программно настроен на работу по отрицательному фронту либо выбран режим SPI, предполагающий работу по отрицательному фронту, то на выходе преобразователя тактового сигнала передатчика формируется инвертированный тактовый сигнал, в противном случае тактовый сигнал передается на выход без изменений.

Сформированный таким образом тактовый сигнал передается блоку передатчика и блоку генерации управляющих сигналов передатчика.

На выходе делителя частоты приемника формируется тактовый сигнал с частотой, равной частоте системного тактового сигнала, поделенной на значение делителя частоты приемника. Если в регистре управления приемником установлен бит дублирования тактового сигнала, то на преобразователь тактового сигнала приемника подается сигнал с вывода тактового сигнала передатчика, в противном случае, если направление вывода тактового сигнала задано как выход, то на преобразователь тактового сигнала подается сигнал с выхода делителя, этот же сигнал подается на вывод тактового сигнала RCLK, если же направление вывода тактового сигнала задано как вход, то на вход преобразователя тактового сигнала подается тактовый сигнал непосредственно с вывода RCLK. В случае, если порт программно настроен на работу по отрицательному фронту либо выбран режим SPI, предполагающий работу по отрицательному фронту, то на выходе преобразователя тактового сигнала приемника формируется инвертированный тактовый сигнал, в противном случае тактовый сигнал передается на выход без изменений.

Сформированный таким образом тактовый сигнал передается блоку приемника и блоку генерации управляющих сигналов приемника.

В случае, если направление вывода управляющего сигнала передатчика TCS задано как выход, то управляющие сигналы генерируются формирователем управляющего сигнала передатчика и передаются на вход преобразователя управляющего сигнала передатчика и непосредственно на вывод управляющего сигнала TCS. В противном случае на вход преобразователя управляющего сигнала передатчика подается сигнал, взятый непосредственно с вывода TCS. Преобразователь управляющего сигнала содержит логику, преобразующую интерфейсные управляющие сигналы, поступающие на его вход, к трем универсальным контрольным сигналам, использующимся для управления блоком передатчика. В случае работы в режиме SPI блок генерации управляющих сигналов путем умножения контрольного сигнала, получаемого на выходе формирователя управляющего сигнала передатчика на биты контрольного регистра, отвечающие за выбор ведомого, формирует двухразрядную шину выбора ведомого устройства. При этом младший разряд шины направляется на вывод контрольного сигнала передатчика, а старший разряд на вывод контрольного сигнала приемника, позволяя таким образом в режиме полнодуплексного SPI работать с двумя параллельно подключенными ведомыми.

В случае, если в регистре управления приемником установлен бит дублирования управляющего сигнала, то на вход преобразователя управляющего сигнала приемника подается сигнал с вывода контрольного сигнала передатчика TCS, в противном случае, если направление вывода управляющего сигнала приемника RCS задано как выход, то управляющие сигналы генерируются формирователем управляющего сигнала приемника и передаются на вход преобразователя управляющего сигнала приемника и непосредственно на вывод управляющего сигнала RCS, если же направление вывода управляющего сигнала приемника RCS задано как вход, то на вход преобразователя управляющего сигнала приемника подается сигнал, взятый непосредственно с вывода RCS. Преобразователь управляющего сигнала содержит логику, преобразующую интерфейсные управляющие сигналы, поступающие на его вход, к трем универсальным контрольным сигналам, использующимся для управления блоком передатчика.

В режиме SPI устройство может использоваться как полнодуплексный SPI-контроллер, при этом управляющие сигналы формируются блоком генерации управляющих сигналов передатчика и дублируются для приемника. При этом блок генерации формирует управляющий сигнал "выбора ведомого", который преобразуется в двухразрядную шину "выбора ведомого", причем младший разряд шины идет на вывод TCS передатчика, а второй - на вывод RCS-приемника (направление обоих выводов задано как выход). Для формирования двухразрядной шины "выбора ведомого" используются два разряда контрольного регистра передатчика, в которых содержится информация о том, какое ведомое устройство выбрано.

Заявляемое изобретение согласно данному примеру может быть реализовано как в ПЛИС, например, фирм Xilinx и Altera, так и в составе СБИС микроконтроллеров и микропроцессоров.

Источники информации

1http://www.freescale.com/files/microcontrollers/doc/ref_ manual/M68HC11RM.pdf

2http://www.national.com

3http://www.analog.com/en/prod/0,2877,ADSP-BF537,00.html

4http://www.nxp.com/acrobat_ download/various/I2SBUS.pdf

| название | год | авторы | номер документа |

|---|---|---|---|

| КОНТРОЛЛЕР ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2011 |

|

RU2446559C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| СИСТЕМА ПЕРЕДАЧИ И ОБРАБОТКИ СИГНАЛОВ О СОСТОЯНИИ ОБЪЕКТОВ | 1994 |

|

RU2087036C1 |

| СИСТЕМА ОБЪЕДИНЕНИЯ ЦИФРОВЫХ ПОТОКОВ И СПОСОБ ОБЪЕДИНЕНИЯ ЦИФРОВЫХ ПОТОКОВ (ВАРИАНТЫ) | 2020 |

|

RU2762040C1 |

| МУЛЬТИПЛЕКСОР ПЕРЕДАЧИ ДАННЫХ | 2005 |

|

RU2295148C1 |

| АВТОМАТИЗИРОВАННОЕ РАБОЧЕЕ МЕСТО ОПЕРАТОРА УПРАВЛЕНИЯ ВОЗДУШНЫМ ДВИЖЕНИЕМ | 2001 |

|

RU2219586C2 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| УСТРОЙСТВО КОММУНИКАЦИОННОГО ИНТЕРФЕЙСА ДЛЯ СЕТИ SpaceWire | 2012 |

|

RU2483351C1 |

| ПАРАЛЛЕЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ПРОГРАММИРУЕМОЙ АРХИТЕКТУРОЙ | 2012 |

|

RU2486581C1 |

| КОНТРОЛЛЕР ИНТЕРФЕЙСА | 2010 |

|

RU2419138C1 |

Изобретение относится к устройствам ввода-вывода для процессоров и микроконтроллеров и более точно касается контроллеров последовательных интерфейсов SPI, Microwire, I2S, SPORT. Техническим результатом является расширение функциональной возможности устройства за счет функционального совмещения ряда последовательных интерфейсов. Устройство содержит регистры управления и состояния приемника и передатчика, делители частоты приемника и передатчика, блоки генерации синхроимпульсов приемника и передатчика, каждый из которых состоит из мультиплексора тактового сигнала и преобразователя тактового сигнала, блоки генерации управляющих сигналов приемника и передатчика, каждый из которых состоит из формирователя управляющих сигналов и преобразователя управляющих сигналов, блок передатчика, состоящий из буфера записи, счетчика и мультиплексора, блок приемника, состоящий из буфера чтения, блока логики обмена, приемного регистра, счетчика и дешифратора, блок управления выводами, регистр управления выводами. 1 ил.

Программируемый контроллер последовательных шин, содержащий блок приемника, состоящий из буфера чтения, приемного регистра, счетчика бит и дешифратора, блок передатчика, состоящий из буфера записи, счетчика бит и мультиплексора, регистр управления передатчиком, регистр управления приемником, предназначенных для программной настройки передатчика и приемника, регистр состояния передатчика, регистр состояния приемника, содержащих информацию о состоянии буфера чтения и буфера записи и флаги прерывания, делитель частоты передатчика, на вход которого поступает системный тактовый сигнал, а выход связан с входом мультиплексора тактового сигнала передатчика блока генерации синхроимпульсов передатчика, выход которого связан с входом формирователя управляющих сигналов блока генерации управляющих сигналов передатчика и входом блока передатчика, делитель частоты приемника, на вход которого поступает системный тактовый сигнал, а выход связан с входом мультиплексора тактового сигнала приемника блока генерации синхроимпульсов приемника, выход которого связан с входом формирователя управляющих сигналов блока генерации управляющих сигналов приемника и входом блока приемника, внешние выводы устройства: внешний вывод тактового сигнала приемника, связанный с выходом мультиплексора тактового сигнала приемника, внешний вывод тактового сигнала передатчика, связанный с выходом мультиплексора тактового сигнала передатчика, внешний вывод управляющего сигнала приемника, связанный с выходом формирователя управляющих сигналов приемника, внешний вывод управляющего сигнала передатчика, связанный с выходом формирователя управляющих сигналов передатчика, внешний вывод последовательных данных приемника, связанный с входом блока приемника, внешний вывод последовательных данных передатчика, связанный с выходом блока передатчика, отличающийся тем, что в блок приемника дополнительно включен блок логики обмена, вход которого связан с выходом приемного регистра, а выход связан с входом буфера чтения, выход которого соединен с системной шиной, вход блока приемника соединен с другим входом блока логики обмена и входом дешифратора, выход которого соединен с входом приемного регистра, управляющий вход дешифратора соединен с выходом счетчика бит, в блок генерации синхроимпульсов приемника включен блок преобразования тактовых сигналов, вход которого соединен с выходом мультиплексора тактовых сигналов, а выход - с выходом блока генерации синхроимпульсов приемника, в блок генерации управляющих сигналов приемника включен блок преобразования управляющих сигналов, вход которого соединен с выходом формирователя управляющего сигнала, а выходы, на которых формируются управляющие сигналы «сброс счетчика», «разрешение приема» и «разрешение записи в буфер чтения», соединены соответственно с входом сброса счетчика, входом разрешения работы счетчика и входом разрешения записи в буфер чтения, в блок генерации синхроимпульсов передатчика включен блок преобразования тактовых сигналов, вход которого соединен с выходом мультиплексора тактовых сигналов, а выход - с выходом блока генерации синхроимпульсов передатчика, в блок генерации управляющих сигналов передатчика включен блок преобразования управляющих сигналов, вход которого соединен с выходом формирователя управляющего сигнала, а выходы, на которых формируются управляющие сигналы «сброс счетчика», «разрешение передачи» и «разрешение чтения из буфера записи», соединены соответственно с входом сброса счетчика, входом разрешения работы счетчика и входом разрешения чтения из буфера записи, вход которого соединен с системной шиной, выход соединен с входом мультиплексора, выход которого соединен с выходом блока передатчика, управляющий вход мультиплексора соединен с выходом счетчика бит, в схему устройства дополнительно включен блок управления выводами, подключенный к двунаправленным внешним выводам тактового и управляющего сигналов передатчика, тактового и управляющего сигналов приемника, двунаправленным внешним выводам последовательных данных передатчика и приемника, входу и выходу блока генерации тактовых сигналов приемника, входу и выходу блока генерации тактовых сигналов передатчика, входу и выходу блока генерации управляющих сигналов приемника, входу и выходу блока генерации управляющих сигналов передатчика, выходу последовательных данных блока передатчика, входу последовательных данных блока приемника, дополнительно установлена связь между выходом последовательных данных блока передатчика и внешним выводом последовательных данных приемника, дополнительно установлена связь между входом последовательных данных блока приемника с внешними выводом последовательных данных передатчика, дополнительно установлена связь между выходом старшего разряда двухразрядного управляющего сигнала формирователя управляющего сигнала блока генерации управляющих сигналов передатчика с внешним выводом управляющих сигналов приемника.

| Кухонный очаг | 1922 |

|

SU537A1 |

| ANALOG DEVICES, INC | |||

| Способ обработки целлюлозных материалов, с целью тонкого измельчения или переведения в коллоидальный раствор | 1923 |

|

SU2005A1 |

| ЧЕРЕДОВАНИЕ ИНТЕРФЕЙСОВ | 1999 |

|

RU2231230C2 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| Периферийный контроллер с последовательным интерфейсом | 1988 |

|

SU1631523A1 |

| US 5619720 А, 08.04.1997 | |||

| US 7240129 В2, 03.07.2007. | |||

Авторы

Даты

2009-06-27—Публикация

2007-08-31—Подача