b

10

Изобретение относится к цифровой вычислительной технике и может быть использовано в ЦВМ при создании высокоточных арифметических устройств сложениями вычитания двоично-кодированных чисел с плавающей запятой,представленных в прямом или дополнительном коде.

Целью изобретения является повьш1е- ние точности вычислений.

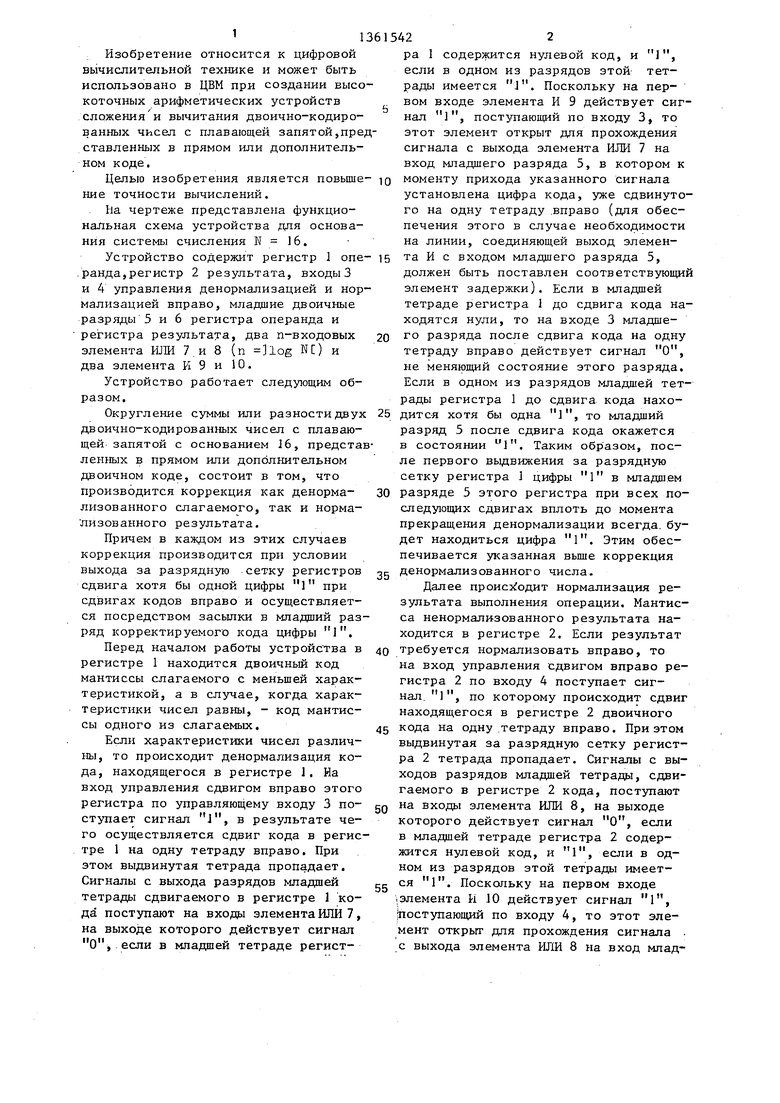

На чертеже представлена функциональная схема устройства для основания системы счисления Н 16.

Устройство содержит регистр J one- 15 ранда,регистр 2 результата, входы 3 и 4 управления денормализацией и нормализацией вправо, младшие двоичные разряды 5 и 6 регистра операнда и регистра результата, два п-входовых элемента ШШ 7. и 8 (п log N) и два элемента И 9 и 10.

Устройство работает следующим образом.

Округление суммы или разности двух двоично-кодированных чисел с плавающей запятой с основанием 16, представ ленных в прямом или дополнительном двоичном коде, состоит в том, что

20

25

производится коррекция как денорма- лизованного слагаемого, так и норма- лизованного результата.

Причем в каждом из этих случаев коррекция производится при условии выхода за разрядную сетку регистров сдвига хотя бы одной цифры 1 при сдвигах кодов вправо и осуществляется посредством засылки в младший разряд корректируемого кода цифры 1.

Перед началом работы устройства в регистре 1 находится двоичный код мантиссы слагаемого с меньшей характеристикой, а в случае, когда, характеристики чисел равны, - код мантиссы одного из слагаемых.

Если характеристики чисел различны, то происходит денормализация кода, находящегося в регистре 1. На вход управления сдвигом вправо этого регистра по управляющему входу 3 поступает сигнал J, в результате чего осуществляется сдвиг кода в регистре 1 на одну тетраду вправо. При этом выдвинутая тетрада пропадает. Сигналы с выхода разрядов младшей тетрады сдвигаемого в регистре 1 кода поступают на входы элемента ИЛИ 7, на выходе которого действует сигнал О, если в младшей тетраде регист

0

5

0

5

0

ра 1 содержится нулевой код, и 1, если в одном из разрядов этой тетрады имеется J. Поскольку на первом входе элемента И 9 действует сигнал , поступающий по входу 3, то этот элемент открыт для прохождения сигнала с выхода элемента ИЛИ 7 на вход младшего разряда 5, в котором к моменту прихода указанного сигнала установлена цифра кода, уже сдвинутого на одну тетраду .вправо (для обеспечения этого в случае необходимости на линии, соединяющей выход элемента И с входом младшего разряда 5, должен быть поставлен соответствующий элемент задержки). Если в младшей тетраде регистра 1 до сдвига кода находятся нули, то на входе 3 младшего разряда после сдвига кода на одну тетраду вправо действует сигнал О, не меняющий состояние этого разряда. Если в одном из разрядов младшей тетрады регистра 1 до сдвига кода находится хотя бы одна 1, то младший разряд 5 после сдвига кода окажется в состоянии . Таким образом, после первого выдвижения за разрядную сетку регистра 1 цифры 1 в младшем разряде 5 этого регистра при всех последующих сдвигах вплоть до момента прекращения денормализации всегда, будет находиться цифра 1. Этим обеспечивается указанная вьш1е коррекция денормализованного числа.

Далее происз одит нормализация результата выполнения операции. Мантисса ненормализованного результата находится в регистре 2. Если результат требуется нормализовать вправо, то на вход управления сдвигом вправо регистра 2 по входу 4 поступает сигнал. 1, по которому происходит сдвиг находящегося в регистре 2 двоичного кода на одну .тетраду вправо. При этом выдвинутая за разрядную сетку регистра 2 тетрада пропадает. Сигналы с выходов разрядов младшей тетрады, сдвигаемого в регистре 2 кода, поступают на входы элемента ИЛИ 8, на выходе которого действует сигнал О, если в младшей тетраде регистра 2 содержится нулевой код, и 1, если в одном из разрядов этой тетрады имеет- g ся 1. Поскольку на первом входе |элемента И JO действует сигнал 1, поступающий по входу 4, то этот элемент открыт для прохождения сигнала . с выхода элемента ИЛИ 8 на вход млад5

0

5

0

шего разряда 6, в котором к моменту прихода указанного сигнала установлена .цифра кода, уже сдвинутого вправо на одну тетраду. Если в младшей тетраде регистра-2 до нормализации результата вправо находится нулевой код то младшая цифра сдвинутого кода не корректируется, так как на входе младшего разряда 6 действует в этом случае сигнал О, не меняюш,ий состояния этого разряда. Если при сдвиге вправо за разрядную сетку регистра 2 выдвигается 1, то на вход младшего разряда 6 поступает сигнал 1, в ре- зультате чего указанный разряд оказывается в состоянии 1. Этим обеспечивается указанная коррекция нормализованного результата.

Округление, осуществляемое устройством, приводит к тому, что погрешность округления может иметь различные знаки независимо от знаков чисел типа кода, в котором они. представлены, и выполняемой операции. Действи- тельно, пусть, например, величины слагаемых таковы, что нормализация вправо результата не проводится. В этом случае погрешность округления складьшается из погрешности денорма- лизации одного из слагаемых, связанной с отбрасыванием выдвинутых за разрядную сетку регистра сдвига битов денормализованного числа, и погрешности, связанной с засылкой J в младший разряд денормализованного числа. Так как появление цифры О или в мпадшем разряде денормализованного слагаемого равновероятно, то засылка в этот разряд цифры 1 дает в половине случаев погрешность, отличную от нуля, которая по абсолютной величине больше погрешности де-

Редактор В.Бугренкова

6291/48

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

5

5 0

0

5

нормализации и имеет противоположный ей знак. Таким образом, в половине случаев погрешность округления положительна, а в половине случаев - отрицательна.

Математическое ожидание погрешности округления, возникающей в процессе работы предлагаемого устройства, строго равно нулю.

Формула изобретения

Устройство для округления суммы и разности двоично-кодированных чисел с плавающей запятой, содержащее регистр операнда и регистр результата, причем вход сдвига вправо на п разрядов (п log N, Ы - основание системы счисления) регистра операнда и регистра результата соединены соответственно с входом управления де- нормализацией и входом управления нормализацией вправо устройства, отличающееся тем, что, с целью повьш1ения точности вычислений, оно содержит два п-входовых элемента ИЛИ и два элемента И, причем входы п нпадших двоичных разрядов регистров операнда и результата соединены соответственно с входами первого и второго п-входовых элементов ИЛИ, выходы которых соединены с первыми входами соответственно первого и второго элементов И, вторые входы которых соединены соответственно с входом управления денормализацией и входом управления нормализацией вправо устройства, выходы первого и второго элементов И соединены с входами младших двоичных разрядов соответственно регистра операнда и регистра результата .

Составитель О.Березикова

Техред А.Кравчук Корректор А. Зимокосов

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для округления суммы и разности двоично-кодированных чисел с плавающей запятой | 1986 |

|

SU1361543A1 |

| Устройство для округления суммы и разности двоичнокодированных чисел с плавающей запятой | 1986 |

|

SU1339549A1 |

| Устройство для округления суммы и разности двоичнокодированных чисел с плавающей запятой | 1986 |

|

SU1339550A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для вычитания чисел с плавающей запятой | 1975 |

|

SU567172A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| ЭФФЕКТИВНАЯ ПАРАЛЛЕЛЬНАЯ ОБРАБОТКА ИСКЛЮЧЕНИЯ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ В ПРОЦЕССОРЕ | 2009 |

|

RU2427897C2 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ПОРЯДКА РЕЗУЛЬТАТА СЛОЖЕНИЯ ЧИСЕЛ С ПЛАВАЮЩЕЙ ЗАПЯТОЙ | 2004 |

|

RU2267806C1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в ЦВМ при создании высокоточных арифметических устройств в сложении и вычитании двоично-кодированных чисел с плавающей запятой, представленных в прямом или дополнительнрм коде. Цель изобретения - повышение точности вычислений. Цель достигается благодаря коррекции как де- нормализованного слагаемого, так и нормализованного результата. Коррекция в каждом из этих случаев осуществляется посредством засылки в младший разряд корректируемого кода цифры 1. Засылка 1 в младший разряд денормализованного слагаемого производится в случае отброса хотя бы одной 1 в процессе денормализации, а засылка 1 в младший разряд результата - в случае отброса хотя бы одной 1 в процессе нормализации. Устройство содержит регистр 1 операнда, регистр 2 результата, входы 3 и 4 управления денормализацией и нормализацией вправо, младшие разряг ды 5,6 регистров, п-входовые элементы ИЛИ 7 и 8, элементы И 9 и 10. 1 ил. сл vTn оэ о:) ел 4;; го

| Китов А.И., Криницкий Н.А | |||

| Электронные цифровые машины и npoi- раммирование.- М., 1961, с.90-93 | |||

| Способ приготовления искусственной массы из продуктов конденсации фенолов с альдегидами | 1920 |

|

SU360A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-27—Подача