Область техники

Настоящее изобретение относится к области запоминающих устройств, в частности к системе и способу для снижения энергопотребления динамического ОЗУ.

Предшествующий уровень техники

Твердотельные динамические ОЗУ (DRAM) представляют собой рентабельное решение памяти большого объема для многих современных вычислительных систем, включая портативные электронные устройства. DRAM, в том числе синхронное динамическое ОЗУ (SDRAM), обеспечивает высокую плотность битов и сравнительно низкую стоимость в расчете на бит по сравнению со структурами быстродействующей внутрикристальной памяти, такими как регистры, статические ОЗУ (SRAM) и тому подобное, а также значительно более высокие скорости доступа, чем электро-, магнито- или оптико-механические блоки памяти большого объема, такие как жесткие диски, ПЗУ на компакт-диске (CD-ROM) и тому подобное.

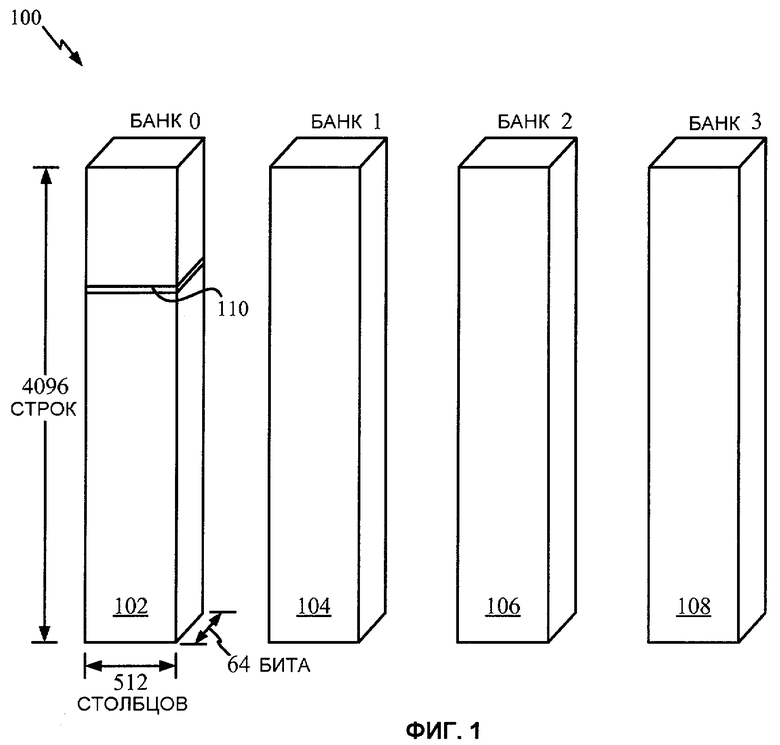

Фиг.1 изображает логическое представление характерной 512- Мбитовой матрицы 100 DRAM. Матрица 100 организована в виде множества отдельно адресуемых банков 102, 104, 106, 108. Каждый банк разделен на большое число, например, 4096, строк 110. Каждая строка 110 раздела на множество столбцов (например, 512 столбцов), а каждый столбец содержит некоторое количество битов данных, как правило, организованных как байты (например, 8 байтов). Различные схемы адресации данных известны в технике. Например, при адресации по банку, строке, столбцу (BRC), адрес памяти может быть интерпретирован как

кристалла

банка

При альтернативной схеме адресации, такой как адресация по строке, банку, столбцу (RBC), адреса памяти могут быть интерпретированы как

кристалла

строки

Матрицы памяти DRAM являются энергозависимыми; данные, сохраненные в матрице DRAM, должны периодически обновляется, чтобы сохранить свою целостность. Во время операции обновления DRAM, большое количество ячеек хранения данных одновременно считываются из матрицы 100 и повторно загружаются. Традиционно, матрицы DRAM обновляются строка за строкой. То есть строка - или, в некоторых реализациях, та же самая строка одновременно в каждом банке - выбирается, и все данные в строке обновляются в одной операции. Используемый здесь термин "независимо обновляемый блок памяти" или IRMU, относится к кванту данных, которые обновляются в рамках одной операции обновления. IRMU для матрицы DRAM, как правило, является строкой, хотя настоящее изобретение не ограничивается операцией обновления строка за строкой.

Операции обновления, направленные на IRMU, обычно перемежаются с доступами к памяти, и спланированы по времени так, что вся матрица DRAM обновляется, прежде чем какие-либо данные будут потеряны вследствие снижения заряда. Традиционно, адреса обновления - то есть адрес каждого независимо обновляемого блока памяти - поставляются контроллером памяти, таким как процессор, который определяет операцию обновления с помощью уникальной комбинации сигналов управления. Современные компоненты SDRAM могут включать в себя два дополнительных режима обновления: самообновление и автоматическое обновление. В обоих режимах компонент SDRAM включает в себя внутренний счетчик адреса обновления. Самообновление используется во многих системах, таких как электронные устройства с батареями питания, которые используют "неактивный" режим для энергосбережения. В режиме самообновления компонент SDRAM не является доступным для хранения и извлечения данных, однако SDRAM выполняет операции обновления внутренним образом для обеспечения целостности хранимых данных. В режиме автоматического обновления контроллер памяти определяет операцию обновления, но не обеспечивает адрес обновления. Вместо этого компонент SDRAM обеспечивает приращение внутреннему счетчику адресов обновления, который обеспечивает последовательные независимо обновляемые адреса блоков памяти (например, строки).

Каждая операция обновления потребляет энергию, когда данные считываются из матрицы DRAM и перезаряжаются. Однако особенно после включения питания или системного сброса, большинство ячеек хранения памяти в матрице DRAM не содержат действительных данных.

Сущность изобретения

В соответствии с одним или несколькими вариантами осуществления раскрытыми и заявленными здесь, поддерживается указатель, который указывает, содержит или нет обновляемый сегмент памяти действительные данные. Когда операция обновления направлена на ассоциированную память, операция обновления подавляется, если память не содержит действительных данных. Значительная экономия питающей мощности может быть реализована путем подавления операций обновления, направленных на недействительные данные.

Один вариант осуществления относится к способу обновления динамической памяти. Указатель ассоциирован с каждым независимо обновляемым блоком памяти. После записи данных в независимо обновляемый блок памяти ассоциированный указатель устанавливается, чтобы отражать действительные данные. Только независимо обновляемые блоки памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в нем, обновляются.

Один вариант осуществления относится к компоненту DRAM. Компонент DRAM включает в себя матрицу DRAM, действующую для хранения данных и организованную как множество независимо обновляемых блоков памяти. Компонент DRAM также включает в себя множество указателей, каждый из которых ассоциирован с независимо обновляемым блоком памяти и указывает, являются ли действительными данные, хранящиеся в независимо обновляемом блоке памяти. Компонент DRAM также включает в себя контроллер, принимающий сигналы управления и действующий для проверки указателей и обновления только независимо обновляемых блоков памяти, хранящих действительные данные.

Краткое описание чертежей

На фиг.1 представлена функциональная блок-схема организации данных в матрице DRAM.

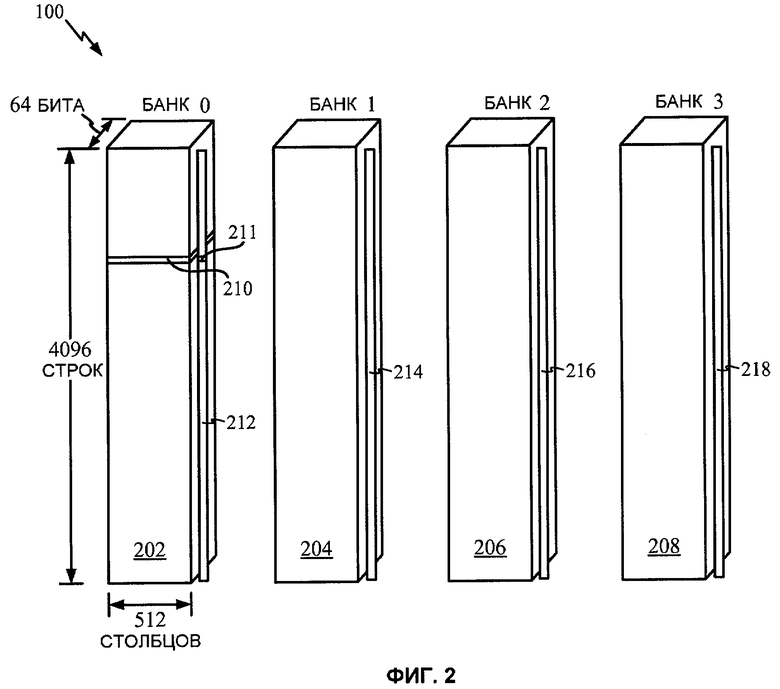

Фиг.2 представляет функциональную блок-схему организации данных в матрице DRAM с указателем или битом действительности, ассоциированным с каждым независимо обновляемым блоком памяти.

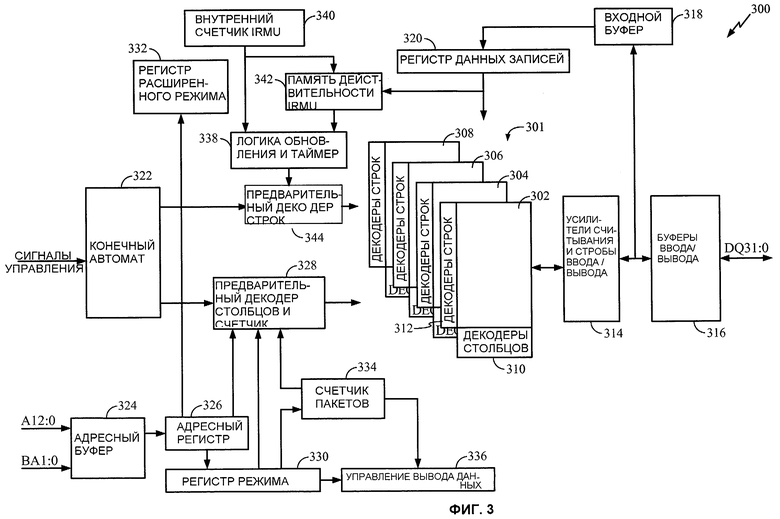

Фиг.3 представляет функциональную блок-схему компонента SDRAM.

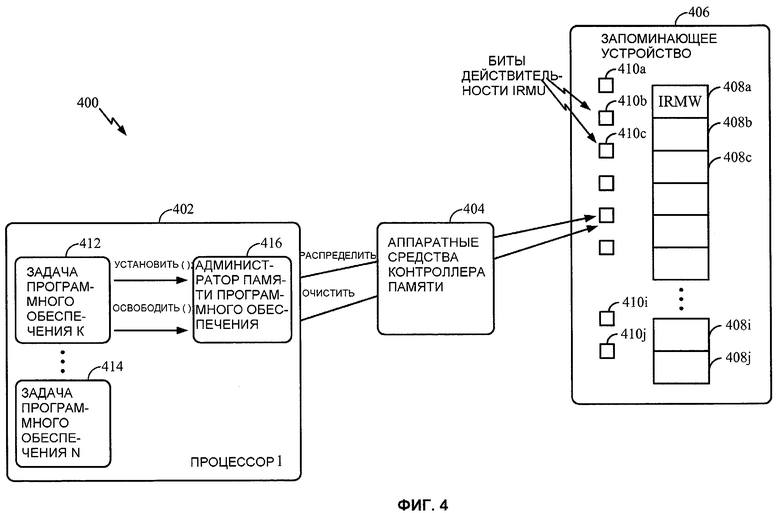

Фиг.4 представляет функциональную блок-схему однопроцессорной вычислительной системы.

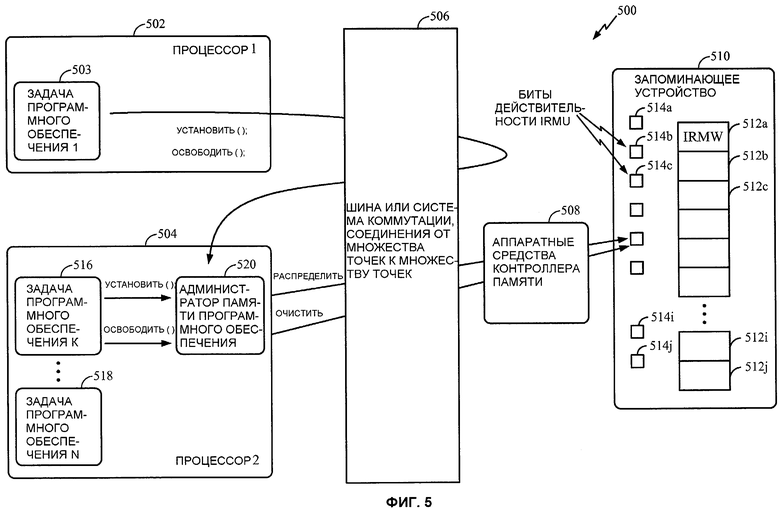

Фиг.5 представляет функциональную блок-схему многопроцессорной вычислительной системы.

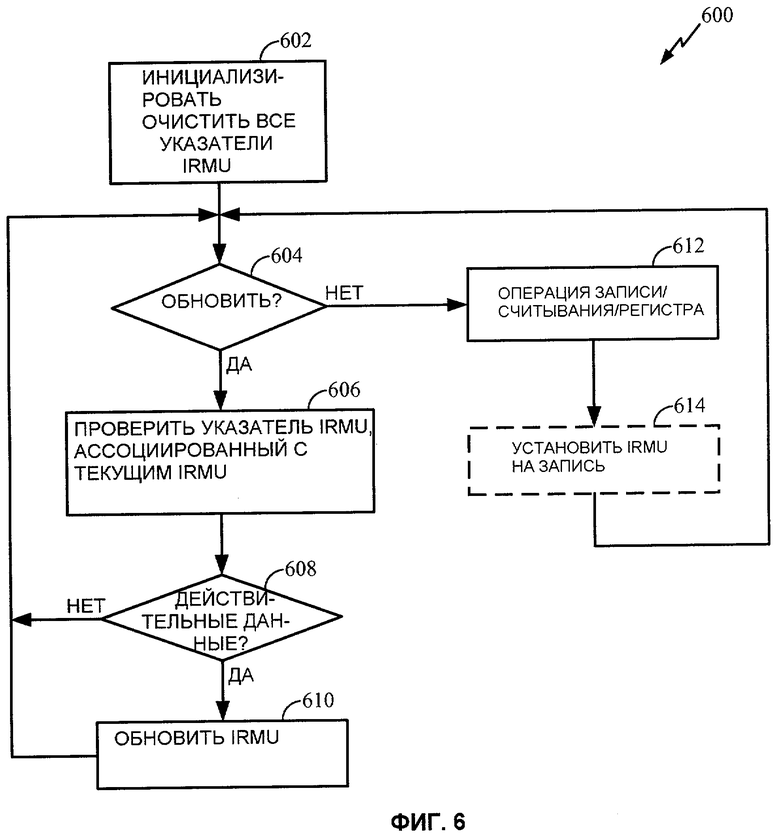

Фиг.6 - блок-схема способа обновления матрицы DRAM.

Детальное описание

Фиг.2 изображает логическое представление организации матрицы DRAM 200 в соответствии с одним вариантом осуществления. Матрица 200 логически организована как четыре банка 202, 204, 206, 208, причем каждый банк содержит 4096 строк. Характерная строка изображается как 210. В этом варианте осуществления строка 210 является наименьшим независимо обновляемым блоком памяти. Со строкой 210 в матрице 200 ассоциирован указатель 211, отражающий то, содержит ли строка 210 действительные данные. В показанном варианте осуществления каждый указатель 211 содержит один бит, а также упоминаемый в настоящем документе как бит действительности, ассоциированный с каждой строкой. Фиг.2 изображает наборов битов 212, 214, 216, 218 указателей, причем каждый бит-указатель ассоциирован с банками 202, 204, 206, 208 соответственно. В одном варианте осуществления, где наименьший независимо обновляемый блок памяти содержит строку, охватывающую все четыре банка 202, 204, 206, 208, потребуется только один набор битов-указателей 212.

Во время операции обновления проверяется индикатор или бит действительности, например, указатель 211, ассоциированный с текущим адресуемым независимо обновляемым блоком памяти, например, IRMU 210. Если установлен бит-индикатор, указывающий, что ассоциированный IRMU содержит действительные данные, то операция обновления выполняется над IRMU, чтобы сохранить данные. Если бит-индикатор не установлен, указывая, что ассоциированный IRMU не содержит действительных данных, в одном варианте осуществления операция обновления подавляется, что позволяет экономить мощность питания, которая в противном случае потреблялась бы при обновлении IRMU. Таким образом, только IRMU, которые содержат действительные данные, будут обновляться, а IRMU в матрице, которые находятся в неинициализированном или в безразличном состоянии, не обновляются. Адрес обновления может быть предоставлен контроллером памяти, или может генерироваться внутренним адресным счетчиком, например, при автоматическом обновлении или самообновлении.

Биты-индикаторы могут поддерживаться различными путями. В одном варианте осуществления биты-индикаторы хранятся в фиксированной или программируемой части матрицы 200 памяти. В этом случае полезный размер матрицы 200 снижается на 0,003%. В другом варианте осуществления биты-индикаторы хранятся в компоненте DRAM/SDRAM в памяти иной, чем матрица DRAM 200, например, в структуре статической оперативной памяти, в регистрах и т.п. В одном варианте осуществления память индикатора действительности IRMU доступна через 2-цикловую последовательность, подобную последовательностям доступа регистра режима и регистра расширенного режима компонентов SDRAM.

Фиг.3 представляет собой функциональную блок-схему компонента SDRAM 300 в соответствии с одним вариантом осуществления. SDRAM 300 включает в себя матрицу DRAM 301, организованную в виде четырех банков 302, 304, 306, 308. Каждый банк содержит декодеры 312, 310 строк и столбцов. Усилитель 314 считывания выводит считанные данные из матрицы DRAM 301 на буферы 316 ввода-вывода. Записанные данные из буферов 316 ввода-вывода проходят через входной буфер 318 и сохраняются в регистре 320 данных записи перед записью в матрицу DRAM 301.

Работа компонента SDRAM 300 управляется конечным автоматом 322. Адреса банков и памяти вводятся в адресный буфер 324 и сохраняются в адресном регистре 326, где они управляют схемой 328 предварительного декодера столбцов и счетчика. Регистр 330 режима и регистр 332 расширенного режима сохраняют биты выбора режима, такие как задержка строба адреса столбца (CAS), длина пакета и т.п., которые управляют работой счетчика 334 пакетов и схемой 336 управления выводом данных.

Схема 338 логики обновления и таймера принимает адреса IRMU от внутреннего счетчика 340 и биты действительности IRMU из памяти 342 действительности IRMU. Логика обновления выводит адреса IRMU на предварительный декодер 344 строк. Заметим, что хотя память 342 действительности IRMU изображена на фиг.3 как функциональный блок, отдельный от матрицы DRAM 301, память, физически выделенная для хранения указателей действительности IRMU, может быть частью матрицы DRAM 301, или могут иметься отдельные DRAM, SRAM, регистры или другая память.

В одном варианте компонент SDRAM 300 автоматически контролирует адреса записи и устанавливает указатель действительности IRMU соответственно IRMU, на который направлена каждая операция записи. Логика 338 обновления затем проверяет память 342 действительности IRMU после каждой операции обновления, и подавляет циклы обновления, направленные на любой IRMU, который не содержит действительных данных. Это минимизирует энергопотребление компонента SDRAM 300, но не требует никакого знания об обновлении-подавлении или участия контроллера памяти или процессора. Основная экономия электроэнергии может иметь место после включения питания или сброса, когда матрица DRAM 301 большей частью не заполнена действительными данными. По мере того как контроллер памяти записывает данные в большее количество IRMU в матрице DRAM 301, устанавливается больше битов действительности IRMU, и подавляется меньше циклов обновления. В этом варианте осуществления память 342 IRMU автоматически очищается как часть инициализации компонента SDRAM 300 после включения питания или сброса. Этот вариант осуществления позволяет разработчикам систем получать выгоду от низкого энергопотребления компонента SDRAM 300 при использовании существующих контроллеров памяти и программного обеспечения, которые не включают сложные функции управления памятью.

В одном варианте осуществления память 342 IRMU может быть очищена по команде с контроллера памяти, такой как предварительно определенная операция записи регистра 330 режима или регистра 332 расширенного режима или комбинация битов. Этот вариант осуществления позволяет сократить потребляемую мощность компонента SDRAM 300 после программно-инициированного сброса, но требует, чтобы контроллер памяти выдавал команду очистки памяти 342 IRMU.

Фиг.4 изображает вычислительную систему 400, которая управляет и снижает энергопотребление DRAM. Система 400 включает в себя контроллер памяти, такой как процессор 402, аппаратные средства 404 контроллера памяти (которые могут быть интегрированы с процессором 402) и устройство памяти, такое как компонент SDRAM 406. Матрица DRAM в компоненте SDRAM 406 логически делится на независимо обновляемые блоки памяти 408а, 408b, 408c, … 408j. С каждым IRMU ассоциирован указатель действительности IRMU, такой как бит 410а, 410b, 410c, … 410j, который указывает, содержит ли ассоциированный IRMU действительные данные.

Множество задач 412, 414 программного обеспечения выполняются на процессоре 402. Каждая задача программного обеспечения может распределить память для хранения данных и может освободить память, которая больше не требуется. Администратор 416 памяти программного обеспечения представляет собой программный модуль, который управляет памятью для процессора 402. Администратор 416 памяти программного обеспечения принимает запросы "распределить" и/или "освободить" память от задач 412, 414 программного обеспечения. В ответ администратор 416 памяти программного обеспечения распределяет память для и от задач 412, 414, отображает распределенную память одному или более независимо обновляемым блокам 408а, 408b, 408c, … 408j памяти (например, строкам) и устанавливает и сбрасывает соответствующие указатели 410а, 410b, 410c, … 410j действительности IRMU, чтобы отразить статус данных в текущее время в IRMU 408f, 408b, 408c, … 408j. В одном варианте осуществления контроллер текущей памяти является независимым элементом 404 аппаратных средств, в другом варианте осуществления функциональность контроллера памяти интегрирована в процессор 402. Компонент SDRAM 406 подавляет все операции обновления, направленные на IRMU 408а, 408b, 408c, … 408j, которые содержат недействительные данные.

На фиг.5 показана многопроцессорная система, которая управляет распределением памяти и минимизирует потребление мощности SDRAM. Процессоры 502, 504 осуществляют связь друг с другом и с аппаратными средствами 508 контроллера памяти через системную шину 506. Шина 506 также может быть реализована в виде системы коммутации, координатного коммутатора и т.п., как известно в технике. Одна или более задач 503, 516, 518 программного обеспечения выполняются на процессорах 502, 504. Системный администратор 520 памяти программного обеспечения выполняется на одном процессоре 504, распределяя память к и от всех программных задач 503, 516, 518, исполняющихся в системе. Любая программная задача 503, исполняющаяся на процессоре 502, может посылать запросы распределения и освобождения памяти к администратору 520 памяти программного обеспечения по шине 506. Как описано выше, администратор 520 памяти программного обеспечения распределяет память к и от задач 503, 516, 518, отображает распределенную память на один или более независимо обновляемых блоков 512a, 512b, 512с, … 512j памяти и устанавливает и сбрасывает соответствующие указатели 514a, 514b, 514c, … 514j действительности IRMU через аппаратное средство 508 контроллера памяти для отражения состояния данных, сохраненных в текущее время в IRMU 512a, 512b, 512с, … 512j. Компонент SDRAM 510 подавляет операции обновления, направленные на IRMU 512a, 512b, 512с, … 512j, которые содержат недействительные данные.

В обычном режиме обновления, режиме автоматического обновления или режиме самообновления, компонент SDRAM 300, 406, 510 сравнивает адреса обновления (предоставляемые контроллером памяти или внутренним счетчиком) с памятью 342, 410, 514 действительности IRMU и подавляет операции обновления, направленные на IRMU 408, 512, которые не содержат действительных данных. В одном варианте осуществления, в котором администратор 416, 520 памяти программного обеспечения активно управляет памятью и устанавливает/очищает биты 410, 514 действительности IRMU, система может дополнительно оптимизировать обновление памяти и минимизировать энергопотребление путем динамического подавления команд обновления IRMU, когда физическая память освобождается из распределения для программных задач и возвращается в "пул", в этом случае ее содержимое данных не является релевантным.

В обычном режиме обновления администратор 416, 520 памяти программного обеспечения может обеспечивать обновление адресов только IRMU 408, 512, содержащих действительные данные. В режиме автоматического обновления или режиме самообновления компонент SDRAM 300, 406, 510 может "пропустить" недействительную память, путем приращения своего адресного счетчика обновления до следующего IRMU 408, 512 содержащего действительные данные, вслед за каждой операцией обновления. В любом случае контроллер 404, 508 памяти может увеличить задержку между операциями обновления, так что только IRMU 408, 512, которые содержат действительные данные, все обновляются с максимальным периодом обновления. В этом варианте осуществления никакие команды обновления не подавляются компонентом SDRAM 300, 406, 510. Это дополнительно оптимизирует потребление энергии (и уменьшает перегрузку шины), избегая ненужных циклов команд памяти, и сокращает задержки, которые команды обновления накладывают на текущие обращения к памяти.

Фиг.6 изображает способ 600 обновления DRAM в соответствии с одним или несколькими вариантами осуществления. При инициализации все указатели IRMU очищаются (блок 602). Способ затем проверяет, должна ли выполняться операция обновления (блок 604). В традиционном режиме обновления операция обновления указывается сигналами управления, направляемыми на компонент DRAM из контроллера памяти, и IRMU, подлежащий обновлению, указывается на адресной шине. В режиме автоматического обновления операция обновления предписывается командами контроллера памяти, и внутренний счетчик обеспечивает адреса обновления IRMU. В режиме самообновления истечение таймера обновления указывает, что требуется операция обновления, и внутренний счетчик предоставляет адрес IRMU.

Если указывается операция обновления (блок 604), указатель IRMU, ассоциированный с текущим адресом IRMU (таким как, например, адрес строки), проверяется (блок 606). Если указатель IRMU указывает, что IRMU содержит действительные данные (блок 608), то операция обновления выполняется над адресованным IRMU (блок 610). Если указатель IRMU указывает, что IRMU не содержит действительных данных (блок 608), то операция обновления подавляется, экономя энергию, которая иначе была бы израсходована на обновление недействительных (или "безразличных") данных.

В режиме самообновления SDRAM компонент ожидает в блоке 604 следующего истечения счетчика адреса обновления. В других режимах обновления, если операция обновления не предписывается командами (блок 604), DRAM (или SDRAM) компонент выполняет операции считывания, записи и/или доступа к регистру, как предписывается командами контроллера памяти (блок 612). В одном варианте осуществления, в котором программный модуль управления памятью распределяет и освобождает блоки памяти, операции доступа к памяти или регистру могут включать в себя операции, направленные на память IRMU - считывание, настройку и очистку указателей IRMU. В одном варианте осуществления указатель IRMU автоматически устанавливается после операции записи, направленной на ассоциированный IRMU (блок 614). В этом варианте осуществления указатели IRMU лишь сбрасываются при инициализации (блок 602), но могут обеспечивать значительную экономию энергопитания до тех пор, пока действительные данные не будут записаны, по меньшей мере, однократно во многие IRMU.

Путем применения программной парадигмы управления памятью - где память релевантна, только когда она распределяется задаче, и предполагает «безразличное» состояние до распределения или после освобождения - к физическим операциям обновления матрицы DRAM, значительная экономия мощности питания может быть реализована за счет устранения ненужных операций обновления, направленных на сегменты памяти, которые не имеют действительных данных. В одном из вариантов осуществления отслеживание действительных данных путем установки ассоциированных IRMU битов происходит автоматически. В этом варианте энергосберегающие преимущества настоящего изобретения доступны в системах без программного управления памятью или знания о возможности выборочного подавления операций обновления. В других вариантах прямое управление памятью IRMU обеспечивает возможность применения сложного управления памятью и получения максимальной экономии энергопитания.

Используемый здесь термин "независимо обновляемый блок памяти" или IRMU относится к сегменту (кванту) данных, которые обновляются в рамках одной операции обновления. IRMU для матрицы DRAM, как правило, представляет собой строку, хотя настоящее изобретение не ограничено этим. Используемый здесь термин "установить" относится к записи данных в указатель IRMU, чтобы указать, что действительные данные хранятся в ассоциированном IRMU, независимо от значения данных (например, 0 или 1, или многобитовая комбинация). "Очистить" относится к записи данных в указатель IRMU, чтобы указать, что действительные данные не хранятся в ассоциированном IRMU, независимо от значения данных (например, 0 или 1, или многобитовая комбинация). Используемый в настоящем документе термин "матрица DRAM" относится к матрице памяти с динамическим случайным доступом, которая хранит данные в интегрированных компонентах схем как DRAM, так и SDRAM. Как используется в настоящем документе, в объем терминов "DRAM" или "компонент DRAM" включаются как компоненты асинхронной памяти DRAM, так и компоненты SDRAM. Используемый здесь термин "распределять" относится к назначению диапазона адресов памяти для программных задач, а термин "освобождать" означает возвращение ранее распределенных адресов памяти в пул нераспределенной памяти.

Хотя в настоящем изобретении было описано здесь в связи с конкретными признаками, аспектами и вариантами осуществления, должно быть очевидно, что многочисленные вариации, модификации и другие варианты осуществления возможны в широком объеме настоящего изобретения и, соответственно, все вариации, модификации и варианты осуществления должны рассматриваться как входящие в объем изобретения. Поэтому представленные варианты осуществления следует рассматривать во всех аспектах как иллюстративные, а не ограничительные, и все изменения, находящиеся в диапазоне значения и эквивалентности приложенных пунктов формулы изобретения, предполагаются охватываемыми ими.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНДИКАТОР ИЗМЕНЕНИЙ ДЛЯ УМЕНЬШЕНИЯ ПОТРЕБЛЕНИЯ ЭНЕРГИИ ПРИ НЕУДАЧНЫХ ОБРАЩЕНИЯХ К КЭШ-ПАМЯТИ | 2006 |

|

RU2390855C2 |

| МЕХАНИЗМ ЗАПРОСА ПОЗДНЕЙ БЛОКИРОВКИ ДЛЯ ПРОПУСКА АППАРАТНОЙ БЛОКИРОВКИ (HLE) | 2008 |

|

RU2501071C2 |

| ОТОБРАЖЕНИЕ ВСТРОЕННОГО АДРЕСА ЕСС | 2014 |

|

RU2644529C2 |

| ГИБРИДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ЕДИНЫМ ИНТЕРФЕЙСОМ | 2007 |

|

RU2442211C2 |

| ПАРАЛЛЕЛЬНАЯ ПРОЦЕССОРНАЯ СИСТЕМА | 1991 |

|

RU2084953C1 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ ДЛЯ ВЫСОКОСКОРОСТНОГО УПРАВЛЕНИЯ ДОСТУПОМ К СРЕДЕ | 2007 |

|

RU2491737C2 |

| УПРАВЛЕНИЕ ПАМЯТЬЮ ДЛЯ ВЫСОКОСКОРОСТНОГО УПРАВЛЕНИЯ ДОСТУПОМ К СРЕДЕ | 2007 |

|

RU2419226C2 |

| ПЕРЕРАСПРЕДЕЛЕНИЕ СЕГМЕНТОВ ПАМЯТИ ДЛЯ РЕШЕНИЯ ПРОБЛЕМЫ ФРАГМЕНТАЦИИ | 2013 |

|

RU2666241C2 |

| ОПРЕДЕЛЕНИЕ ПРОФИЛЯ ПУТИ, ИСПОЛЬЗУЯ КОМБИНАЦИЮ АППАРАТНЫХ И ПРОГРАММНЫХ СРЕДСТВ | 2013 |

|

RU2614583C2 |

| СПОСОБ И СИСТЕМА ДЛЯ ОБНОВЛЕНИЯ ДИНАМИЧЕСКОГО ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА (DRAM) И УСТРОЙСТВО | 2015 |

|

RU2665883C2 |

Изобретение относится к вычислительной технике. Технический результат заключается в снижении энергопотребления динамической оперативной памяти. Способ обновления матрицы динамической оперативной памяти (DRAM), организованной в виде множества независимо обновляемых блоков памяти, содержащий: ассоциирование указателя с каждым независимо обновляемым блоком памяти; при записи данных в независимо обновляемый блок памяти, установку ассоциированного указателя для отражения действительных данных; увеличение задержки между операциями обновления, пропорционально ненулевому числу подавленных циклов обновления, причем цикл обновления подавляется, если ассоциированный указатель отражает недействительные данные, таким образом, чтобы только все независимо обновляемые блоки памяти, которые содержат действительные данные, могли обновляться с максимальным периодом обновления; и обновление с упомянутым максимальным периодом обновления только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них. 3 н. и 23 з.п. ф-лы, 6 ил.

1. Способ обновления матрицы динамической оперативной памяти (DRAM), организованной в виде множества независимо обновляемых блоков памяти, содержащий:

ассоциирование указателя с каждым независимо обновляемым блоком памяти;

при записи данных в независимо обновляемый блок памяти, установку ассоциированного указателя для отражения действительных данных; увеличение задержки между операциями обновления, пропорционально ненулевому числу подавленных циклов обновления, причем цикл обновления подавляется, если ассоциированный указатель отражает недействительные данные, таким образом, чтобы только все независимо обновляемые блоки памяти, которые содержат действительные данные, могли обновляться с максимальным периодом обновления; и обновление с упомянутым максимальным периодом обновления только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них.

2. Способ по п.1, в котором независимо обновляемым блоком памяти является строка.

3. Способ по п.1, в котором независимо обновляемый блок памяти содержит строку по двум или более банкам памяти.

4. Способ по п.1, в котором указателем является бит действительности.

5. Способ по п.4, в котором бит действительности сохранен в матрице DRAM.

6. Способ по п.4, в котором бит действительности сохранен в статической памяти.

7. Способ по п.4, в котором бит действительности сохранен в регистре.

8. Способ по п.1, в котором установка ассоциированного указателя для отражения действительных данных включает в себя установку указателя по команде от контроллера памяти.

9. Способ по п.1, в котором указатели, установленные для отражения действительных данных, очищаются при сбросе.

10. Способ по п.1, в котором указатели, установленные для отражения действительных данных, очищаются по команде от контроллера памяти.

11. Способ по п.1, в котором обновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них, содержит самообновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них.

12. Способ по п.1, в котором обновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них, содержит автоматическое обновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них.

13. Способ по п.1, в котором обновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них, содержит последовательное обновление несмежных независимо обновляемых блоков памяти.

14. Способ по п.1, в котором обновление только независимо обновляемых блоков памяти, у которых ассоциированный указатель отражает действительные данные, сохраненные в них, содержит:

прием команды обновления;

проверку указателя, ассоциированного с текущим адресом обновления; и если указатель отражает действительные данные, обновление адресуемого независимо обновляемого блока памяти.

15. Способ по п.13, дополнительно содержащий, если указатель отражает действительные данные, выполнение приращения адреса обновления до следующего независимо обновляемого блока памяти, имеющего указатель, отражающий действительные данные.

16. Компонент динамической оперативной памяти (DRAM), содержащий матрицу DRAM, действующую для хранения данных, причем матрица DRAM организована как множество независимо обновляемых блоков памяти, причем компонент DRAM дополнительно содержит:

множество указателей, каждый из которых ассоциирован с независимо обновляемым блоком памяти, для указания, сохранены ли действительные данные в независимо обновляемом блоке памяти;

причем каждый ассоциированный указатель выполнен с возможностью установки при записи данных в независимо обновляемый блок памяти, таким образом, чтобы отражать действительные данные, сохраненные в блоке; и

контроллер, выполненный с возможностью увеличения задержки между операциями обновления, пропорционально ненулевому числу подавленных циклов обновления, причем цикл обновления подавляется, если ассоциированный указатель отражает недействительные данные, таким образом, чтобы только все независимо обновляемые блоки памяти, которые содержат действительные данные, могли обновляться с максимальным периодом обновления;

причем контроллер дополнительно выполнен с возможностью проверки указателей и обновления с упомянутым максимальным периодом обновления только независимо обновляемых блоков памяти, ассоциированные указатели которых отражают действительные данные, сохраненные в блоке.

17. Компонент DRAM по п.16, дополнительно содержащий счетчик обновления, действующий для генерации адресов независимо обновляемых блоков памяти в матрице DRAM.

18. Компонент DRAM по п.16, дополнительно содержащий модуль управления памятью, действующий для установки указателя, когда данные записываются в ассоциированный независимо обновляемый блок памяти.

19. Компонент DRAM по п.16, в котором указатели очищаются в процессе инициализации.

20. Компонент DRAM по п.16, в котором контроллер дополнительно действует для установки или очистки указателей в ответ на сигналы управления.

21. Компонент DRAM п.16, в котором указатели хранятся в одном или более независимо обновляемых блоках памяти.

22. Машиночитаемый носитель, включающий в себя, по меньшей мере, компьютерную программу управления памятью, действующую для выполнения этапов способа по любому из пп.1-15.

23. Машиночитаемый носитель по п.22, в котором компьютерная программа управления памятью дополнительно действует для выполнения следующих этапов:

приема запросов из программной задачи для освобождения памяти, ранее распределенной этой задаче;

освобождения памяти, ранее распределенной задаче; и

если вся память в независимо обновляемом блоке памяти освобождена, очистки ассоциированного указателя, чтобы предписывать запоминающему устройству подавлять операции обновления,

направленные на этот независимо обновляемый блок памяти.

24. Машиночитаемый носитель по п.22, в котором компьютерная программа управления памятью распределяет память для множества программных задач, исполняемых на одном процессоре.

25. Машиночитаемый носитель по п.22, в котором компьютерная программа управления памятью распределяет память для двух или более программных задач, каждая из которых исполняется на другом процессоре.

26. Машиночитаемый носитель по п.22, в котором компьютерная программа управления памятью устанавливает указатель независимо обновляемого блока памяти после первоначальной записи данных в ассоциированный независимо обновляемый блок памяти.

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| US 6415353 B1, 02.07.2002 | |||

| Способ и приспособление для нагревания хлебопекарных камер | 1923 |

|

SU2003A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| УСТРОЙСТВО ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ ДЛЯ ДОСТИЖЕНИЯ ВЫСОКОЙ ПРОИЗВОДИТЕЛЬНОСТИ И СПОСОБ РАСПОЛОЖЕНИЯ В НЕМ СИГНАЛЬНЫХ ШИН | 1995 |

|

RU2170955C2 |

Авторы

Даты

2011-11-27—Публикация

2008-07-25—Подача