Изобретение относится к области радиотехники и связи и может быть использовано в качестве выходного каскада для усиления быстроизменяющихся аналоговых сигналов по мощности (буферного усилителя), в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ).

Одним из классических вариантов построения буферных усилителей (БУ) являются схемы так называемых «бриллиантовых» составных транзисторов, которые стали основой современных аналоговых микросхем [1-23].

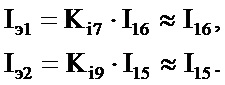

Ближайшим прототипом заявляемого устройства является БУ, представленный в патенте США № 5.512.859, fig 3. (эта архитектура БУ присутствует в большем числе других патентов [2-23]). Он содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой второго 5 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой первого 4 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и первого 1 входного транзисторов связаны со второй 10 шиной источника питания, а коллекторы второго 2 входного и второго 5 выходного транзисторов связаны с первой 8 шиной источника питания.

Существенный недостаток известного буферного усилителя состоит в том, что он имеет малую скорость нарастания выходного напряжения (

Основная задача предлагаемого изобретения состоит в повышении максимальной скорости нарастания выходного напряжения и уменьшении времени установления переходного процесса в БУ при больших импульсных входных сигналах (соизмеренных с напряжением питания).

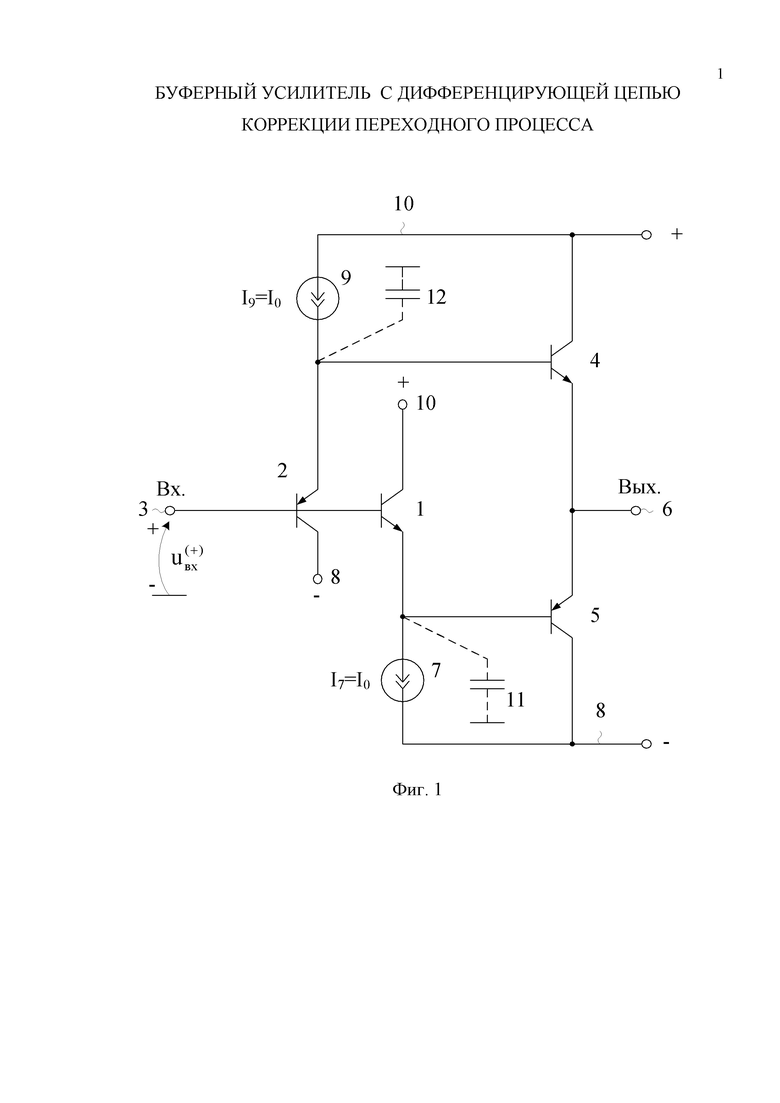

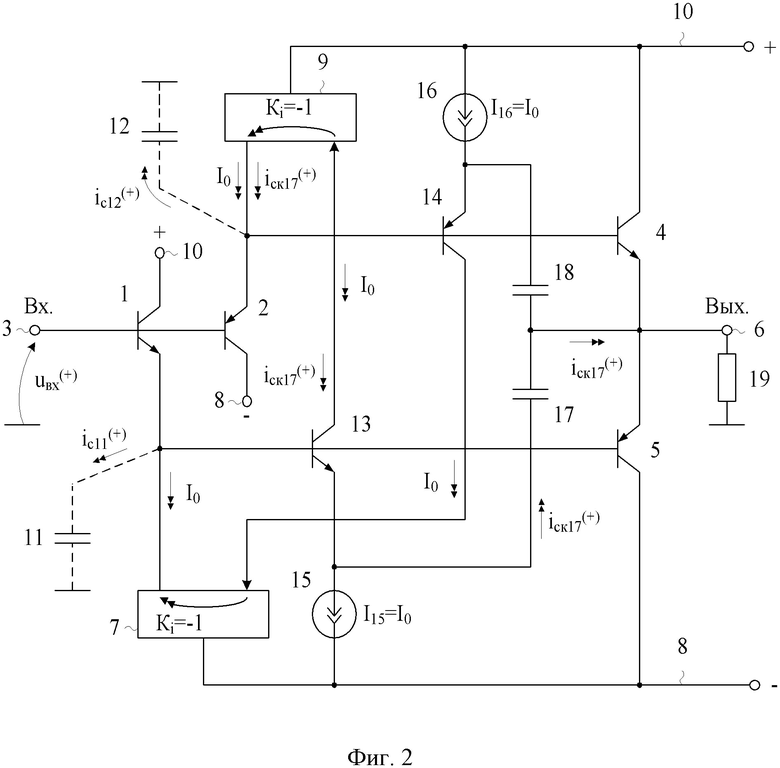

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой второго 5 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой первого 4 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и первого 1 входного транзисторов связаны со второй 10 шиной источника питания, а коллекторы второго 2 входного и второго 5 выходного транзисторов связаны с первой 8 шиной источника питания, предусмотрены новые элементы и связи – в качестве первой 7 и второй 9 цепей управления статическим режимом первого 1 и второго 2 входных транзисторов соответственно применяются инвертирующие усилители тока, причем в схему введены первый 13 и второй 14 дополнительные транзисторы разного типа проводимости, база первого 13 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, коллектор первого 13 дополнительного транзистора соединен со входом второго 9 инвертирующего усилителя тока, эмиттер первого 13 дополнительного транзистора связан с первой 8 шиной источника питания через первый 15 дополнительный токостабилизирующий двухполюсник, база второго 14 дополнительного транзистора связана с эмиттером второго 2 входного транзистора, коллектор второго 14 дополнительного транзистора соединен со входом первого 7 инвертирующего усилителя тока, эмиттер второго 14 дополнительного транзистора связан со второй 10 шиной источника питания через второй 16 дополнительный токостабилизирующий двухполюсник, между эмиттерами первого 13 и второго 14 дополнительных транзисторов включены последовательно соединённые первый 17 и второй 18 корректирующие конденсаторы, причем выход устройства 6 связан с объединёнными выводами первого 16 и второго 18 корректирующих конденсатора.

На чертеже фиг. 1 представлена схема БУ-прототипа, а на чертеже фиг. 2 – схема заявляемого устройства в соответствии с п.1 формулы изобретения.

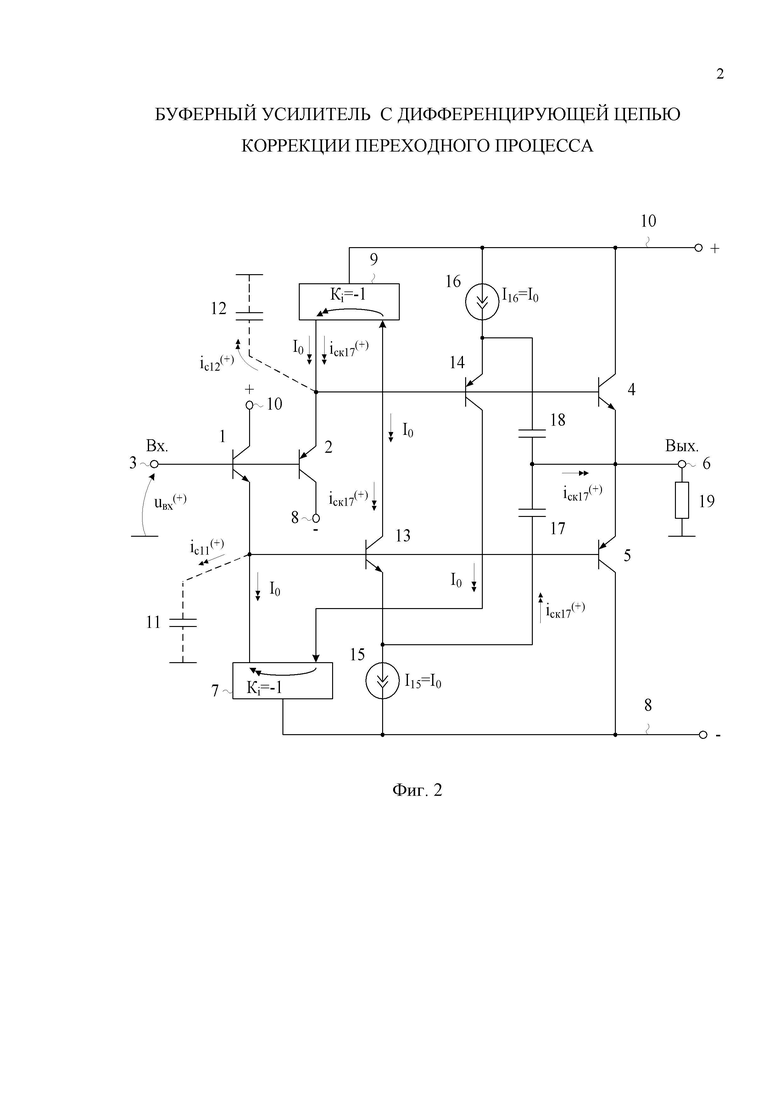

На чертеже фиг. 3 показана схема заявляемого устройства фиг. 2 в соответствии с п.2 формулы изобретения.

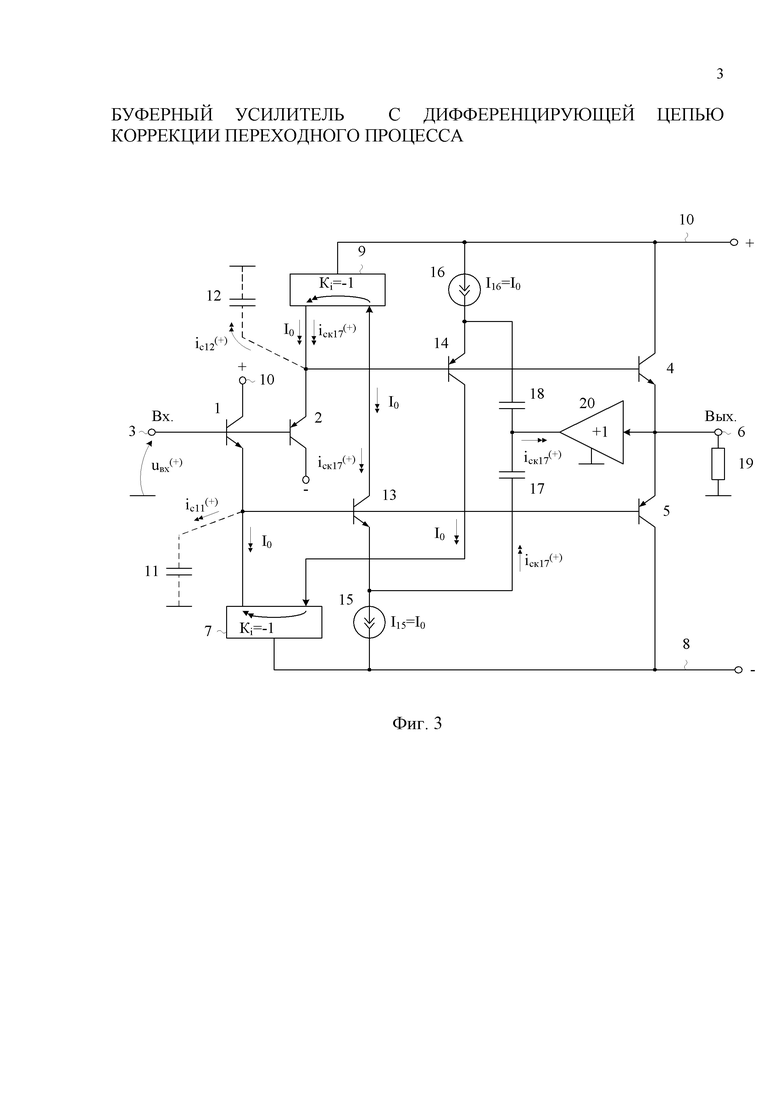

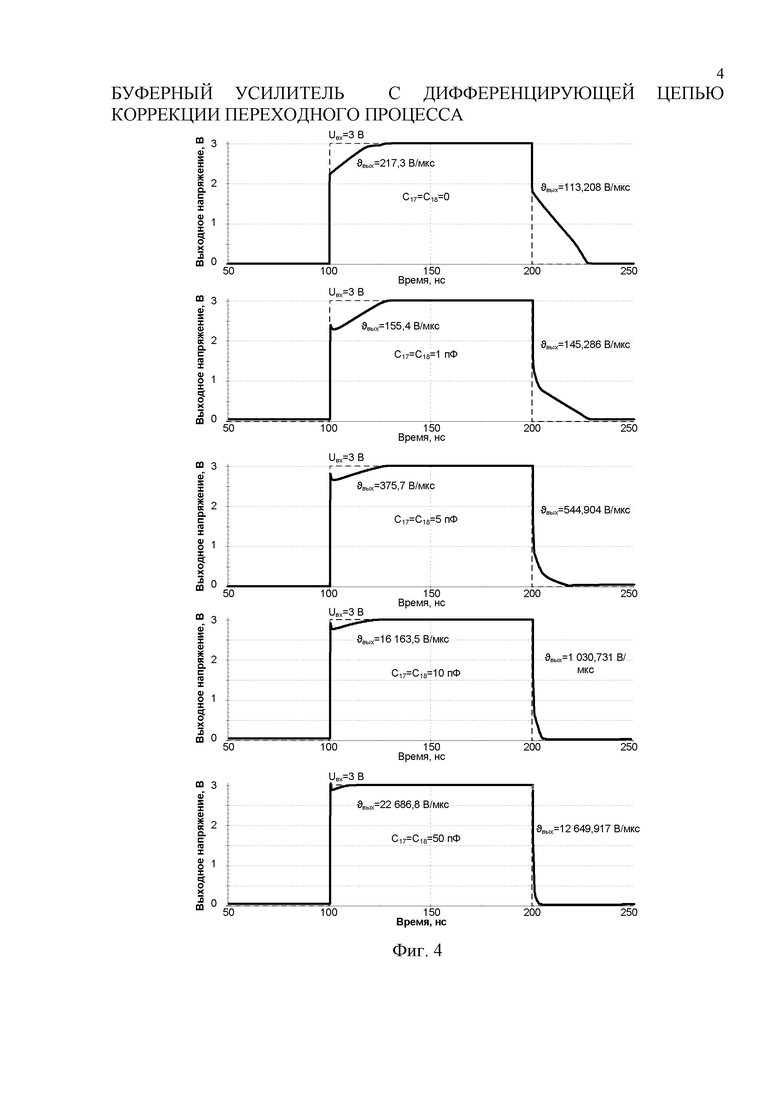

На чертеже фиг. 4 показаны переходные процессы в заявляемом БУ фиг. 2 при разных значениях ёмкости первого 17 и второго 18 корректирующих конденсаторов С17=С18=0;1;5;10;50 пФ.

Буферный усилитель с дифференцирующей цепью коррекции переходного процесса фиг. 2 содержит первый 1 и второй 2 входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства 3, первый 4 и второй 5 выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства 6, первая 7 цепь управления статическим режимом первого 1 входного транзистора, согласованная с первой 8 шиной источника питания, связанная с эмиттером первого 1 входного транзистора и базой второго 5 выходного транзистора, вторая 9 цепь управления статическим режимом второго 2 входного транзистора, согласованная со второй 10 шиной источника питания, связанная с эмиттером второго 2 входного транзистора и базой первого 4 выходного транзистора, первая 11 паразитная емкость, связанная с базой второго 5 выходного транзистора, вторая 12 паразитная емкость, связанная с базой первого 4 выходного транзистора, причем коллекторы первого 4 выходного и первого 1 входного транзисторов связаны со второй 10 шиной источника питания, а коллекторы второго 2 входного и второго 5 выходного транзисторов связаны с первой 8 шиной источника питания. В качестве первой 7 и второй 9 цепей управления статическим режимом первого 1 и второго 2 входных транзисторов соответственно применяются инвертирующие усилители тока, причем в схему введены первый 13 и второй 14 дополнительные транзисторы разного типа проводимости, база первого 13 дополнительного транзистора соединена с эмиттером первого 1 входного транзистора, коллектор первого 13 дополнительного транзистора соединен со входом второго 9 инвертирующего усилителя тока, эмиттер первого 13 дополнительного транзистора связан с первой 8 шиной источника питания через первый 15 дополнительный токостабилизирующий двухполюсник, база второго 14 дополнительного транзистора связана с эмиттером второго 2 входного транзистора, коллектор второго 14 дополнительного транзистора соединен со входом первого 7 инвертирующего усилителя тока, эмиттер второго 14 дополнительного транзистора связан со второй 10 шиной источника питания через второй 16 дополнительный токостабилизирующий двухполюсник, между эмиттерами первого 13 и второго 14 дополнительных транзисторов включены последовательно соединённые первый 17 и второй 18 корректирующие конденсаторы, причем выход устройства 6 связан с объединёнными выводами первого 16 и второго 18 корректирующих конденсатора. Нагрузка БУ 19 подключена к выходу устройства 6.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, выход устройства 6 связан с объединенными выводами первого 17 и второго 18 корректирующих конденсаторов через дополнительный буферный усилитель 20.

Рассмотрим работу заявляемого БУ фиг. 2. Статический режим схемы фиг. 2 устанавливается первым 15 и вторым 16 дополнительными токостабилизирующими двухполюсниками. При коэффициенте передачи по току Ki≈1 первого 7 и второго 9 инвертирующих усилителей тока статические эмиттерные токи первого 1 (

При малых входных импульсных сигналах все элементы схемы БУ работают в линейном режиме, и как следствие, БУ имеет максимально возможное быстродействие. В этом режиме переменная составляющая напряжений на первом 17 и втором 18 корректирующих конденсаторах будет близка к нулю, так как приращение напряжений на эмиттере первого 13 (второго 14) дополнительного транзистора и выходе устройства 6 идентично. Поэтому эти конденсаторы не влияют на работу схемы в режиме малого сигнала.

При большом положительном импульсном входном сигнале (соизмеримом с напряжением питания) второй 2 входной транзистор запирается по цепи базы, и поэтому медленный заряд второй 12 паразитной емкости обеспечивается выходным током второго 9 инвертирующего усилителя. В этом режиме образуется большая разность напряжений между входом 3 и выходом 6 устройства, которая дифференцируется первым 17 корректирующим конденсатором. В результате через первый 17 корректирующий конденсатор формируется большой импульс тока, который передается через первый 13 дополнительный транзистор на вход второго 9 инвертирующего усилителя в эмиттерной цепи второго 2 входного транзистора, а затем – в цепь базы первого 4 выходного транзистора. Как следствие скорость перезаряда второй 12 паразитной емкости существенно возрастает, что способствует быстрому увеличению напряжения на базе первого 4 выходного транзистора и, как следствие, выходного напряжения БУ.

По мере приближения уровня выходного напряжения uвых к уровню входного напряжения БУ uвх, приращение напряжения на первом 17 корректирующем конденсаторе, и следовательно, ток через первый 17 корректирующий конденсатор уменьшаются. В конечном итоге схема БУ входит в линейный режим, когда ток заряда второй 12 паразитной емкости уменьшается до уровня тока I15 первого 15 дополнительного токостабилизирующего двухполюсника.

Компьютерное моделирование показывает, что в сравнении с прототипом динамические параметры предлагаемого БУ существенно улучшаются. Так, для переднего фронта скорость нарастания выходного напряжения увеличивается более чем в 110 раз, а для заднего фронта – более чем в 120 раз.

Замечательной особенностью схемы фиг. 3 является слабое влияние первого 13 и второго 14 дополнительных транзисторов на входной ток БУ, его входное сопротивление Rвх и входную емкость.

В соответствии с п. 2 формулы изобретения в схему фиг. 3 введен дополнительный буферный усилитель 20. Это позволяет уменьшить влияние сопротивления нагрузки 19 на параметры переходного процесса. В качестве дополнительного буферного усилителя 20 могут использоваться классические эмиттерные повторители.

Таким образом, заявляемое устройство обладает более высоким быстродействием в режиме большого сигнала.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США № № 5.512.859 fig.3 (прототип)

2. Патент США № 6.268.769 fig.3

3. Патент США № 6.420.933

4. Патент США № 5.223.122

5. Патентная заявка США № 2004/0196101

6. Патентная заявка США № 2005/0264358 fig.1

7. Патентная заявка США № 2002/0175759

8. Патент США № 5.049.653 fig.8

9. Патент США № 4.837.523

10. Патент США № 5.179.355

11. Патент Японии JP 10.163.763

12. Патент Японии JP 10.270.954

13. Патент США № 5.170.134 fig.6

14. Патент США № 4.540.950

15. Патент США № 4.424.493

16. Патент Японии JP 6310950

17. Патент США № 5.378.938

18. Патент США № 4.827.223

19. Патент США № 6.160.451

20. Патент США № 4.639.685

21. А.св. СССР 1506512

22. Патент США № 5.399.991

23. Патент США № 6.542.032

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2018 |

|

RU2674885C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2668985C1 |

| КАСКОДНЫЙ СВЧ-УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2460206C1 |

| Быстродействующий операционный усилитель | 2023 |

|

RU2810548C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩЕЙ ЦЕПЬЮ КОРРЕКЦИИ | 2018 |

|

RU2669075C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ | 2011 |

|

RU2465720C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2011 |

|

RU2439783C1 |

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2012 |

|

RU2479113C1 |

Изобретение относится к буферным усилителям с дифференцирующей цепью коррекции переходного процесса. Технический результат заключается в повышении максимальной скорости нарастания выходного напряжения и уменьшении времени установления переходного процесса в БУ. В усилитель введены первый и второй дополнительные транзисторы разного типа проводимости, база первого дополнительного транзистора соединена с эмиттером первого входного транзистора, коллектор первого дополнительного транзистора соединен со входом второго инвертирующего усилителя тока, эмиттер первого дополнительного транзистора связан с первой шиной источника питания через первый дополнительный токостабилизирующий двухполюсник, база второго дополнительного транзистора связана с эмиттером второго входного транзистора, коллектор второго дополнительного транзистора соединен со входом первого инвертирующего усилителя тока, эмиттер второго дополнительного транзистора связан со второй шиной источника питания через второй дополнительный токостабилизирующий двухполюсник, между эмиттерами первого и второго дополнительных транзисторов включены последовательно соединённые первый и второй корректирующие конденсаторы, причем выход устройства связан с объединёнными выводами первого и второго корректирующих конденсаторов. 1 з.п. ф-лы, 4 ил.

1. Буферный усилитель с дифференцирующей цепью коррекции переходного процесса, содержащий первый (1) и второй (2) входные транзисторы разного типа проводимости, объединенные базы которых подключены ко входу устройства (3), первый (4) и второй (5) выходные транзисторы разного типа проводимости, объединенные эмиттеры которых соединены с выходом устройства (6), первая (7) цепь управления статическим режимом первого (1) входного транзистора, согласованная с первой (8) шиной источника питания, связанная с эмиттером первого (1) входного транзистора и базой второго (5) выходного транзистора, вторая (9) цепь управления статическим режимом второго (2) входного транзистора, согласованная со второй (10) шиной источника питания, связанная с эмиттером второго (2) входного транзистора и базой первого (4) выходного транзистора, первая (11) паразитная емкость, связанная с базой второго (5) выходного транзистора, вторая (12) паразитная емкость, связанная с базой первого (4) выходного транзистора, причем коллекторы первого (4) выходного и первого (1) входного транзисторов связаны со второй (10) шиной источника питания, а коллекторы второго (2) входного и второго (5) выходного транзисторов связаны с первой (8) шиной источника питания, отличающийся тем, что в качестве первой (7) и второй (9) цепей управления статическим режимом первого (1) и второго (2) входных транзисторов соответственно применяются инвертирующие усилители тока, причем в схему введены первый (13) и второй (14) дополнительные транзисторы разного типа проводимости, база первого (13) дополнительного транзистора соединена с эмиттером первого (1) входного транзистора, коллектор первого (13) дополнительного транзистора соединен со входом второго (9) инвертирующего усилителя тока, эмиттер первого (13) дополнительного транзистора связан с первой (8) шиной источника питания через первый (15) дополнительный токостабилизирующий двухполюсник, база второго (14) дополнительного транзистора связана с эмиттером второго (2) входного транзистора, коллектор второго (14) дополнительного транзистора соединен со входом первого (7) инвертирующего усилителя тока, эмиттер второго (14) дополнительного транзистора связан со второй (10) шиной источника питания через второй (16) дополнительный токостабилизирующий двухполюсник, между эмиттерами первого (13) и второго (14) дополнительных транзисторов включены последовательно соединённые первый (17) и второй (18) корректирующие конденсаторы, причем выход устройства (6) связан с объединёнными выводами первого (16) и второго (18) корректирующих конденсаторов.

2. Буферный усилитель с дифференцирующей цепью коррекции переходного процесса по п.1, отличающийся тем, что выход устройства (6) связан с объединенными выводами первого (17) и второго (18) корректирующих конденсаторов через дополнительный буферный усилитель (20).

| ИЗБИРАТЕЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ НЕИНВЕРТИРУЮЩЕГО УСИЛИТЕЛЯ ТОКА | 2012 |

|

RU2488955C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2368066C1 |

| Операционный усилитель | 1986 |

|

SU1356196A1 |

| US 5512859, 30.04.1996. | |||

Авторы

Даты

2018-11-21—Публикация

2018-03-05—Подача