t

Изобретение относится к области импульсной техники и может быть использовано в устоойствах преобразованкя информацииS а также контрольно-измерительных устройствах.

Известны компараторы, содержйщие каскад с прямым и инверсным входом и выходом 8 два коммутационкьг транзистора в цепи обратной связи в каждом .плече дифференциального каскада

Недостатком известных схем является низкая точность ввиду невысокого коэффициента усиления дифференциального каскада.

Наиболее близким по технической сущности к данному является компаратор на МДП- транэисторах, содержащий дифференциальный каскад, два конденсатора, два транзистора, каждый из которых подключен соответственно между прямым входом и инверсным выходом и между инверсным входом и прямым выходом дифференциального каскада, прямой и инверсный выходы которого подключены соответственно к первым выводам первого и второго конденсатора, а затворы транзисторо подключены к шике управляю Д1-:х сигналов 2),

Недостатком такого устройства яв.;/яется низкая точность ввиду невысокого коэффициента усиления.

Цель изобретения - повьпление точ.нести путем увеличения коэффициента усиления,

р/,;я достижения поставленной цели 3 компаратор на МДП-транзисторах сойвржащий дифференциальный каскадj два :говдангатора,два транзистора каж, из которых подключен соответствеьно между входом и инверным выходом и- мелэду 7днверсньпу1 входом и прямым выходом дифференцИсШЬ кого каскада.,, прямой и инверсный чкоды .го под слючены соответствекно к нервьп-. т-зыводам первогс- и второго конденсаторовэ а затворы транзисторов подключены к жине уп .равляюпщх си.гяаловр введены третий „ четвертыйS пятый и шестой транзисторы к два .дополнительных конденсатора,- при этом каждый дополнительньш конденсатор подключен соответственно ме7кду прямыми входог-; и выходом и инверсным входом и выходом дифференциальногс каскада„ а третий и чег.8ерто1й,; пятгзЧ li щестой транзис694:32

тиры включены последовательно и подключень к шинам входных сигналов, а затворы третьего и шестого четБертого и пятого транзисторов под5 ключены соответствекно к шинам парафазного управляющего сигнала, а точки соединения третьего и четвертого, пятого и шестого транзисторов подключены соответственно к вторым выводам второго и первого конденсаторов ,

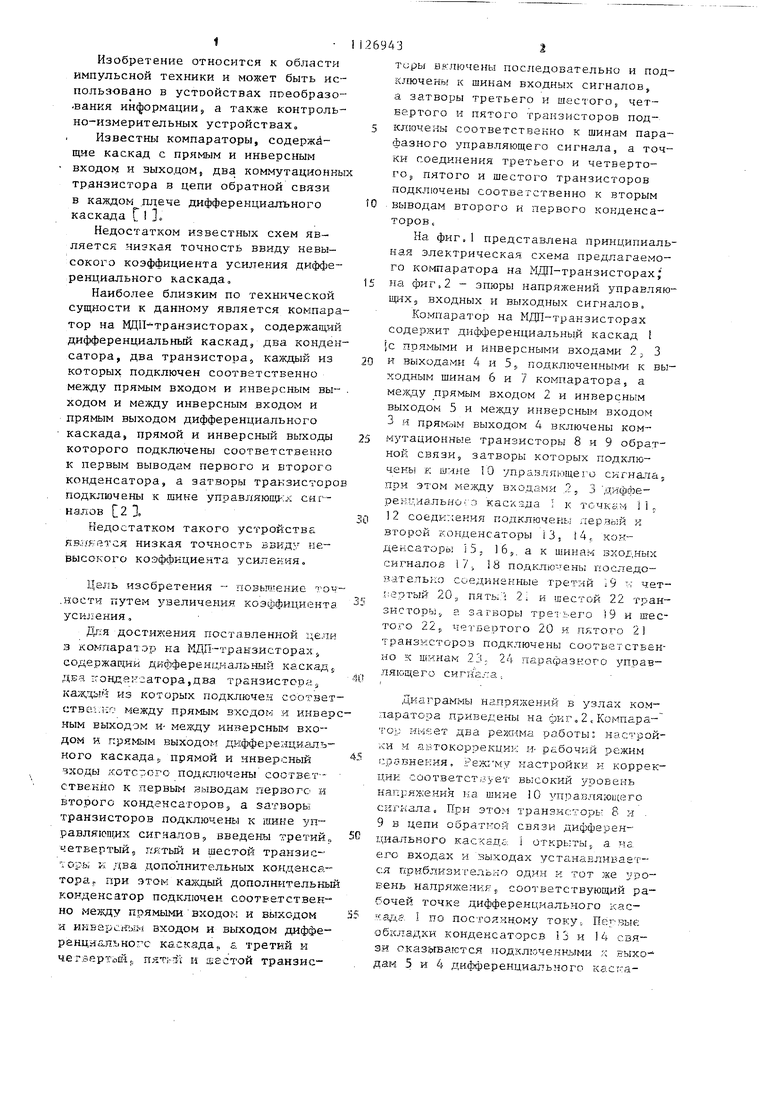

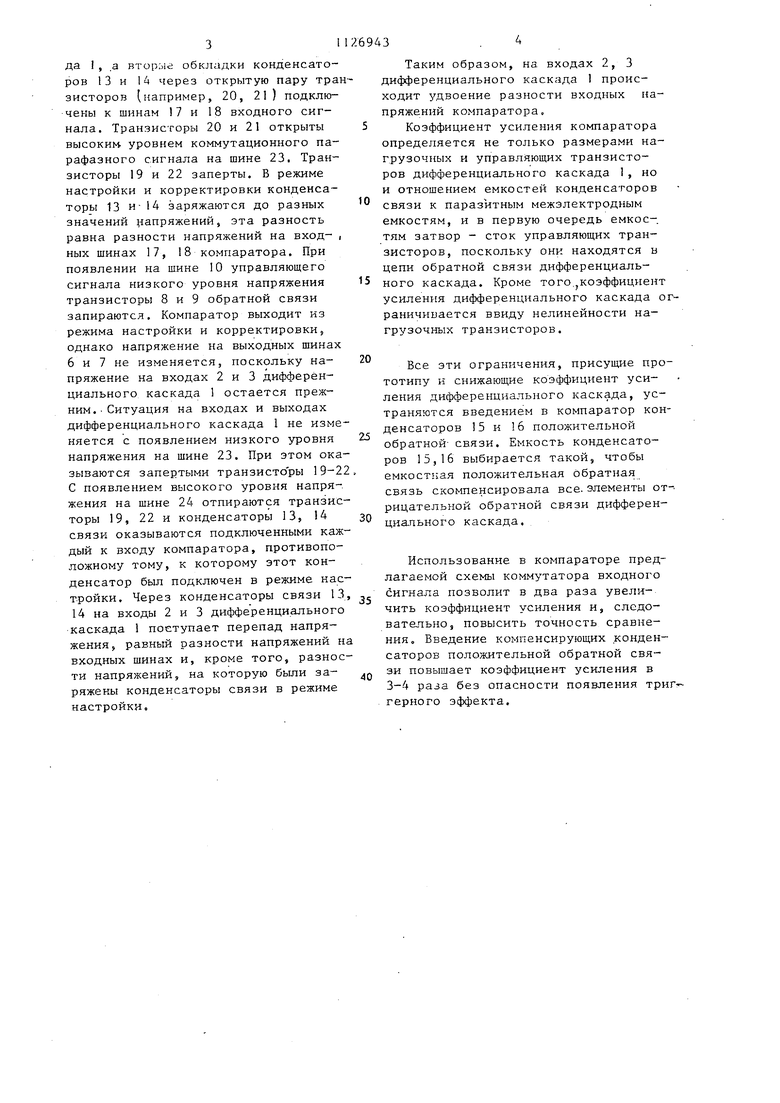

На фиг,1 представлена принципиальная электрическа.я схема предлагаемого компаратора на МДП-транзисгорах на фиг,2 - эпюры напряжений управляющиХд .входных и выходных сигналов.

Компаратор на МДП-транзисторах содержит дифференциальный каскад 1 |с прямыми и инверсными входами 2 3 и выходами 4 и 5,, пoдключeнны да к выходным шинам 6 и 7 компаратора, а меж,цу прямым входом 2 и инверсньгм выходом 5 и между инверсным входо.м 3 я прямым выходом 4 включены коммутационные транзисторы 8 и 9 обрат ной связи, затворы которых подключень к шине 10 управляющего сигнала, при этом ме5кду входами .2, 3 дифференциа.льнОэ каскада I к точкам 11„ 12 соеди:;екия подклгачень лер.вый к второй конденсаторы 13, 14, конденсаторы 5, 16,. а к шинам входных сигналов 17,. 18 подклю-гень; последовате.лько соединенные третий 19 к чет;;-зртый 203 21 к шестой 22 транSHCTOpbJs а затворы трет.ьего i9 и шестого 22р четБертого 20 и пятого 21 транзнсторов подключены соответственно к шинам 23.: 24 парафазного управляющего сигйала;

Диаграммы на.пряжений в узлах компаратора .пр.иведены на фкг, 2, Компарато.; инвет два режима работы: н. и автокоррекцик и- рабочий режим :р,ЗБкекия, Режму настройки и коррекции соот.ветст;з ет высокий уровень напряжения ка шине 0 управляюигего сигнала. При этом транзис;торь; 8 и . 9 в цепи обратной связи дифференциального каскадй: i иткрь;ты5 а на. его входах и выходах устанавливается приблизительно один и тот же уровень напряжения, соответствующий рабочей точке дифференциального к.асs&j:i.s. I по постояян.ому тов;уо Первые обкладки кондексаторсй 13 и 14 связи оказываются подключенными .;: выхо- дам .5 и 4 дифференциального кастада 1, .а вторые обкладки конденсаторов 13 и 14 через открытую пару транзисторов (например, 20, 21) подключены к шинам 7 и 18 входного сигнала. Транзисторы 20 и 21 открыты высоким уровнем коммутационного парафазного сигнала на шине 23. Транзисторы 19 и 22 заперты. В режиме настройки и корректировки конденсаторы 13 и-14 заряжаются до разных значений aпpяжeний, эта разность равна разности напряжений на вход- , ных шинах 17, 18 компаратора. При появлении на шине 10 управляющего сигнала низкого уровня напряжения транзисторы 8 и 9 обратной связи запираются. Компаратор выходит кз режима настройки и корректировки, однако напряжение на выходных шинах 6 и 7 не изменяется, поскольку напряжение на входах 2 и 3 дифференциального каскада 1 остается прежним. Ситуация на входах и выходах дифференциального каскада 1 не изменяется с появлением низкого уровня напряжения на шине 23. При этом оказываются запертыми транзисторы 19-22 С появлением высокого уровня напряжения на шине 24 отпираются транзисторы 19, 22 и конденсаторы 13, 14 связи оказываются подключенными каждый к входу компаратора, противоположному тому, к которому этот конденсатор был подключен в режиме настройки. Через конденсаторы связи 13 14 на входы 2 и 3 дифференци.ального каскада 1 поступает перепад напряжения, равный разности напряжений на входных шинах и, кроме того, разности напряжений, на которую были заряжены конденсаторы связи в режиме настройки.

Таким образом, на входах 2, 3 дифференциального каскада 1 происходит удвоение разности входных напряжений компаратора,

Коэффициент усиления компаратора определяется не только размерами нагрузочных и управляющих транзисторов дифференциального каскада 1, но и отношением емкостей конденсаторов связи к паразитным межэлектродным емкостям, и в первую очередь емкое-, тям затвор - сток управляющих транзисторов, поскольку они находятся в цепи обратной связи дифференциального каскада. Кроме того,коэффициент усиления дифференциального каскада ограничивается ввиду нелинейности нагрузочных транзисторов.

Все эти ограничения, присущие прототипу и снижающие коэффициент усиления дифференциального каскада, устраняются введением в компаратор конденсаторов 15 и 6 положительной обратной- связи. Емкость конденсаторов 15,16 выбирается такой, чтобы емкостная положительная обратная связь скомпенсировала все. элементы отрицательной обратной связи дифференциапьного каскада.

Использование в компараторе предлагаемой схемы коммутатора входного сигнала позволит в два раза увеличить коэффициент усиления и, следовательно, повысить точность сравнения. Введение компенсирующих конденсаторов положительной обратной связи повышает коэффициент усиления в 3-4 раза без опасности появления триг герного эффекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| Компаратор напряжения | 1985 |

|

SU1246049A1 |

| Усилительное устройство | 1988 |

|

SU1571749A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Компаратор | 1989 |

|

SU1690184A1 |

| КАСКАДНОЕ ПАРАФАЗНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2008 |

|

RU2349028C1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| Буферное устройство | 1979 |

|

SU822366A1 |

| КМДП-компаратор с регенерацией | 1988 |

|

SU1614106A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Источник питания | 1980 |

|

SU900376A1 |

КОМПАРАТОР НА МДП-ТРАНЗИСТОРАХ, содержащий дифференциальный .каскад, два конденсатора, два транзистора, каждый из которых подключен соответственно меядцу прямым входом и инверсным выходом и между инверсным входом и прямым выходом дифференциального каскада, прямой и ин.версный входы которого подключены соответственно к первым выводам первого и второго конденсаторов, а затворы транзисторов подключены к шине управляющих сигналов, о т л и ч а ющ и и с я тем, что, с целью повышения точности за счет увеличения коэффициента усиления, в него введены третий, четвертый, пятый, шестой транзисторы и два дополнительных конденсатора, при зтом каждый дополнительный конденсатор подключен соответственно между прямыми входом и. выходом и инверсным входом и выходом дифференциального каскада, -а третий и четвертый, пятый и шестой транзисторы включены последовательно и подключены к шинам входных сигналов, а затворы третьего ишестого, четвертого и пятого транзисторов подключены соответственно к шинам парафазного управляющего сигнала а точки соединения .третьего и четвертого, пятого и шестого транзисторов подключены соответственно к вторым выводам второго и -первого конденсаторов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3882326, кл | |||

| Приспособление для выпечки формового хлеба в механических печах с выдвижным подом без смазки форм жировым веществом | 1921 |

|

SU307A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1984-11-30—Публикация

1983-03-17—Подача