Изобретение относится к области электротехники, а именно к компараторам с постоянной нагрузкой при высокой частоте сигнала данных, которые являются частью интегральной схемы и могут применяться в мобильных телефонах, в аналого-цифровых преобразователях, а также могут быть использованы как часть цепи фазовой автоподстройки частоты.

Из уровня техники известны различные конструкции компараторов, например, описанные в патентах США №6400215 [1], 6714079 [2] и в российском патенте №2393630 [3], однако их основным недостатком является малая эффективность при высоких частотах.

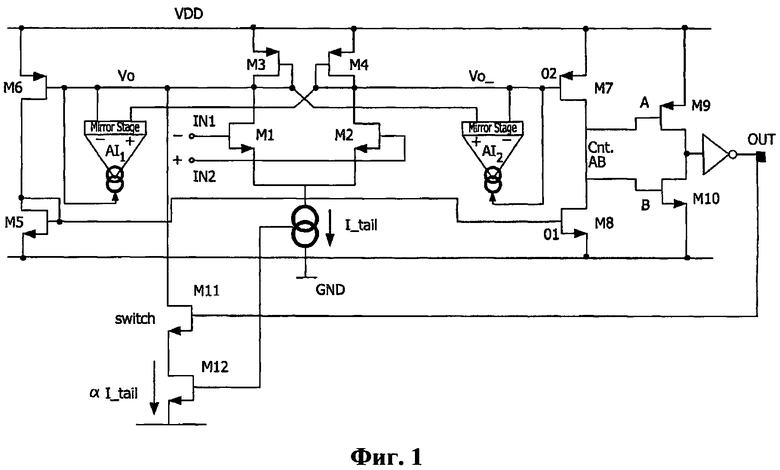

Наиболее близким к заявленному изобретению является компаратор, описанный в патенте США №7498851 [4] и представленный на (Фиг.1). Компаратор-прототип функционирует с постоянной нагрузкой при высокой частоте сигналов данных и включает в себя: дифференциальный усилитель (M1, M2), имеющий дифференциальные входы (IN1, IN2), являющиеся также входами компаратора; первый и второй выходы усилителя (Vo, Vo-), являющиеся также результатами первого этапа компарирования. Причем первый дифференциальный токовый усилитель (А11) соединен своими входами с выходами усилителя (Vo, Vo-), а своим выходом - с первым выходом усилителя (Vo). Наконец, второй дифференциальный токовый усилитель (А12) соединен своими входами с выходами усилителя (Vo, Vo-), а своим выходом - со вторым выходом усилителя (Vo-). При этом следует пояснить, что на Фиг.1, воспроизведенной с оригинального документа, использованы следующие обозначения: I_tail - следовый ток, switch - ключ, Mirror Stage - каскад токовых зеркал.

Недостаток компаратора-прототипа состоит в том, что он вносит существенные дополнительные флуктуации (джиттер).

Задачей заявленного изобретения является создание компаратора, обеспечивающего более низкий джиттер, повышенное быстродействие и улучшенную защищенность от сбоев, который по сравнению с тактируемыми компараторами не нуждается во внешнем синхросигнале.

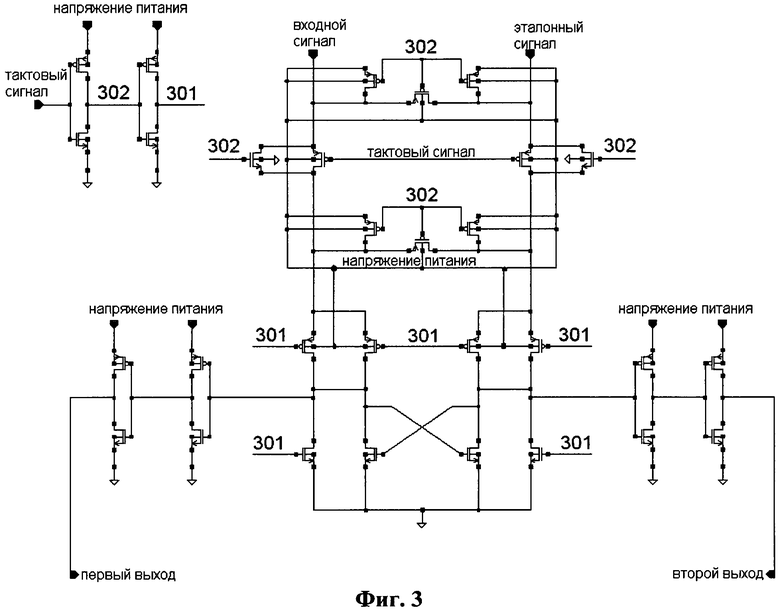

Технический результат достигается за счет создания новой конструкции компаратора напряжений, содержащего линию задержки и высокопроизводительный высокочувствительный тактовый усилитель считывания с дифференциальным выходом и кодировкой выходного сигнала "с возвратом к нулю" (RZ), который соединен в петлю с линией задержки через логический элемент «или», при этом оба выхода усилителя считывания соединены с входами логического элемента «или», выход которого соединен с входом линии задержки, выход которой соединен с входом тактового сигнала усилителя считывания, причем общая задержка линии усилителя считывания и элемента «или» близка по величине к периоду входного сигнала.

Иными словами, заявляемый эффект получают за счет формирования регулируемой петли, состоящей из усилителя считывания с дифференциальным выходом и кодировкой выходного сигнала "с возвратом к нулю" (RZ), линии задержки и логического элемента «или», а также за счет использования усилителя считывания с высокой производительностью и высокой чувствительностью.

Для функционирования компаратора напряжений важно, чтобы он дополнительно содержал выходной D-триггер, выходы которого соединены с выходом усилителя считывания и выходом линии задержки соответственно.

Для лучшего понимания заявленного изобретения далее приводится его подробное описание с соответствующими графическими материалами.

Фиг.1 - Схема компаратора, известного из уровня техники.

Фиг.2 - Схема компаратора напряжений, выполненного согласно изобретению.

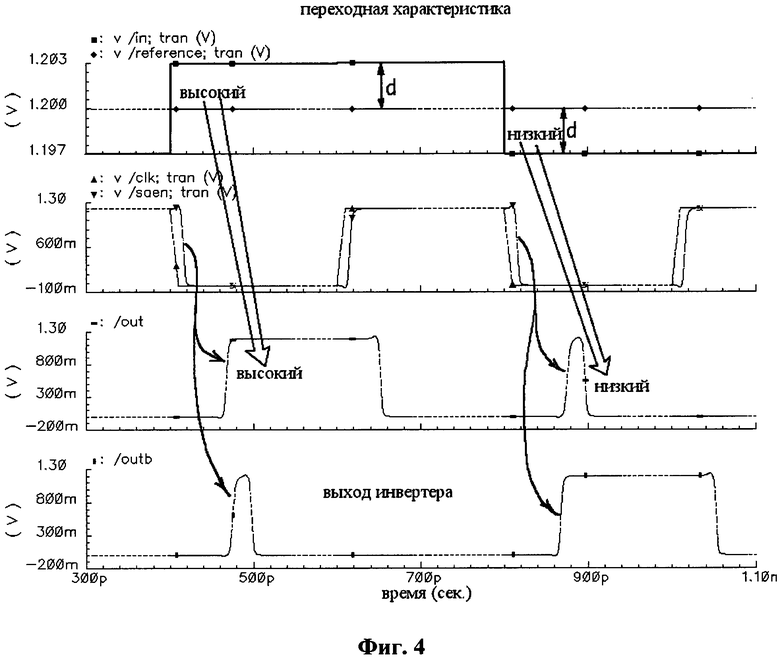

Фиг.3 - Схема зарядового усилителя считывания, выполненного согласно изобретению.

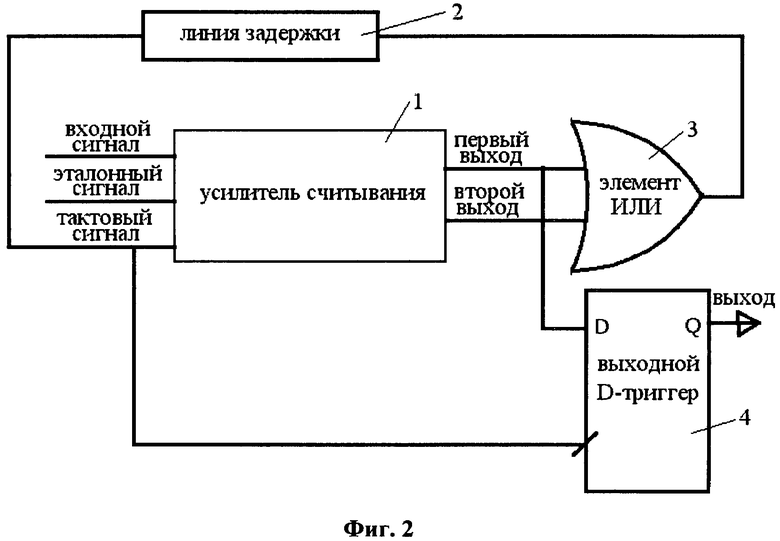

Фиг.4 - Временная диаграмма зарядового усилителя считывания, выполненного согласно изобретению.

Заявленный компаратор напряжений, представленный на Фиг.2, состоит из зарядового усилителя 1 считывания (sense amplifier) и линии 2 задержки (delay line), соединенных через элемент 3 «или», и, в данном варианте реализации, выходного D-триггера 4 (D flip-flop).

Усилитель 1 считывания удовлетворяет следующим условиям: во-первых, он обладает высокой производительностью и высокой чувствительностью, а во-вторых, выходной сигнал усилителя считывания находится в кодировке "с возвратом в нулевое значение". В данном варианте выполнения компаратора напряжений используется зарядовый усилитель считывания, представленный на Фиг.3, временная диаграмма которого представлена на Фиг.4. На Фиг.3 показаны следующие обозначения: 301 - строб усилителя считывания (saen), 302 - строб предзаряда (pch), а также входной сигнал (in), эталонный сигнал (reference), тактовый сигнал (clk), первый выход (out) и второй выход (outb), напряжение питания (VCC).

На входы усилителя 1 считывания подается эталонный сигнал (reference) и входной сигнал (in).

Оба выхода (первый выход и второй выход) усилителя 1 считывания соединены с входами логического элемента 3 «или». Результат операции «или» подают на вход линии 2 задержки. Суммарная величина задержка линии, усилителя считывания и элемента «или» должна быть близка к периоду входного сигнала. Выход линии задержки подают на вход тактового сигнала (clk) усилителя 1 считывания.

Увеличение разности напряжений входных сигналов усилителя 1 считывания приводит к уменьшению временной задержки его выходного сигнала. Уменьшение разности напряжений входных сигналов усилителя 1 считывания приводит к увеличению задержки выходного сигнала усилителя 1 считывания. Таким образом, задержка цепи будет подстраиваться к периоду входного сигнала.

На Фиг.4 показана временная диаграмма работы зарядового усилителя считывания.

Лучшая реализация заявленного изобретения основана на CMOS схемотехнике.

Вместо зарядового усилителя 1 считывания, приведенного в описанном выше варианте выполнения заявленного изобретения, может быть использован любой усилитель считывания, удовлетворяющий условиям высокого быстродействия и высокой чувствительности, с кодировкой выходного сигнала "с возвратом к нулю" (RZ). Выходная задержка усилителя считывания должна зависеть от разности напряжений входных сигналов.

Наличие в составе компаратора напряжений такого элемента, как выходной D-триггер (D flip-flop), является опционным.

Следует отметить, что указанный выше вариант выполнения изобретения был изложен с целью иллюстрации настоящего изобретения, и специалистам должно быть ясно, что возможны разные модификации, добавления и замены, не выходящие из объема и смысла настоящего изобретения, раскрытого в прилагаемой формуле изобретения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ГЕНЕРАТОР ХАОТИЧЕСКОГО СИГНАЛА С ПОСТОЯННОЙ АМПЛИТУДОЙ (ВАРИАНТЫ) | 2011 |

|

RU2469460C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И СИНХРОНИЗАЦИИ КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2344543C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| СПОСОБ И УСТРОЙСТВО ВЫДЕЛЕНИЯ ТАКТОВОГО СИГНАЛА | 1995 |

|

RU2127955C1 |

| СЛЕДЯЩАЯ ЛИНИЯ ЗАДЕРЖКИ | 1993 |

|

RU2085026C1 |

| ВЫСОКОСКОРОСТНАЯ ПЕРЕДАЧА СИГНАЛОВ ДЛЯ СОПРЯГАЮЩИХ СХЕМ КМОП СВСИ | 1999 |

|

RU2239956C2 |

Изобретение относится к области электротехники, а именно к компараторам с постоянной нагрузкой при высокой частоте сигнала данных, которые являются частью интегральной схемы и могут применяться в мобильных телефонах, в аналого-цифровых преобразователях, а также могут быть использованы как часть цепи фазовой автоподстройки частоты. Техническим результатом является обеспечение более низкого джиттера, повышение быстродействия и улучшение защиты от сбоев за счет создания новой конструкции компаратора напряжений. Устройство содержит линию задержки и высокопроизводительный высокочувствительный тактовый усилитель считывания с дифференциальным выходом и кодировкой выходного сигнала "с возвратом к нулю" (RZ), который соединен в петлю с линией задержки через логический элемент «или», при этом оба выхода усилителя считывания соединены с входами логического элемента «или», выход которого соединен с входом линии задержки, выход которой соединен с входом тактового сигнала усилителя считывания, причем период суммарной задержки линии усилителя считывания и элемента «или» близок к периоду входного сигнала. 1 з.п. ф-лы, 4 ил.

1. Компаратор напряжений, содержащий линию задержки и высокопроизводительный высокочувствительный тактовый усилитель считывания с дифференциальным выходом и кодировкой выходного сигнала "с возвратом к нулю" (RZ), который соединен в петлю с линией задержки через логический элемент ИЛИ, при этом оба выхода усилителя считывания соединены с входами логического элемента ИЛИ, выход которого соединен с входом линии задержки, выход которой соединен с входом тактового сигнала усилителя считывания, причем период суммарной задержки линии усилителя считывания и элемента ИЛИ близок к периоду входного сигнала.

2. Компаратор напряжений по п.1, отличающийся тем, что дополнительно содержит выходной D-триггер, выходы которого соединены с выходом усилителя считывания и выходом линии задержки соответственно.

| RU 2008134248 A, 27.02.2010 | |||

| Устройство фазовой автоподстройки частоты | 1991 |

|

SU1826135A1 |

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

2012-05-27—Публикация

2010-07-02—Подача