Область техники, к которой относится изобретение

Настоящее изобретение относится к полупроводниковому устройству, которое включает в себя транзисторы одного типа электропроводности.

Уровень техники

Жидкокристаллическое дисплейное устройство включает в себя возбуждающую схему линии сигналов сканирования и возбуждающую схему линии сигналов данных, каждая из которых включает в себя модуль сопротивления сдвигу для формирования сигнала для последовательного возбуждения пикселов в компоновке матрицы. Дополнительно жидкокристаллическое дисплейное устройство также включает в себя: модуль сдвига уровня для преобразования уровня напряжения питания и буфер, который имеет низкий выходной импеданс и выводит сигнал усиления, в широком смысле, к примеру, схему усиления для вывода сигнала, который имеет 100-процентное усиление относительно входного сигнала. В случае если CMOS-транзистор используется для того, чтобы создавать полупроводниковое устройство, такое как модуль сопротивления сдвигу или буфер, процессы для формирования канала p-типа и канала n-типа соответственно должны требоваться, тем самым усложняя процесс изготовления полупроводникового устройства. Следовательно, в целях упрощения процесса изготовления полупроводникового устройства предпочтительно использовать транзистор одного типа электропроводности, такой как транзистор с униполярным типом электропроводности канала (например, транзистор, имеющий только канал p-типа). Например, патентная литература 1 раскрывает полупроводниковое устройство, составленное из таких униполярных транзисторов.

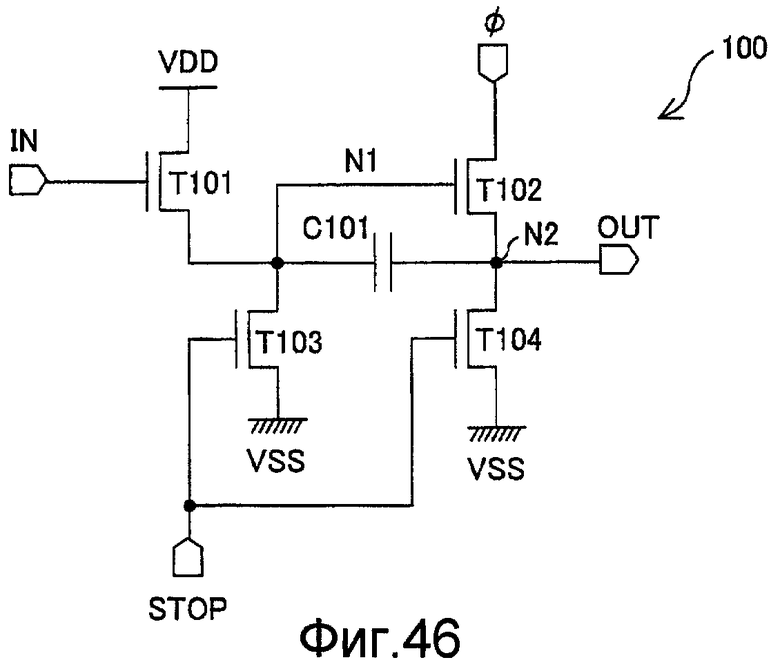

Фиг.46 - это принципиальная схема, иллюстрирующая компоновку полупроводникового устройства, раскрытого в патентной литературе 1. Это полупроводниковое устройство составлено из MOS-транзисторов n-типа.

В частности, полупроводниковое устройство 100 включает в себя четыре MOS-транзистора T101-T104 n-типа и конденсатор C101. Транзистор T101 расположен так, что его контактный вывод стока подключается к источнику VDD питания, а его контактный вывод затвора подключается к входному контактному выводу IN. Транзистор T103 расположен так, что его контактный вывод истока подключается к источнику VSS питания, а его контактный вывод затвора принимает сигнал STOP (останов) (управляющий сигнал). Транзистор T102 расположен так, что его контактный вывод стока подключается к контактному выводу синхросигнала φ, а его контактный вывод затвора подключается к (i) контактному выводу истока транзистора T101 и (ii) контактному выводу стока транзистора T103. Транзистор T104 расположен так, что (i) его контактный вывод стока подключается к контактному выводу истока транзистора T102, (ii) его контактный вывод истока подключается к источнику VSS питания, а (iii) его контактный вывод затвора подключается к контактному выводу затвора транзистора T103. Точка соединения между транзисторами T101, T102 и T103 - это узел N1, а точка соединения между транзисторами T102 и T104 - это узел N2. Конденсатор C101 предоставляется между узлами N1 и N2. Узел N2 подключается к выходному контактному выводу OUT.

Далее последующее описание поясняет работу полупроводникового устройства 100. Фиг.47 - это временная диаграмма, показывающая формы различных сигналов полупроводникового устройства 100.

Когда входной сигнал IN переключается к высокому уровню, транзистор T101 включается и электрический потенциал в узле N1 увеличивается до "VDD-Vth (где Vth - это пороговое напряжение транзистора T101)" (операция предварительной зарядки). Поскольку электрический потенциал в узле N1 увеличивается, транзистор T102 включается. Здесь, в случае если синхросигнал φ находится на низком уровне, сигнал, имеющий низкий уровень, выводится из выходного контактного вывода OUT. После того как электрический заряд предварительно заряжается, электрический потенциал в узле N1 сохраняется до тех пор, пока сигнал STOP не переходит в активное состояние (высокий уровень) (высокоимпедансное состояние). Если синхросигнал φ переключается к высокому уровню в этом высокоимпедансном состоянии, электрический потенциал в узле N1 повышается на электрический потенциал α до "VDD-Vth+α" вследствие конденсатора C101 (операция компенсационной обратной связи). В течение периода времени, в котором этот электрический потенциал превышает "VDD+Vth", сигнал, имеющий уровень электрического потенциала VDD, выводится из выходного контактного вывода OUT.

Затем, когда сигнал STOP переключается к высокому уровню, электрический потенциал в узле N1 разряжается до VSS посредством транзистора T103, так что транзистор T102 отключается. Транзистор T104 включается, так что сигнал, имеющий уровень электрического потенциала VSS, выводится из выходного контактного вывода OUT.

Таким образом, при этой компоновке традиционного полупроводникового устройства можно выводить сигнал, имеющий высокий электрический потенциал, с помощью простой компоновки схем посредством использования преимущества операции компенсационной обратной связи. Следовательно, можно использовать такое полупроводниковое устройство надлежащим образом в узлах жидкокристаллического дисплейного устройства.

Список библиографических ссылок

Патентная литература 1

Патент Японии номер 3092506 B (дата регистрации: 28 июля 2000 года)

Сущность изобретения

Тем не менее, традиционное полупроводниковое устройство, состоящее из транзисторов одного типа электропроводности, к примеру, как описанное выше, имеет такую проблему, что электрический потенциал выходного сигнала постепенно понижается вследствие тока утечки в отключенном состоянии (незначительного тока, просачивающегося из транзистора в то время, когда транзистор находится в выключенном состоянии) и т.п. Дополнительно, такое уменьшение электрического потенциала обуславливает выходной сигнал иметь высокий импеданс, так что выходной сигнал подвержен шуму. Это приводит к ложному срабатыванию в последующей схеме, которая принимает выходной сигнал. В частности, например, в случае если полупроводниковое устройство используется как схема выбора линии сигналов сканирования модуля сопротивления сдвигу, предоставленного в жидкокристаллическом дисплейном устройстве, имеется риск того, что выходной сигнал становится подверженным шуму, тем самым приводя к такому ложному срабатыванию, что последующая операция выбора линий сигналов сканирования не выполняется точно.

Здесь, последующее описание объясняет, как выходной сигнал становится подверженным шуму вследствие снижения его электрического потенциала в традиционном полупроводниковом устройстве. Фиг.47 показывает форму сигнала для выходного сигнала, на который влияет ток утечки в отключенном состоянии и т.п., чья форма сигнала показывается посредством пунктирных линий.

Например, в полупроводниковом устройстве 100 электрический заряд, предварительно заряжаемый в узле N1, разряжается вследствие влияния тока утечки в отключенном состоянии транзистора T103 и т.п., так что электрический потенциал в узле N1 постепенно понижается (см. пунктирную линию узла N1 на Фиг.47). Затем, в случае если электрический потенциал в узле N1 понижается до "VDD+Vth" в то время, когда синхросигнал φ находится на высоком уровне (VDD), транзистор T102 отключается. Это обуславливает выходной сигнал транзистора T102 иметь высокий импеданс, так что выходной сигнал OUT становится подверженным шуму.

Кроме того, если электрический потенциал в узле N1 дополнительно понижается ниже VDD, поскольку транзистор T102 находится в выключенном состоянии, уровень электрического потенциала самого выходного сигнала OUT понижается вследствие, например, тока утечки в отключенном состоянии транзистора T104 и т.п., как показано посредством пунктирной линии на Фиг.47. Это может приводить к ложному срабатыванию в последующей схеме.

Как описано выше, электрический потенциал в узле N1 понижается вследствие тока утечки в отключенном состоянии и т.п. По этой причине, например, в случае если синхросигнал φ низкий по частоте, или в случае, если период времени для сохранения (удержания) электрического заряда в узле N1 является длительным, электрический потенциал в узле N1 понижается еще больше. Вследствие этого выходной сигнал имеет высокий импеданс, тем самым становясь подверженным шуму.

Настоящее изобретение осуществлено с учетом проблем. Цель настоящего изобретения состоит в том, чтобы предоставлять полупроводниковое устройство, составленное из транзисторов одного типа электропроводности, причем полупроводниковое устройство может выводить стабильный сигнал посредством предотвращения снижения уровня электрического потенциала сигнала; и дисплейное устройство, включающее в себя полупроводниковое устройство.

Чтобы достигать цели, полупроводниковое устройство настоящего изобретения составлено из множества транзисторов одного типа электропроводности, причем полупроводниковое устройство включает в себя: из множества транзисторов первый транзистор, включающий в себя первый контактный вывод для приема напряжения включения, второй контактный вывод и управляющий контактный вывод для приема входного сигнала; из множества транзисторов, второй транзистор, включающий в себя первый контактный вывод для приема напряжения включения, второй контактный вывод, подключенный к выходному контактному выводу, и управляющий контактный вывод, подключенный ко второму контактному выводу первого транзистора; и конденсатор, предоставленный между точкой соединения между первым транзистором и вторым транзистором и контактным выводом синхросигнала для приема синхросигнала, причем синхросигнал имеет частоту, выше частоты выходного сигнала, выводимого из выходного контактного вывода.

Транзистор - это схема, включающая в себя первый контактный вывод, второй контактный вывод и управляющий контактный вывод. Когда в управляющий контактный вывод подается управляющий сигнал, первый контактный вывод и второй контактный вывод электрически подключаются друг к другу. Следовательно, схема выводит сигнал, имеющий требуемый уровень электрического потенциала, через первый и второй контактные выводы. Управляющий сигнал при этом имеет напряжение (уровень сигнала: VDD) для включения транзистора, когда управляющий сигнал вводится в управляющий контактный вывод, и напряжение (уровень сигнал: VSS) для выключения транзистора, когда управляющий сигнал вводится в управляющий контактный вывод.

Здесь, как описано выше, в традиционном полупроводниковом устройстве электрический потенциал в узле, подключенном к управляющему контактному выводу транзистора для вывода сигнала, имеющего требуемый уровень электрического потенциала, в общем, постепенно понижается вследствие тока утечки в отключенном состоянии и т.п.

С учетом этой проблемы полупроводниковое устройство настоящего изобретения имеет такую компоновку, что синхросигнал, имеющий частоту выше частоты выходного сигнала, вводится, через конденсатор, в узел, подключенный к управляющему контактному выводу транзистора для вывода сигнала, имеющего требуемый уровень электрического потенциала, т.е. точку соединения (узел) между первым и вторым транзисторами.

При этой компоновке электрический потенциал в узле повышается на электрический потенциал α посредством синхросигнала и конденсатора и затем, например, понижается на электрический потенциал β до "VDD-Vth+α-β (где Vth - это пороговое напряжение первого транзистора)" вследствие тока утечки в отключенном состоянии и т.п. После этого, когда синхросигнал переключается к низкому уровню (VSS), электрический потенциал в узле понижается до "VDD-Vth-β". Тем не менее, здесь, в случае если входной сигнал находится на высоком уровне (VDD), электрический потенциал в узле заряжается до "VDD-Vth". Затем, когда синхросигнал переключается к высокому уровню снова, электрический потенциал в узле повышается снова до "VDD-Vth+α".

Таким образом, в компоновке полупроводникового устройства операция повышения выполняется в соответствии с циклом синхросигнала, имеющего частоту выше частоты выходного сигнала. Следовательно, даже если электрический потенциал в узле понижается вследствие тока утечки в отключенном состоянии и т.п., электрический потенциал может сразу заряжаться обратно посредством операции повышения. Это дает возможность увеличения электрического потенциала с периодом, меньшим периода для традиционной компоновки. Следовательно, можно стабилизировать уровень электрического потенциала выходного сигнала и работу последующей схемы, которая принимает выходной сигнал.

Дополнительно, посредством задания амплитуды синхросигнала и конденсатора так, что повышенный электрический потенциал (VDD-Vth+α) в узле не меньше "VDD+Vth (где Vth - это пороговое напряжение второго транзистора)", становится возможным сохранять электрический уровень выходного сигнала на VDD.

Кроме того, поскольку сигнал, имеющий высокий электрический потенциал, вводится в управляющий контактный вывод второго транзистора, выходной сигнал может иметь низкий импеданс и может быть стабильным в отношении шума.

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов третий транзистор, включающий в себя первый контактный вывод, подключенный к точке соединения, второй контактный вывод для приема напряжения отключения и управляющий контактный вывод для приема управляющего сигнала.

При такой компоновке, в случае если третий транзистор включается посредством управляющего сигнала, электрический потенциал в узле может быть успешно уменьшен до VSS.

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов четвертый транзистор, включающий в себя первый контактный вывод, подключенный к выходному контактному выводу, второй контактный вывод для приема напряжения отключения и управляющий контактный вывод для приема управляющего сигнала.

При такой компоновке, в случае если третий и четвертый транзисторы включаются посредством управляющего сигнала, электрический потенциал в узле может быть успешно уменьшен до VSS и одновременно уровень электрического потенциала выходного сигнала может быть стабилизирован на низком уровне (напряжение выключения-VSS).

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов пятый транзистор, включающий в себя первый контактный вывод для приема напряжения включения, второй контактный вывод, подключенный к точке соединения, и управляющий контактный вывод, подключенный к выходному контактному выводу.

При такой компоновке выходной сигнал вводится в управляющий контактный вывод пятого транзистора. Следовательно, даже если электрический потенциал в узле понижается вследствие тока утечки в отключенном состоянии и т.п. при условии, что входной сигнал находится на низком уровне и первый транзистор находится в выключенном состоянии, электрический потенциал в узле может заряжаться снова до "VDD-Vth" в течение периода времени, в котором выходной сигнал находится на высоком уровне (напряжение включения-VDD).

Вследствие этого электрический потенциал в узле может повышаться до "VDD-Vth+α" в течение периода времени, в котором синхросигнал находится на высоком уровне. Следовательно, становится возможным более успешно стабилизировать уровень электрического потенциала выходного сигнала.

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов шестой транзистор, который выводит входной сигнал, при этом шестой транзистор включает в себя первый контактный вывод, подключенный к входному контактному выводу; второй контактный вывод, подключенный к управляющему контактному выводу первого транзистора и выходному контактному выводу, и управляющий контактный вывод для приема сигнала разрешения.

При такой компоновке, как только сигнал разрешения переключается к высокому уровню, независимо от того, переключается или нет сигнал разрешения к низкому уровню позднее, можно сохранять ввод сигнала, находящегося на высоком уровне, в управляющий контактный вывод первого транзистора в течение периода времени, в котором выходной сигнал находится на высоком уровне. Следовательно, можно стабильно сохранять активное состояние полупроводникового устройства.

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов седьмой транзистор, включающий в себя первый контактный вывод, подключенный к точке соединения, второй контактный вывод для приема напряжения отключения и управляющий контактный вывод для приема сигнала инициализации для стабилизации начального состояния полупроводникового устройства.

При такой компоновке сигнал инициализации, находящийся на высоком уровне, вводится в седьмой транзистор в начальном состоянии, так что электрический потенциал в узле может быть стабилизирован на VSS. Следовательно, можно стабилизировать начальное состояние.

Полупроводниковое устройство настоящего изобретения предпочтительно дополнительно включает в себя: из множества транзисторов восьмой транзистор, включающий в себя первый контактный вывод, подключенный к контактному выводу синхросигнала, второй контактный вывод, подключенный к концу конденсатора, и управляющий контактный вывод для приема входного сигнала.

При такой компоновке, посредством управления включенным/отключенным состоянием восьмого транзистора можно электрически разделять контактный вывод синхросигнала и конденсатор, подключенный к узлу, друг от друга. Это может заставлять нагрузку контактного вывода синхросигнала быть только паразитной емкостью восьмого транзистора. Следовательно, можно снизить потребление электроэнергии посредством снижения требуемой возбуждающей способности схемы для возбуждения контактного вывода синхросигнала и сокращения емкости.

Чтобы достигать цели, полупроводниковое устройство настоящего изобретения составлено из множества транзисторов одного типа электропроводности, причем полупроводниковое устройство включает в себя: из множества транзисторов первый транзистор, включающий в себя первый контактный вывод для приема напряжения включения, второй контактный вывод и управляющий контактный вывод для приема входного сигнала; из множества транзисторов второй транзистор, включающий в себя первый контактный вывод для приема напряжения включения, второй контактный вывод, подключенный к выходному контактному выводу, и управляющий контактный вывод, подключенный ко второму контактному выводу первого транзистора; конденсатор, предоставленный между точкой соединения между первым транзистором и вторым транзистором и контактным выводом синхросигнала для приема синхросигнала; из множества транзисторов десятый транзистор, включающий в себя первый контактный вывод, подключенный к точке соединения, второй контактный вывод и управляющий контактный вывод для приема напряжения включения; и из множества транзисторов третий транзистор, включающий в себя первый контактный вывод, подключенный ко второму контактному выводу десятого транзистора, второй контактный вывод для приема напряжения отключения и управляющий контактный вывод для приема управляющего сигнала, причем синхросигнал имеет частоту выше частоты выходного сигнала, выводимого из выходного контактного вывода.

Электрический потенциал в узле повышается посредством синхросигнала так, что высокое напряжение прикладывается к каждому из транзисторов, подключенных к узлу. Следовательно, имеется риск того, что этот транзистор ломается вследствие более высокого напряжения, чем его выдерживаемое напряжение.

Полупроводниковое устройство, описанное выше, включает в себя десятый транзистор между узлом и третьим транзистором. Это может уменьшать электрический потенциал, например, в третьем транзисторе (подробности этого эффекта описываются ниже). Следовательно, можно создавать высоконадежную схему.

В полупроводниковом устройстве настоящего изобретения синхросигнал предпочтительно показывает такую форму сигнала, что высокий уровень и низкий уровень повторяются попеременно и периодически, причем синхросигнал задается так, что период времени низкого уровня в одном цикле является эквивалентным периоду времени от времени, когда синхросигнал переключается от высокого уровня к низкому уровню, до времени, когда электрический потенциал в точке соединения насыщается.

Это может уменьшать импеданс выходного сигнала при сохранении активного состояния полупроводникового устройства.

Дисплейное устройство настоящего изобретения включает в себя любое одно из полупроводниковых устройств, описанных выше.

Следовательно, можно предоставлять дисплейное устройство, которое может выводить стабильный сигнал посредством предотвращения снижения уровня электрического потенциала.

Следует отметить, что дисплейным устройством настоящего изобретения предпочтительно является жидкокристаллическое дисплейное устройство.

Дополнительные цели, признаки и эффекты настоящего изобретения должны стать очевидными посредством нижеприведенного описания. Дополнительно, преимущества настоящего изобретения будут очевидны из последующего пояснения со ссылками на чертежи.

Краткое описание чертежей

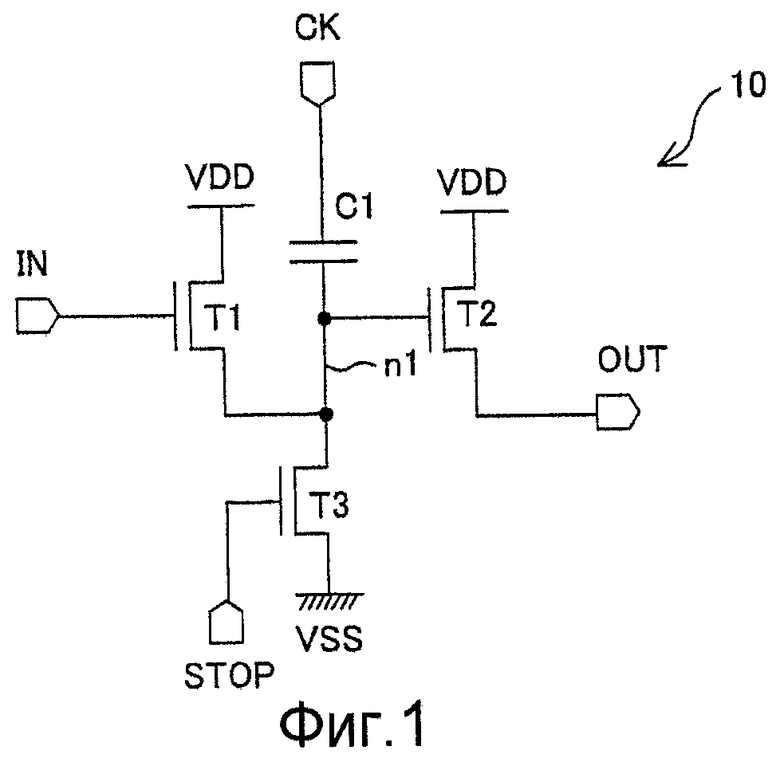

Фиг.1 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 1 настоящего изобретения.

Фиг.2 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.1.

Фиг.3 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.1, в случае если на схему оказывает влияние ток утечки в отключенном состоянии и т.п.

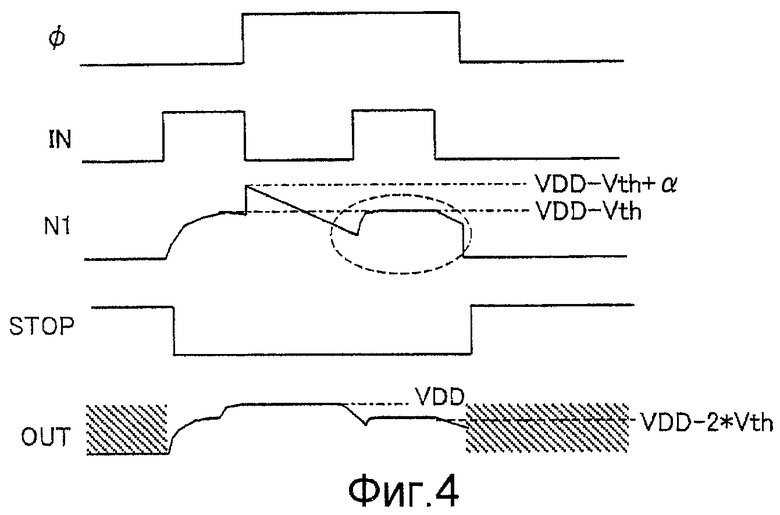

Фиг.4 - это временная диаграмма, показывающая формы различных сигналов традиционной схемы в случае, если на схему оказывает влияние ток утечки в отключенном состоянии и т.п.

Фиг.5 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.1, в случае если синхросигнал φ вводится в контактный вывод стока транзистора T2.

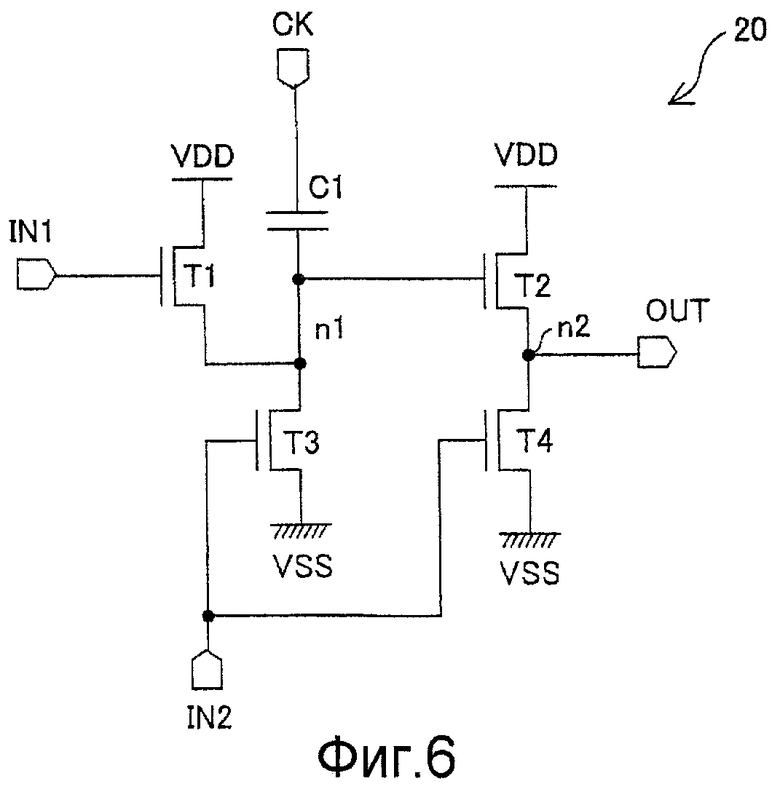

Фиг.6 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 2 настоящего изобретения.

Фиг.7 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.6.

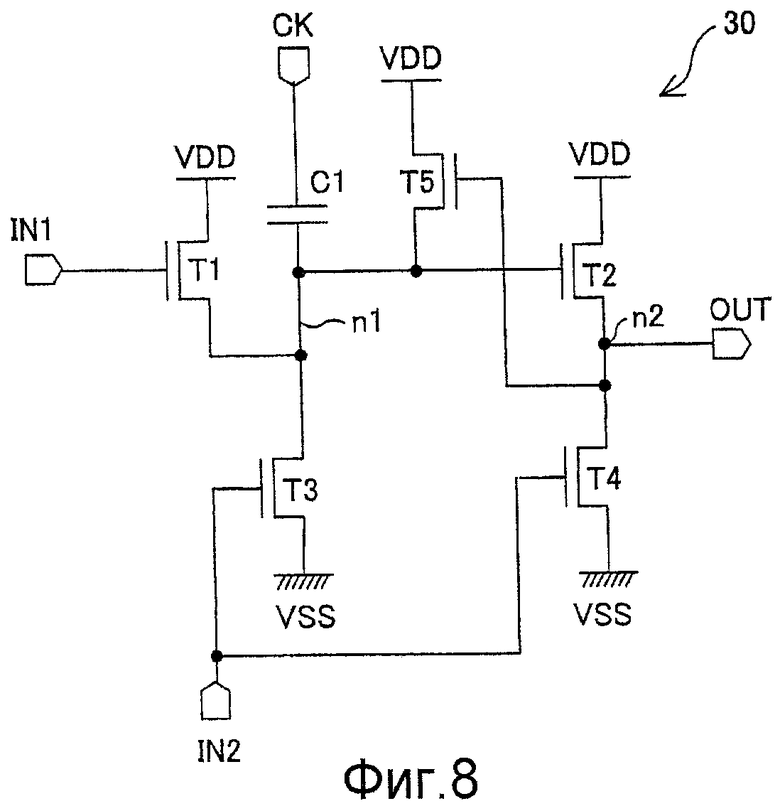

Фиг.8 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 3 настоящего изобретения.

Фиг.9 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 4 настоящего изобретения.

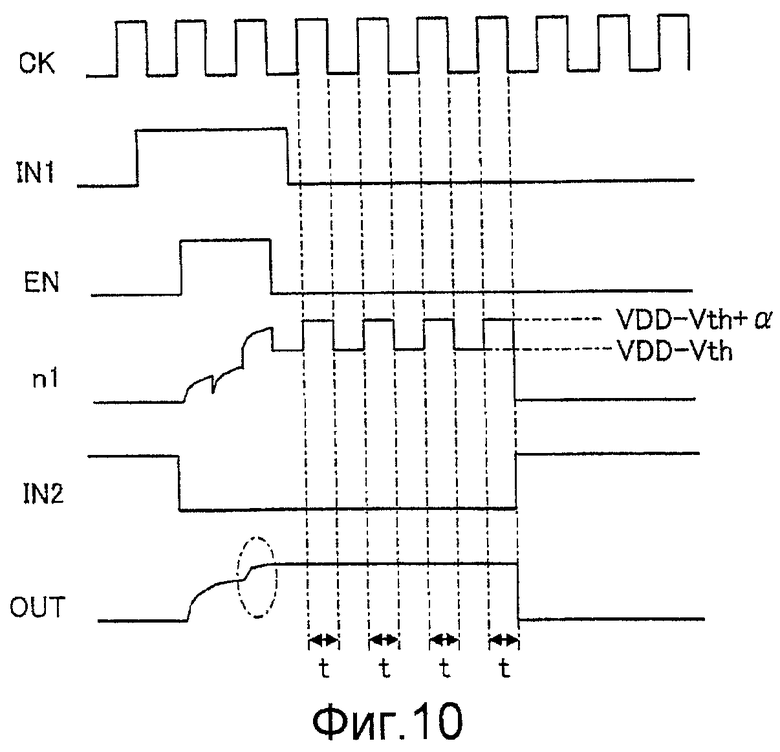

Фиг.10 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.9.

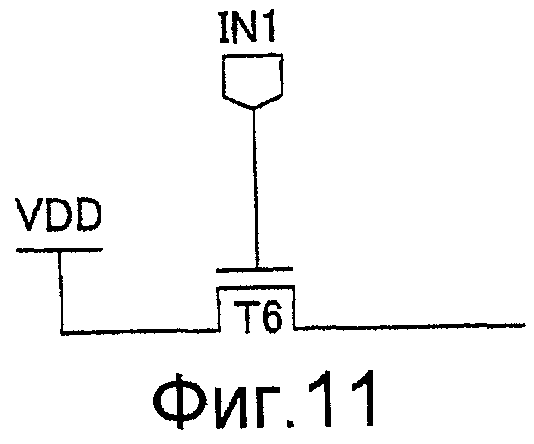

Фиг.11 - это принципиальная схема, иллюстрирующая другое расположение транзистора T6 в схеме, проиллюстрированной на Фиг.9.

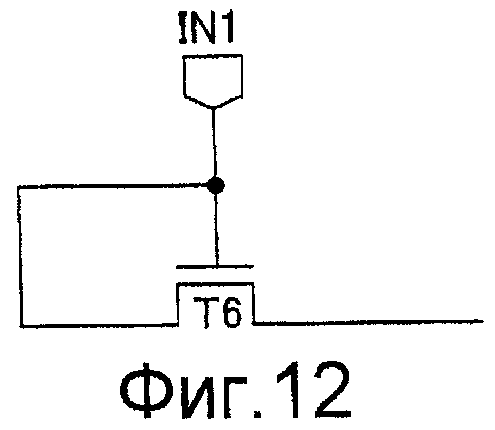

Фиг.12 - это принципиальная схема, иллюстрирующая еще одно другое расположение транзистора T6 в схеме, проиллюстрированной на Фиг.9.

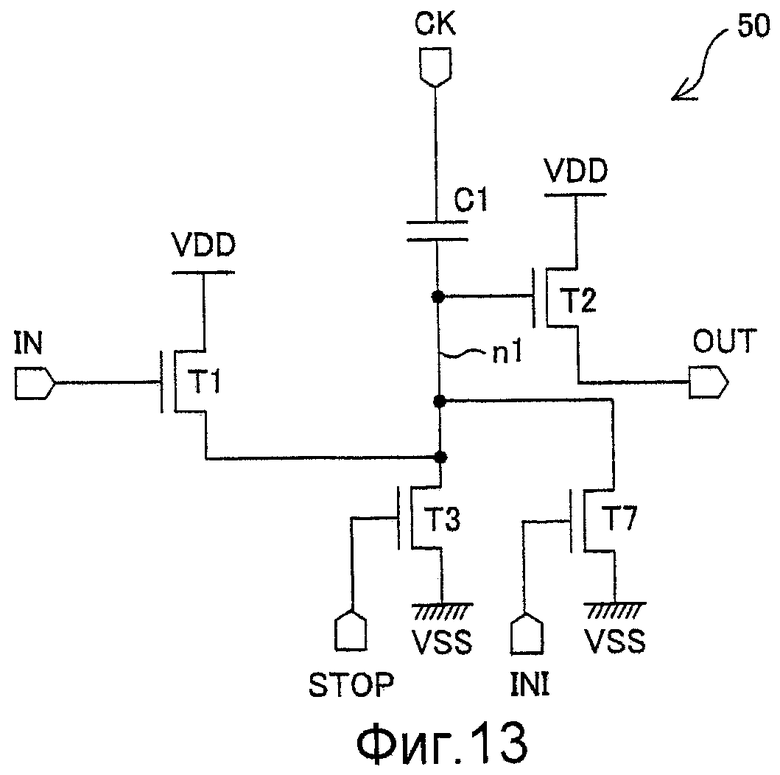

Фиг.13 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 5 настоящего изобретения.

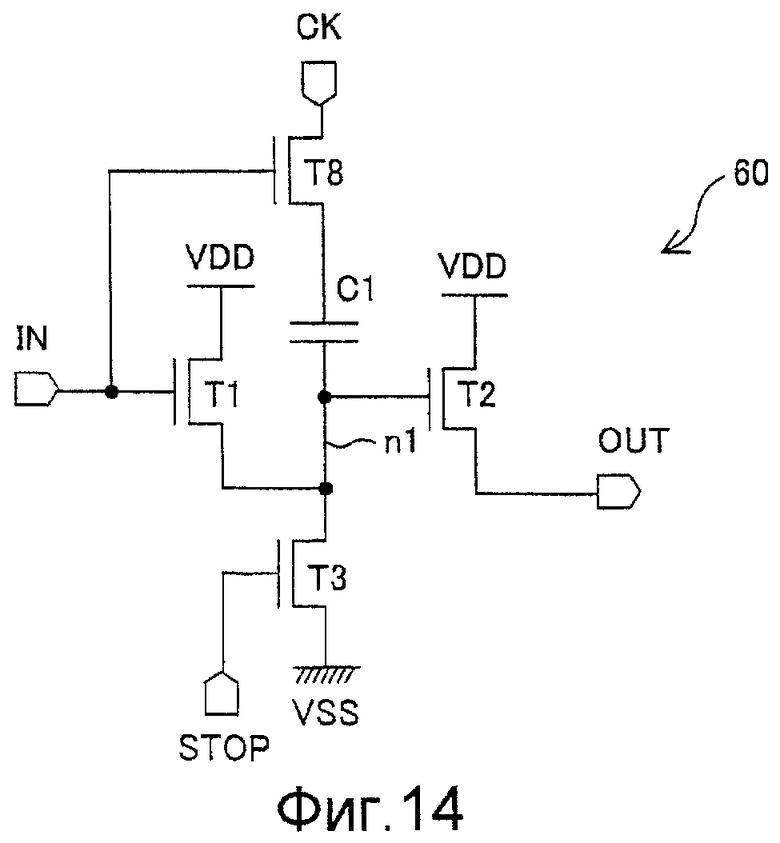

Фиг.14 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 6 настоящего изобретения.

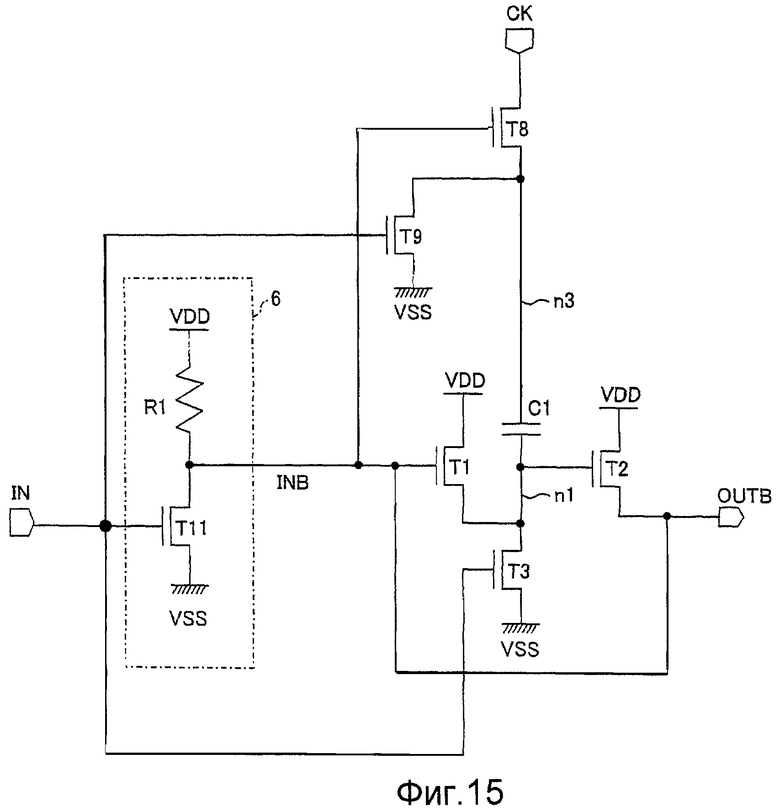

Фиг.15 - это принципиальная схема, иллюстрирующая другую компоновку схемы, проиллюстрированной на Фиг.14.

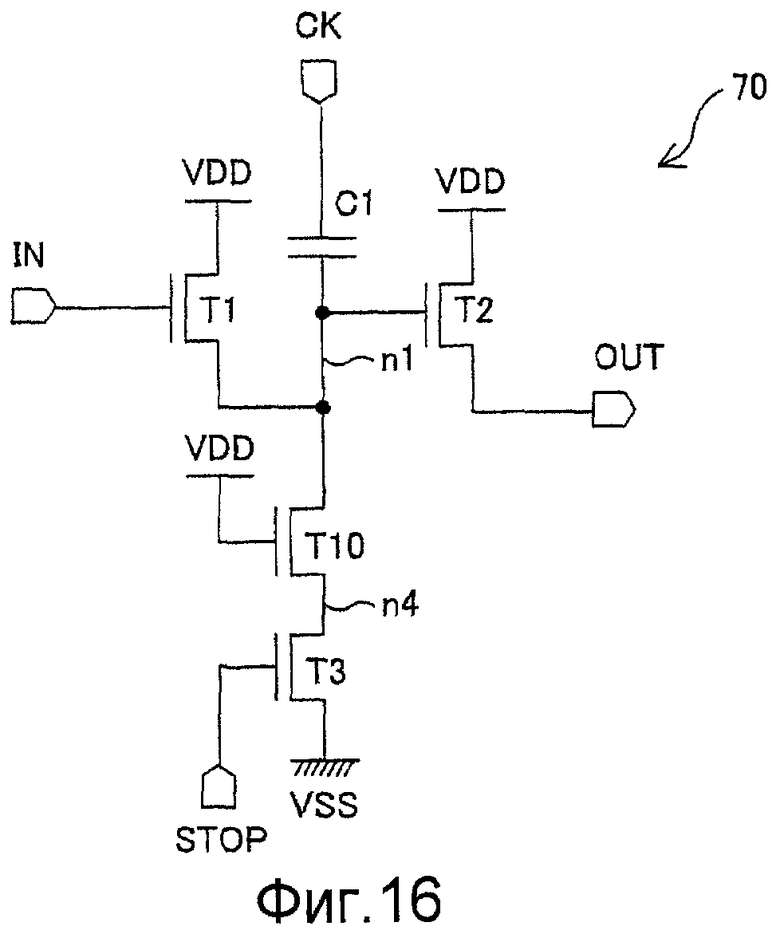

Фиг.16 - это принципиальная схема, иллюстрирующая компоновку схемы в соответствии с вариантом осуществления 7 настоящего изобретения.

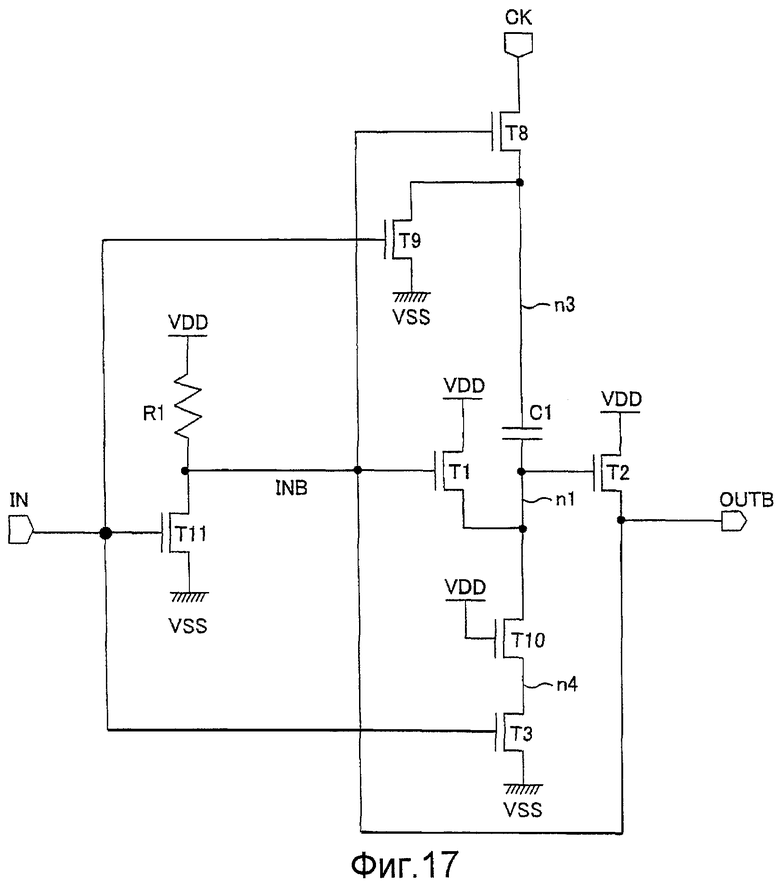

Фиг.17 - это принципиальная схема, иллюстрирующая другую компоновку схемы в соответствии с вариантом осуществления 7 настоящего изобретения.

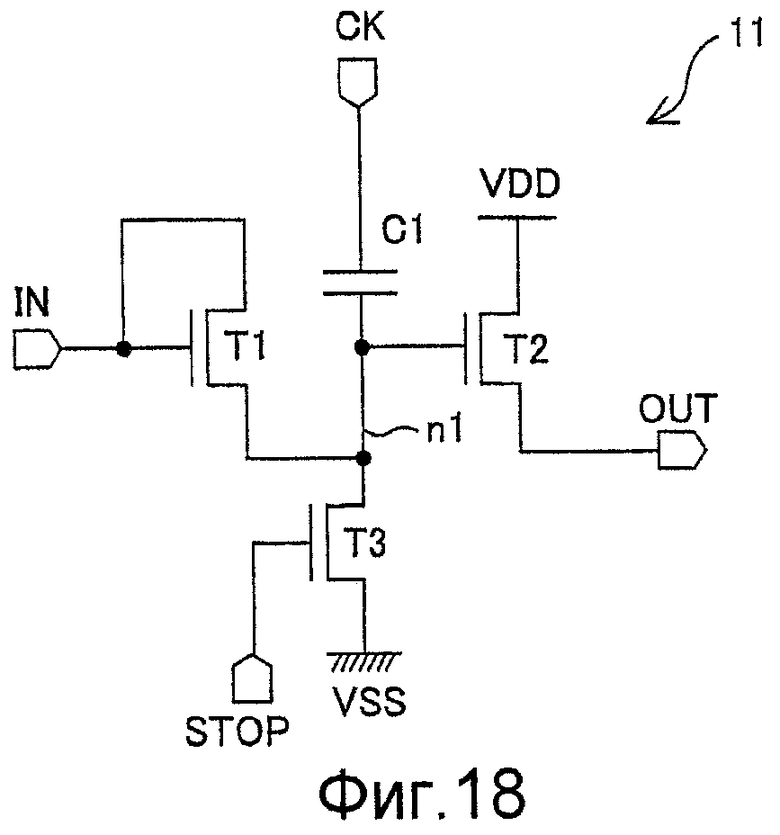

Фиг.18 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.1.

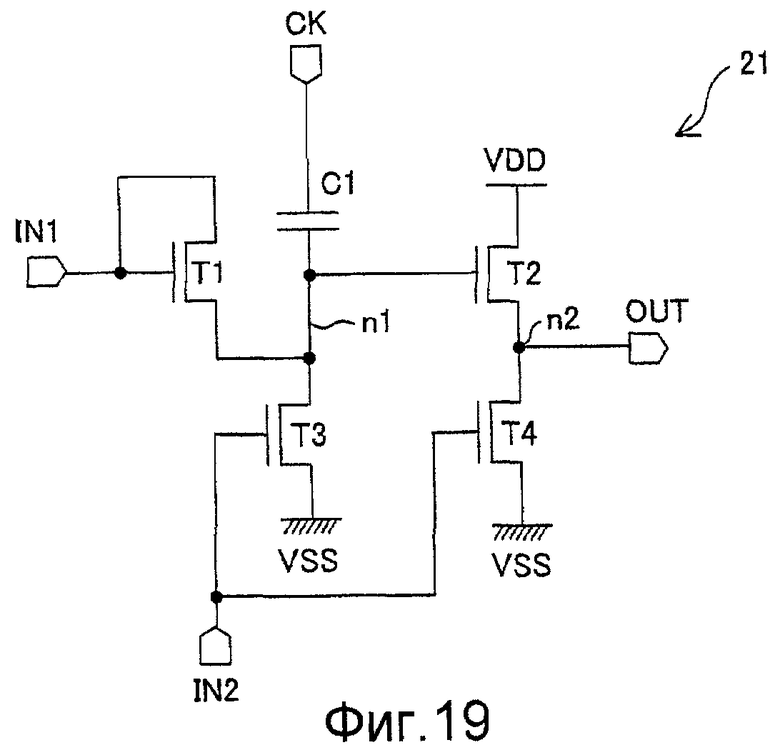

Фиг.19 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.6.

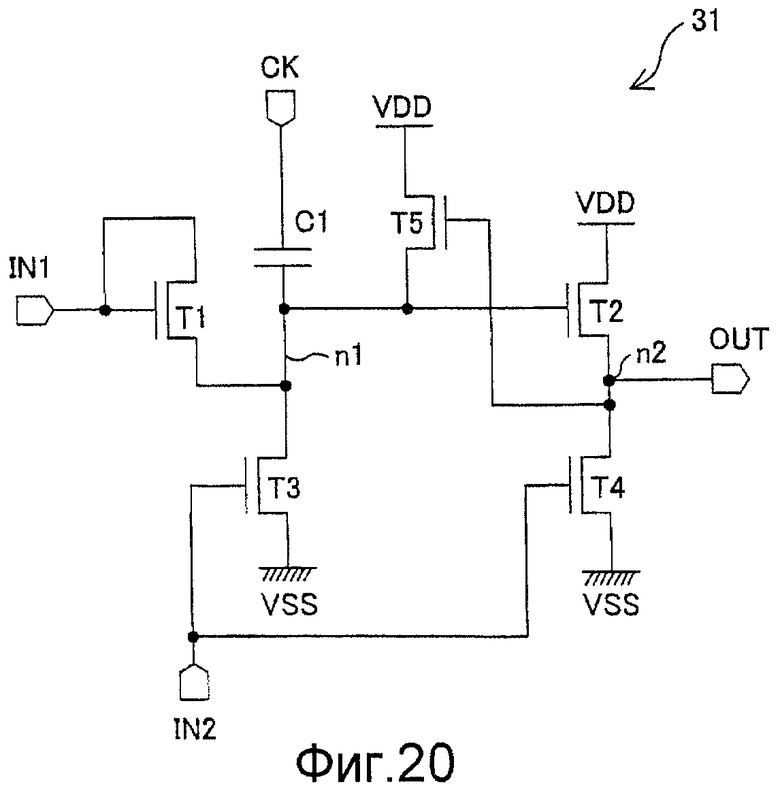

Фиг.20 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.8.

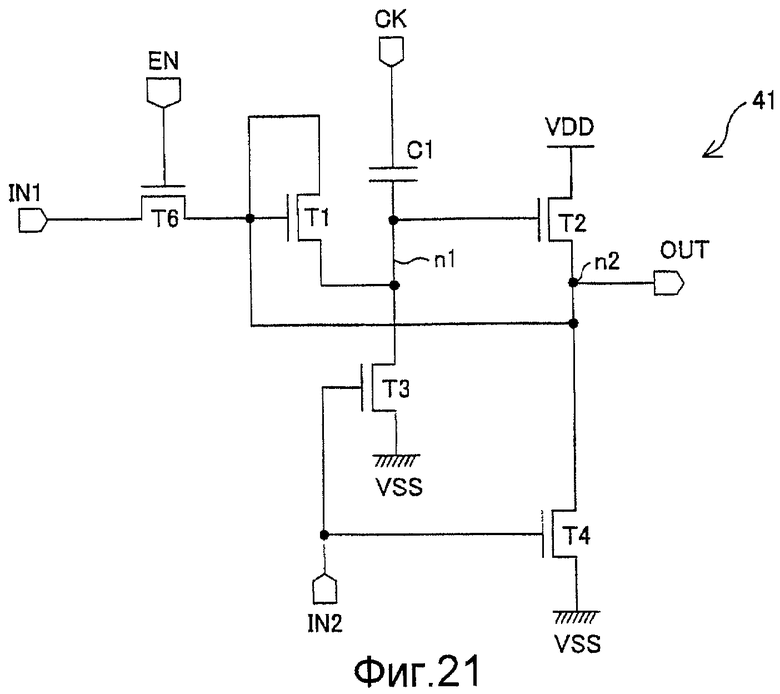

Фиг.21 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.9.

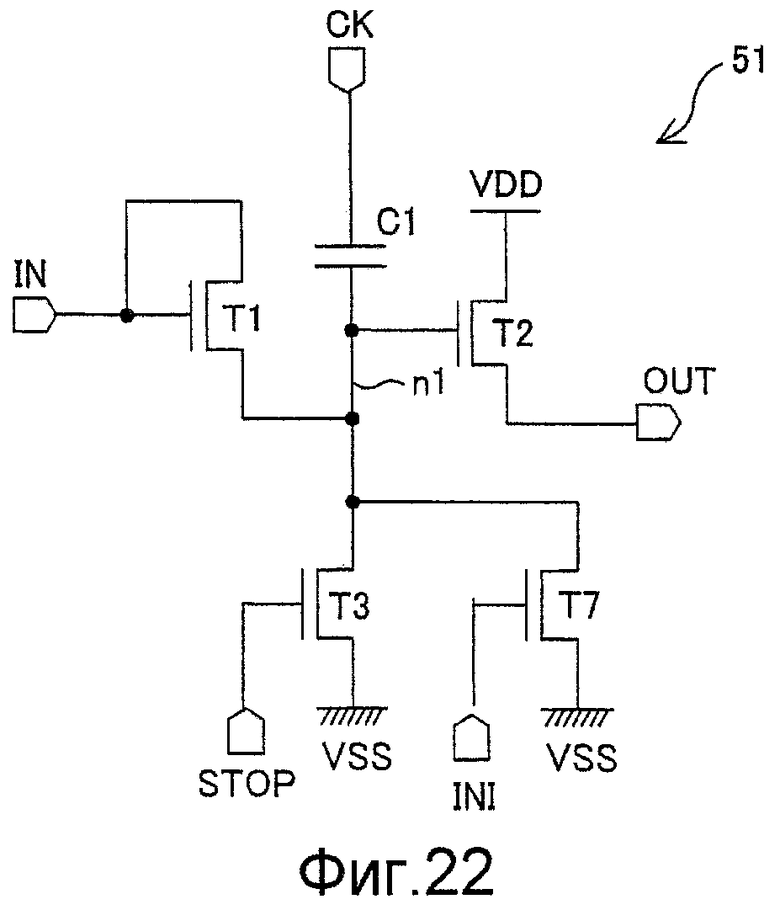

Фиг.22 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.13.

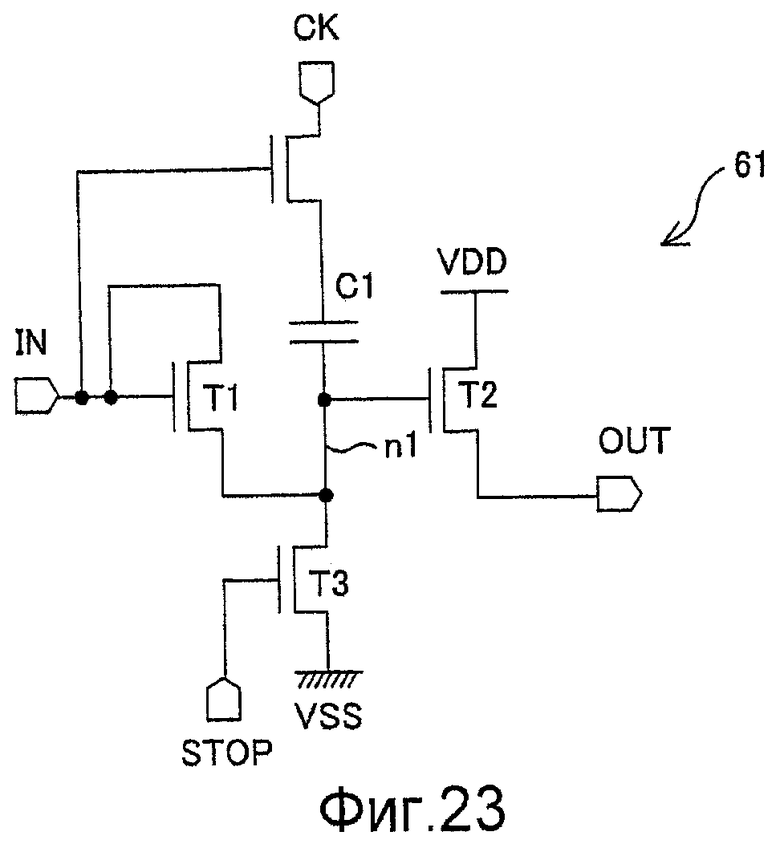

Фиг.23 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.14.

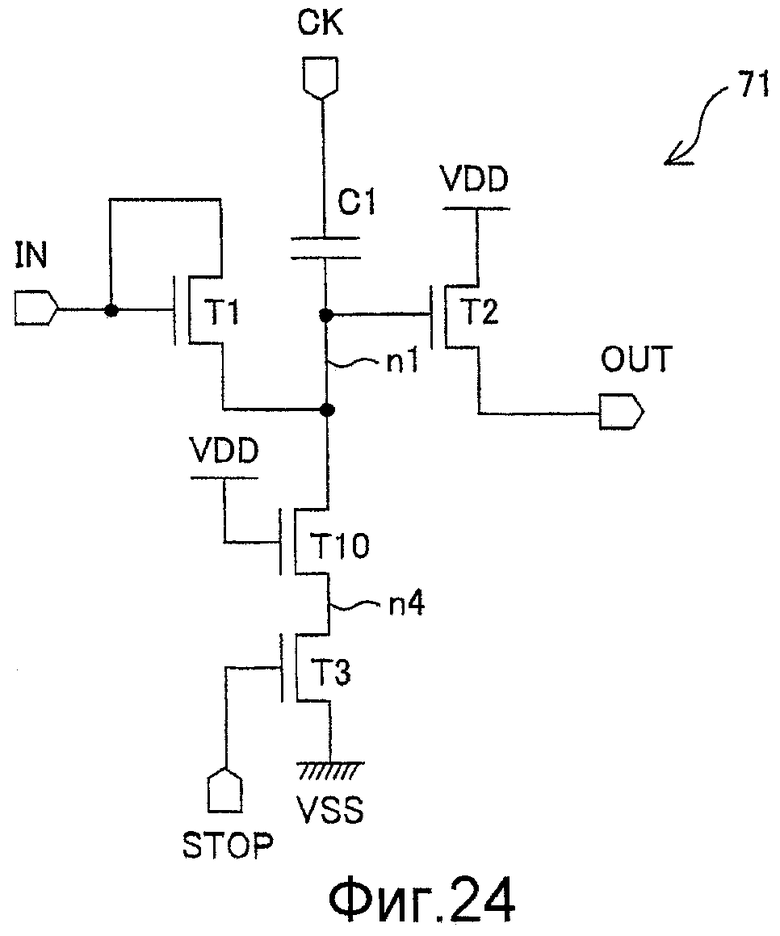

Фиг.24 - это принципиальная схема, иллюстрирующая такую компоновку, что транзистор T1 имеет диодное включение в схеме, проиллюстрированной на Фиг.16.

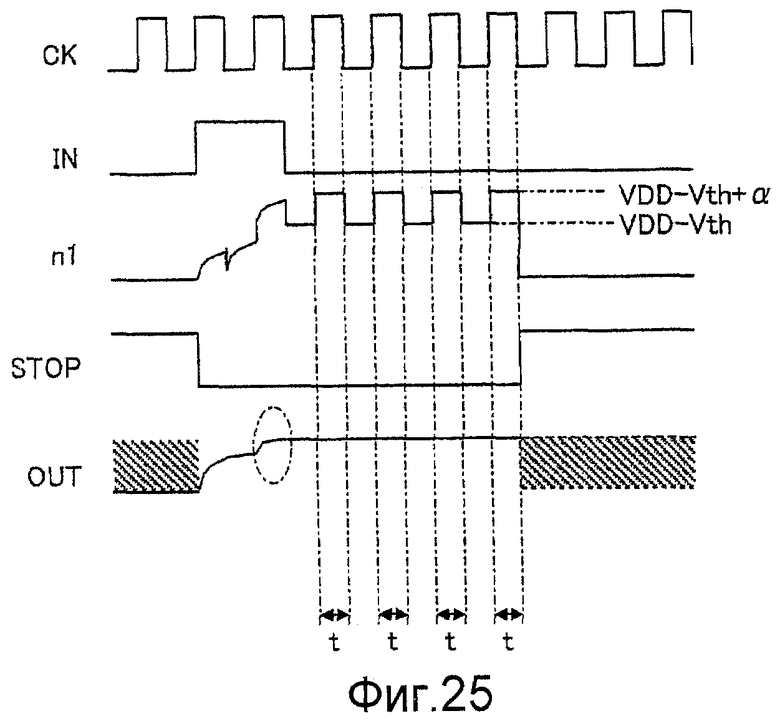

Фиг.25 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.18.

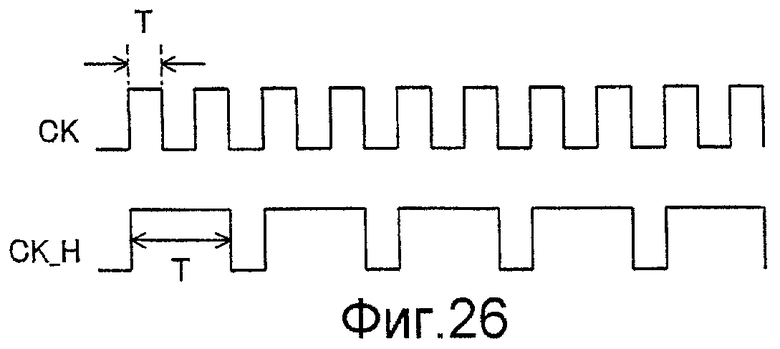

Фиг.26 - это вид, показывающий форму синхросигнала CK каждого из вариантов осуществления настоящего изобретения.

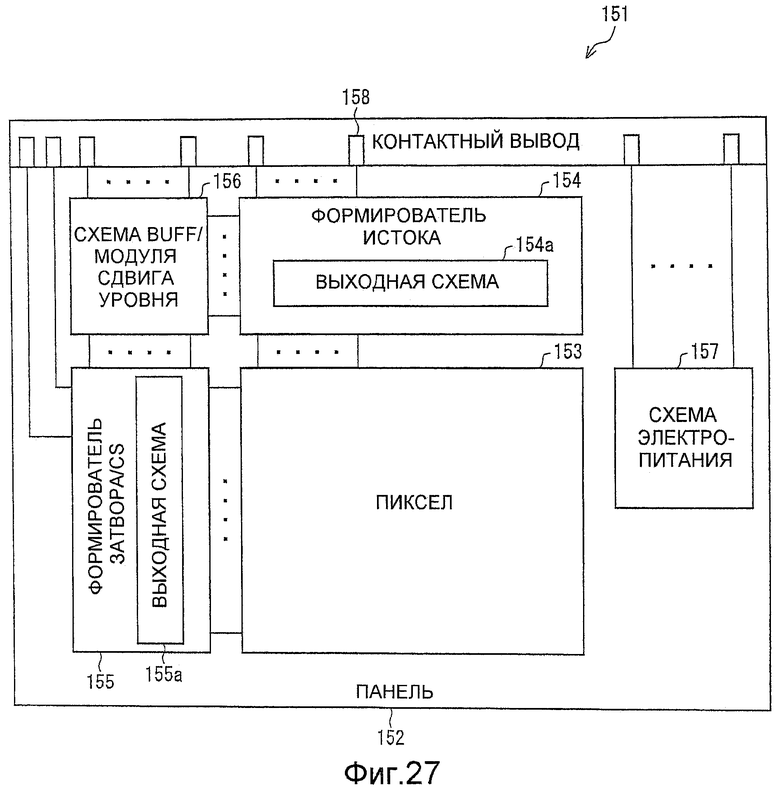

Фиг.27 - это блок-схема, иллюстрирующая полную компоновку жидкокристаллического дисплейного устройства в соответствии с одним вариантом осуществления настоящего изобретения.

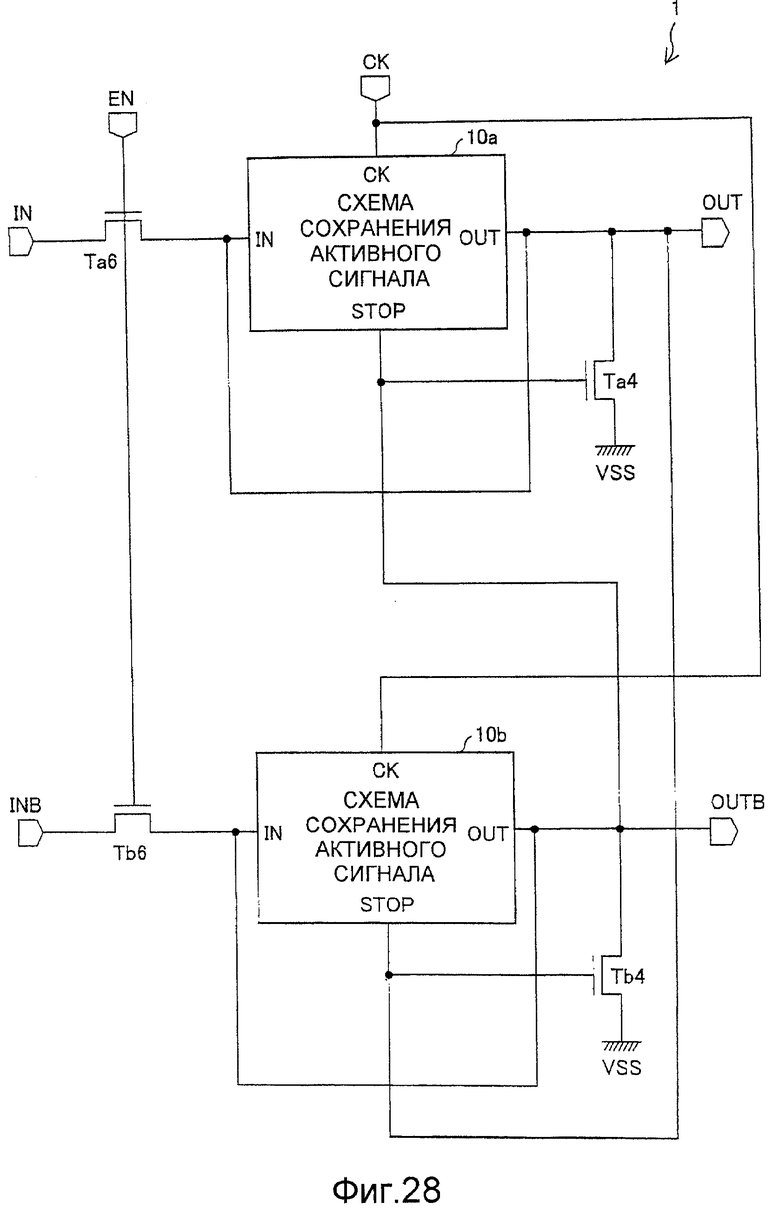

Фиг.28 - это блок-схема, иллюстрирующая компоновку запоминающей схемы в соответствии с примером 1 настоящего изобретения, причем запоминающая схема предоставляется в CS-формирователе.

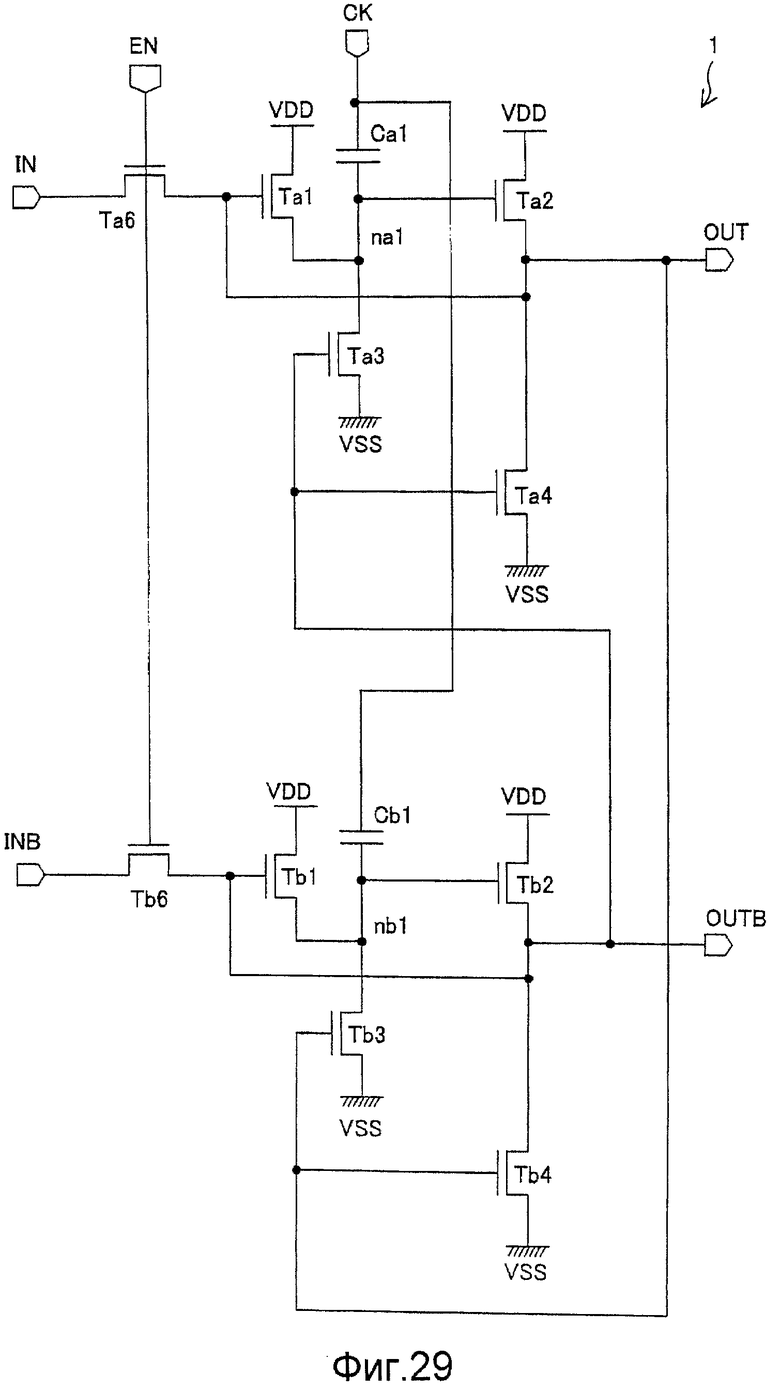

Фиг.29 - это принципиальная схема, иллюстрирующая компоновку запоминающей схемы, проиллюстрированной на Фиг.28.

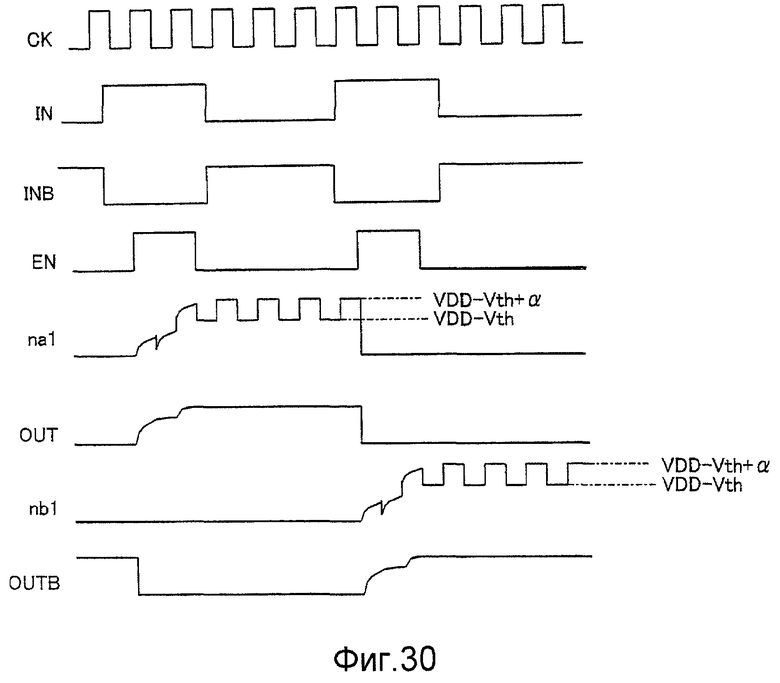

Фиг.30 - это временная диаграмма, показывающая формы различных сигналов запоминающей схемы, проиллюстрированной на Фиг.28.

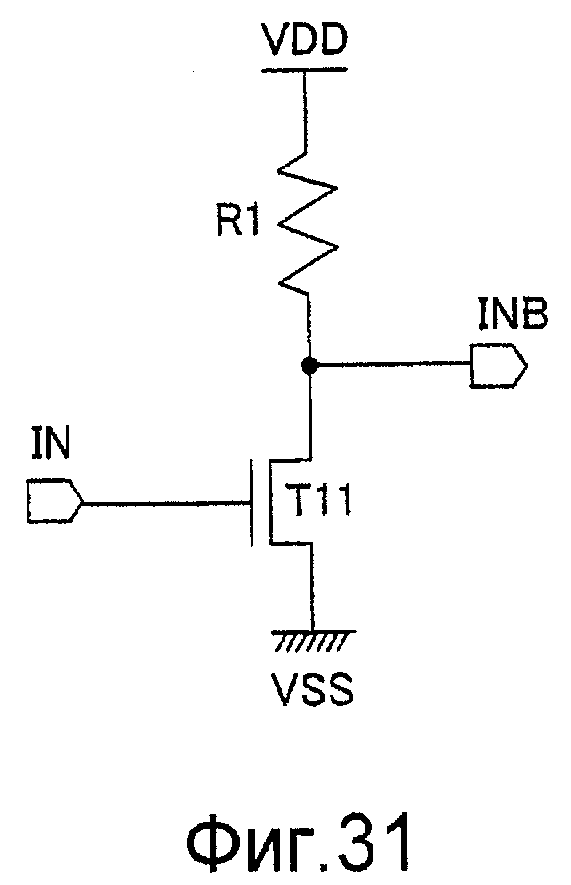

Фиг.31 - это принципиальная схема, иллюстрирующая компоновку схемы инвертора для формирования инверсного сигнала INB на основе входного сигнала IN в запоминающей схеме, проиллюстрированной на Фиг.28.

Фиг.32 - это принципиальная схема, иллюстрирующая другую компоновку схемы инвертора для формирования инверсного сигнала INB на основе входного сигнала IN в запоминающей схеме, проиллюстрированной на Фиг.28.

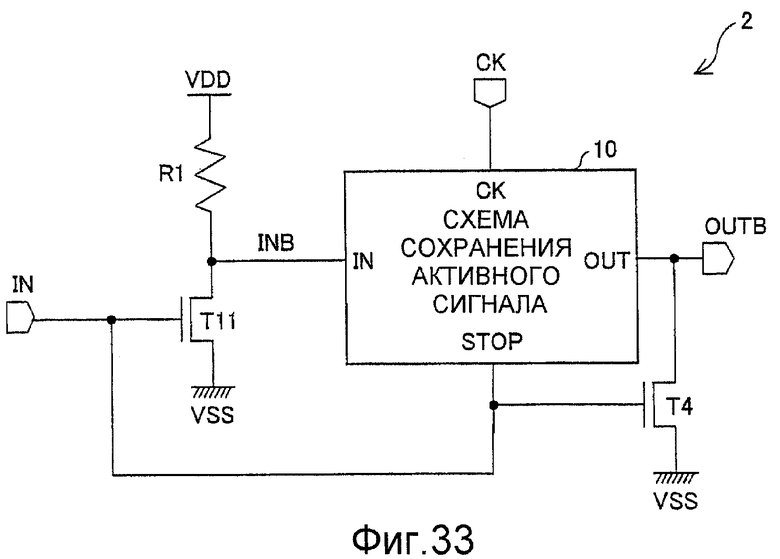

Фиг.33 - это блок-схема, иллюстрирующая компоновку буферной схемы в соответствии с примером 2 настоящего изобретения.

Фиг.34 - это принципиальная схема, иллюстрирующая компоновку буферной схемы, проиллюстрированной на Фиг.33.

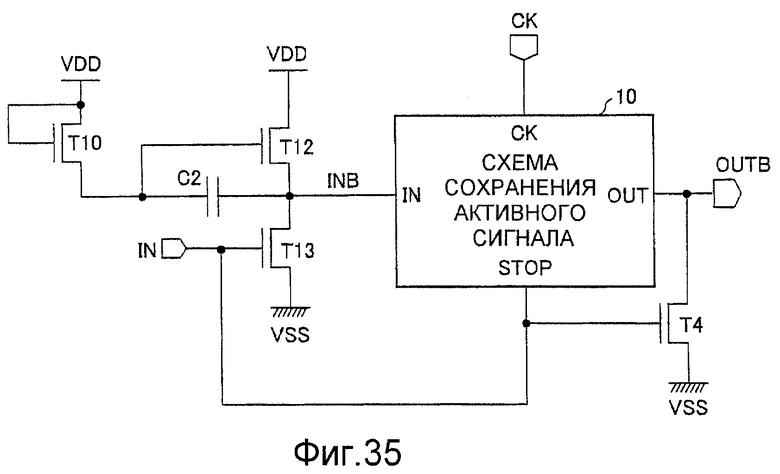

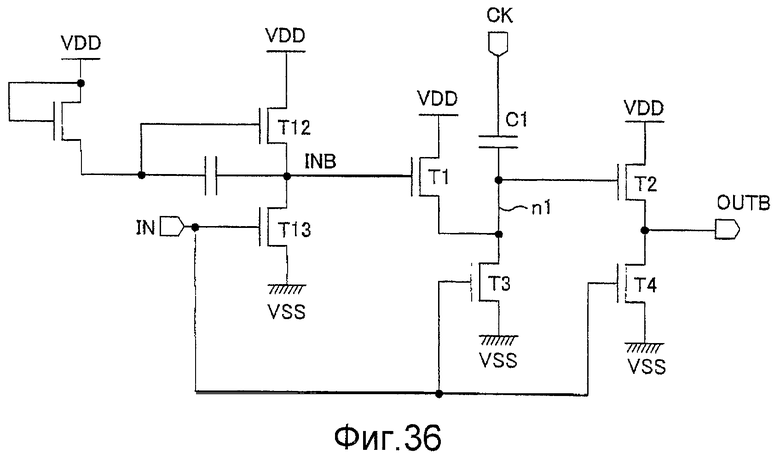

Фиг.35 - это блок-схема, иллюстрирующая такую компоновку, что инвертор составлен из схемы компенсационной обратной связи в буферной схеме, проиллюстрированной на Фиг.33.

Фиг.36 - это принципиальная схема, иллюстрирующая компоновку буферной схемы, проиллюстрированной на Фиг.35.

Фиг.37 - это блок-схема, иллюстрирующая компоновку буферной схемы в соответствии с примером 3 настоящего изобретения.

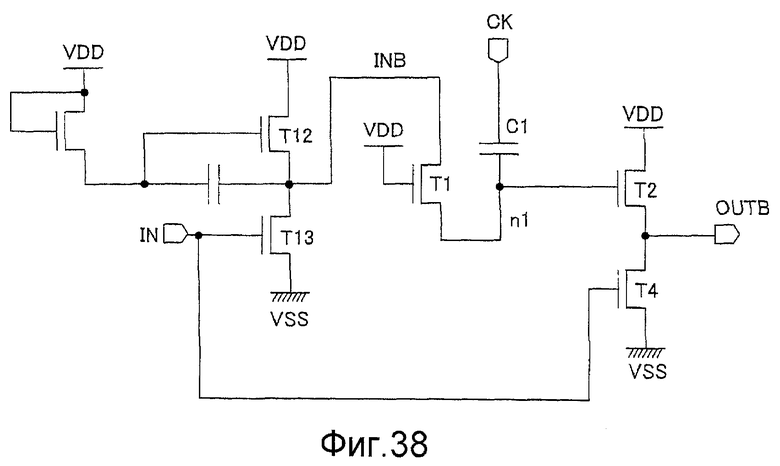

Фиг.38 - это принципиальная схема, иллюстрирующая такую компоновку, что инвертор составлен из схемы компенсационной обратной связи в буферной схеме, проиллюстрированной на Фиг.37.

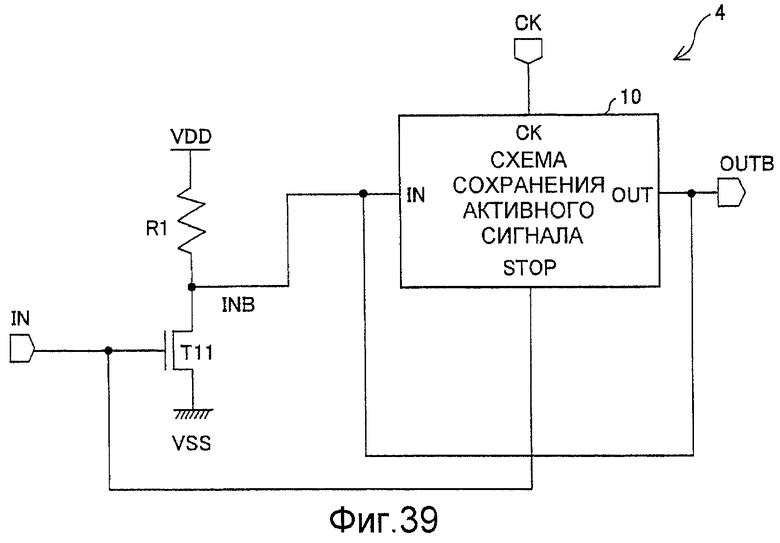

Фиг.39 - это блок-схема, иллюстрирующая компоновку буферной схемы в соответствии с примером 4 настоящего изобретения.

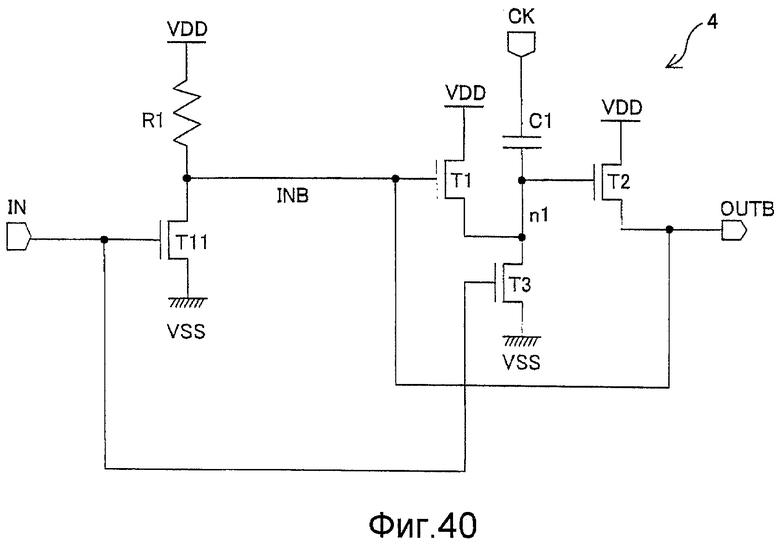

Фиг.40 - это принципиальная схема, иллюстрирующая компоновку буферной схемы, проиллюстрированной на Фиг.39.

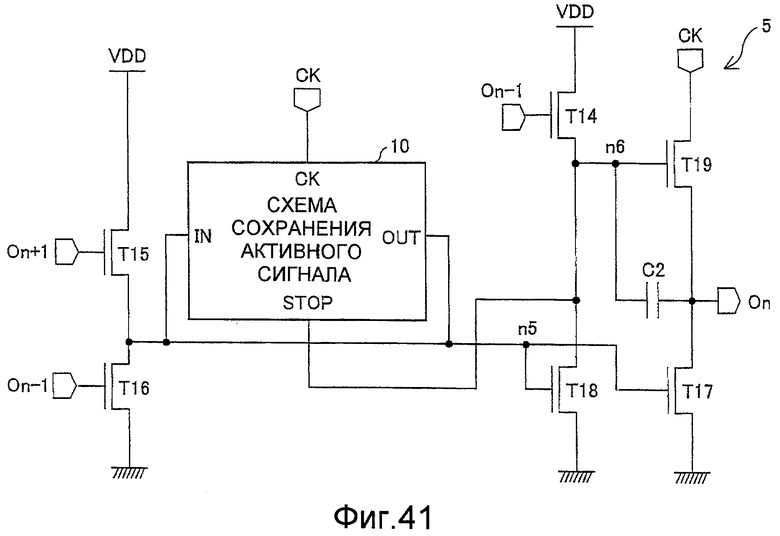

Фиг.41 - это блок-схема, иллюстрирующая компоновку модульной схемы в соответствии с примером 4 настоящего изобретения, причем модульная схема составляет модуль сопротивления сдвигу.

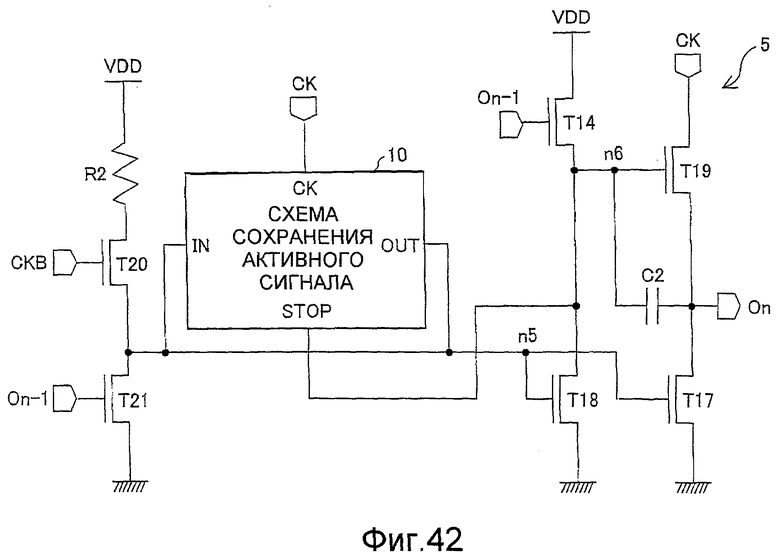

Фиг.42 - это блок-схема, иллюстрирующая другую компоновку модульной схемы, проиллюстрированной на Фиг.41, причем модульная схема составляет модуль сопротивления сдвигу.

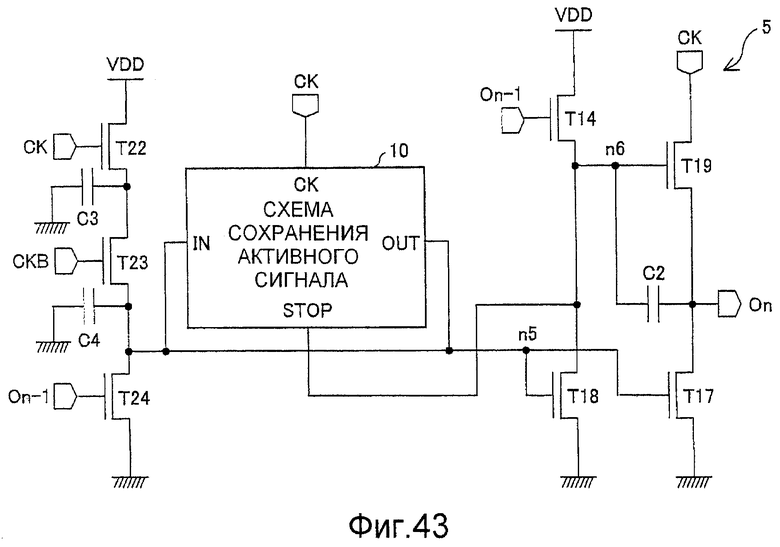

Фиг.43 - это блок-схема, иллюстрирующая еще одну другую компоновку модульной схемы, проиллюстрированной на Фиг.41, причем модульная схема составляет модуль сопротивления сдвигу.

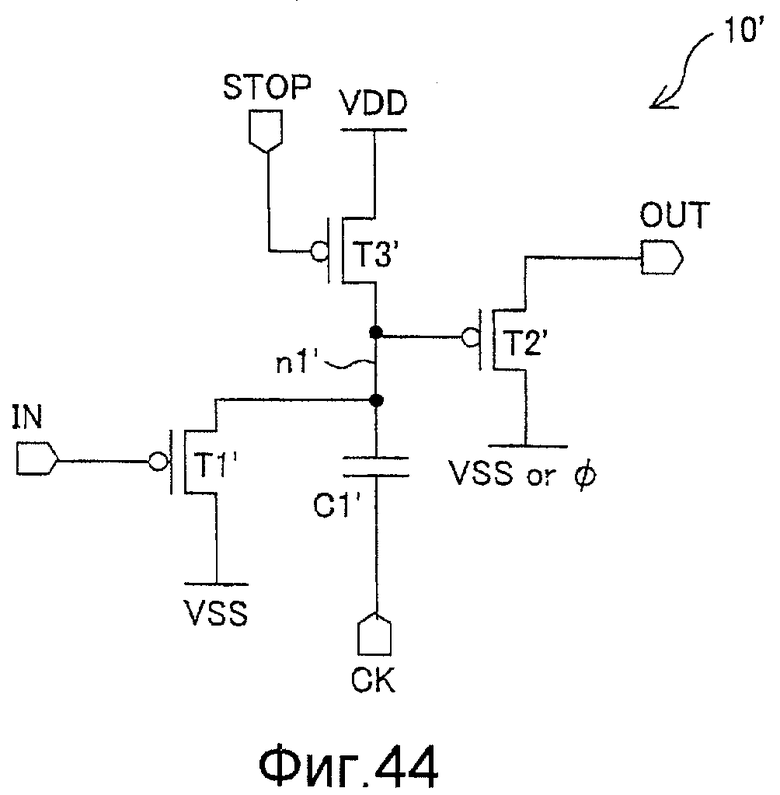

Фиг.44 - это принципиальная схема, иллюстрирующая такую компоновку, что схема, проиллюстрированная на Фиг.16, составлена из транзисторов с каналом p-типа.

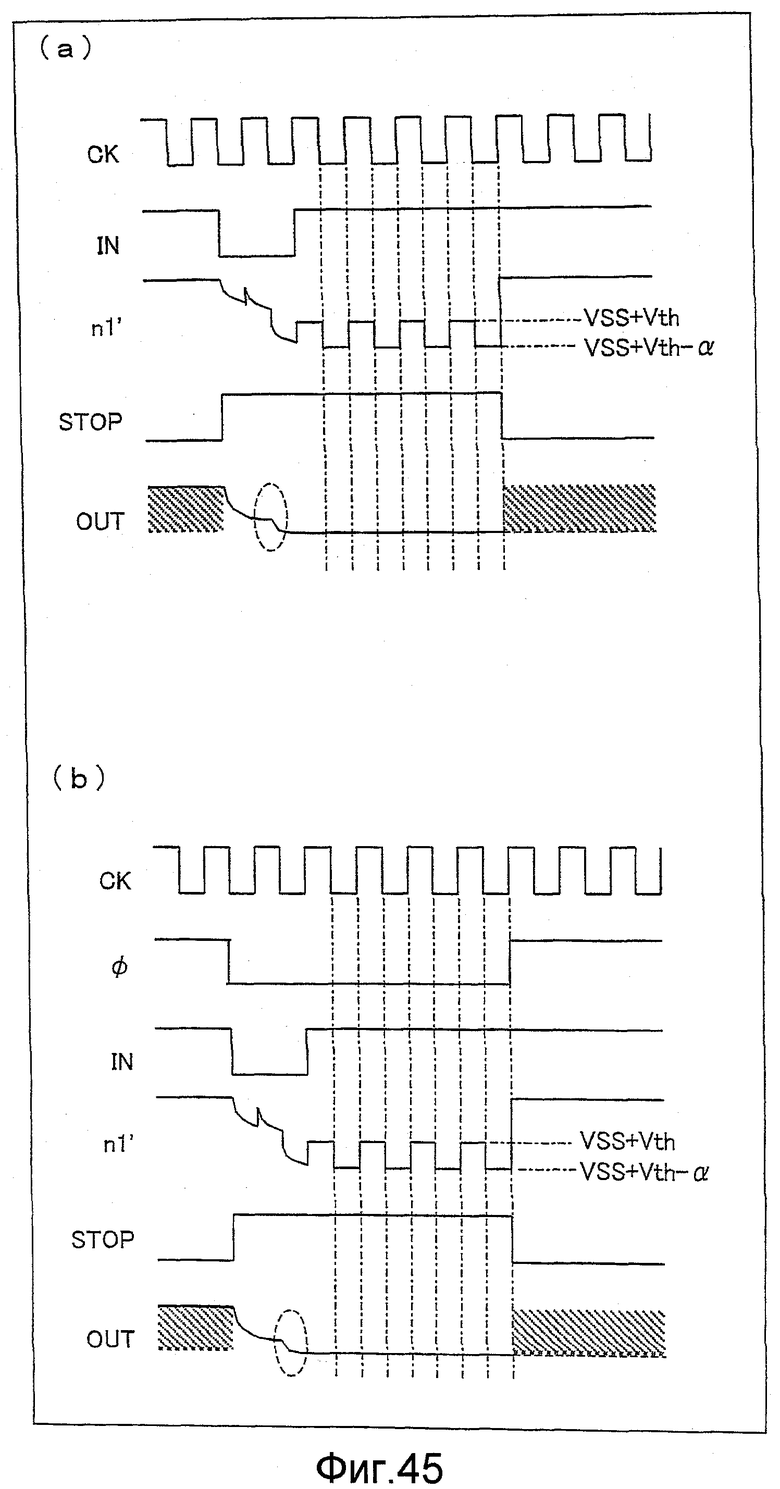

Фиг.45 - это временная диаграмма, показывающая формы различных сигналов схемы, проиллюстрированной на Фиг.44: (a) на Фиг.45 показывает формы сигнала в случае, если VSS вводится в контактный вывод истока транзистора T2'; и (b) на Фиг.45 показывает формы сигнала в случае, если синхросигнал φ вводится в контактный вывод истока транзистора T2'.

Фиг.46 - это принципиальная схема, иллюстрирующая компоновку традиционного полупроводникового устройства.

Фиг.47 - это временная диаграмма, показывающая формы различных сигналов полупроводникового устройства, проиллюстрированного на Фиг.46.

Список номеров ссылок

1 - запоминающая схема

2, 3, 4 - буферная схема

5 - модульная схема (модуля сопротивления сдвигу)

10, 20, 30, 40, 50, 60, 70 - схема (полупроводниковое устройство)

11, 21, 31, 41, 51, 61, 71 - схема (полупроводниковое устройство)

T1 - транзистор (первый транзистор)

T2 - транзистор (второй транзистор)

T3 - транзистор (третий транзистор)

T4 - транзистор (четвертый транзистор)

T5 - транзистор (пятый транзистор)

T6 - транзистор (шестой транзистор)

T7 - транзистор (седьмой транзистор)

T8 - транзистор (восьмой транзистор)

T9 - транзистор (девятый транзистор)

T10 - транзистор (десятый транзистор)

151 - жидкокристаллическое дисплейное устройство (дисплейное устройство)

n1, n2, n3, n4, n5, n6 - узел

100 - полупроводниковое устройство

Описание вариантов осуществления

Варианты осуществления настоящего изобретения описываются ниже со ссылкой на Фиг.1-45.

Схема сохранения (удержания) активного сигнала (в дальнейшем в этом документе эта схема упоминается как "схема" для простоты пояснения), соответствующая полупроводниковому устройству настоящего изобретения, состоит из транзисторов одного типа электропроводности, т.е. транзисторов с униполярным типом канала (транзисторов с каналом n-типа или p-типа). В каждом из вариантов осуществления, описанных ниже, транзисторы с каналом n-типа используются в качестве примера. Компоновка с использованием транзисторов с каналом p-типа упоминается только в конце описания вариантов осуществления, и подробные пояснения такой компоновки опускаются в настоящем описании изобретения. Транзистор с униполярным типом канала может быть TFT или полевым транзистором в форме кремниевой подложки.

(Первый вариант осуществления)

Последующее описание поясняет компоновку схемы 10 настоящего варианта осуществления. Фиг.1 - это принципиальная схема, иллюстрирующая компоновку схемы 10, а Фиг.2 - это временная диаграмма, показывающая формы различных сигналов схемы 10.

Схема 10 включает в себя: транзистор T1 (первый транзистор); транзистор T2 (второй транзистор); транзистор T3 (третий транзистор) и конденсатор C1. В один конец конденсатора C1 вводится синхросигнал CK, имеющий частоту выше частоты выходного сигнала OUT схемы 10. В дальнейшем в этом документе напряжение (уровень сигнала), которое включает транзистор, когда приложено к контактному выводу затвора (управляющему контактному выводу), упоминается как "напряжение включения (уровень включения)", а напряжение (уровень сигнала), которое отключает транзистор, когда приложено к контактному выводу затвора, упоминается как "напряжение отключения (уровень отключения)". Для транзистора с каналом n-типа напряжение включения - это высокое напряжение (уровень включения - это высокий уровень), а напряжение отключения - это низкое напряжение (уровень отключения - это низкий уровень). С другой стороны, для транзистора с каналом p-типа напряжение включения - это низкое напряжение, а напряжение отключения - это высокое напряжение.

Как проиллюстрировано на Фиг.1, транзистор T1 расположен так, что его контактный вывод стока (первый контактный вывод) подключается к источнику VDD питания, а его контактный вывод затвора (управляющий контактный вывод) подключается к входному контактному выводу IN. Транзистор T2 расположен так, что (i) его контактный вывод стока (первый контактный вывод) подключается к источнику VDD питания, (ii) его контактный вывод затвора (управляющий контактный вывод) подключается к контактному выводу истока транзистора T1 и (iii) его контактный вывод истока (второй контактный вывод) подключается к выходному контактному выводу OUT.

Транзистор T3 расположен так, что его контактный вывод стока (первый контактный вывод) подключается к контактному выводу истока транзистора T1, контактному выводу затвора транзистора T2 и контактному выводу CK синхросигнала через конденсатор C1. Точкой соединения между транзисторами T1, T2 и T3 и конденсатором C1 является узел n1.

Таким образом, в отличие от традиционной схемы (полупроводниковой схемы 100), проиллюстрированной на Фиг.46, схема 10 настоящего варианта осуществления имеет такую компоновку, что синхросигнал CK, имеющий частоту выше частоты выходного сигнала OUT, вводится в один конец конденсатора C1, а другой конец конденсатора C1 подключается к узлу n1, который удерживает сигнал с высоким уровнем в высокоимпедансном состоянии. При этой компоновке становится возможным сохранять уровень электрического потенциала, чтобы выводить стабильный сигнал, на который почти не влияет шум. Последующее описание конкретно поясняет этот эффект наряду с работой схемы 10 со ссылкой на Фиг.2. Следует отметить, что сигналы в схеме 10, входной сигнал и выходной сигнал имеют электрический потенциал VDD, когда находятся на высоком уровне, и имеют электрический потенциал VSS (нуль), когда находятся на низком уровне, если не указано иное.

Когда входной сигнал IN переключается к высокому уровню (VDD), транзистор T1 включается и электрический потенциал в узле n1 увеличивается до "VDD-Vth (где Vth - это пороговое напряжение транзистора T1)" (операция предварительной зарядки). Когда электрический потенциал в узле n1 увеличивается, транзистор T2 включается. Когда входной сигнал IN переключается от высокого уровня к низкому уровню (VSS), узел n1 переходит в высокоимпедансное состояние при сохранении электрического заряда высокого уровня. В этом состоянии, если синхросигнал CK переключается к высокому уровню, электрический потенциал в узле n1 повышается на электрический потенциал α до "VDD-Vth+α" вследствие синхросигнала CK. В случае если этот электрический потенциал превышает "VDD+Vth", транзистор T2 выводит VDD в выходной контактный вывод OUT.

Как описано выше, сигнал, имеющий высокий электрический потенциал, вводится в контактный вывод затвора транзистора T2 в то время, когда электрический потенциал в узле n1 повышается посредством синхросигнала CK. Следовательно, транзистор T2 выводит сигнал, имеющий уровень электрического потенциала VDD, в выходной контактный вывод OUT, и одновременно выходной импеданс понижается (период t на Фиг.2).

После этого, когда сигнал STOP переключается к высокому уровню, транзистор T3 включается, так что электрический заряд в узле n1 разряжается. Как результат транзистор T2 отключается. Это вызывает выходной контактный вывод OUT быть в высокоимпедансном состоянии (см. области, указываемые посредством наклонных линий на Фиг.2).

Таким образом, в течение периода времени до тех пор, пока сигнал STOP не переключается к высокому уровню, выходной контактный вывод OUT нормально выводит VDD до тех пор, пока электрический потенциал в узле n1, повышенный посредством синхросигнала CK, не понижается ниже "VDD+Vth", вследствие тока утечки в отключенном состоянии транзистора T3 и т.п.

Дополнительно, как показано на Фиг.2, электрический потенциал в узле n1 увеличивается посредством операции повышения посредством синхросигнала CK, когда входной сигнал IN, находящийся на высоком уровне, вводится, и узел n1 предварительно заряжается. Следовательно, выходной сигнал быстро повышается (см. область, окруженную пунктирной линией), тем самым приводя к большей скорости возбуждения.

Здесь последующее описание поясняет работу схемы 10 в случае, если на схему 10 оказывает влияние ток утечки в отключенном состоянии и т.п., по сравнению с компоновкой традиционной схемы. Фиг.3 - это временная диаграмма, показывающая формы различных сигналов схемы 10, в случае если на схему 10 оказывает влияние ток утечки в отключенном состоянии и т.п. Фиг.4 - это временная диаграмма, показывающая формы различных сигналов традиционной схемы, проиллюстрированной на Фиг.46, в случае если на традиционную схему оказывает влияние ток утечки в отключенном состоянии и т.п.

В традиционной схеме, проиллюстрированной на Фиг.46, в случае если узел N1 имеет путь утечки, электрический потенциал в узле N1 постепенно понижается в течение периода времени, в котором синхросигнал φ находится на высоком уровне. Здесь, в случае если электрический потенциал в узле N1 понижается до "VDD-Vth" или менее вследствие утечки, электрический потенциал в узле N1 заряжается только до "VDD-Vth" (см. область, окруженную пунктирной линией на Фиг.4), даже если входной сигнал IN переключается к высокому уровню снова. Следовательно, выходной сигнал имеет высокий импеданс, тем самым становясь подверженным шуму. Дополнительно, в случае если выходной сигнал имеет утечку, электрический потенциал в узле N2 увеличивается только до "VDD-2×Vth", даже если узел N2 перезаряжен. По этой причине допустимый рабочий запас последующей схемы, подключенной к выходному контактному выводу OUT, понижается.

С другой стороны, в схеме 10 настоящего варианта осуществления, если электрический потенциал в узле n1 повышается посредством синхросигнала CK и затем понижается на электрический потенциал β вследствие утечки, электрический потенциал в узле n1 становится "VDD-Vth+α-β". Затем, когда синхросигнал CK переключается к низкому уровню, электрический потенциал в узле n1 понижается до "VDD-Vth-β". Тем не менее, на этой стадии, если входной сигнал IN находится на высоком уровне, электрический потенциал узла n1 заряжается до "VDD-Vth". Следовательно, когда синхросигнал CK переключается к высокому уровню снова, электрический потенциал в узле n1 повышается до "VDD-Vth+α" (см. область, окруженную пунктирной линией на Фиг.3). Вследствие этого можно стабильно сохранять электрический потенциал VDD, даже если выходной сигнал имеет утечку и т.п. Соответственно, последующая схема, подключенная к выходному сигналу, может стабильно управляться. Дополнительно, поскольку сигнал, имеющий высокий электрический потенциал, вводится в контактный вывод затвора транзистора T2, выходной сигнал OUT может сохранять низкий импеданс и может быть стабильным в отношении шума.

Таким образом, в компоновке схемы 10 настоящего варианта осуществления можно заряжать электрический потенциал в узле n1 до "VDD-Vth" снова, даже если выходной сигнал OUT имеет утечку и т.п. Поскольку частота синхросигнала CK задается так, чтобы быть выше частоты выходного сигнала, можно повышать снова, посредством операции повышения посредством синхросигнала CK, электрический потенциал в узле n1 до "VDD+Vth" или более до того, как сигнал STOP переключается к высокому уровню. Основываясь на этом, можно обеспечивать более длительный, чем в традиционной схеме, (i) период времени, в котором VDD может выводиться, и (ii) период времени низкого импеданса.

Здесь амплитуда синхросигнала CK и конденсатор CI задаются так, что повышенный электрический потенциал (VDD-Vth+α) в узле n1 составляет "VDD+Vth" или более.

В компоновке схемы 10, проиллюстрированной на Фиг.1, контактный вывод стока транзистора T2 подключается к источнику VDD питания. Следует отметить, что настоящее изобретение не ограничено этой компоновкой. Например, синхросигнал φ может вводиться в контактный вывод стока. Фиг.5 - это временная диаграмма, показывающая формы различных сигналов схемы 10, имеющей компоновку, в которой синхросигнал φ вводится в контактный вывод стока транзистора T2. В этой компоновке также можно выводить сигнал, вводимый в транзистор T2, при сохранении уровня электрического потенциала сигнала способом, аналогичным компоновке схемы 10, проиллюстрированной на Фиг.1. Следовательно, когда транзистор T2 включается, уровень электрического потенциала, эквивалентный синхросигналу φ, выводится.

(Второй вариант осуществления)

Последующее описание поясняет компоновку схемы 20 настоящего варианта осуществления. Фиг.6 - это принципиальная схема, иллюстрирующая компоновку схемы 20, а Фиг.7 - это временная диаграмма, показывающая формы различных сигналов схемы 20. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в варианте осуществления 1, используются идентичные номера ссылок, и пояснения этих элементов опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в варианте осуществления 1, также используются в настоящем варианте осуществления так, как определено в варианте осуществления 1, если не указано иное.

Здесь в компоновке (см. Фиг.1) схемы 10, описанной в варианте осуществления 1, во время, когда сигнал STOP переключается к высокому уровню и электрический потенциал в узле n1 становится низким уровнем, выходной контактный вывод OUT переходит в высокоимпедансное состояние (см. области, указываемые посредством наклонных линий на Фиг.2). Это вызывает влияние шума на выходной сигнал.

Чтобы исключать это высокоимпедансное состояние, схема 20 настоящего варианта осуществления имеет такую компоновку, что схема 10 дополнительно включает в себя транзистор T4 (четвертый транзистор). Как проиллюстрировано на Фиг.6, транзистор T4 расположен так, что (i) его контактный вывод стока (первый контактный вывод) подключается к контактному выводу истока транзистора T2 и выходному контактному выводу OUT, (ii) его контактный вывод истока (второй контактный вывод) подключается к источнику VSS питания и (iii) его контактный вывод затвора (управляющий контактный вывод) подключается к контактному выводу затвора транзистора T3. Контактные выводы затворов транзисторов T3 и T4 подключаются к входному контактному выводу IN2. Входной сигнал IN2 для управления включенным/отключенным состоянием каждого из транзисторов T3 и T4 вводится в каждый из контактных выводов затвора. Точка соединения между транзистором T2, транзистором T4 и выходным контактным выводом OUT - это узел n2.

При такой компоновке, как показано на Фиг.7, во время, когда электрический потенциал в узле n1 становится низким уровнем, входной сигнал IN2, имеющий высокий уровень, вводится так, что транзисторы T3 и T4 включаются. Следовательно, электрический заряд в узле n1 может успешно разряжаться, и одновременно уровень электрического потенциала выходного сигнала может быть стабилизирован на низком уровне (VSS).

Следует отметить, что сигнал, вводимый в контактный вывод затвора транзистора T4, не ограничен конкретным образом и может быть другим управляющим сигналом до тех пор, пока сигнал может стабилизировать уровень электрического потенциала выходного сигнала OUT на низком уровне (VSS).

(Третий вариант осуществления)

Последующее описание поясняет компоновку схемы 30 настоящего варианта осуществления. Фиг.8 - это принципиальная схема, иллюстрирующая компоновку схемы 30. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в вариантах осуществления 1 и 2, используются идентичные номера ссылок, и их пояснения опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в вариантах осуществления 1 и 2, также используются в настоящем варианте осуществления так, как определено в вариантах осуществления 1 и 2, если не указано иное.

Схема 30 настоящего варианта осуществления имеет такую компоновку, что схема 20, проиллюстрированная на Фиг.6, дополнительно включает в себя транзистор T5 (пятый транзистор), который играет роль функции обновления. Как проиллюстрировано на Фиг.8, транзистор T5 расположен так, что (i) его контактный вывод стока (первый контактный вывод) подключается к источнику VDD питания, (ii) его контактный вывод истока (второй контактный вывод) подключается к узлу n1 и (iii) его контактный вывод затвора (управляющий контактный вывод) подключается к узлу n2.

При такой компоновке выходной сигнал OUT вводится в контактный вывод затвора транзистора T5. Следовательно, даже если электрический потенциал в узле n1 понижается вследствие тока утечки в отключенном состоянии и т.п. при условии, что входной сигнал IN1 находится на низком уровне и транзистор T1 находится в выключенном состоянии, электрический потенциал в узле n1 может заряжаться снова до "VDD-Vth" в течение периода времени, в котором выходной сигнал OUT находится на высоком уровне (операция обновления). Вследствие этого в течение периода времени, в котором синхросигнал CK находится на высоком уровне, электрический потенциал в узле n1 может повышаться до "VDD-Vth+α". Следовательно, выходной сигнал OUT может стабильно выводить VDD и может управлять нормально и без ложного срабатывания в течение периода работы в низкочастотном режиме.

(Четвертый вариант осуществления)

Последующее описание поясняет компоновку схемы 40 настоящего варианта осуществления. Фиг.9 - это принципиальная схема, иллюстрирующая компоновку схемы 40, а Фиг.10 - это временная диаграмма, показывающая формы различных сигналов схемы 40. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в вариантах осуществления 1-3, используются идентичные номера ссылок, и их пояснения опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в вариантах осуществления 1-3, также используются в настоящем варианте осуществления так, как определено в вариантах осуществления 1-3, если не указано иное.

Схема 40 настоящего варианта осуществления имеет такую компоновку, что схема 20, проиллюстрированная на Фиг.6, дополнительно включает в себя транзистор T6 (шестой транзистор) между входным контактным выводом IN1 и транзистором T1. Как проиллюстрировано на Фиг.9, транзистор T6 расположен так, что (i) его контактный вывод стока (первый контактный вывод) подключается к входному контактному выводу IN1, (ii) его контактный вывод истока (второй контактный вывод) подключается к контактному выводу затвора транзистора T1 и (iii) его контактный вывод затвора (управляющий контактный вывод) принимает сигнал EN разрешения. Дополнительно, контактный вывод истока транзистора T6 также подключается к точке соединения (узел n2) между транзисторами T2 и T4.

При такой компоновке, после того как сигнал EN разрешения переключается к высокому уровню, независимо от того, переключается или нет сигнал EN разрешения к низкому уровню позднее, можно сохранять ввод сигнала, имеющего высокий уровень, в контактный вывод затвора транзистора T1 в течение периода времени, в котором выходной сигнал OUT имеет высокий уровень. Это позволяет сохранять схему 40 в активном состоянии.

Дополнительно, выходной контактный вывод OUT и контактный вывод затвора транзистора T1 подключаются друг к другу. Следовательно, в случае если электрический потенциал в узле n1 понижается до "VDD-Vth" или менее в периоде времени, в котором выходной сигнал OUT имеет высокий уровень, транзистор T1 включается. Следует отметить, что когда электрический потенциал в узле n1 увеличивается до "VDD-Vth" или более, транзистор T1 отключается и узел n1 переходит в высокоимпедансное состояние.

Вследствие этого, даже если электрический потенциал в узле n1 понижается вследствие тока утечки в отключенном состоянии и т.п., электрический потенциал в узле n1 может заряжаться снова до "VDD-Vth" посредством транзистора T1 в течение периода времени, в котором выходной сигнал OUT имеет высокий уровень (операция обновления). Соответственно, в течение периода времени, в котором синхросигнал CK имеет высокий уровень, электрический потенциал в узле n1 может повышаться до "VDD-Vth+α". Следовательно, выходной сигнал OUT может стабильно выводить VDD и может управлять нормально и без ложного срабатывания в течение периода работы в низкочастотном режиме.

Здесь транзистор T6 не ограничен вышеуказанной компоновкой, проиллюстрированной на Фиг.9. Например, транзистор T6 может быть расположен таким образом, что его контактный вывод истока переходит в высокоимпедансное состояние, когда входной сигнал IN1 имеет электрический потенциал низкого уровня. Фиг.11 и 12 конкретно иллюстрируют примеры такой компоновки. В компоновке, проиллюстрированной на Фиг.11, контактный вывод стока транзистора T6 подключается к источнику VDD питания, и входной сигнал IN1 вводится в контактный вывод затвора транзистора T6. Дополнительно, в компоновке, проиллюстрированной на Фиг.12, входной сигнал IN1 вводится в контактный вывод стока и контактный вывод затвора транзистора T6. Эти компоновки являются подходящими для компоновки без использования другого сигнала (например, сигнала EN разрешения), в которой, после того как входной сигнал IN1 становится активным (высокий уровень), активное состояние сохраняется независимо от того, переключается или нет входной сигнал IN1 к низкому уровню позднее.

(Пятый вариант осуществления)

Последующее описание поясняет компоновку схемы 50 настоящего варианта осуществления. Фиг.13 - это принципиальная схема, иллюстрирующая компоновку схемы 50. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в вариантах осуществления 1-4, используются идентичные номера ссылок, и их пояснения опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в вариантах осуществления 1-4, также используются в настоящем варианте осуществления так, как определено в вариантах осуществления 1-4, если не указано иное.

Здесь, в компоновках схем, описанных в вариантах осуществления 1-4, в случае если входной сигнал IN имеет низкий уровень в начальном состоянии, величина электрического заряда, заряжаемого в конденсаторе, C1 не обнаруживается, и электрический потенциал в узле n1 является нестабильным. Следовательно, эти компоновки являются нестабильными в начальном состоянии.

Чтобы реализовывать стабильное начальное состояние, схема 50 настоящего варианта осуществления имеет такую компоновку, что любые компоновки в соответствии с вариантами осуществления 1-4 дополнительно включают в себя транзистор T7 (седьмой транзистор). Схема 50, проиллюстрированная на Фиг.13, имеет такую компоновку, что схема 10, проиллюстрированная на Фиг.1, включает в себя транзистор T7. Транзистор T7 расположен так, что (i) его контактный вывод затвора (управляющий контактный вывод) принимает сигнал INI инициализации, (ii) его контактный вывод истока (второй контактный вывод) подключается к источнику VSS питания и (iii) его контактный вывод стока (первый контактный вывод) подключается к узлу n1.

При такой компоновке сигнал INI инициализации, имеющий высокий уровень, вводится в начальном состоянии, так что электрический потенциал узла n1 может быть стабилизирован на VSS. Следовательно, можно стабилизировать начальное состояние.

Следует отметить, что можно стабилизировать начальное состояние любой из схем в соответствии с вариантами осуществления 2-4 посредством предоставления в схеме транзистора T7 таким же образом, как описано выше.

(Шестой вариант осуществления)

Последующее описание поясняет компоновку схемы 60 настоящего варианта осуществления. Фиг.14 - это принципиальная схема, иллюстрирующая компоновку схемы 60. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в вариантах осуществления 1-5, используются идентичные номера ссылок, и их пояснения опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в вариантах осуществления 1-5, также используются в настоящем варианте осуществления так, как определено в вариантах осуществления 1-5, если не указано иное.

Здесь любая из компоновок схем в соответствии с вариантами осуществления 1-5 имеет такую проблему, что требуется большая емкость контактного вывода CK синхросигнала. Последующее описание конкретно поясняет нагрузку синхронизации с использованием схемы 10, проиллюстрированной на Фиг.1, в качестве примера.

В случае если электрический потенциал в узле n1 имеет высокий уровень ("VDD-Vth" или более), т.е. период времени, в котором узел n1 находится в высокоимпедансном состоянии, емкость контактного вывода CK синхросигнала может быть выражена посредством следующего равенства:

1/емкость контактного вывода CK синхросигнала=1/C1+1/Ctr (где Ctr - это сумма паразитных емкостей транзисторов T1, T2 и T3) (1).

Следует отметить, что проводная нагрузка и т.п. опускается в равенстве для простоты пояснения.

Здесь, чтобы значительно повышать электрический потенциал в узле n1, требуется "C1>Ctr". Например, для повышения напряжения узла n1 на "2×Vp/3" относительно амплитуды Vp синхросигнала CK требуется "C1:Ctr=2:1". Посредством подстановки этого равенства в равенство (1) следующее равенство может получаться:

емкость контактного вывода CK синхросигнала=1/3×C1.

Затем, в случае если электрический потенциал в узле n1 имеет низкий уровень (VSS), т.е. период времени, в котором узел n1 не находится в высокоимпедансном состоянии, емкость контактного вывода CK синхросигнала может быть выражена посредством следующего равенства:

емкость контактного вывода CK синхросигнала=C1.

Таким образом, обнаруживается то, что емкость контактного вывода CK синхросигнала является большой в то время, когда узел n1 не находится в высокоимпедансном состоянии. В частности, в случае если множество схем, последовательно подключенных, принимают тот же синхросигнал CK через свои контактные выводы CK синхросигнала, емкость контактного вывода CK синхросигнала становится очень большой.

Чтобы уменьшать эту нагрузку синхронизации, схема 60 настоящего варианта осуществления имеет такую компоновку, что любые схемы в соответствии с вариантами осуществления 1-5 дополнительно включают в себя транзистор T8 (восьмой транзистор). Схема 60, проиллюстрированная на Фиг.14, имеет такую компоновку, что схема 10, проиллюстрированная на Фиг.1, включает в себя транзистор T8. Транзистор T8 расположен так, что (i) его контактный вывод затвора (управляющий контактный вывод) подключается к входному контактному выводу IN, (ii) его контактный вывод стока (первый контактный вывод) подключается к контактному выводу CK синхросигнала и (iii) его контактный вывод истока (второй контактный вывод) подключается к узлу n1 через конденсатор C1.

В схеме 60 вследствие транзистора T8 можно отключать контактный вывод CK синхросигнала и конденсатор C1 друг от друга в течение периода времени, в котором узел n1 не переходит в высокоимпедансное состояние, и нагрузка контактного вывода CK синхросигнала становится очень большой.

В частности, в случае если электрический потенциал в узле n1 стабилизирован на VSS, узел n1 не требует повышать посредством синхросигнала CK. Следовательно, посредством электрического отделения контактного вывода CK синхросигнала и конденсатора C1 друг от друга посредством использования транзистора T8 в течение периода времени, в котором электрический потенциал узла n1 стабилизирован на VSS, нагрузка контактного вывода CK синхросигнала становится только паразитной емкостью транзистора T8, которая является очень небольшой.

Соответственно, с уменьшением требуемой возбуждающей способности схемы для возбуждения контактного вывода CK синхросигнала и уменьшением емкости контактного вывода CK синхросигнала, можно снизить потребление электроэнергии.

Здесь, чтобы стабилизировать электрический потенциал в узле n3, предоставленном между транзистором T8 и конденсатором C1, в течение периода времени, в котором транзистор T8 находится в выключенном состоянии, схема 60 дополнительно может включать в себя транзистор T9 и инвертор 6, включающий в себя сопротивление R1 и транзистор T11, как проиллюстрировано на Фиг.15. В этой компоновке транзистор T9 расположен так, что (i) его контактный вывод стока подключается к узлу n3, (ii) его контактный вывод истока подключается к источнику VSS питания и (iii) его контактный вывод затвора подключается к входному контактному выводу IN, который подключается к инвертору 6. При этой компоновке, в случае если транзисторы T1 и T8 отключаются, транзисторы T3 и T9 включаются, так что электрические потенциалы в узле n1 и узле n3 могут быть стабилизированы на VSS.

Дополнительно, контактный вывод затвора транзистора T8, проиллюстрированного на Фиг.14, подключается к входному контактному выводу IN. Сигнал, вводимый в контактный вывод затвора транзистора T8, не ограничен конкретным образом. Можно вводить в течение периода времени, в котором электрический потенциал в узле n1 стабилизирован на VSS, или в течение части такого периода времени другой управляющий сигнал для управления транзистором T8, который должен отключаться.

Дополнительно, на Фиг.15, инверсный сигнал входного контактного вывода IN создается посредством инвертора 6 и выводится во входной контактный вывод INB. Тем не менее, в случае если имеется другой управляющий сигнал в качестве инверсного сигнала сигнала, вводимого во входной контактный вывод IN, управляющий сигнал может вводиться во входной контактный вывод INB как инверсный сигнал.

Кроме того, схема 60 дает уменьшение электроэнергии, потребляемой посредством конденсатора. Тем не менее, можно иметь, посредством операции внешней синхронизации, (i) компоновку, в которой синхросигнал CK стабилизирован на определенном уровне DC в течение периода времени, в котором электрический потенциал в узле n1 стабилизирован на VSS, или (ii) компоновку, в которой частота синхросигнала CK замедлена в целях уменьшения потребления электроэнергии в течение периода времени, в котором электрический потенциал в узле n1 стабилизирован на VSS.

Следует отметить, что вышеуказанная компоновка настоящего варианта осуществления для уменьшения нагрузки синхронизации посредством использования транзистора T8 может быть надлежащим образом применимой к любым схемам в соответствии с вариантами осуществления 1-5 способом, аналогичным настоящему варианту осуществления.

(Седьмой вариант осуществления)

Последующее описание поясняет компоновку схемы 70 настоящего варианта осуществления. Фиг.16 - это принципиальная схема, иллюстрирующая компоновку схемы 70. Следует отметить, что относительно элементов, имеющих функции, идентичные функциям элементов, описанных в вариантах осуществления 1-6, используются идентичные номера ссылок, и их пояснения опускаются в данном документе для простоты пояснения. Дополнительно, термины, определенные в вариантах осуществления 1-6, также используются в настоящем варианте осуществления так, как определено в вариантах осуществления 1-6, если не указано иное.

Здесь для любой компоновки схем в соответствии с вариантами осуществления 1-6 операция повышения посредством синхросигнала CK заставляет узел n1 иметь высокий электрический потенциал "VDD-Vth+α". Следовательно, возникает риск того, что высокое напряжение прикладывается к транзистору, подключенному к узлу n1, в частности, (i) между затвором и истоком, (ii) между затвором и стоком и (iii) между истоком и стоком, так что транзистор может быть поврежден вследствие высокого напряжения, превышающего выдерживаемое напряжение транзистора.

А именно в схеме 10 высокое напряжение прикладывается, в частности, (i) между затвором и стоком транзистора T3 и (ii) между истоком и стоком транзистора T3. В случае если входной сигнал IN находится на VSS и электрический потенциал в узле n1 повышается, электрический потенциал в узле n1 увеличивается до "VDD-Vth+α". Следовательно, как напряжение между затвором и стоком транзистора T3, так и напряжение между истоком и стоком транзистора T3 становятся "VDD-Vth+α-VSS". Здесь может получаться следующее равенство:

"VDD-Vth+α-VSS=35В-Vth (где VDD=10В, VSS=-10В и=15В)".

С другой стороны, к другим узлам прикладывается разность электрических потенциалов 20В между VDD и VSS. Таким образом, высокое напряжение прикладывается к транзистору, подключенному к узлу n1.

Следовательно, чтобы защищать транзистор от такого высокого напряжения, схема 70 настоящего варианта осуществления имеет такую компоновку, что любая из схем в соответствии с вариантами осуществления 1-6 дополнительно включает в себя транзистор T10 (десятый транзистор). Схема 70, проиллюстрированная на Фиг.16, имеет такую компоновку, что схема 10, проиллюстрированная на Фиг.1, включает в себя транзистор T10. Транзистор T10 расположен так, что (i) его контактный вывод затвора (управляющий контактный вывод) подключается к источнику VDD питания, (ii) его контактный вывод стока (первый контактный вывод) подключается к узлу n1 и (iii) его контактный вывод истока (второй контактный вывод) подключается к контактному выводу стока транзистора T3. Точкой соединения между транзисторами T3 и T10 является узел n4.

При такой компоновке, в случае если входной сигнал IN находится на VSS, электрический потенциал в узле n1 увеличивается до "VDD-Vth+α", а электрический потенциал в узле n4 увеличивается только до "VDD-Vth". Следовательно, как напряжение между затвором и стоком транзистора T3, так и напряжение между истоком и стоком транзистора T3 становятся "VDD-Vth-VSS=20В-Vth", что ниже на электрический потенциал α, чем напряжения в схеме 10.

Дополнительно, транзистор T10 имеет такие низкие напряжения, что электрический потенциал между затвором и стоком составляет "α-Vth=15В-Vth", электрический потенциал между затвором и истоком составляет Vth, а электрический потенциал между истоком и стоком составляет "α=15В".

Поэтому, даже если электрический потенциал в узле n1, находящемся в высокоимпедансном состоянии, повышается вследствие синхросигнала CK, можно уменьшать нагрузку по напряжению, прикладываемому к транзистору, подключенному к узлу n1. Следовательно, можно создавать высоконадежную схему.

Вышеуказанная компоновка настоящего варианта осуществления, для защиты транзистора от высокого напряжения, является применимой к любой схеме в соответствии с вариантами осуществления 1-6 способом, аналогичным настоящему варианту осуществления. Фиг.17 иллюстрирует пример, в котором компоновка настоящего варианта осуществления применяется к схеме в соответствии с вариантом осуществления 6, причем эта схема проиллюстрирована на Фиг.15.

Здесь любая из схем в соответствии с вариантами осуществления 1-7 имеет компоновку, в которой контактный вывод стока транзистора T1 подключается к источнику VDD питания. Тем не менее, компоновка схемы настоящего изобретения не ограничена этой компоновкой. Например, можно подключать контактный вывод стока и контактный вывод затвора транзистора T1 друг к другу, т.е. иметь диодное включение. Фиг.18-24 являются принципиальными схемами, которые иллюстрируют компоновки схем 11, 21, 31, 41, 51, 61 и 71 соответственно. Компоновки схем 11-71 соответствуют компоновкам схем 10, 20, 30, 40, 50, 60 и 70 соответственно, в каждой из этих компоновок транзистор T1 имеет диодное включение. Например, в случае когда транзистор T1 расположен так, как в схеме 10, если шум формируется относительно входного сигнала в то время, когда транзистор T3 находится во включенном состоянии, и входной сигнал, вводимый во входной контактный вывод IN, имеет низкий уровень, транзистор T1 включается мгновенно. Из этого следует, что сквозной ток протекает от источника VDD питания к источнику VSS питания через транзисторы T1 и T3, тем самым вызывая увеличение потребляемого тока или ложное срабатывание. С учетом этой проблемы, в компоновке с использованием диодного включения контактный вывод затвора и контактный вывод стока транзистора T1 подключаются друг к другу так, что даже если формирование шума относительно входного контактного вывода IN вызывает включение транзистора T1, разность электрических потенциалов между источником и стоком равняется только электрическому потенциалу шума. Следовательно, по сравнению со случаем, где контактный вывод стока подключается к источнику VDD питания, разность электрических потенциалов между истоком и стоком меньше, так что сквозной ток меньше. Дополнительно, поскольку транзистор T3 находится во включенном состоянии, даже если транзистор T1 включается вследствие шума, электрический потенциал, колеблющийся вследствие шума, формируемого относительно входного контактного вывода IN, отводится в направлении источника VSS питания через транзистор T3. Таким образом, на транзистор T1 оказывается такое влияние, чтобы отключить его. Следовательно, можно предотвращать ложное срабатывание транзистора T1 вследствие влияния шума.

Фиг.25 - это временная диаграмма, показывающая формы различных сигналов схемы 11, проиллюстрированной на Фиг.18, из схем, описанных выше, в каждой из которых транзистор T1 имеет диодное включение. Как показано на Фиг.25 способом, аналогичным компоновке схемы 10, проиллюстрированной на Фиг.1, можно выводить сигнал при сохранении уровня электрического потенциала сигнала, вводимого в контактный вывод стока транзистора T2. Следовательно, когда транзистор T2 включается, VDD выводится.

Дополнительно, компоновка, поясненная в варианте осуществления 1, описанном выше, причем в этой компоновке синхросигнал φ вводится в контактный вывод стока транзистора T2, также является применимой к любой из схем в соответствии с вариантами осуществления, описанными выше. В этом случае, когда транзистор T2 включается, выводится уровень электрического потенциала синхросигнала φ.

Между тем, синхросигнал CK, вводимый в схему сохранения активного сигнала настоящего изобретения, показывает такую форму сигнала, что высокий уровень и низкий уровень повторяются попеременно и периодически, как показано на Фиг.26. Как описано выше, выходной сигнал OUT схемы сохранения активного сигнала имеет низкий импеданс, в частности, в то время, когда синхросигнал CK имеет высокий уровень (период T). Следовательно, в течение периода времени, в котором коэффициент заполнения синхросигнала CK составляет, например, 50%, как показано на Фиг.26, выходной сигнал OUT имеет низкий импеданс. Таким образом, посредством регулирования коэффициента заполнения синхросигнала CK становится возможным регулировать период времени, в течение которого выходной сигнал OUT имеет низкий импеданс.

Здесь последующее описание поясняет предпочтительное значение коэффициента заполнения синхросигнала CK посредством обращения к компоновке, проиллюстрированной на Фиг.1. Как описано выше, когда синхросигнал CK переключается к низкому уровню, электрический потенциал в узле n1 понижается до "VDD-Vth-β" вследствие тока утечки в отключенном состоянии и т.п. Здесь идеальный коэффициент заполнения - это "период высокого уровня:период низкого уровня=T1-tβ:tβ (где tβ является периодом времени, требуемым для того, чтобы перезаряжать электрический потенциал в узле n1 до "VDD-Vth", и T1 составляет один цикл)". Дополнительно, период времени, необходимый для синхросигнала CK, чтобы переключаться от высокого уровня к низкому уровню, определяется в соответствии с постоянной времени нагрузки (емкости и сопротивления) контактного вывода CK синхросигнала. Период времени, необходимый для синхросигнала CK, чтобы переключаться от высокого уровня к низкому уровню (или наоборот), упоминается как "tck". Если tck не обеспечено как ширина импульса, невозможно получать требуемое повышающее напряжение α для повышения в узле n1. Следовательно, с учетом постоянной времени, идеальный коэффициент заполнения - это "период высокого уровня:период низкого уровня=T1-tck:tck".

На практике перезарядка для компенсации снижения вследствие тока утечки в отключенном состоянии и т.п. и переключения синхросигнала CK от высокого уровня к низкому уровню выполняется одновременно. Следовательно, с учетом обоих этих факторов, идеальный коэффициент заполнения - это "период высокого уровня:период низкого уровня=T1-tβ':tβ' (где tβ' является периодом времени, необходимым для того, чтобы перезаряжать электрический потенциал в узле n1 до "VDD-Vth")". При этом коэффициенте заполнения становится возможным понижать выходной импеданс транзистора T2 при сохранении активного состояния схемы в нормальных условиях.

Согласно пояснению, описанному выше, предпочтительно задавать коэффициент заполнения синхросигнала таким образом, что период времени низкого уровня в одном цикле синхросигнала CK является эквивалентным периоду времени от времени, когда синхросигнал CK переключается от высокого уровня к низкому уровню, до времени, когда электрический потенциал в узле n1 насыщается.

Дополнительно, предпочтительно задавать коэффициент заполнения так, что период времени, в котором транзистор T2 демонстрирует низкий импеданс, является более длительным.

Следует отметить, что в случае, если период времени для переключения синхросигнала CK больше чем 50%, синхросигнал CK переключается к следующему высокому уровню перед полным переключением к низкому уровню. Поэтому, чтобы получать напряжение α вольтодобавки, необходимо вызвать (регулировать) конденсатор C1, чтобы он был больше. Это приводит к схеме большего размера или увеличению нагрузки конденсатора, тем самым требуя более длительного периода времени для переключения. Чтобы избежать этого, в общем, период времени для переключения задается так, чтобы находиться в рамках 50%, посредством замедления частоты синхросигнала или посредством задания, чтобы нагрузка, возбуждаемая посредством синхросигнала CK была меньше. Следовательно, предпочтительно, чтобы коэффициент заполнения составлял 50% или более, чтобы вызвать период времени, в котором транзистор T2 демонстрирует низкий импеданс, быть насколько возможно более длительным.

Фиг.26 показывает синхросигнал CK_H, который является примером формы сигнала, заданной так, что период T высокого уровня является более длительным (коэффициент заполнения задан так, чтобы быть больше). Это позволяет задавать более длительный период времени, в котором выходной сигнал OUT схемы сохранения активного сигнала имеет низкий импеданс. Вследствие более длительного периода времени низкого импеданса выходной сигнал может быть более стабильным в отношении шума и нагрузка может возбуждаться более быстро. Таким образом, предпочтительно, чтобы синхросигнал CK имел частоту выше частоты выходного сигнала OUT и одновременно был на высоком уровне (электрический потенциал на активной стороне) в течение периода времени, более длительного, чем низкий уровень.

Следует отметить, что в случае, если транзистор с каналом p-типа используется, логика полностью изменяется на противоположную. Следовательно, в таком случае, предпочтительно, чтобы синхросигнал CK имел низкий уровень в течение периода времени, более длительного, чем имел высокий уровень, по причине, аналогичной описанной выше.

Каждая из схем (схем сохранения активного сигнала) в соответствии с вариантами осуществления 1-7, описанными выше, может надлежащим образом использоваться, в частности, в жидкокристаллическом дисплейном устройстве (дисплейном устройстве). Фиг.27 - это блок-схема, иллюстрирующая полную компоновку жидкокристаллического дисплейного устройства.

Жидкокристаллическое дисплейное устройство 151 включает в себя панель 152, на которой жидкокристаллическое дисплейное устройство 151 дополнительно включает в себя: пиксельную область 153; формирователь 154 истока; формирователь 155 затвора/CS; схему 156 BUFF/модуля сдвига уровня; схему 157 электропитания; и контактные выводы 158.... Формирователь 154 истока включает в себя выходную схему 154a и выводит сигнал данных в каждую из линий шины истока пиксельной области 153. Формирователь 155 затвора/CS включает в себя выходную схему 155a и выводит (i) сигнал выбора в линии шины затвора с тем, чтобы записывать, в каждый пиксел пиксельной области 153, сигнал данных, выводимый из формирователя 154 истока, и (ii) сигнал CS в линии шины CS с тем, чтобы вызвать повышение записывающего электрического потенциала относительно каждого пиксела пиксельной области 153. Каждая из выходных схем 154a и 155a состоит из буфера, который является схемой усиления для формирования сигнала данных со 100-процентным усилением в соответствии с входным сигналом, причем схема усиления имеет низкий выходной импеданс. Схема 156 BUFF/модуля сдвига уровня включает в себя буфер, который является схемой усиления, имеющей низкий выходной импеданс, такой как схема 100-процентного усиления, для компенсации ослабления сигнала инвертора и т.п., и схему модуля сдвига уровня для преобразования уровня источника питания сигнала. Схема 156 BUFF/модуля сдвига уровня предоставляет в формирователь 154 истока и формирователь 155 затвора сигнал, подвергнутый процессу этого буфера. Схема 157 электропитания формирует электропитание для логической схемы, опорное напряжение сигнала данных, противодействующее напряжение сигнала данных, напряжение вспомогательной емкости и т.п. Каждый из контактных выводов 158... является контактным выводом для ввода сигнала и электропитания в каждую из вышеуказанных схем, предоставленных на панели 152. Следует отметить, что жидкокристаллическое дисплейное устройство может включать в себя демультиплексор вместо формирователя истока.

Каждая из схем в соответствии с вариантами осуществления 1-7 является применимой к любой части жидкокристаллического дисплейного устройства 151. В частности, каждая из схем является надлежащим образом применимой к переключателю, предоставленному в CS-формирователе, буферной схеме, схеме модуля сдвига уровня и модулю сопротивления сдвигу, предоставленному в каждом формирователе истока (возбуждающей схеме линии сигналов данных) и формирователе затвора (возбуждающей схеме линии сигналов сканирования). Последующее описание поясняет примеры такого применения: пример 1, в котором схема применяется к запоминающей схеме, предоставленной в CS-формирователе; примеры 2-4, в каждом из которых схема применяется к буферной схеме и схеме модуля сдвига уровня; и пример 5, в котором схема применяется к модулю сопротивления сдвигу.

Пример 1

Фиг.28 - это блок-схема, иллюстрирующая компоновку запоминающей схемы 1, предоставленной в CS-формирователе настоящего примера, а Фиг.29 - это принципиальная схема запоминающей схемы 1. Фиг.30 - это временная диаграмма, показывающая формы различных сигналов запоминающей схемы 1. Запоминающая схема 1 включает в себя две схемы (схемы сохранения активного сигнала), соответствующие любой из схем, описанных в вариантах осуществления, описанных выше. В частности, например, запоминающая схема 1 имеет такую компоновку, что контактный вывод STOP одной из схем 10 (которая упоминается как "схема 10b"), проиллюстрированной на Фиг.1, и выходной контактный вывод OUT другой одной из схем 10 (которая упоминается как "схема 10a") подключаются друг к другу. Следует отметить, что запоминающая схема должна иметь только, по меньшей мере, компоновку схемы 10, проиллюстрированной на Фиг.1. Запоминающая схема 1 настоящего примера имеет такую компоновку, что схема 10 дополнительно включает в себя транзистор T4 (на Фиг.28 транзисторы Ta4 и Tb4), что является компоновкой схемы 20, проиллюстрированной на Фиг.6.

Затем ниже описывается работа запоминающей схемы 1. Здесь следующие пояснения направлены на пример, в котором входной сигнал IN, имеющий высокий уровень, вводится в схему 10a, а входной сигнал INB (инверсный сигнал входного сигнала IN), имеющий низкий уровень, вводится в схему 10b в то время, когда сигнал EN разрешения имеет высокий уровень.

Когда сигнал, имеющий высокий уровень, вводится в схему 10a, схема 10a переходит в активное состояние. Электрический заряд сохраняется в узле na1 в то время, когда синхросигнал вводится. Следовательно, как описано в каждом из вышеуказанных вариантов осуществления, выходной сигнал OUT VDD выводится из схемы 10a. Этот выходной сигнал OUT вводится в контактный вывод STOP (см. Фиг.29) другой схемы 10b.

При приеме сигнала VDD схема 10b переходит в неактивное состояние и выводит VSS через транзистор Tb4. Полярности входных сигналов IN и INB являются противоположными друг другу, так что одна из схем выводит VDD в то время, когда другая из схем выводит VSS. Следовательно, в течение периода времени, в котором вводится синхросигнал CK, электрические потенциалы схем 10a и 10b сохраняются до тех пор, пока следующий сигнал EN разрешения не переключается к высокому уровню.

Следует отметить, что запоминающая схема 1, проиллюстрированная на Фиг.28, имеет компоновку, в которой инверсный сигнал INB входного сигнала IN вводится внешне, но настоящее изобретение не ограничено этой компоновкой. Например, в качестве еще одной компоновки можно создавать схему инвертора в запоминающей схеме 1 так, чтобы создавать инверсный сигнал INB на основе входного сигнала IN, как проиллюстрировано на Фиг.31 и 32. Фиг.31 иллюстрирует инвертор, состоящий из сопротивления R1 и транзистора T11, а Фиг.32 иллюстрирует инвертор, состоящий из схемы компенсационной обратной связи. При этих компоновках сигнал, имеющий низкий уровень (VSS), выводится как инверсный сигнал INB в то время, когда входной сигнал IN имеет высокий уровень (VDD), тогда как сигнал, имеющий высокий уровень (VDD), выводится как инверсный сигнал INB в то время, когда входной сигнал IN имеет низкий уровень (VSS).

Дополнительно, чтобы стабилизировать начальное состояние, запоминающая схема 1, проиллюстрированная на Фиг.28, дополнительно может включать в себя транзисторы T7 (см. Фиг.13), описанные в варианте осуществления 5, например, в соответствующих схемах 10a и 10b. Транзистор Ta7 схемы 10a и транзистор Tb7 схемы 10b расположены таким образом, что (i) сигнал INI инициализации вводится в их контактный вывод затвора, (ii) их контактные выводы стока подключаются к узлу na1 и узлу nb1 соответственно и (iii) их контактные выводы истока подключаются к источнику VSS питания и источнику VDD питания соответственно. При этой компоновке становится возможным стабилизировать начальное состояние посредством ввода, в начальном состоянии, сигнала INI инициализации, имеющего высокий уровень.

Следует отметить, что запоминающая схема 1 имеет функцию обновления, описанную в вышеуказанных вариантах осуществления, с тем чтобы иметь возможность сохранять значение в нормальных условиях, даже если подвергается низкочастотному возбуждению.

В настоящем примере запоминающая схема 1 включает в себя схему 20 в соответствии с вариантом осуществления 2, но настоящее изобретение не ограничено этим. Запоминающая схема 1 может включать в себя любую из схем (например, схему 30, схему 40 или схему 50) в соответствии с другими вариантами осуществления. Компоновка с использованием такой схемы также может реализовывать эффекты, аналогичные эффектам настоящего примера.

Пример 2

Фиг.33 - это блок-схема, иллюстрирующая компоновку буферной схемы 2 настоящего примера, а Фиг.34 - это принципиальная схема буферной схемы 2. Буферная схема 2 включает в себя любую одну из схем (схем сохранения активного сигнала) в соответствии с вариантами осуществления, описанными выше. В частности, буферная схема 2 должна иметь только, по меньшей мере, компоновку схемы 10, проиллюстрированной на Фиг.1. Буферная схема 2 настоящего примера имеет такую компоновку, что схема 10 дополнительно включает в себя транзистор T4, что является компоновкой схемы 20, проиллюстрированной на Фиг.6.

Здесь инвертор для формирования сигнала INB, который должен вводиться в схему 10, состоит из сопротивления R1 и транзистора T11. Следовательно, в случае если входной сигнал IN инвертора имеет высокий уровень, неизменный ток (сквозной ток) протекает от источника VDD питания к источнику VSS питания, тем самым увеличивая потребление электроэнергии. Чтобы снизить потребление электроэнергии, сопротивление R может иметь более высокое значение сопротивления. Тем не менее, в этом случае возникают другие новые проблемы, такие как снижение возбуждающей способности и увеличение подверженности шуму.